## Stratix GX Transceiver User Guide

101 Innovation Drive San Jose, CA 95134 (408) 544-7000 http://www.altera.com

UG-STXGX-3.0 P25-10021-02

Copyright © 2005 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device designations, and all other words and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and other countries. All other product or service names are the property of their respective holders. Altera products are protected under numerous U.S. and foreign patents and pending applications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the ap-

changes to any products and services at any time without nonce. After assumes to responsibility or hability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

## Contents

# About This User Guide vii How to Contact Altera vii Typographic Conventions viii

#### **Chapter 1. Introduction**

| Gigabit Transceiver Block Highlights | . 1–1 |

|--------------------------------------|-------|

| Transceiver Block Architecture       |       |

| Analog Section Overview              | . 1–2 |

| Digital Overview                     |       |

| Modes of Operation                   | . 1–5 |

| Basic Mode                           | . 1–5 |

| SONET Mode                           | . 1–6 |

| XAUI Mode                            | . 1–7 |

| GigE Mode                            | . 1–8 |

| Loopback                             | . 1–9 |

| Built-In Self Test                   | . 1–9 |

#### **Chapter 2. Stratix GX Analog Description**

| Introduction                                |     |

|---------------------------------------------|-----|

| Transmitter Analog                          |     |

| Transmitter Buffer                          |     |

| Transmitter PLL                             |     |

| Serializer (Parallel-to-Serial Converter)   |     |

| Receiver Analog                             | 2–9 |

| Receiver Input Buffer                       |     |

| Receiver PLL                                |     |

| Clock Recovery Unit                         |     |

| Deserializer (Serial-to-Parallel Converter) |     |

| MegaWizard Analog Features                  |     |

| MegaWizard Analog Feature Considerations    |     |

|                                             |     |

#### **Chapter 3. Basic Mode**

| Introduction                               |      |

|--------------------------------------------|------|

| Basic Mode Receiver Architecture           | 3–2  |

| Word Aligner                               | 3–2  |

| 8B/10B Decoder                             |      |

| Byte Deserializer                          | 3–13 |

| Receiver Phase Compensation FIFO Buffer    | 3–15 |

| Basic Mode Transmitter Architecture        |      |

| Transmitter Phase Compensation FIFO Buffer | 3–16 |

| Byte Serializer                                      | 3–17 |

|------------------------------------------------------|------|

| 8B/10B Encoder                                       | 3–17 |

| Basic Mode Clocking                                  | 3–20 |

| Basic Mode Channel Clocking                          |      |

| Basic Mode Inter-Transceiver Block Clocking          |      |

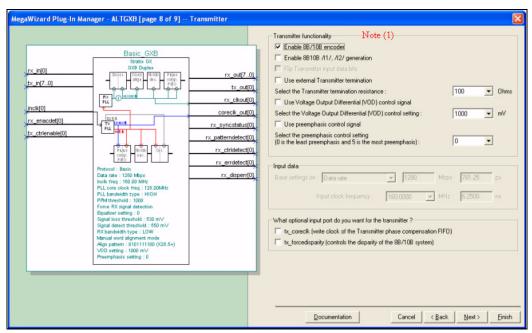

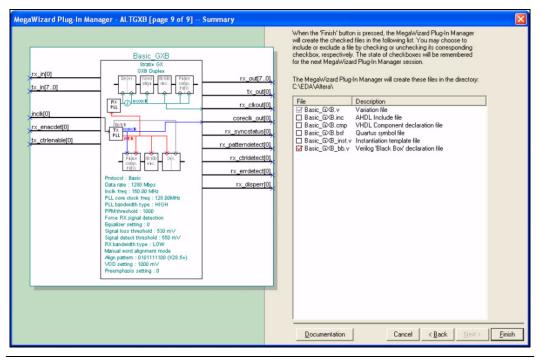

| Basic Mode MegaWizard Plug-In                        |      |

| Basic Mode MegaWizard Plug-In Manager Considerations |      |

| Basic Mode altgxb MegaWizard Options                 |      |

|                                                      |      |

#### **Chapter 4. SONET Mode**

| Ι | ntroduction                                 | 4–1    |

|---|---------------------------------------------|--------|

| 5 | ONET Mode Receiver Architecture             | 4–2    |

|   | Word Aligner                                | 4–2    |

|   | Byte Deserializer                           | 4–8    |

|   | Receiver Phase Compensation FIFO Module     |        |

| 5 | ONET Mode Transmitter Architecture          |        |

|   | Transmitter Phase Compensation FIFO Buffer  | . 4–11 |

|   | Byte Serializer                             | . 4–12 |

| 5 | SONET Mode Clocking                         | . 4–12 |

|   | SONET Mode Channel Clocking                 | . 4–12 |

|   | SONET Mode Inter-Transceiver Block Clocking |        |

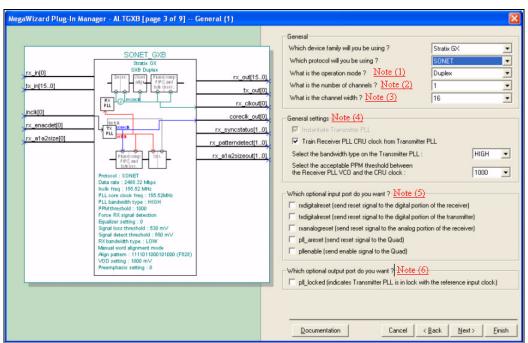

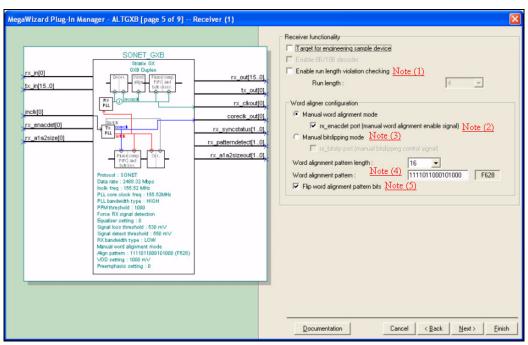

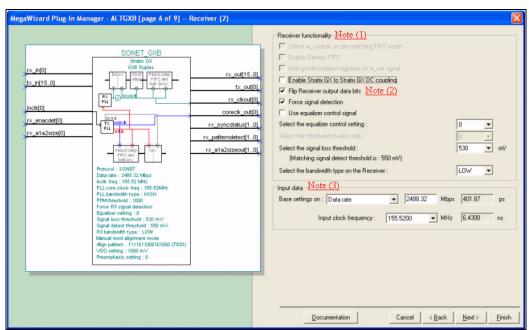

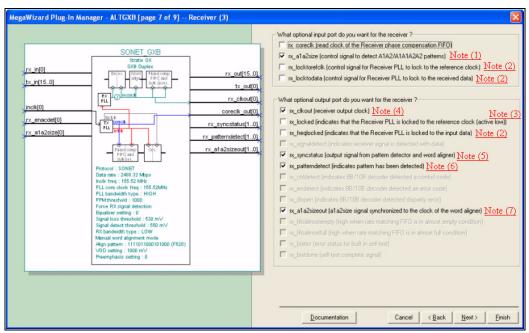

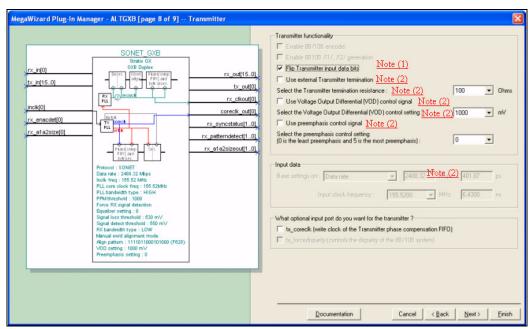

| 9 | ONET Mode MegaWizard Plug-In Manager        | . 4–23 |

|   | SONET Mode MegaWizard Considerations        |        |

|   | SONET Mode altgxb MegaWizard Options        |        |

|   |                                             |        |

#### Chapter 5. XAUI Mode

| Introduction                               | 5–1  |

|--------------------------------------------|------|

| XAUI Mode Receiver Architecture            | 5–5  |

| Word Aligner                               | 5–6  |

| Channel Äligner                            |      |

| Rate Matcher                               |      |

| 8B/10B Decoder                             | 5–11 |

| PCS - XGMII Code Conversion                |      |

| Byte Deserializer                          | 5–15 |

| Receiver Phase Compensation FIFO Module    |      |

| XAUI Mode Transmitter Architecture         | 5–18 |

| Transmitter Phase Compensation FIFO Module | 5–18 |

| Byte Serializer                            | 5–19 |

| XGMII Character to PCS Code-Group Mapping  |      |

| 8B/10B Encoder                             | 5–21 |

| XAUI Mode Clocking                         | 5–24 |

| XAUI Mode Channel Clocking                 |      |

| XAUI Inter-Transceiver Block Clocking      |      |

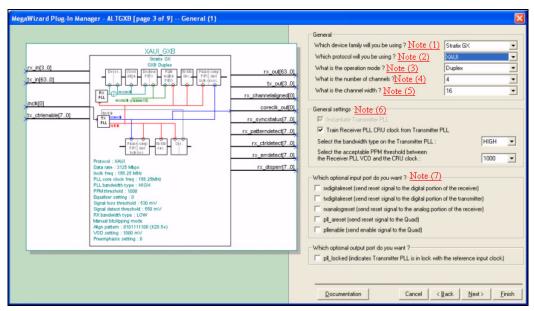

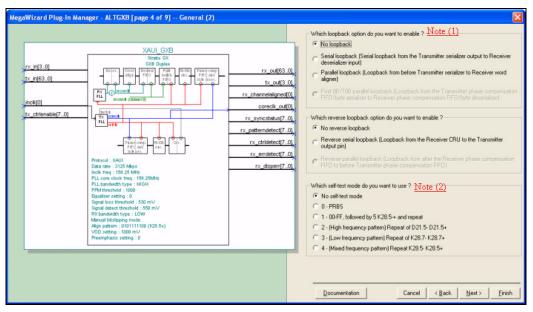

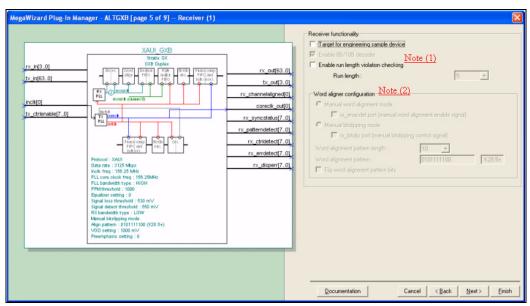

| XAUI Mode MegaWizard Plug-In Manager       |      |

| XAUI Mode MegaWizard Considerations        |      |

| XAUI Mode altgxb MegaWizard Options        |      |

#### Chapter 6. GigE Mode

| Introduction                                        |      |

|-----------------------------------------------------|------|

| Word Aligner                                        |      |

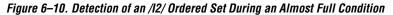

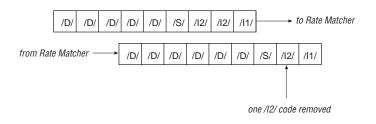

| Rate Matcher                                        |      |

| 8B/10B Decoder                                      |      |

| Receiver Phase Compensation FIFO Buffer             |      |

| GigE Mode Transmitter Architecture                  |      |

| Transmitter Phase Compensation FIFO Buffer          |      |

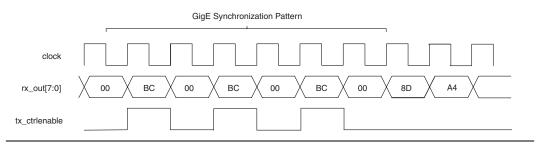

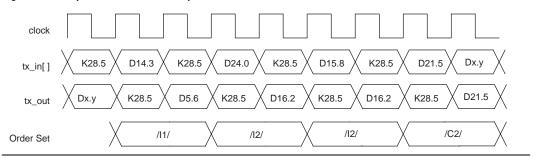

| GigE Transmitter Synchronization                    |      |

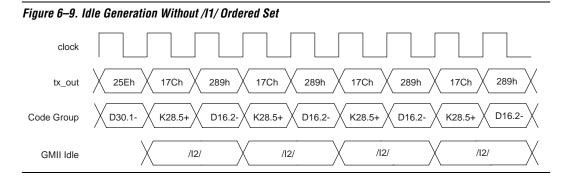

| Idle Generation                                     |      |

| 8B/10B Encoder                                      |      |

| GigE Mode Clocking                                  |      |

| GigE Mode Channel Clocking                          |      |

| GigE Mode Inter-Transceiver Clocking                |      |

| GigE Mode MegaWizard Considerations                 |      |

| GigE Mode altgxb MegaWizard Options                 | 6–31 |

| Design Example                                      |      |

| Design Description                                  |      |

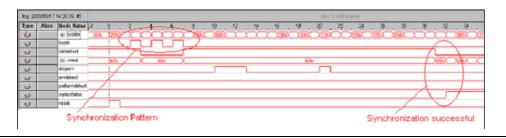

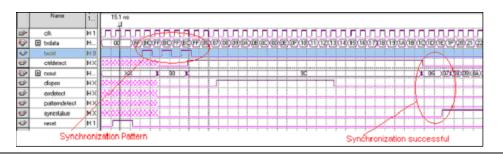

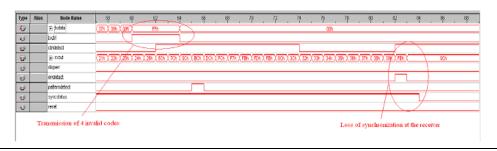

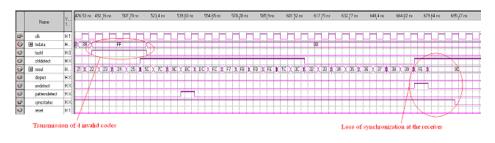

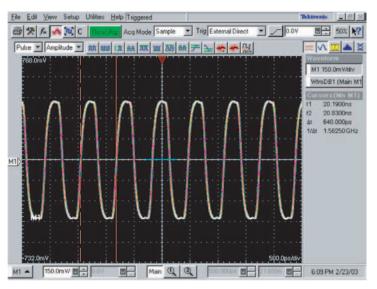

| Simulation Waveform & Hardware Verification Results | 6–44 |

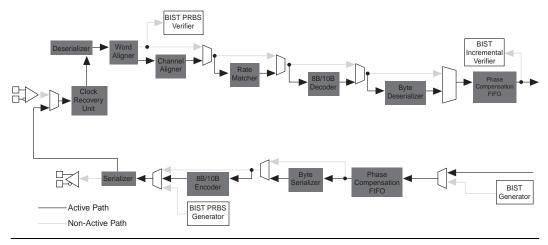

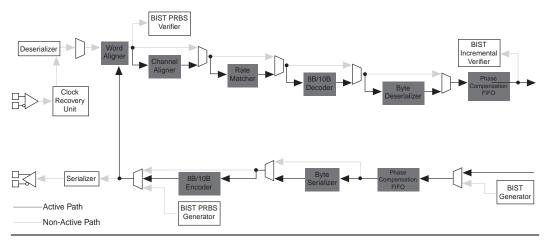

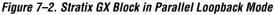

#### **Chapter 7. Loopback Modes**

| Introduction            | '–1 |

|-------------------------|-----|

| Serial Loopback         | 7–1 |

| Parallel Loopback       | 7–2 |

| Reverse Serial Loopback | 7_3 |

|                         |     |

#### Chapter 8. Stratix GX Built-In Self Test (BIST)

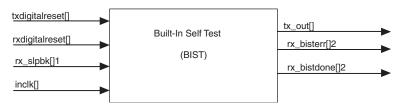

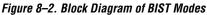

| Introduction                                               | 8–1  |

|------------------------------------------------------------|------|

| Pattern Generator                                          | 8–2  |

| PRBS Mode Generator                                        |      |

| Incremental Mode Generator                                 | 8–3  |

| High-Frequency Mode Generator                              | 8–3  |

| Low-Frequency Mode Generator                               | 8–4  |

| Mix-Frequency Mode Generator                               |      |

| Pattern Verifier                                           |      |

| PRBS Mode Verifier                                         | 8–5  |

| Incremental Mode Verifier                                  | 8–6  |

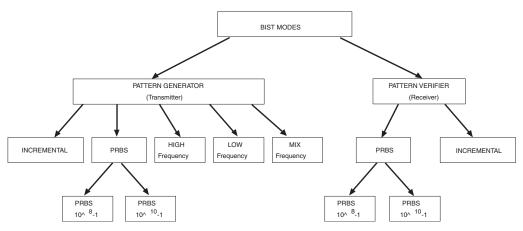

| Design Examples                                            | 8–7  |

| Design 1: PRBS BIST Generator & Verification Design        | 8–7  |

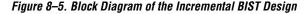

| Design 2: Incremental BIST Generator & Verification Design |      |

| Design 3: High-Frequency Transmitter Generator Design      | 8–16 |

| Design 4: Low-Frequency Transmitter Generator Design       |      |

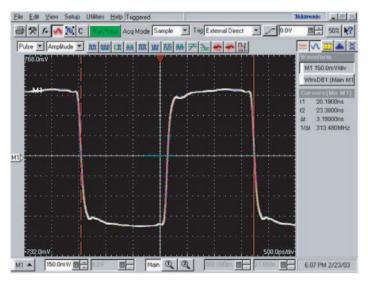

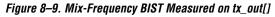

| Design 5: Mix-Frequency Transmitter Generator Design       | 8–20 |

|                                                            |      |

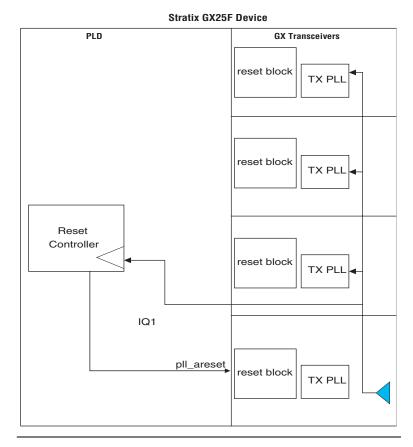

## Chapter 9. Reset Control & Power Down

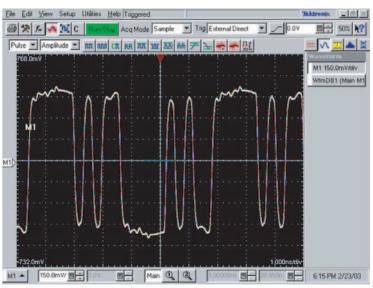

| Introduction                 |  |

|------------------------------|--|

| Power On Reset (POR)         |  |

| USER Reset & Enable Signals  |  |

| Recommended Resets           |  |

| Receiver & Transmitter Reset |  |

| Receiver Reset               |  |

| Transmitter Reset            |  |

| Power Down                   |  |

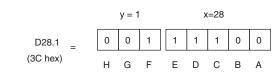

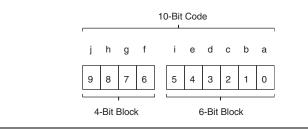

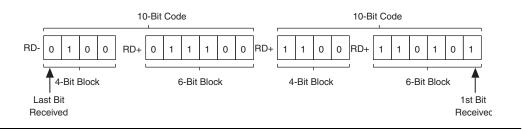

#### Appendix A. Data & Control Codes

| 3/10B Code            | A-1 |

|-----------------------|-----|

| Code Notation         | A-1 |

| Disparity Calculation | A-1 |

| Supported Codes       | A-3 |

#### Appendix B. Ports & Parameters

| Input Ports            | B–1 |

|------------------------|-----|

| Output Ports           | B–5 |

| Parameter Descriptions | B-9 |

#### Appendix C. REFCLKB Pin Constraints

| Known Issues                 | C-' | 1 |

|------------------------------|-----|---|

| Quartus II Software Messages | C   | 3 |

| Recommendations              | C-! | 5 |

## **About This User Guide**

## How to Contact Altera

For the most up-to-date information about Altera<sup>®</sup> products, go to the Altera world-wide web site at www.altera.com. For technical support on this product, go to www.altera.com/mysupport. For additional information about Altera products, consult the sources shown below.

| Information Type               | USA & Canada                                                   | All Other Locations                                                    |

|--------------------------------|----------------------------------------------------------------|------------------------------------------------------------------------|

| Technical support              | www.altera.com/mysupport/                                      | www.altera.com/mysupport/                                              |

|                                | (800) 800-EPLD (3753)<br>(7:00 a.m. to 5:00 p.m. Pacific Time) | +1 408-544-8767<br>7:00 a.m. to 5:00 p.m. (GMT -8:00)<br>Pacific Time  |

| Product literature             | www.altera.com                                                 | www.altera.com                                                         |

| Altera literature services     | literature@altera.com                                          | literature@altera.com                                                  |

| Non-technical customer service | (800) 767-3753                                                 | + 1 408-544-7000<br>7:00 a.m. to 5:00 p.m. (GMT -8:00)<br>Pacific Time |

| FTP site                       | ftp.altera.com                                                 | ftp.altera.com                                                         |

## Typographic Conventions

This document uses the typographic conventions shown below.

| Visual Cue                                  | Meaning                                                                                                                                                                                                                                                                                                                 |

|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bold Type with Initial<br>Capital Letters   | Command names, dialog box titles, checkbox options, and dialog box options are shown in bold, initial capital letters. Example: <b>Save As</b> dialog box.                                                                                                                                                              |

| bold type                                   | External timing parameters, directory names, project names, disk drive names, filenames, filename extensions, and software utility names are shown in bold type. Examples: <b>f</b> <sub>MAX</sub> , <b>\qdesigns</b> directory, <b>d:</b> drive, <b>chiptrip.gdf</b> file.                                             |

| Italic Type with Initial Capital<br>Letters | Document titles are shown in italic type with initial capital letters. Example: AN 75: High-Speed Board Design.                                                                                                                                                                                                         |

| Italic type                                 | Internal timing parameters and variables are shown in italic type.<br>Examples: $t_{P A}$ , $n + 1$ .                                                                                                                                                                                                                   |

|                                             | Variable names are enclosed in angle brackets (< >) and shown in italic type.<br>Example: <i><file name="">, <project name="">.<b>pof</b> file.</project></file></i>                                                                                                                                                    |

| Initial Capital Letters                     | Keyboard keys and menu names are shown with initial capital letters. Examples: Delete key, the Options menu.                                                                                                                                                                                                            |

| "Subheading Title"                          | References to sections of a document and titles of on-line help topics are shown in quotation marks. Example: "Typographic Conventions."                                                                                                                                                                                |

| Courier type                                | Signal and port names are shown in lowercase Courier type. Examples: data1, tdi, input. Active-low signals are denoted by suffix n, e.g., resetn.                                                                                                                                                                       |

|                                             | Anything that must be typed exactly as it appears is shown in Courier type. For example: c:\qdesigns\tutorial\chiptrip.gdf. Also, sections of an actual file, such as a Report File, references to parts of files (e.g., the AHDL keyword SUBDESIGN), as well as logic function names (e.g., TRI) are shown in Courier. |

| 1., 2., 3., and<br>a., b., c., etc.         | Numbered steps are used in a list of items when the sequence of the items is important, such as the steps listed in a procedure.                                                                                                                                                                                        |

| ••                                          | Bullets are used in a list of items when the sequence of the items is not important.                                                                                                                                                                                                                                    |

| $\checkmark$                                | The checkmark indicates a procedure that consists of one step only.                                                                                                                                                                                                                                                     |

| IP                                          | The hand points to information that requires special attention.                                                                                                                                                                                                                                                         |

| 4                                           | The angled arrow indicates you should press the Enter key.                                                                                                                                                                                                                                                              |

| ••••                                        | The feet direct you to more information on a particular topic.                                                                                                                                                                                                                                                          |

## 1. Introduction

| Introduction                               | Stratix <sup>®</sup> GX devices combine highly advanced 3.1875-gigabit-per-second (Gbps) four-channel gigabit transceiver blocks with one of the industry's most advanced FPGA architectures. Stratix GX devices are manufactured on a 1.5-V, 0.13-µm, all-layer copper CMOS process technology with 1.5-V PCML I/O standard support.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                            | Historically, designers have used high-speed transceivers in strictly<br>structured, line-side applications. Now, with the new gigabit transceiver<br>blocks embedded in FPGAs, you can use transceivers in a host of new<br>systems that require flexibility, increased time-to-market, high<br>performance, and top-of-the-line features.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

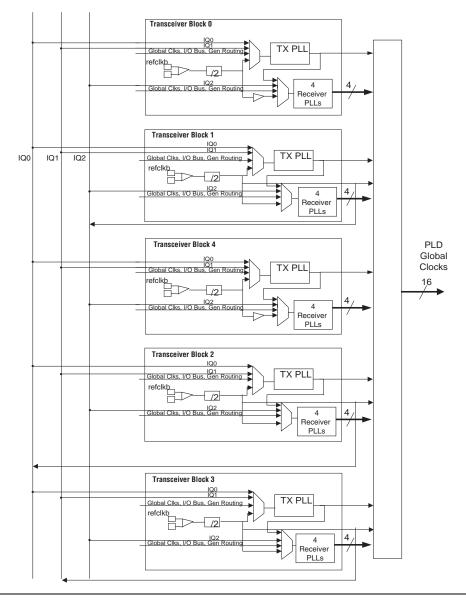

| Gigabit<br>Transceiver<br>Block Highlights | <ul> <li>Stratix GX devices are organized into four-channel blocks with four</li> <li>3.1875 Gbps full-duplex channels per block and up to 20 channels (in five blocks) per device. Each self-contained Stratix GX gigabit transceiver block supports a variety of embedded functions and does the following:</li> <li>Supports frequencies from 500 megabits per second (Mbps) to 3.1875 Gbps</li> <li>Integrates serializer/deserializer (SERDES), clock data recovery (CDR), word aligner, channel aligner, rate matcher, 8B/10B encoder/decoder, byte serializer/deserializer, and phase compensation first-in first-out (FIFO) modules</li> <li>Supports flexible reference clock generation capabilities, including a dedicated transmitter phase-locked loop (PLL) and four receiver PLLs per gigabit transceiver block</li> <li>Supports programmable pre-emphasis, equalization, and programmable V<sub>OD</sub> settings in I/O buffers, and dynamic reprogrammability for each of these features</li> <li>Implements XAUI physical media attachment (PMA) and physical coding sublayer (PCS) functionality for 10GBASE-X systems</li> <li>Provides built-in Gigabit Ethernet (GigE) physical coding sublayer functionality</li> <li>Provides individual transmitter and receiver power-down capability for reduced power consumption during non-operation</li> <li>Includes built-in self test (BIST) capability, including embedded Pseudo Random Binary Sequence (PRBS) pattern generation and verification</li> </ul> |

Includes three independent loopback paths for system verification

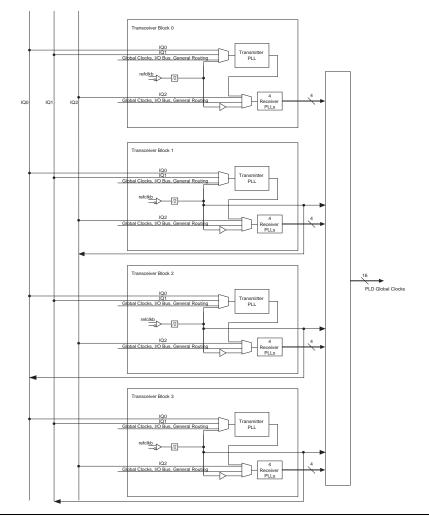

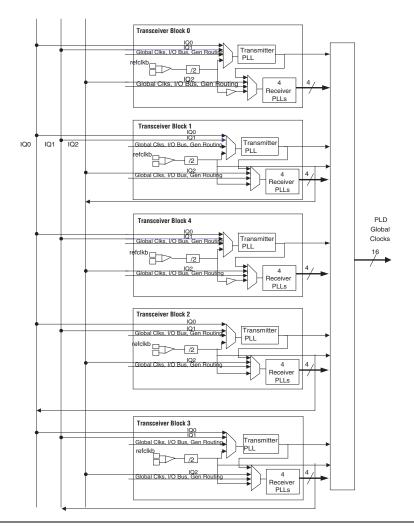

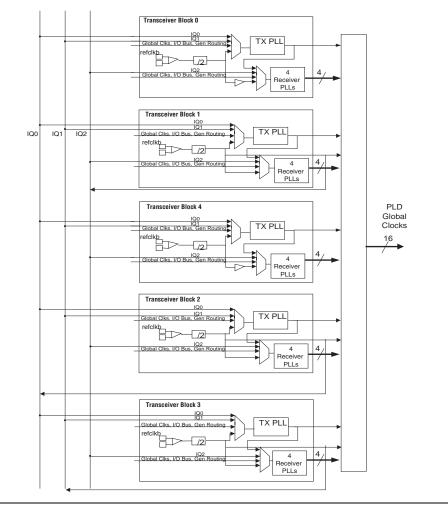

### Transceiver Block Architecture

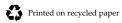

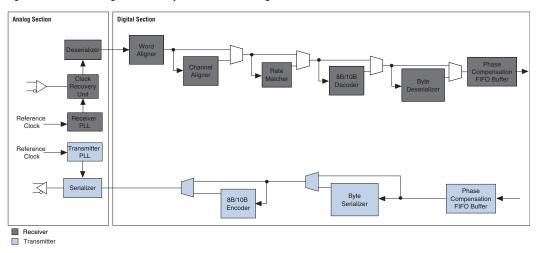

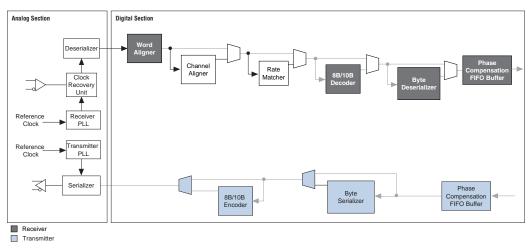

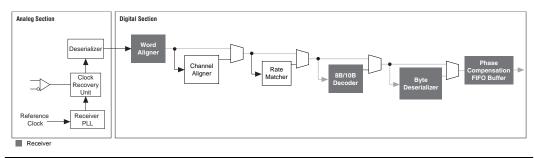

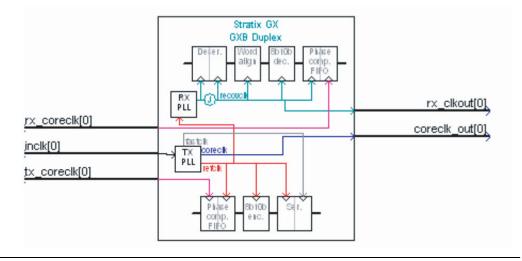

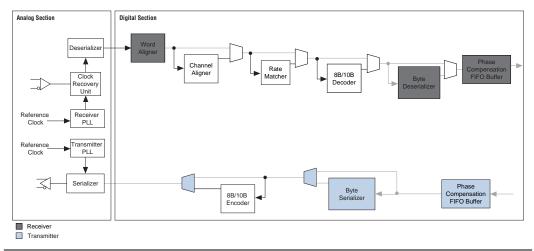

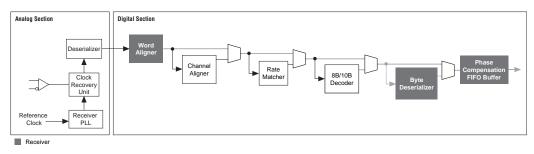

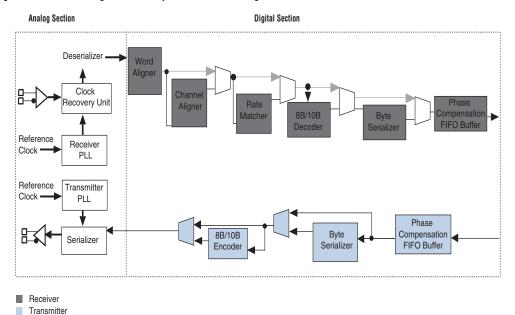

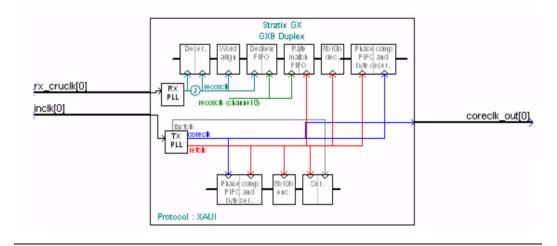

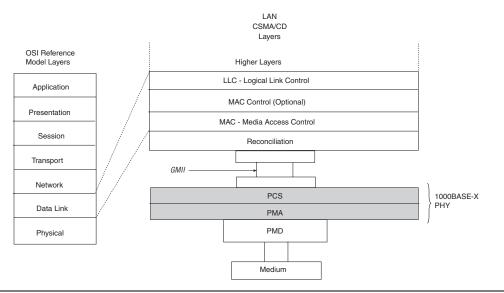

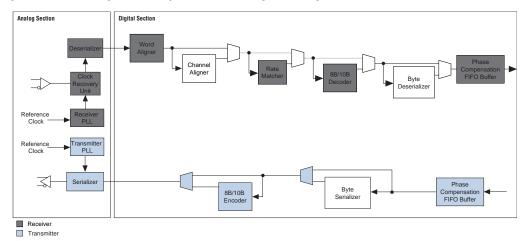

Figure 1–1 shows a block diagram of the gigabit transceiver block (GXB). You can bypass various modules if desired. Refer to "Modes of Operation" on page 1–5 for a description of the supported features in each mode. You can divide the transceiver block into an analog section and a digital section, as shown in Figure 1–1.

Figure 1–1. Block Diagram of a Stratix GX Gigabit Transceiver Block

#### **Analog Section Overview**

This section describes the various components within the analog section of the transceiver block.

#### Transmitter Differential I/O Buffers

The gigabit transmitter block differential I/O buffers support the 1.5-V PCML I/O standard, and contain features that improve system signal integrity. These features include programmable pre-emphasis, which helps compensate for high frequency losses, and a variety of programmable V<sub>OD</sub> settings that support noise margin tuning.

#### Receiver Differential I/O Buffers

The gigabit transceiver block differential I/O buffers support the 1.5-V PCML I/O standard, and contain a variety of features that improve system signal integrity. Programmable equalization capabilities are used to compensate for signal degradation across transmission mediums.

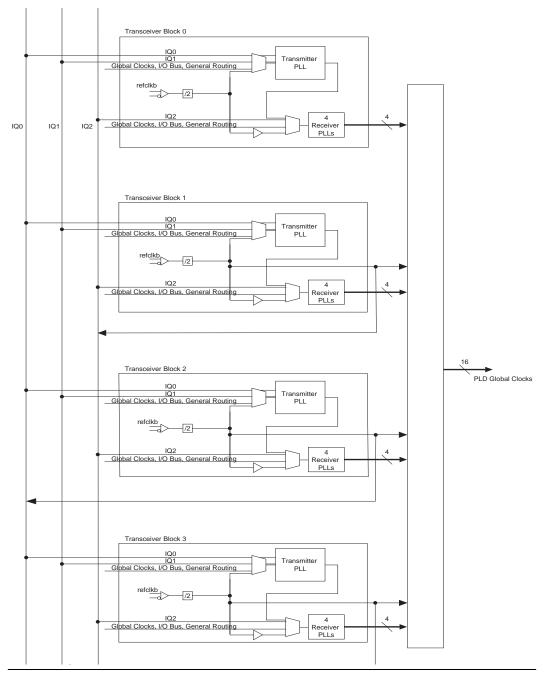

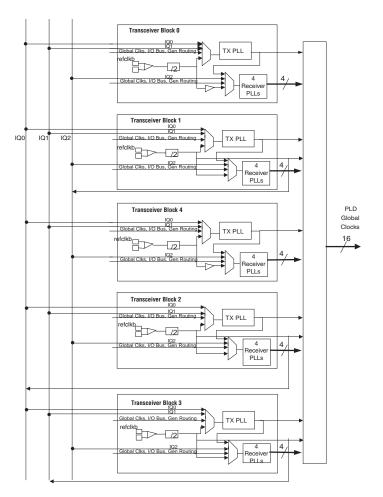

#### Transmitter & Receiver PLLs

Each gigabit transceiver block contains one dedicated transmitter PLL and four dedicated receiver PLLs. These PLLs provide clocking flexibility and support a range of incoming data streams. For data transmission and recovery, these PLLs generate the required clock frequencies based upon the synthesis of an input reference clock. Each transmitter PLL supports multiplication factors of 2, 4, 5, 8, 10, 16, or 20. Either external reference clocks or a variety of clock sources within the Stratix GX device drive the PLLs.

#### Clock Recovery Unit

The gigabit transceiver block clock recovery unit (CRU) performs analog Clock Data Recovery (CDR). The CRU uses an external reference clock to extract a recovered clock that is frequency and phase aligned with the incoming data, thereby eliminating any clock-to-data skew. This recovered clock then clocks the data through the rest of the gigabit transceiver block.

#### Serializer Deserializer (SERDES)

The transmitter serializer converts the incoming lower speed parallel signal to a high-speed serial signal on the transmit side. The SERDES supports a variety of conversion factors, ensuring implementation flexibility. For example, the SERDES supports 10- and 20-bit serialization factors, typically required for 8B/10B encoded data, as well as 8- and 16-bit factors.

The receiver deserializer converts the incoming data stream from a high-speed serial signal to a lower-speed parallel signal that can be processed in the FPGA logic array on the receive side. The SERDES supports a variety of conversion factors, ensuring implementation flexibility. For example, the SERDES supports both 10-bit and 8-bit serialization and deserialization factors.

#### **Digital Overview**

This section describes the various components in the digital section of the transceiver block.

#### Transmitter & Receiver Phase Compensation FIFO Buffer

The transmitter and receiver data path has a dedicated phase compensation FIFO buffer that decouples phase variations between the FPGA and transceiver clock domains. These FIFO buffers ensure a consistent, reliable interface to the logic array and simplify system design and timing analysis.

#### Byte Serializer/Deserializer

The byte serializer converts a 16- or 20-bit data bus into two 8- or 10-bit data buses, respectively, at double the data rate. The byte serializer converts an 8- or 10-bit data bus into 16- or 20-bit data buses, allowing maximum throughput of the transceiver without burdening the FPGA logic array.

The byte deserializer converts an 8- or 10-bit data bus into 16- or 20-bit data buses, allowing maximum throughput of the transceiver without burdening the FPGA logic array.

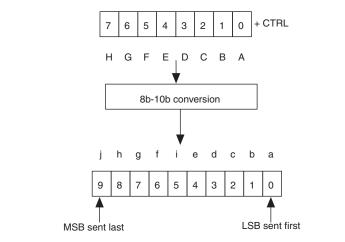

#### 8B/10B Encoder/Decoder

8B/10B encoding/decoding is the backbone of many transceiver protocols, and it is often used in proprietary implementations. The gigabit transceiver block has dedicated circuitry to perform 8B/10B encoding in the transmitter and decoding in the receiver. This coding technique ensures sufficient data transitions and a DC balanced stream in the data signal for successful data recovery at the receiver.

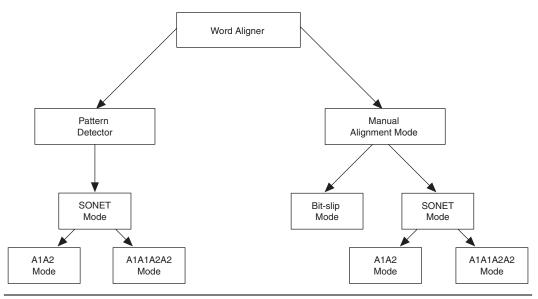

#### Word Aligner

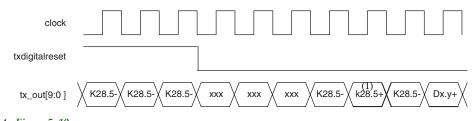

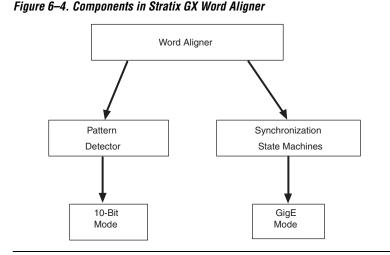

The word aligner module contains a fully programmable pattern detector to identify specific patterns within the incoming data stream. The pattern detector includes recognition support /K28.5/ comma characters for 8B/10B encoded data and A1 or A2 frame alignment patterns for scrambled signals. Additionally, you can specify a custom alignment pattern in lieu of the /K28.5/ comma.

The word aligner in the gigabit transceiver block also creates words from the incoming serial data stream by realigning the data based on identified byte boundaries. The realignment function uses a barrel shifter and works with the pattern detector. Additionally, the word aligner has a manual data realignment mode that lets you control the data realignment in user mode without consistent alignment characters.

#### Channel Aligner

An embedded channel aligner aligns byte boundaries across multiple channels and synchronizes the data entering the logic array from the gigabit transceiver block's four channels. The Stratix GX channel aligner is optimized for a 10-Gigabit Ethernet XAUI 4-channel implementation. The channel aligner includes the control circuitry and channel alignment character detection defined by the XAUI protocol. The channel aligner is only available in XAUI mode.

#### Rate Matcher

In multi-crystal environments, the clock frequencies of the transmitting and receiving devices do not match. This mismatch can cause the data to transmit at a rate slightly faster or slower than the receiving device can interpret. The Stratix GX rate matcher resolves the frequency differences between the recovered clock and the FPGA logic array clock by inserting or deleting removable characters from the data stream, as defined by the transmission protocol, without compromising transmitted data. If the functional mode is XAUI, the rate matcher is based on the 10-Gigabit Ethernet protocol. If the functional mode is GigE, the rate matcher is based on the Gigabit Ethernet protocol.

## Modes of Operation

You can bypass various modules of the gigabit transceiver block based on the configured mode of operation. Stratix GX transceivers currently support basic mode, SONET mode, and XAUI mode. This section provides an overview of each supported mode of operation.

#### **Basic Mode**

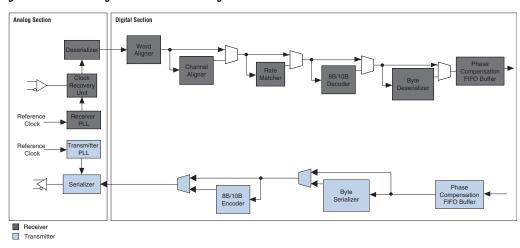

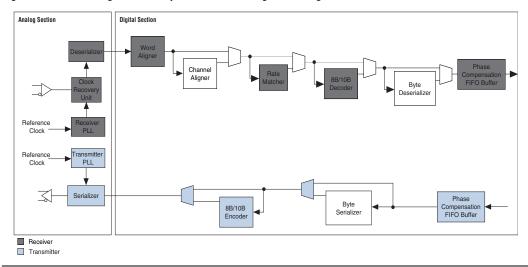

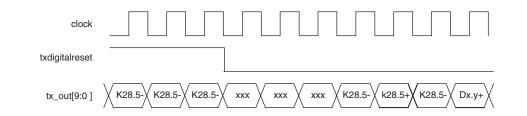

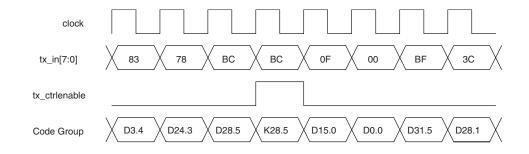

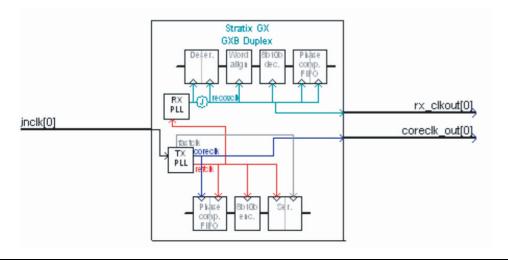

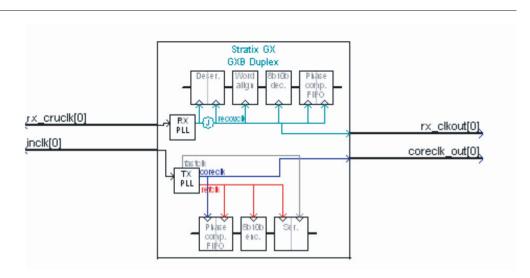

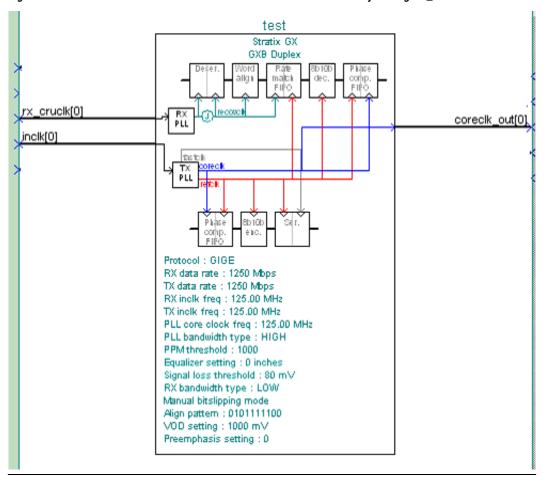

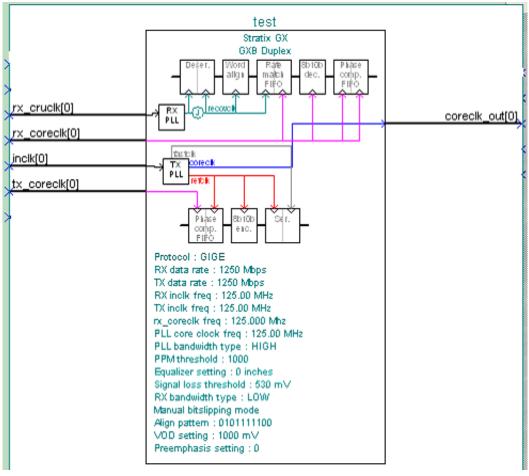

Basic mode enables a subset of the transceiver blocks so you can perform customizable configuration. Channel aligner and the rate matcher features are not available in this mode. Refer to the *Basic Mode* chapter for more details on the configurability of this mode. Figure 1–2 shows a block diagram of a duplex channel configured in basic mode.

Figure 1–2. Block Diagram of a Duplex Channel Configured in Basic Mode

#### **SONET Mode**

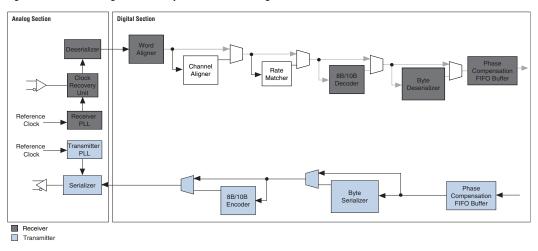

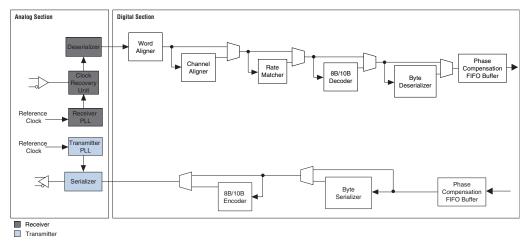

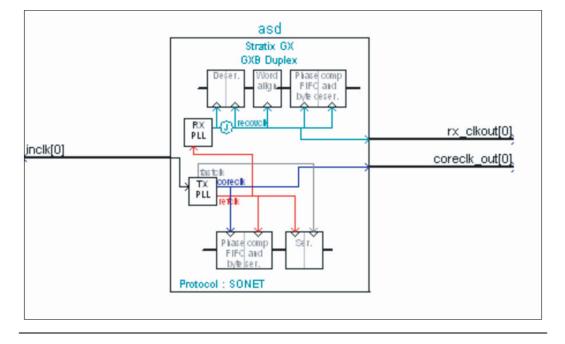

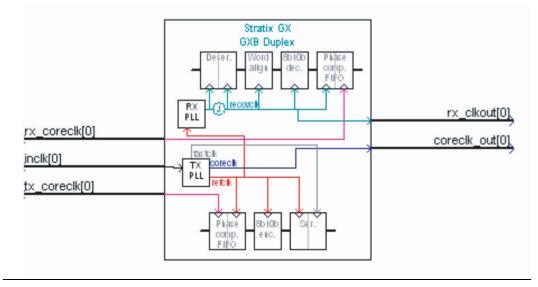

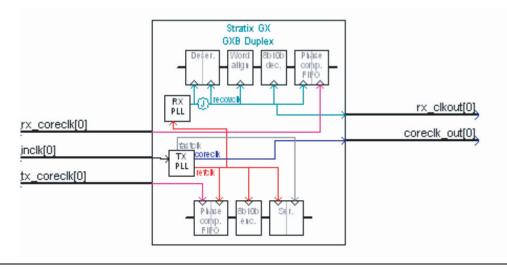

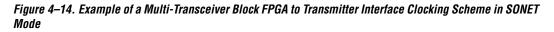

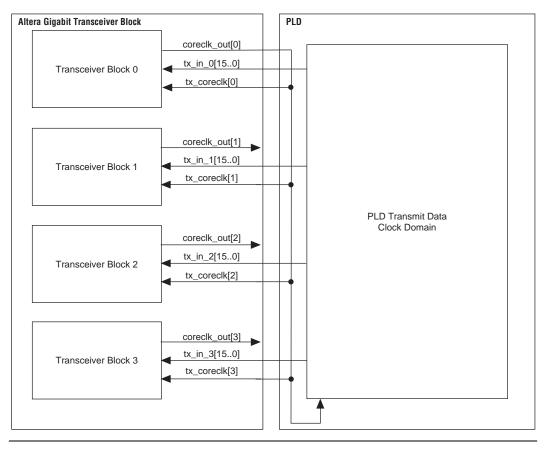

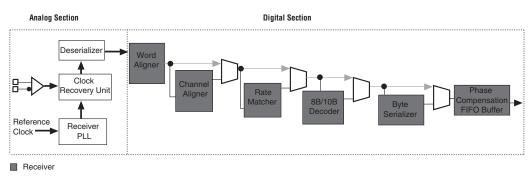

SONET mode lets you to select a subset of the transceiver blocks to perform SONET-like configuration. SONET-like implies that the data width can either be 8 or 16 bits and that the 8B/10B encoder/decoder, channel aligner, and the rate matcher features are not available. Refer to the *SONET Mode* chapter for more details on the configurability of this mode. Figure 1–3 shows a block diagram of a duplex channel configured in SONET mode.

Figure 1–3. Block Diagram of a Duplex Channel Configured in SONET Mode

#### **XAUI Mode**

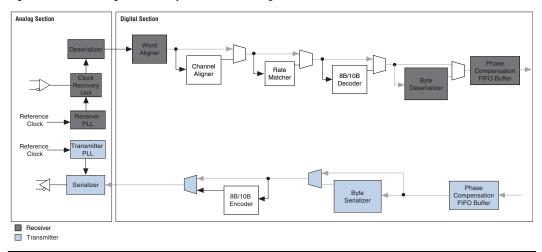

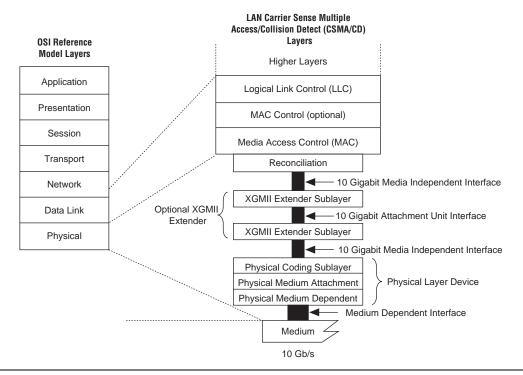

Stratix GX transceivers contain embedded macros dedicated to supporting the XAUI protocol, specified in clause 47 of the IEEE 802.3ae specification. These macros includes synchronization, channel deskew, rate matching, XGXS to XGMII, and XGMII to XGXS code-group conversion. Refer to the *XAUI Mode* chapter for more details on the configurability of this mode. Figure 1–4 shows a block diagram of a duplex channel configured in XAUI mode.

Figure 1–4. Block Diagram of a Duplex Channel Configured in XAUI Mode

#### **GigE Mode**

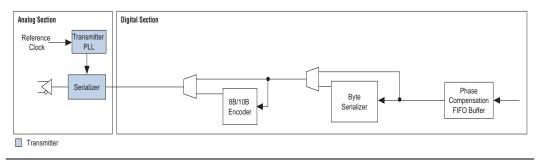

Stratix GX devices in GigE mode can use the 8B/10B encoder/decoder, rate matcher, synchronizer, and byte serializer/deserializer built-in hard macros. Refer to the GigE Mode chapter for more information about this mode. The rate matcher and word aligner each have a dedicated state machine governing their functions. These state machines are active only in GigE mode. Figure 1–5 shows a block diagram of a duplex channel configured in GigE mode.

Figure 1–5. Block Diagram of a Duplex Channel Configured in GigE Mode

#### Loopback

There are three different loopback modes to use in the gigabit transceiver block to allow for a complete method of in-system verification. The loopback modes are versatile and robust enough to accommodate all protocols and let you to choose whether to retime the data.

#### **Built-In Self Test**

The gigabit transceiver block contains several features that simplify design verification. An embedded PRBS pattern generator provides a bitstream pattern that you can use to test the device and board connections. The PRBS pattern generator works with a PRBS receiver to implement a full self-test path. Additionally, serial and parallel loopback paths let you test the FPGA logic without monitoring external signals. The reverse loopback path enables external system testing with minimal device interaction.

## 2. Stratix GX Analog Description

### Introduction

This chapter describes how to serialize the parallel data for transmission and convert received data into parallel data. Data transmission and reception is performed by pseudo current mode logic (PCML) buffers. These transceiver buffers support programmable pre-emphasis, equalization, and programmable V<sub>OD</sub> settings in I/O buffers.

The programmable pre-emphasis setting is available on transmit buffers to maximize the eye opening on the far-end receiver by boosting the high-frequency component of the data signal. Similarly, programmable equalization is available for receive buffers to reduce the high-frequency losses and inter-symbol interference. These features are useful in lossy transmission lines. Transceivers also support flexible reference clock generation capabilities, including a dedicated transmitter phase-locked loop (PLL) and four receiver PLLs per transceiver block.

The clock recovery unit (CRU) is the main part of each receive analog section; it recovers the clock from the serial data stream (see Figure 2–1).

You can set the CRU to automatically or manually alter the receiver PLL phase and frequency to match the bit transition on the incoming data stream. This is to eliminate any clock-to-data skew or to keep the receiver PLL locked to the reference clock (lock-to-data or lock-to-reference mode).

During the clock recovery phase, the receiver PLL initially locks to the reference clock and then attempts to lock on to the incoming data by first recovering the clock from the incoming serial data.

## Transmitter Analog

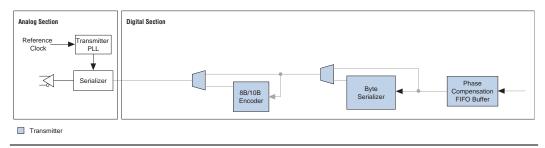

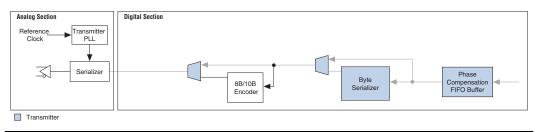

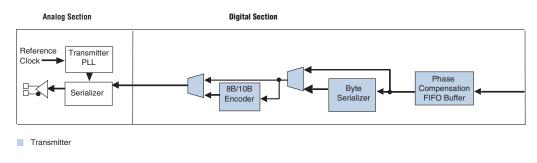

This section describes the transmitter buffer, the transmitter PLL, and the serializer. Figure 2–2 shows the transmitter analog components.

Figure 2–2. Transmitter Analog Components

#### **Transmitter Buffer**

The Stratix<sup>®</sup> GX transceiver buffers support the 1.5-V PCML standard at speeds up to 3.1875 gigabits per second (Gbps) and are capable of driving 40 inches of FR4 trace across two connectors. In addition, the buffer contains programmable output voltage, programmable pre-emphasis circuitry, and internal termination circuitry.

#### Programmable Voltage Output Differential (V<sub>OD</sub>)

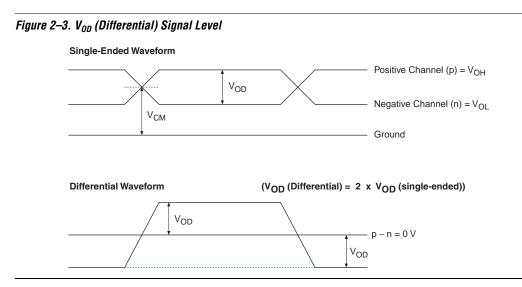

Stratix GX transceivers let you customize the differential output voltage  $(V_{OD})$  to handle different length, backplane, and receiver requirements (see Figure 2–3). You can select the  $V_{OD}$  (differential) from a range of 400 to 1,600 mV, as shown in Table 2–1.

Table 2–1 shows the differential output voltage ( $V_{OD}$ ) setting per current level for each of the on-chip transmitter programmable termination values.

| Table 2–1. Programmable V <sub>0D</sub> (Differential) |                   |            |

|--------------------------------------------------------|-------------------|------------|

| 100 Ω (mV)                                             | <b>120</b> Ω (mV) | 150 Ω (mV) |

| 400                                                    | 480               | 600        |

| 800                                                    | 960               | 1,200      |

| 1,000                                                  | 1,200             | 1,500      |

| 1,200                                                  | 1,440             |            |

| 1,400                                                  |                   |            |

| 1,600                                                  |                   |            |

You can set the differential  $V_{OD}$  values statically during configuration or dynamically adjust them in user mode. You select the static  $V_{OD}$  value through a list in the altgxb MegaWizard® Plug-In Manager, which sets the appropriate  $V_{OD}$  setting in the configuration file. The disadvantage of the static mode setting is that the  $V_{OD}$  is set on a per transceiver block basis and cannot be changed unless you regenerate another programming file.

Alternatively, if you enable dynamic adjustment in the altgxb MegaWizard Plug-In, you can dynamically configure the  $V_{OD}$  setting by the device during user mode. This configuration is done by asserting encoded values on the tx\_vodctrl bus, which is instantiated in the altgxb module when you select the dynamic adjustment option. This option lets you make quick performance evaluations of the various settings without having to recompile and regenerate multiple configuration files. Another advantage of this option is that it allows the  $V_{OD}$  of each channel to be configured independently. Refer to the section "MegaWizard Analog Features" on page 2–20 for further details.

#### Programmable Pre-Emphasis

The programmable pre-emphasis module in each transmit buffer boosts the high frequencies in the transmit data signal, which may be attenuated in the transmission media. This maximizes the data eye opening at the far-end receiver. Pre-emphasis is particularly useful in lossy transmission mediums.

The transfer function of a transmission line can be represented in the frequency domain as a low-pass filter. Any frequency components below the –3 dB frequency pass through with minimal losses. Frequency components that are greater than the –3-dB frequency are attenuated. This variation in frequency response yields data-dependant jitter and other ISI effects. By applying pre-emphasis, the high frequency components are boosted, or in other words, pre-emphasized. This pre-emphasis equalizes the frequency response as seen at the receiver so that the delta between the low-frequency and high-frequency components is reduced, which in return minimizes the ISI effects from the transmission medium.

In Stratix GX transceivers, the programmable pre-emphasis settings can have one of six values (0 to 5). You should experiment with the pre-emphasis values to determine the optimal setting based on your system variables. As with the  $V_{OD}$  settings, you can set the pre-emphasis settings statically during configuration or adjust them dynamically in user mode. You can set the static pre-emphasis value through a drop-down menu in the altgxb MegaWizard Plug-In, which sets the appropriate pre-emphasis setting in the configuration file. The disadvantage of the static mode setting is that the pre-emphasis is set on a per-transceiver-block basis and cannot be changed without regenerating another programming file.

On the other hand, if you select dynamic adjustment in the altgxb MegaWizard Plug-In, the pre-emphasis setting can be configured dynamically by the device during user mode. This configuration is done by asserting encoded values on the tx\_preemphasisctrl bus, which is instantiated in the altgxb module when you select the dynamic adjustment option. This option lets you make quick performance evaluations of the various settings without having to recompile and regenerate multiple configuration files. Another advantage of this option is that it allows the pre-emphasis of each channel to be configured independently. For further details, refer to "MegaWizard Analog Features" on page 2–20.

Avoid pre-emphasis and V<sub>OD</sub> settings that yield a value greater than 1,600 mV. Settings beyond this value do not damage the buffer, but they prevent accurate device operation. Verify that the combination of V<sub>OD</sub> and pre-emphasis settings do not exceed the 1,600-mV limit.

#### Programmable Transmitter Termination

The Stratix GX transmitter buffer includes a 100-, 120-, or 150- $\Omega$  programmable on-chip differential termination resistor. The Stratix GX transmitter buffers are current-mode drivers, so the resultant  $V_{OD}$  is a function of the transmitter termination value. For more information on resultant  $V_{OD}$  values, see "Programmable Voltage Output Differential ( $V_{OD}$ )" on page 2–3.

#### **Transmitter PLL**

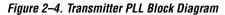

Each transceiver block contains a transmitter PLL and a slow-speed reference clock. The transmitter PLL receives the reference clock and generates the high-speed serial clock used by the serializer. The slow-speed reference clock is used for the transceiver logic. Figure 2–4 shows the transmitter PLL's block diagram. The pll\_locked signal indicates when the transmitter PLL is locked to the reference clock. A high signal indicates that the PLL is locked to the reference clock; a low signal indicates that the PLL is not locked to the reference clock.

Table 2–2 lists some of the transmitter PLL specifications.

| Table 2–2. Transmitter PLL Specifications |                                      |  |

|-------------------------------------------|--------------------------------------|--|

| Parameter                                 | Specifications                       |  |

| Input reference frequency range           | 25 MHz to 650 MHz                    |  |

| Data rate support                         | 500 Mbps to 3.1875 Gbps              |  |

| Multiplication factor (W)                 | 2, 4, 5, 8, 10, 16, or 20 <i>(1)</i> |  |

Note to Table 2–2:

(1) Multiplication factors 2 and 5 can only be achieved with the use of the pre-divider on the REFCLKB.

#### Clock Synthesis

The maximum input frequency of the phase frequency detector (PFD) is 325 MHz. To achieve reference clock frequency above this limitation, the /2 pre-divider on the dedicated local REFCLKB path can be enabled automatically by the Quartus<sup>®</sup> II software. The /2 pre-divider divides the reference clock frequency by a factor of 2 and then the /m factor compensates the frequency difference. An example would be a data rate of 2,488 Mbps with a 622-MHz reference clock. In this scenario, the reference clock must be assigned to the REFCLKB port where the 622-MHz reference clock is divided by 2, yielding a 311-MHz clock at the PFD. This 311-MHz reference clock is then multiplied by a factor of 8 to achieve the 2,488-MHz clock at the VCO.

If the reference clock exceeds 325 MHz, the clock must be fed by the dedicated local reference clock pin, REFCLKB. By default, the Quartus II software assigns pins to be LVTTL, so you must assign the 1.5-V PCML I/O standard to the I/O pins to select the REFCLKB port as the reference source. The Quartus II software prompts a fitter error if the reference clock exceeds 325 MHz and the reference clock source is not on the REFCLKB port.

You can also use the pre-divider on the REFCLKB path to support additional multiplication factors. The block diagram in Figure 2–4 shows that /m can only support multiplication factors of 4, 8, 10, 16, and 20, but Table 2–3 shows that the additional multiplication factors of 2 and 5 are also achievable. You can achieve these multiplication factors by using the pre-divider. A multiplication factor of 2 is achieved by pre-dividing the reference clock by 2 and then multiplying the resultant frequency by 4, which yields a multiplication factor of 2. A multiplication factor of 5 is achieved in the same manner by pre-dividing the reference clock by 2 and then multiplying the resultant frequency by 10, which yields a multiplication factor of 5.

Table 2–3 lists the possible multiplication values as a function of the source to the transmitter PLL. Table 2–3 assumes that the reference clock is directly fed from the source listed and does not factor any pre-clock synthesis (that is, the Stratix GX PLL driving a global clock that is used for the transmitter PLL reference clock source).

Table 2–3. Multiplication Values as a Function of the Reference Clock

Source to the Transmitter PLL

| Transmitter PLL Reference Clock<br>Source | Multiplication Factors |

|-------------------------------------------|------------------------|

| Global clock, I/O bus, general routing    | 4, 8, 10, 16, 20       |

| Inter-transceiver routing                 | 2, 4, 5, 8, 10, 16, 20 |

| Dedicated local REFCLKB                   | 2, 4, 5, 8, 10, 16, 20 |

You must specify the data rate of the channel and input clock period of the reference clock. The data rate divided by the input clock period must equal one of the multiplication factors listed in Table 2–3.

#### Transmitter PLL Bandwidth Setting

The Stratix GX transmitter PLL in the transceiver block offers a programmable bandwidth setting. The PLL bandwidth is the measure of its ability to track the input clock and jitter. The bandwidth is determined by the –3-dB frequency of the closed-loop gain of the PLL.

A high-bandwidth setting provides a faster lock time and tracks more jitter on the input clock source which passes it through the PLL. This helps reject noise from the VCO and power supplies. A low-bandwidth setting, on the other hand, filters out more high frequency input clock jitter, but increases lock time.

You can set the bandwidth for Stratix GX devices to either low or high. The –3-dB frequencies for these settings can vary due to the non-linear nature and frequency dependencies of the circuit. As a result, you can vary the bandwidth to customize the performance on specific systems.

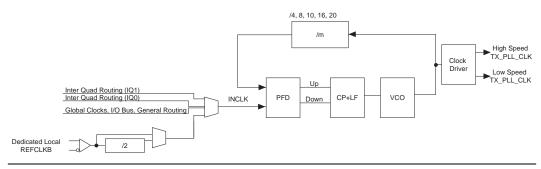

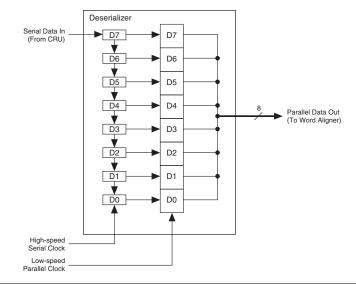

#### Serializer (Parallel-to-Serial Converter)

The serializer converts parallel data to serial data at the transmitter output buffer. The serializer can support 8- or 10-bit words when used with the transmitter multiplexer. The 8-bit serializer drives the serial data to the output buffer, as shown in Figure 2–5. The serializer can drive the serial bit-stream at a data rate range of 500 Mbps to 3.1875 Gbps. The serializer outputs the least significant bit (LSB) of the word first.

Figure 2–5. Example of 8-Bit Serialization

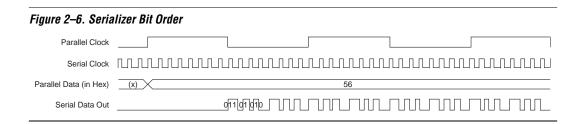

Figure 2–6 shows the serial bit order of the serializer output. In this example, a constant 8'h6a (01010110) value is serialized.

The serial data is transmitted from LSB to most significant bit (MSB).

IP

### **Receiver Analog**

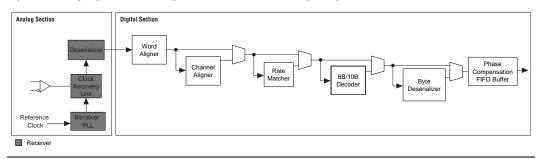

This section describes the receiver input buffer, the receiver PLL, the clock recovery unit, and the deserializer. Figure 2–7 shows the receiver analog components.

Figure 2–7. Highlighted Block Diagram of the Receiver Analog Components

#### **Receiver Input Buffer**

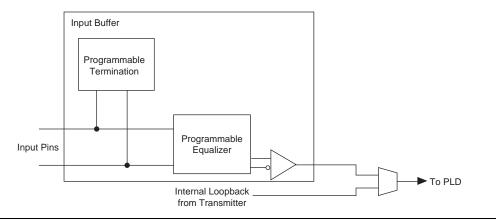

The receiver input buffer contains internal termination and internal equalization. Figure 2–8 shows the structure of the input buffer. The input buffer has programmable equalization that you can apply to increase the signal integrity of the transmission line. The internal termination in the receiver buffer can support AC and DC coupling with programmable differential termination settings of 100, 120, or 150  $\Omega$ .

Figure 2–8. Receiver Input Buffer

#### Programmable Receiver Termination

The Stratix GX receiver buffer includes programmable on-chip differential termination of 100, 120, or 150  $\Omega$ .

This assignment must be made per pin through the Assignment Editor in the Quartus II software. Select **Assignment Organizer > Options for Individual Nodes Only > Stratix GX Termination Value** (Assignments menu).

The proper termination settings should be selected and verified accordingly before compilation.

The transmitter PLL input signal (inclk) drives the termination resistance calibration circuit. The Quartus II software allows receiver-only configurations in Stratix GX devices. However, if you use the Quartus II software to remove the transmitter PLL in a receiver-only configuration, you will see an incorrect value or unpredictable behavior with the receiver input pin termination. If the rx\_cruclk signal is globally routed, the Quartus II software handles this automatically. If the rx\_cruclk signal is not globally routed or routed using the interquadrant line (IQ2), the Quartus II software returns a no-fit. In this situation, you must add a transmitter PLL to your design.

If the pll\_areset (analog reset) signal goes high, the RX\_Vcm value is less than the 1.1 V. This value varies unpredictably because the circuit is tristated. RX\_Vcm is referenced from the Stratix GX receiver analog power supply.

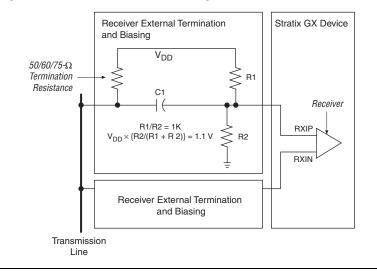

If external termination is used, the receiver must be externally terminated and biased to 1.1 V. Figure 2–9 shows an example of an external termination and biasing circuit.

Figure 2–9. External Termination & Biasing Circuit

#### Enable Stratix GX-to-Stratix GX Receiver DC Coupling

You can configure the Stratix GX receiver buffers so that DC-coupled Stratix GX-to-Stratix GX communication is possible. The Stratix GX transmitter's common-mode is typically around 750 mV, while the receiver common mode by default is approximately 1.1 V. However, by enabling DC coupling, the receiver common mode is biased to allow interoperability with the Stratix GX transmitter.

#### Equalizer Mode

Stratix GX transceivers offer an equalization circuit in each receiver channel to increase noise margins and help reduce the effects of high frequency losses. The programmable equalizer compensates for inter-symbol interference (ISI) and high frequency losses that distort the signal and reduce the noise margin of the transmission medium by equalizing the frequency response.

The transfer function of a transmission line can be represented in the frequency domain as a low-pass filter. Any frequency components below the –3-dB frequency pass through with minimal losses. Frequency components that are greater than the –3-dB frequency are attenuated.

This variation in frequency response yields data-dependant jitter and other ISI effects. By applying equalization, the low frequency components are attenuated. This equalizes the frequency response so that the delta between the low frequency and high frequency components are reduced, which minimizes the ISI effects from the transmission medium.

In Stratix GX transceivers, the programmable equalizer settings can have one of five values (0 through four). You should experiment with the equalization values to determine the optimal setting based on your system variables.

As with the  $V_{OD}$  settings, you can set the equalization settings statically during configuration or adjust them dynamically in user mode. You can select the static equalization value through a drop-down menu in the altgxb MegaWizard Plug-In. This action sets the appropriate equalization setting in the configuration file. The disadvantage of this mode is that the equalization is set on a per-transceiver block basis and cannot be changed without regenerating another programming file.

On the other hand, if you select the dynamic adjustment in the altgxb MegaWizard Plug-In, the equalization setting can be configured dynamically by the device during user mode. This configuration is accomplished by asserting encoded values on the rx\_equalizerctrl signal, which is instantiated in the altgxb module when this option is selected. This feature lets you make quick performance evaluations of the various settings without having to recompile and regenerate multiple configuration files. Another advantage is that this option allows the equalization of each channel to be configured independently. Refer to "MegaWizard Analog Features" on page 2–20 for more details.

#### **Receiver PLL**

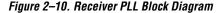

Each transceiver block contains four receiver PLLs and a slow-speed reference clock. The receiver PLLs receive the reference clock and generate the high-speed serial clock used by the CR. The slow-speed reference clock is used for the transceiver logic. Figure 2–10 shows the block diagram for the lock-to-reference portion of the receiver PLL.

This section focuses on the receiver PLL in Lock-to-Reference mode. The lock-to-data circuit has been omitted. Refer to the "Lock-to-Reference Mode & Lock-to-Data Mode" on page 2–16 for more information on the operation between the two modes.

The receiver PLL contains an optional loss-of-lock indicator signal (rx\_locked) that indicates when the receiver PLL is not locked to the reference clock. The rx\_locked signal is active low. A low signal indicates that the PLL is locked to a reference clock; a high signal indicates that the PLL is not locked to the reference clock.

Table 2-4 lists some of the clock recovery unit specifications.

| Table 2–4. Clock Recovery Unit Specifications |                               |  |

|-----------------------------------------------|-------------------------------|--|

| Parameter                                     | Specification                 |  |

| Input reference frequency range               | 25 MHz to 650 MHz             |  |

| Data rate support                             | 500 Mbps to 3.1875 Gbps       |  |

| Multiplication factor (W)                     | 2, 4, 5, 8, 10, 16, or 20 (1) |  |

#### Note to Table 2-4:

(1) Multiplication factors 2, 4, and 5 can only be achieved with the use of the predivider on the REFCLKB port or if the CRU is trained with the low speed clock from the transmitter PLL.

#### Clock Synthesis

The maximum input frequency of the PFD of the receiver PLL is 325 MHz. To achieve reference clock frequency above this limit, the Quartus II software enables the divide by 2 pre-divider on the dedicated local REFCLKB path. This divides the reference clock frequency by a factor of 2 and then the /m factor compensates the frequency difference. For example, given a data rate of 2,488 Mbps with a reference clock of 622 MHz, the reference clock must be assigned to the REFCLKB port,

where the reference clock signal is divided by 2, yielding a 311 MHz clock at the PFD. This 311-MHz reference clock is then multiplied by a factor of 8 to achieve the 2,488-MHz clock at the VCO.

If the reference clock (RX\_CRUCLK) exceeds 325 MHz, the clock must be fed by the dedicated local reference clock pin, REFCLKB. By default, the Quartus II software assigns pins to be LVTTL, so a 1.5-V PCML I/O standard assignment is required to select the REFCLKB port as the reference source. The Quartus II software prompts a fitter error if the reference clock exceeds 325 MHz and the reference clock source is not on the REFCLKB port.

The pre-divider on the REFCLKB path is also used to support additional multiplication factors. The block diagram in Figure 2–10 on page 2–13 shows that /m supports only multiplication factors of 8, 10, 16, and 20, but Table 2–4 states that the additional multiplication factors of 2, 4, and 5 can also be achieved.

Without using the transmitter PLL, the pre-divider achieves the multiplication factors of 4 and 5. A multiplication factor of 4 is achieved by pre-dividing the reference clock by 2 and then multiplying the resulting frequency by 8, which yields a multiplication factor of 4. A multiplication factor of 5 is achieved in the same manner by pre-dividing the reference clock by 2 and then multiplying the resulting frequency by 10, which yields a multiplication factor of 5.

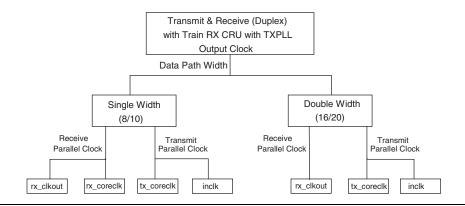

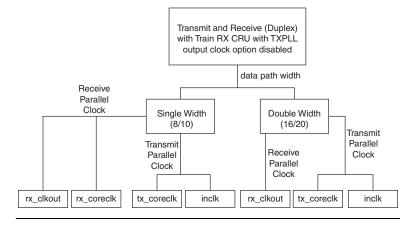

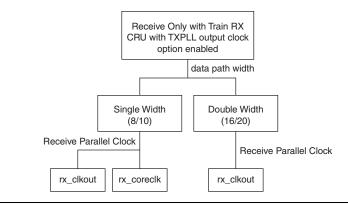

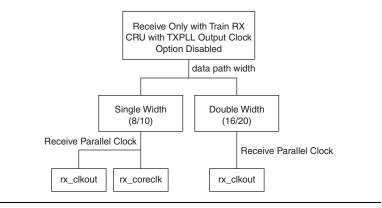

The MegaWizard Plug-In altgxb option enables the transmitter PLL in receiver mode. There is also an option to train the receiver CRU with the output of the low-speed transmitter PLL clock. If you select this option, all the multiplication factors that are supported in the transmitter PLL are also supported in the receiver CRU PLL, including the multiplication factor of 2. This option selects the low-speed transmitter PLL clock as the reference source. The low speed transmitter PLL clock is either divided by a SERDES factor of 8 or 10. The receiver PLL then multiplication factor as the transmitter PLL.

For example, a multiplication factor of 2 is achieved on the transmitter PLL by pre-dividing the reference clock by 2 and then multiplying the resultant frequency by 4, which yields a multiplication factor of 2. However, on the low-speed clock output, this frequency is divided by a factor of 8 or 10, depending on the deserialization factor. The low-speed clock feeds the reference of the receiver PLL where the clock is multiplied back up by a factor of 8 or 10, which results in total multiplication factor of 2.

Table 2–5 lists the possible multiplication values as a function of the reference clock source to the receiver PLL. Table 2–5 assumes that the reference clock (RX\_CRUCLK) is directly fed from the source listed and does not factor any pre-clock synthesis (that is, a Stratix GX PLL driving a global clock used for the receiver PLL reference clock source).

| Table 2–5. Multiplication Values as a Function of the Reference Clock<br>Source to the Receiver PLL |                        |  |

|-----------------------------------------------------------------------------------------------------|------------------------|--|

| Receiver PLL Reference Clock Source                                                                 | Multiplication Factors |  |

| Global clock, IO bus, general routing                                                               | 8, 10, 16, 20          |  |

| Inter-transceiver routing                                                                           | 4, 5, 8, 10, 16, 20    |  |

| Dedicated local REFCLKB                                                                             | 4, 5, 8, 10, 16, 20    |  |

| Low-speed transmitter PLL clock<br>(train CRU with transmitter PLL option)                          | 2, 4, 5, 8, 10, 16, 20 |  |

You specify the data rate of the channel and receiver CRU clock period of the receiver reference clock. The data rate divided by the input clock period must equal one of the multiplication factors listed in Table 2–5.

#### PPM Frequency Threshold Detector

The PPM frequency threshold detector senses whether the incoming reference clock to the CRU and the PLL VCO of the CRU are within a prescribed PPM tolerance range. Valid parameters are 125, 250, 500, or 1,000 PPM. The default parameter, if no assignments are made, is 1,000 PPM. The output of the PPM frequency threshold detector is one of the variables that asserts the rx\_freqlocked signal. Refer to "Clock Recovery Unit" on page 2–16 for more detail regarding the rx\_freqlocked signal.

#### Receiver Bandwidth Type

The Stratix GX receiver PLL in the CRU offers a programmable bandwidth setting. The bandwidth of a data recovery PLL is the measure of its ability to track the input data and jitter. The bandwidth is determined by the -3-dB frequency of the closed-loop gain of the PLL.

A higher bandwidth setting provides a faster lock time and tracks greater jitter on the input data source, rx\_in[], which passes it through the PLL. This helps reject noise from the VCO and power supplies. A low-bandwidth setting, on the other hand, filters out more high-frequency data input jitter, but increases lock time.

Valid receiver bandwidth settings are low, medium, and high. The -3-dB frequencies for these settings vary due to the non-linear nature and data dependencies of the circuit. You vary the bandwidth to customize the performance on specific systems.

#### **Clock Recovery Unit**

The CRU in each Stratix GX receiver channel recovers the clock from the serial data stream on RX IN. You can set the CRU to automatically or manually alter the receiver PLL phase and frequency to match the bit transition on the incoming data stream. This is to eliminate any clock-to-data skew or to keep the receiver PLL locked to the reference clock (lock-to-data or lock-to-reference mode). The CRU generates two clocks, a high-speed RCVD CLK to feed the deserializer and a low-speed RCVD CLK to feed transceiver logic. You can set the CRU to optionally detect run-length violations in the incoming data stream and generate an error whenever the preset run length is exceeded (run-length violation detection circuit).

#### Lock-to-Reference Mode & Lock-to-Data Mode

The Stratix GX device offers both automatic and manual locking options, as described in the following sections.

#### Automatic Lock Mode

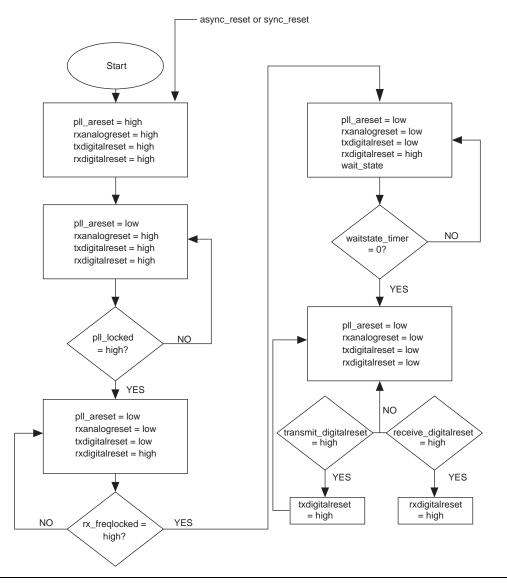

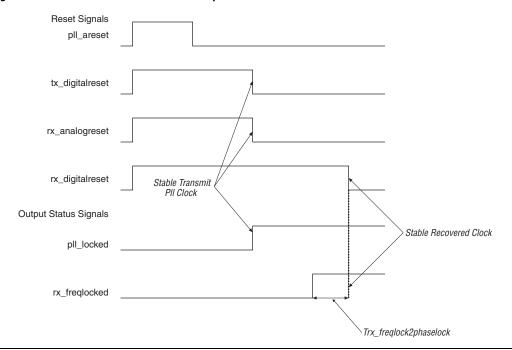

By default, the CRU initially locks to the CRU reference clock RX CRUCLK (lock-to-reference mode) until conditions warrant the switchover to the incoming data (lock-to-data mode). The device switches to the lock-to-data mode when the rx freqlocked signal goes high. After switching to lock-to-data mode, the CRU requires more time to lock to the incoming serial data.

2 - 16

For information about the CRU to serial data lock time, which includes frequency lock (during lock-to-reference mode) and phase lock (during lock-to-data mode), refer to the Stratix GX FPGA Family data sheet. Also refer to the Reset Control & Power Down chapter for the recommendations on resets.

To automatically transition from the lock-to-reference mode to the lock-to-data mode, the following conditions must be met:

- The CRU PLL is within the prescribed PPM frequency threshold setting (125, 250, 500, or 1,000 PPM) of the CRU reference clock.

- Reference clock and CRU PLL output are phase matched (phases are within 0.08 UI).

During the lock-to-reference mode, the frequency detector determines whether the reference clock to the receiver PLL and the VCO output are within the prescribed PPM setting.

The phase lock happens when the phase-frequency detector up/down transitions are relatively few and, the pulse widths are sufficiently narrow. These conditions show that the PLL is close to absolute phase lock to the reference clock. This ensures that when actual data signals are sampled, the receiver PLL locks to the fundamental REFCLK frequency and does not drift off to any sub-harmonic.

In lock-to-data mode, the PLL uses a phase detector to keep the recovered clock aligned properly with the data. If the PLL does not stay locked to data because of problems such as frequency drift or severe amplitude attenuation, the receiver PLL locks back to the reference clock of the CRU to train the VCO. When the device is in lock-to-data mode, the CRU tries to align itself with incoming data and there is no phase relationship with the reference clock.

In lock-to-data mode, the rx\_freqlocked signal is asserted, and the rx\_locked signal looses its significance. The rx\_locked signal signifies that the CRU has locked to the reference clock. When the CRU is in lock-to-data mode, the rx\_locked signal behavior is not predictable.

In automatic lock mode, CRU is forced out of lock-to-data mode if the CRU PLL is not within the recommended PPM frequency threshold setting (125 PPM, 250 PPM, 500 PPM, 1000 PPM) of the CRU reference clock.

When the CRU goes out of lock-to-data mode, the rx\_freqlocked signal goes low. The rx\_freqlocked signal also goes low when either the rx\_analogreset or pll\_areset signal goes high. The rx\_analogreset signal powers down the receiver and the pll\_areset signal powers down the entire transceiver block (four channels).

#### **Manual Lock Options**

Two optional input pins, rx\_locktorefclk[] and rx\_locktodata[], are available that let you control whether the CRU PLL automatically or manually switches between lock-to-reference clock and lock-to-data modes. This lets you bypass the default automatic switchover circuitry if either the rx\_locktorefclk[] or rx\_locktodata[] signal is instantiated.

When the rx\_locktorefclk[] signal is asserted, it forces the CRU PLL to lock to the reference clock (RX\_CRUCLK). Asserting the rx\_locktodata[] signal forces the CRU PLL to lock to data, whether

or not the CRU is ready. When both signals are asserted, the rx\_locktodata[] signal takes precedence over the rx\_locktorefclk[] signal.

You might want to have control over both rx\_locktorefclk[] and rx\_locktodata[] signals to potentially reduce the CRU lock times. The PPM threshold frequency detector and phase relationship detector require additional latencies to ensure that the CRU is ready to lock to data. These extra latencies are potentially reduced by manually controlling the CRU train signals. You assert the rx\_locktorefclk[] signal to initially train the CRU and, after some delta time, assert the rx\_locktodata[] signal.

You configure the controller that controls the signals based on your system. You do this by experimenting because many variables must be considered, such as temperature, transition densities, and data rates. However, by doing so, you are not subjected to the CRU lock times required to verify if the two conditions to switch from lock-to-reference mode to lock-to-data mode in the defaulted automatic mode are met. When the rx\_locktorefclk goes high, the rx\_freqlocked signal is ignored and does not toggle. The rx\_freqlocked signal always goes high if lock-to-data mode is asserted. If you want to transition from lock-to-data mode to automatic mode, the transition should be followed by rx\_analogreset to send the rx\_freqlocked signal low. The CRU does not often transition from manual mode to automatic mode during system operation.

The rx\_analogreset signal functions like a power down signal as opposed to a digital reset. For more information on various reset signals, refer to the chapter *Reset Control & Power Down*.

#### Run Length Violation Detection Circuit

The programmable run length violation (RLV) circuit is in the CRU and detects consecutive ones or zeros in the data. If the data stream exceeds the preset maximum number of consecutive ones or zeros, the violation is signified by the assertion of the rx\_rlv signal.

The rx\_rlv signal is not synchronized to the parallel data, and as a result appears in the logic array earlier than the run-length violation data. To ensure that the FPGA latches this signal in systems where there are frequency variations between the recovered clock and the PLD logic array clock, the rx\_rlv signal is asserted for more than two clock cycles in 8or 10-bit data modes and three clock cycles in 16- or 20-bit data modes. If the data width is 8 or 16, set the legal run length threshold values within the range of 4 to 128 UI in multiples of four. If the data width is 10 or 20, or if using 8b10b, set the legal run length threshold values within the range of 5 to 160 UI in multiples of five.

See the *Stratix GX FPGA Family* data sheet to verify the guaranteed maximum run length.

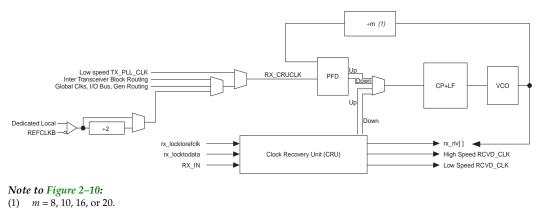

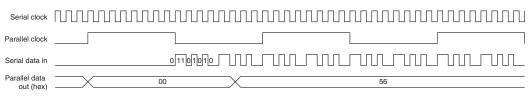

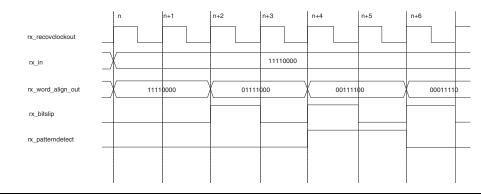

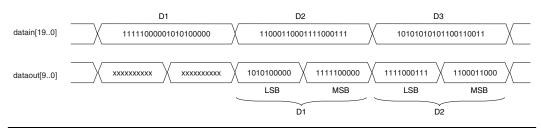

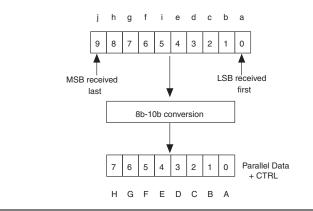

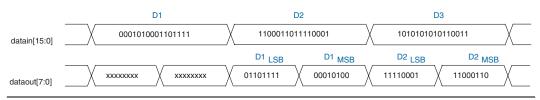

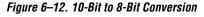

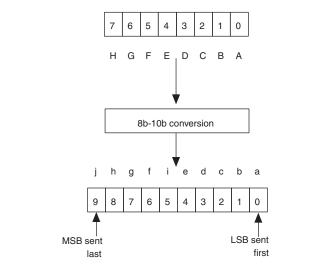

## **Deserializer (Serial-to-Parallel Converter)**

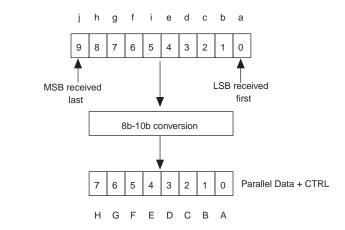

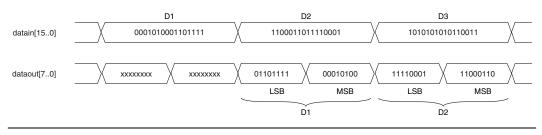

The deserializer converts incoming high-speed serial data streams to either 8- or 10-bit-wide parallel data synchronized to the recovered clock of the CRU. The deserializer drives the parallel data to the pattern detector and word aligner, as shown in Figure 2–11. The data rate of the deserializer output bus is the input data rate divided by the width of the output data bus. For example, for a 10-bit bus and a serial input data rate of 2.5 Gbps, the parallel data rate is 2500/10 or 250 MHz. The first bit into the deserializer is the LSB of the data bus out of the deserializer.

Figure 2–12 shows the serial bit order of the deserializer input and the parallel data out of the deserializer.

The serial data is received LSB to MSB.

#### Figure 2–12. Deserializer Bit Order

## MegaWizard Analog Features

This section describes the analog options for the instantiation of the altgxb megafunction in the Quartus II MegaWizard<sup>®</sup> Plug-In Manager. Altera<sup>®</sup> recommends that the Stratix GX transceiver block be instantiated and parameterized through the MegaWizard Plug-In Manager. The MegaWizard Plug-In Manager offers a graphical user interface (GUI) that organizes the altgxb options in easy-to-use sections. The wizard also sets the proper ports and parameters automatically, based on the options and parameters you select. Invalid settings are automatically flagged to avoid illegal configurations.

Although you can instantiate the Stratix GX block directly by calling out the altgxb megafunction, Altera recommends using the MegaWizard Plug-In Manager to instantiate your altgxb megafunction, reducing the likelihood of invalid settings.

## MegaWizard Analog Feature Considerations

Each altgxb MegaWizard Plug-In uses one or more transceiver blocks based on the number of channels you select. There are four channels per transceiver block. If a MegaWizard Plug-In Manager instantiation uses fewer than four channels, the remaining channels in that transceiver block are not available for use.

Each MegaWizard Plug-In Manager instantiation must have similar functionality and data rates. If you want transceiver blocks that differ in functionality and data rates, create a separate MegaWizard Plug-In Manager instantiation for each transceiver block.

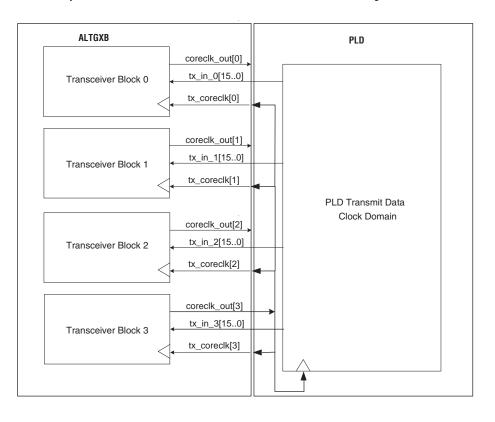

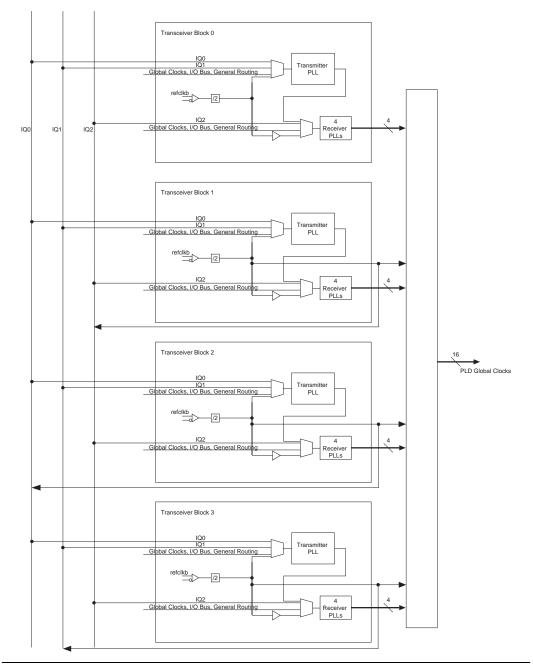

As mentioned in the clocking section, the MegaWizard Plug-In Manager also displays the configuration of the altgxb megafunction. Figures 2–13 through 2–19 change dynamically based on the selected mode, options, and clocking schemes.

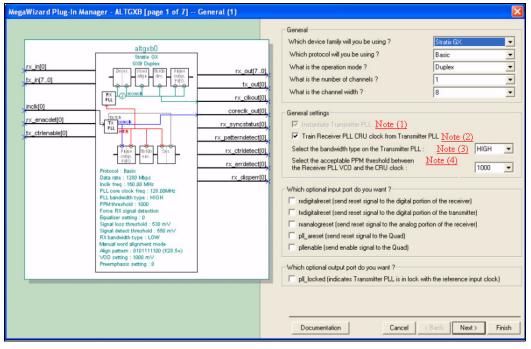

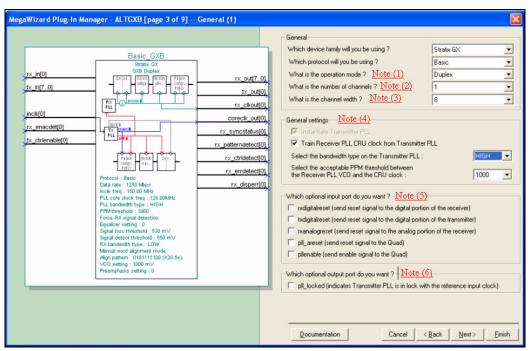

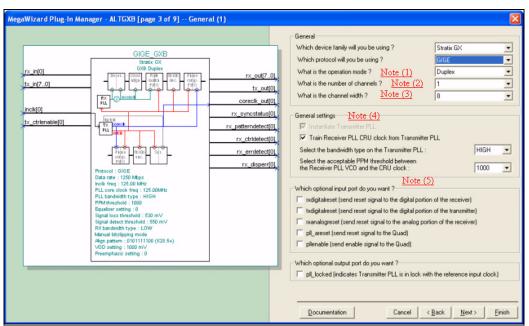

#### Figure 2–13. MegaWizard Plug-In Manager - ALTGXB (Page 1 of 7) - General (1) Notes (1)–(4)

#### Notes to Figure 2–13:

- Option available in receiver-only mode: Supports use of the transmitter PLL even when the transmit channel is disabled. Provides a non-recovered clock output for the logic array.

- (2) Enables the transmitter PLL to train the receiver PLL: Use this option to support additional multiplication factors for the receiver PLL. This option also supports the separation of receiver and transmitter reference clocks. An additional input receiver reference clock (rx\_cruclk) is available when this option is turned off. The first option that is enabled is needed for non-encoded 16-bit modes with a line rate of 2,600 Mbps or greater. For more details regarding this feature, refer to "Clock Synthesis" on page 2–6.

- (3) Selectable High and Low: High bandwidth supports faster lock times. It also tracks higher frequency jitter (based on the -3-db frequency of the PLL gain plot) on the input clock. Low bandwidth has a smaller pass band to filter out more high-frequency jitter, but has a slower lock time.

- (4) Selectable PPM difference tolerance {125, 250, 500, 1000} between the Receiver PLL VCO and the CRU clock: This is one of three parameters that affect the rx\_freqlocked signal. If an out-of-tolerance event occurs, rx\_freqlocked goes low.

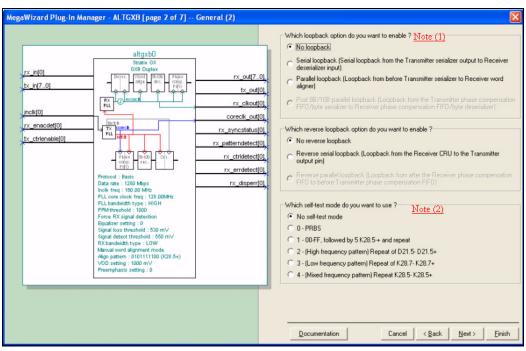

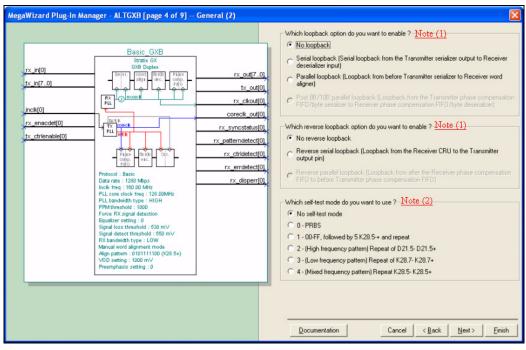

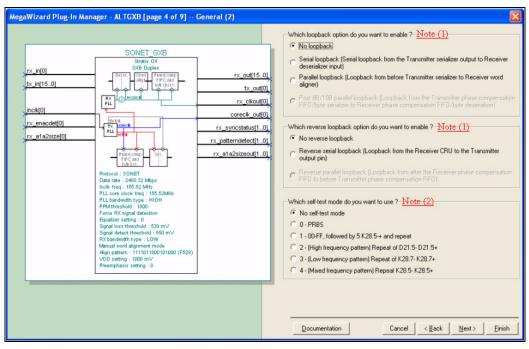

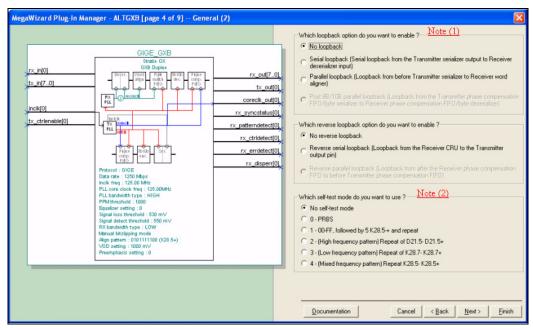

Figure 2–14. MegaWizard Plug-In Manager - ALTGXB (Page 2 of 7) - General (2) Notes (1), (2)

Notes to Figure 2–14:

- (1) For information, refer to the Loopback Modes chapter.

- (2) For more information, refer to the Stratix GX Built-In Self Test (BIST) chapter.

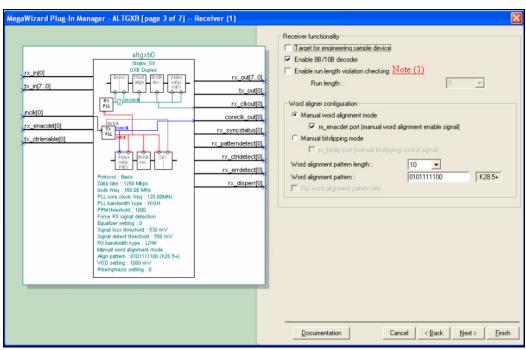

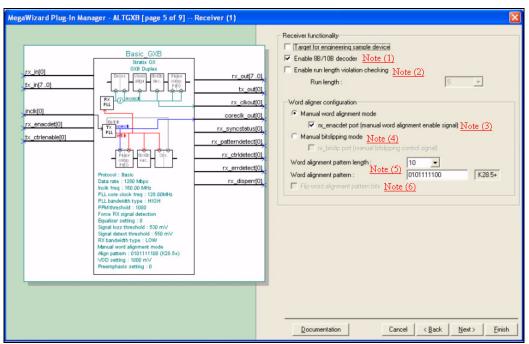

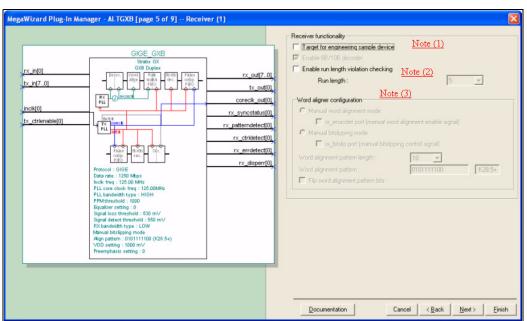

Figure 2–15. MegaWizard Plug-In Manager - ALTGXB (Page 3 of 7) - Receiver (1) Note (1)

#### Note to Figure 2–15:

(1) Enable run length violation circuit. If enabled, the optional output pin rx\_rlv pin is available and pulses high when the specified run length is violated. In 8-bit or 16-bit mode, set the run length threshold from 4 to 124 in steps of 4. In 10-bit and 20-bit mode, or if using 8b10b, set the run length threshold from 5 to 160 in steps of 5.

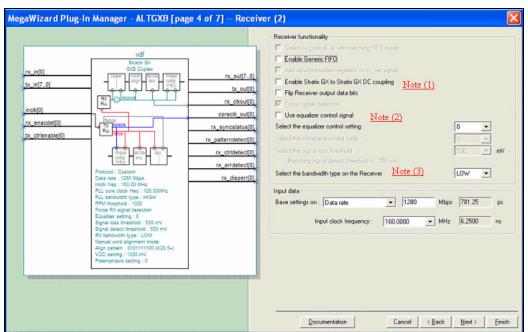

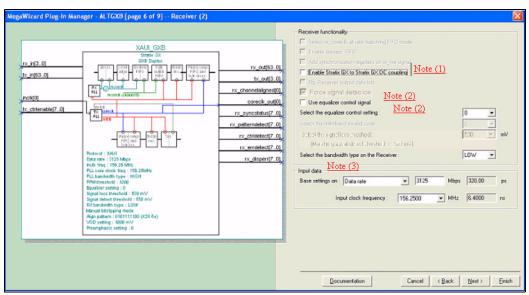

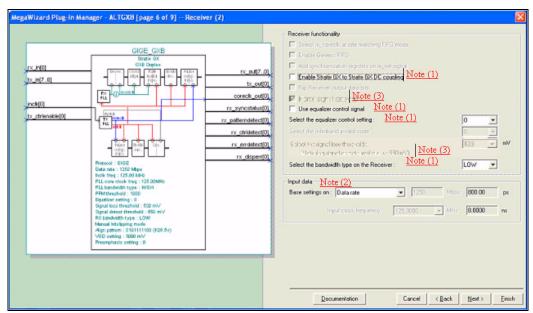

Figure 2–16. MegaWizard Plug-In Manager - ALTGXB (Page 4 of 7) - Receiver (2) Notes (1)–(3)

#### Notes to Figure 2–16:

- Stratix GX to Stratix GX DC coupling only. Lets the receiver accept a 1.5-V PCML signal from a Stratix GX transmitter buffer.

- (2) The Use equalizer control signal option enables dynamic equalization via the optional rx\_equalizerctrl input port. If this control signal is not used, you can set equalization in the MegaWizard Plug-In Manager via the Select the equalizer control setting. The valid values are 0 through 4, with 0 being off and 4 being the largest gain setting.

- (3) Available settings are High, Medium, and Low. High bandwidth allows for faster lock times and tracks higher frequency jitter (based on the -3 db frequency of the PLL gain plot) on the input clock. Low bandwidth contains a smaller pass band to filter out more high-frequency jitter, but has slower lock times.

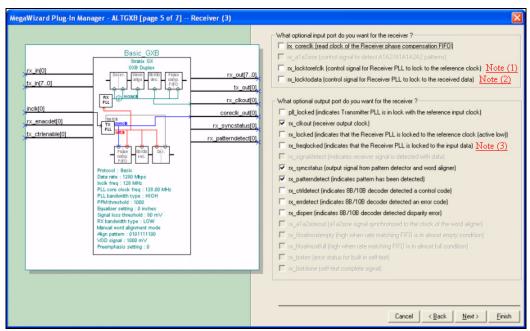

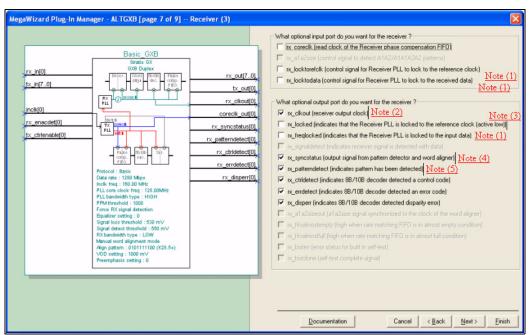

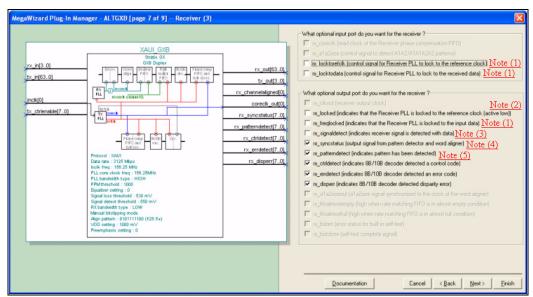

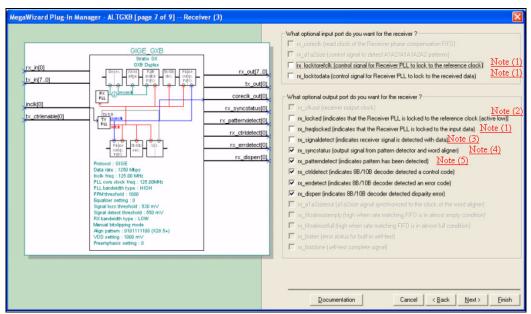

Figure 2–17. MegaWizard Plug-In Manager - ALTGXB (Page 5 of 7) - Receiver (3) Notes (1)–(3)

#### Notes to Figure 2–17:

- (1) Optional input signal that forces the CRU to lock to the reference clock. This disables the auto switch- over mode that switches the CRU to lock-to-data mode. If both rx\_locktorefclk and rx\_locktodata are asserted, then rx\_locktodata takes precedence.

- (2) Optional input signal that forces the CRU to lock to the incoming data. If both rx\_locktorefclk and rx locktodata are asserted, rx locktodata takes precedence.

- (3) Optional output signal that indicates when the CRU is locked to the incoming data stream. The lock indication is based on the following conditions:

a. The CRU PLL is within the prescribed PPM frequency threshold setting (125 PPM, 250 PPM, 500 PPM, 1,000 PPM) of the CRU reference clock.

b. The reference clock and CRU PLL output are phase matched (~ phases are within 0.08 UI).

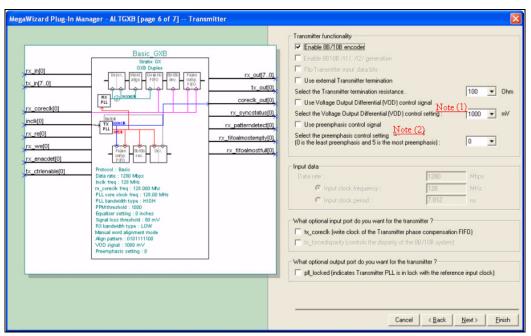

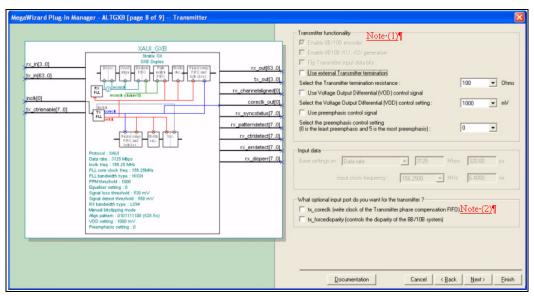

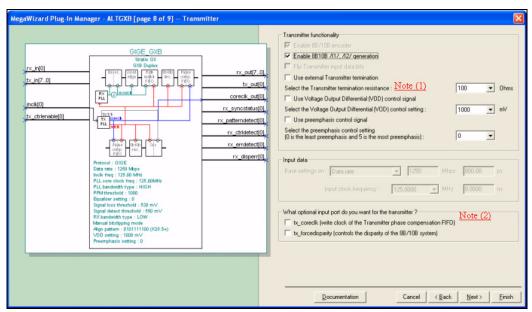

Figure 2–18. MegaWizard Plug-In Manager - ALTGXB (Page 6 of 7) - Transmitter Notes (1), (2)

#### Notes to Figure 2–18:

- (1) The Use V<sub>OD</sub> control signal option enables dynamic V<sub>OD</sub> adjustment via the optional tx\_vodctrl input port. If this control signal is not used, set the V<sub>OD</sub> in the MegaWizard Plug-In Manager via the Select the V<sub>OD</sub> control setting option. The valid values are based on your transmitter termination value and range from 400 to 1,600 mV.

- (2) The Use Preemphasis control signal option enables dynamic pre-emphasis control using the optional tx\_preemphasisctrl input port. If this control signal is not used, set the pre-emphasis in the MegaWizard Plug-In Manager using the Select the preemphasis control setting. The valid values are 1 through 5, where 1 is the smallest pre-emphasis value and 5 is the largest. The amount of pre-emphasis is based on your V<sub>OD</sub> values.

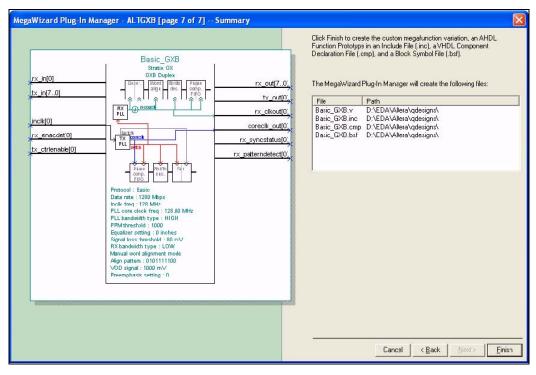

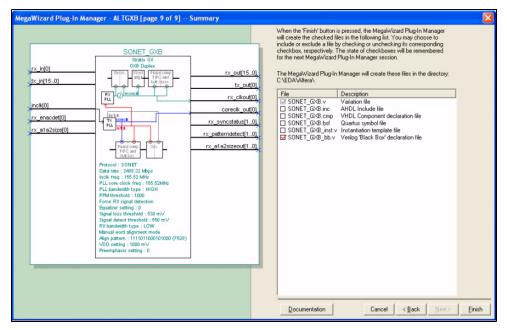

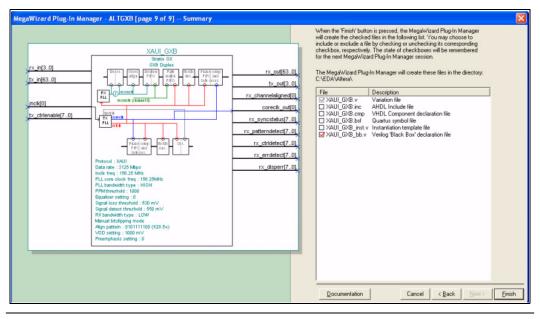

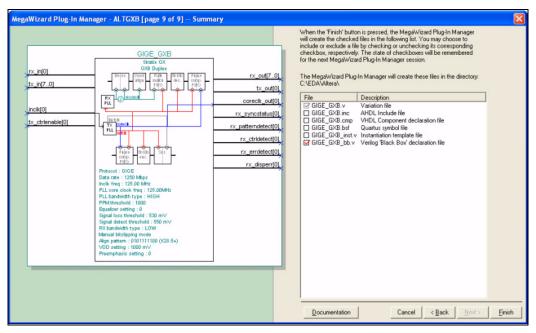

Figure 2–19. MegaWizard Plug-In Manager - ALTGXB (Page 7of 7) - Summary

# 3. Basic Mode

## Introduction

The basic mode of the Stratix<sup>®</sup> GX device includes the following features:

- Serial data rate range from 500 Mbps to 3.1875 Gbps

- Input reference clock range from 25 to 650 MHz

- Parallel interface width of 8, 10, 16, or 20-bit support

- 8B/10B encoder/decoder can be enabled or bypassed

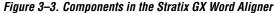

- Word aligner supports 7-bit, 10-bit, 16-bit, or bit slip mode

Applications like packet or streaming data applications, chip-to-chip connectivity, backplanes, or board-to-board connectivity, which do not have a defined protocol overhead or a custom protocol to transfer data serially over a medium, can use the basic mode offered by Stratix GX devices. The basic mode includes SERDES and parallel interconnect functionality. In this mode, the transceiver performs serialization and deserialization with an optional 8B/10B coding scheme. Basic mode is not aware of the system level protocol wrapped on top of it.

Basic mode enables a subset of the transceiver blocks for customizable configuration. The channel aligner and the rate matcher features are not available in basic mode.

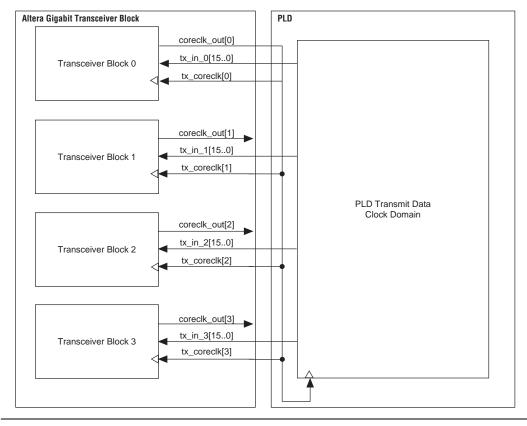

This chapter details the supported digital architecture, clocking schemes, and software implementation for basic mode. Figure 3–1 shows a block diagram of a duplex channel configured in basic mode.

The digital section starts at the word aligner of the receiver channel and propagates up to the device logic array.

Figure 3–1. Block Diagram of a Duplex Channel Configured in Basic Mode

## Basic Mode Receiver Architecture

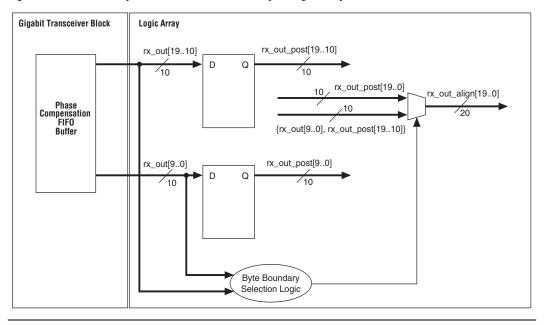

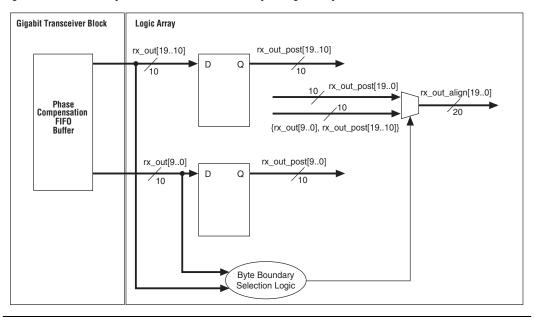

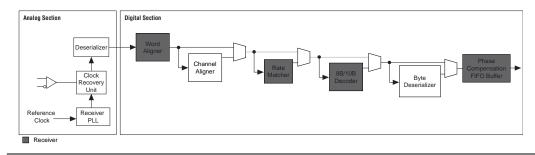

Figure 3–2 shows a block diagram of the digital components of the receiver in basic mode.

Figure 3–2. Block Diagram of the Receiver Digital Components in Basic Mode

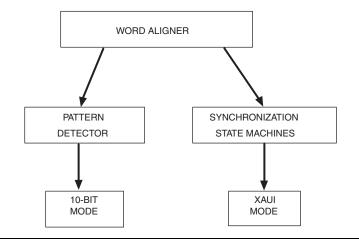

## Word Aligner

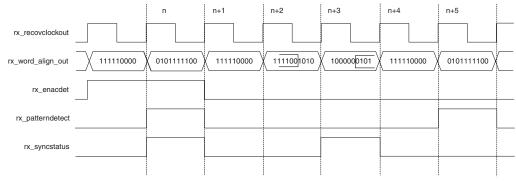

For embedded clocking schemes, the clock is recovered from the incoming data stream based on transition density of the data. This feature eliminates the need to factor in receiver skew margins between the clock and data. However, with this clocking methodology, the word boundary of the re-timed data can be altered. Stratix GX devices offer an embedded

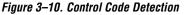

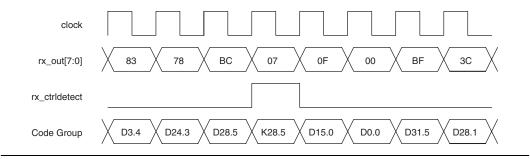

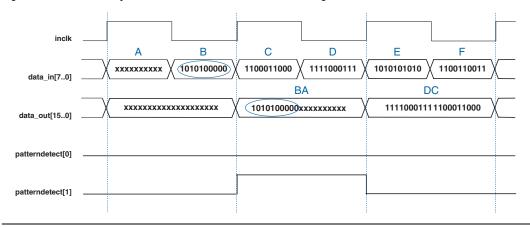

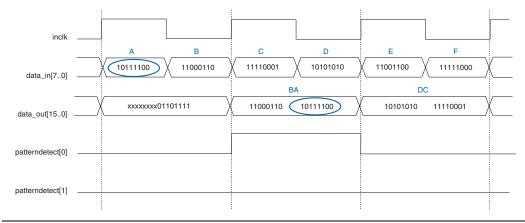

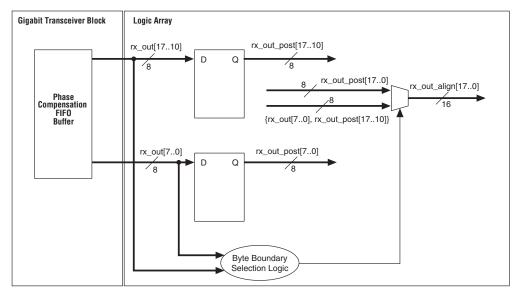

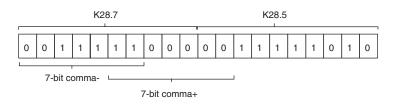

word alignment circuit that is used in conjunction with the pattern detector to align the word boundary of the re-timed data to a specified comma. In basic mode, this embedded circuit is configured to manual alignment mode, which consists of 10-bit, 16-bit, and bit-slip modes.