# STM32W108HB STM32W108CB

# High-performance, 802.15.4 wireless system-on-chip

Data brief

## Features

- Complete System-on-Chip

- 32-bit ARM® Cortex<sup>™</sup>-M3 processor

- 2.4 GHz IEEE 802.15.4 transceiver & lower MAC

- 128-Kbyte Flash, 8-Kbyte RAM memory

- AES128 encryption accelerator

- Flexible ADC, SPI/UART/TWI serial communications, and general-purpose timers

- 24 highly configurable GPIOs with Schmitt trigger inputs

- Industry-leading ARM® Cortex™-M3 processor

- Leading 32-bit processing performance

- Highly efficient Thumb®-2 instruction set

- Operation at 6, 12 or 24 MHz

- Flexible nested vectored interrupt controller

- Low power consumption, advanced management

- RX Current (w/ CPU): 27 mA

- TX Current (w/ CPU, +3 dBm TX): 31 mA

- Low deep sleep current, with retained RAM and GPIO: 400 nA/800 nA with/without sleep timer

- Low-frequency internal RC oscillator for low-power sleep timing

- High-frequency internal RC oscillator for fast (100 μs) processor start-up from sleep

- Exceptional RF performance

- Normal mode link budget up to 102 dB; configurable up to 107 dB

- -99 dBm normal RX sensitivity; configurable to -100 dBm (1% PER, 20 byte packet)

- +3 dB normal mode output power; configurable up to +7 dBm

- Robust WiFi and Bluetooth coexistence

- Innovative network and processor debug

- Non-intrusive hardware packet trace

- Serial wire/JTAG interface

- Standard ARM debug capabilities: Flash patch & breakpoint; data watchpoint & trace; instrumentation trace macrocell

- Application flexibility

- Single voltage operation: 2.1-3.6 V with internal 1.8 V and 1.25 V regulators

- Optional 32.768 kHz crystal for higher timer accuracy

- Low external component count with single 24 MHz crystal

- Support for external power amplifier

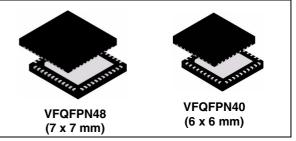

- Small 7x7 mm 48-pin QFN package or 6x6 mm 40-pin QFN package

# Applications

- Smart energy

- Building automation and control

- Home automation and control

- Security and monitoring

- ZigBee® Pro wireless sensor networking

- RF4CE products and remote controls

- 6LoWPAN and custom protocols

#### Table 1. Device summary

| Feature | STM32W108HB | STM32W108CB |

|---------|-------------|-------------|

| Package | 40-pin QFN  | 48-pin QFN  |

August 2009

Doc ID 15851 Rev 1

For further information contact your local STMicroelectronics sales office.

# 1 Description

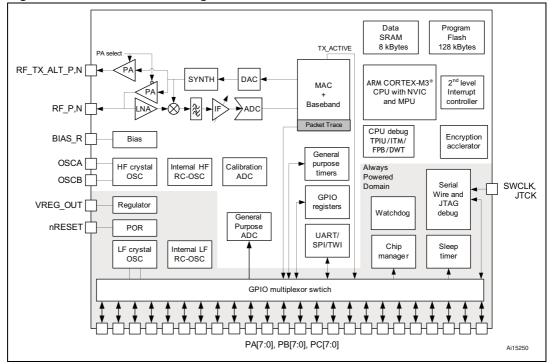

The STM32W is a fully integrated System-on-Chip that integrates a 2.4 GHz, IEEE 802.15.4-compliant transceiver, 32-bit ARM® Cortex<sup>™</sup>-M3 microprocessor, Flash and RAM memory, and peripherals of use to designers of ZigBee-based systems.

The transceiver utilizes an efficient architecture that exceeds the dynamic range requirements imposed by the IEEE 802.15.4-2003 standard by over 15 dB. The integrated receive channel filtering allows for robust co-existence with other communication standards in the 2.4 GHz spectrum, such as IEEE 802.11 and Bluetooth. The integrated regulator, VCO, loop filter, and power amplifier keep the external component count low. An optional high performance radio mode (boost mode) is software-selectable to boost dynamic range.

The integrated 32-bit ARM® Cortex<sup>™</sup>-M3 microprocessor is highly optimized for high performance, low power consumption, and efficient memory utilization. Including an integrated MPU, it supports two different modes of operation: System mode and Application mode. The networking stack software runs in System mode with full access to all areas of the chip. Application code runs in Application mode with limited access to the STM32W resources; this allows for the scheduling of events by the application developer while preventing modification of restricted areas of memory and registers. This architecture results in increased stability and reliability of deployed solutions.

The STM32W has 128 Kbytes of embedded Flash memory and 8 Kbytes of integrated RAM for data and program storage. The STM32W HAL software employs an effective wear-leveling algorithm that optimizes the lifetime of the embedded Flash.

To maintain the strict timing requirements imposed by the ZigBee and IEEE 802.15.4-2003 standards, the STM32W integrates a number of MAC functions into the hardware. The MAC hardware handles automatic ACK transmission and reception, automatic backoff delay, and clear channel assessment for transmission, as well as automatic filtering of received packets. A packet trace interface is also integrated with the MAC, allowing complete, non-intrusive capture of all packets to and from the STM32W.

The STM32W offers a number of advanced power management features that enable long battery life. A high-frequency internal RC oscillator allows the processor core to begin code execution quickly upon waking. Various deep sleep modes are available with less than 1  $\mu$ A power consumption while retaining RAM contents. To support user-defined applications, on-chip peripherals include UART, SPI, TWI, ADC and general-purpose timers, as well as up to 24 GPIOs. Additionally, an integrated voltage regulator, power-on-reset circuit, and sleep timer are available.

## 1.1 Development tools

Finally, the STM32W utilizes standard Serial Wire and JTAG interfaces for powerful software debugging and programming of the ARM Cortex-M3 core. The STM32W integrates the standard ARM system debug components: Flash Patch and Breakpoint (FPB), Data Watchpoint and Trace (DWT), and Instrumentation Trace Macrocell (DWT).

Figure 1. STM32W block diagram

# 2 Electrical characteristics

## 2.1 Parameter conditions

Unless otherwise specified, all voltages are referenced to V<sub>SS</sub>.

#### 2.1.1 Minimum and maximum values

Unless otherwise specified the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A = 25$  °C and  $T_A = T_A$ max (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean  $\pm 3\Sigma$ ).

### 2.1.2 Typical values

Unless otherwise specified, typical data are based on  $T_A$  = 25 °C,  $V_{DD}$  = 3.3 V (for the 2 V  $\leq$  V<sub>DD</sub>  $\leq$  3.6 V voltage range). They are given only as design guidelines and are not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range, where 95% of the devices have an error less than or equal to the value indicated (mean  $\pm 2\Sigma$ ).

### 2.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

### 2.1.4 Loading capacitor

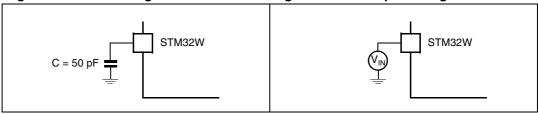

The loading conditions used for pin parameter measurement are shown in Figure 2.

### 2.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in Figure 3.

### Figure 2. Pin loading conditions Figure 3. Pin input voltage

## 2.2 Absolute maximum ratings

Stresses above the absolute maximum ratings listed in *Table 2: Voltage characteristics*, *Table 3: Current characteristics*, and *Table 4: Thermal characteristics* may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Table 2. Voltage characteristic |

|---------------------------------|

|---------------------------------|

| Ratings                                                                                                                                   | Min. | Max.              | Unit |

|-------------------------------------------------------------------------------------------------------------------------------------------|------|-------------------|------|

| Regulator input voltage (VDD_PADS)                                                                                                        | -0.3 | +3.6              | V    |

| Analog, Memory and Core voltage (VDD_24MHZ, VDD_VCO,<br>VDD_RF, VDD_IF, VDD_PADSA, VDD_MEM, VDD_PRE,<br>VDD_SYNTH, VDD_CORE)              | -0.3 | +2.0              | v    |

| Voltage on RF_P,N; RF_TX_ALT_P,N                                                                                                          | -0.3 | +3.6              | V    |

| RF Input Power (for max level for correct packet reception see <i>Table 11: Receive characteristics</i> ) RX signal into a lossless balun |      | +15               | dBm  |

| Voltage on any GPIO (PA[7:0], PB[7:0], PC[7:0]), SWCLK, nRESET, VREG_OUT                                                                  | -0.3 | VDD_PADS<br>+0.3  | V    |

| Voltage on BIAS_R, OSCA, OSCB                                                                                                             | -0.3 | VDD_PADSA<br>+0.3 | v    |

#### Table 3.Current characteristics

| Symbol                 | Ratings                                                  | Max. | Unit |

|------------------------|----------------------------------------------------------|------|------|

| I <sub>VDD</sub>       | Total current into $V_{DD}/V_{DDA}$ power lines (source) | 150  |      |

| I <sub>VSS</sub>       | Total current out of V <sub>SS</sub> ground lines (sink) | 150  |      |

| 1                      | Output current sunk by any I/O and control pin           | 25   |      |

| IO                     | Output current source by any I/Os and control pin        | - 25 | mA   |

|                        | Injected current on NRST pin                             | ± 5  | ШA   |

| I <sub>INJ(PIN)</sub>  | Injected current on HSE OSC_IN and LSE OSC_IN pins       | ± 5  |      |

|                        | Injected current on any other pin                        | ± 5  |      |

| ΣΙ <sub>INJ(PIN)</sub> | Total injected current (sum of all I/O and control pins) | ± 25 |      |

#### Table 4.Thermal characteristics

| Symbol           | Ratings                      | Value       | Unit |

|------------------|------------------------------|-------------|------|

| T <sub>STG</sub> | Storage temperature range    | -40 to +140 | °C   |

| TJ               | Maximum junction temperature | 150         | °C   |

## 2.3 Operating conditions

### 2.3.1 General operating conditions

#### Table 5. General operating conditions

| Symbol             | Parameter                                                                                                             | Conditions                             | Min. | Тур.                                                                                                                                                                                                                                                         | Max. | Unit |

|--------------------|-----------------------------------------------------------------------------------------------------------------------|----------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|

| _                  | Regulator input voltage (VDD_PADS)                                                                                    |                                        | 2.1  |                                                                                                                                                                                                                                                              | 3.6  | V    |

| _                  | Analog and memory input voltage<br>(VDD_24MHZ, VDD_VCO, VDD_RF,<br>VDD_IF, VDD_PADSA, VDD_MEM,<br>VDD_PRE, VDD_SYNTH) |                                        | 1.7  | 1.8                                                                                                                                                                                                                                                          | 1.9  | V    |

| _                  | Core input voltage (VDD_CORE)                                                                                         |                                        | 1.18 | 1.25                                                                                                                                                                                                                                                         | 1.32 | V    |

| _                  | Operating temperature range                                                                                           |                                        | -40  |                                                                                                                                                                                                                                                              | +85  | °C   |

| f <sub>HCLK</sub>  | Internal AHB clock frequency                                                                                          |                                        | 0    |                                                                                                                                                                                                                                                              | 72   |      |

| f <sub>PCLK1</sub> | Internal APB1 clock frequency                                                                                         |                                        | 0    |                                                                                                                                                                                                                                                              | 36   | MHz  |

| f <sub>PCLK2</sub> | Internal APB2 clock frequency                                                                                         |                                        | 0    |                                                                                                                                                                                                                                                              | 72   |      |

| $V_{DD}$           | Standard operating voltage                                                                                            |                                        | 2    |                                                                                                                                                                                                                                                              | 3.6  | V    |

|                    | Analog operating voltage<br>(ADC not used) Must be the same                                                           | 2                                      |      | 3.6                                                                                                                                                                                                                                                          | V    |      |

| V <sub>DDA</sub>   | Analog operating voltage<br>(ADC used)                                                                                | potential as V <sub>DD</sub>           | 2.4  |                                                                                                                                                                                                                                                              | 3.6  | v    |

| V <sub>BAT</sub>   | Backup operating voltage                                                                                              |                                        | 1.8  |                                                                                                                                                                                                                                                              | 3.6  | V    |

|                    | Ambient temperature for 6 suffix                                                                                      | Maximum power dissipation              | -40  |                                                                                                                                                                                                                                                              | 85   | °C   |

| TA                 | version                                                                                                               | Low power<br>dissipation               | -40  |                                                                                                                                                                                                                                                              | 105  | C    |

| IA                 |                                                                                                                       | t temperature for 7 suffix dissipation |      |                                                                                                                                                                                                                                                              | 105  | °C   |

|                    | version                                                                                                               | Low power<br>dissipation               | -40  | 36       72       3.6       3.6       3.6       3.6       3.6       3.6       105       105       125       105                                                                                                                                              | U    |      |

| TJ                 |                                                                                                                       | 6 suffix version                       | -40  |                                                                                                                                                                                                                                                              | 105  | °C   |

| IJ                 | Junction temperature range                                                                                            | 7 suffix version                       | -40  | 1.18     1.25     1.32       -40     +85       0     72       0     36       0     72       0     36       0     72       0     36       2     3.6       2     3.6       2.4     3.6       1.8     3.6       -40     105       -40     105       -40     105 |      |      |

### 2.3.2 Absolute maximum ratings (electrical sensitivity)

Based on three different tests (ESD, LU) using specific measurement methods, the device is stressed in order to determine its performance in terms of electrical sensitivity.

### Electrostatic discharge (ESD)

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts  $\times$  (n+1) supply pins). This test conforms to the JESD22-A114/C101 standard.

| Symbol                | Ratings                                                                     | Conditions                                              | Class | Maximum value <sup>(1)</sup> | Unit |

|-----------------------|-----------------------------------------------------------------------------|---------------------------------------------------------|-------|------------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge voltage (human body model)                          | $T_A = +25 \ ^{\circ}C$<br>conforming to<br>JESD22-A114 | 2     | ±2000                        |      |

| V                     | Electrostatic discharge<br>voltage (charge device<br>model) for non-RF pins | T <sub>A</sub> = +25 °C<br>conforming to                | 11    | ±400                         | v    |

| V <sub>ESD(CDM)</sub> | Electrostatic discharge<br>voltage (charge device<br>model)for RF pins      | JESD22-C101                                             |       | ±225                         |      |

| MSL                   | Moisture sensitivity level                                                  |                                                         |       | MSL3                         | Ι    |

Table 6.ESD absolute maximum ratings

1. Based on characterization results, not tested in production.

#### Static latch-up

Two complementary static tests are required on six parts to assess the latch-up performance:

- A supply overvoltage is applied to each power supply pin

- A current injection is applied to each input, output and configurable I/O pin

These tests are compliant with EIA/JESD 78A IC latch-up standard.

#### Table 7. Electrical sensitivities

| Symbol | Parameter             | Conditions                                    | Class      |

|--------|-----------------------|-----------------------------------------------|------------|

| LU     | Static latch-up class | $T_A = +105 \text{ °C conforming to JESD78A}$ | II level A |

## 2.4 DC electrical characteristics

#### Table 8. DC electrical characteristics

| Parameter                                             | Conditions                         | Min. | Тур. | Max. | Unit |

|-------------------------------------------------------|------------------------------------|------|------|------|------|

| Regulator input voltage<br>(VDD_PADS)                 |                                    | 2.1  |      | 3.6  | v    |

| Power supply range (VDD_MEM)                          | Regulator output or external input | 1.7  | 1.8  | 1.9  | v    |

| Power supply range<br>(VDD_CORE)                      | Regulator output                   | 1.18 | 1.25 | 1.32 | v    |

| Deep Sleep Current                                    |                                    |      |      |      |      |

|                                                       | -40°C, VDD_PADS = 3.6 V            |      | 0.4  |      | μA   |

| Quiescent current, internal RC<br>oscillator disabled | +25°C, VDD_PADS = 3.6 V            |      | 0.4  |      | μA   |

|                                                       | +85°C, VDD_PADS = 3.6 V            |      | 0.6  |      | μA   |

| Parameter                                                       | Conditions                                                                                                                                                        | Min. | Тур. | Max. | Unit |

|-----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

|                                                                 | -40°C, VDD_PADS=3.6 V                                                                                                                                             |      | 0.7  |      | μA   |

| Quiescent current, including internal RC oscillator             | +25°C, VDD_PADS=3.6 V                                                                                                                                             |      | 0.8  |      | μA   |

|                                                                 | +85°C, VDD_PADS=3.6 V                                                                                                                                             |      | 1.2  |      | μA   |

|                                                                 | -40°C, VDD_PADS=3.6V                                                                                                                                              |      | 1.2  |      | μA   |

| Quiescent current, including 32.768 kHz oscillator              | +25°C, VDD_PADS=3.6 V                                                                                                                                             |      | 1.3  |      | μA   |

| 32.700 KHZ USCHIALUI                                            | +85°C, VDD_PADS=3.6 V                                                                                                                                             |      | 1.7  |      | μA   |

| Onice and compare includion                                     | -40°C, VDD_PADS=3.6V                                                                                                                                              |      | 1.4  |      | μA   |

| Quiescent current, including internal RC oscillator and 32.768  | +25°C, VDD_PADS=3.6V                                                                                                                                              |      | 1.5  |      | μA   |

| kHz oscillator                                                  | +85°C, VDD_PADS=3.6 V                                                                                                                                             |      | 2.0  |      | μA   |

| Simulated deep sleep (debug mode) current                       | With no debugger activity                                                                                                                                         |      | 200  |      | μA   |

| Reset current                                                   |                                                                                                                                                                   |      |      |      |      |

| Quiescent current, nRESET asserted                              | Typ at 25°C/3 V<br>Max at 85°C/3.6 V                                                                                                                              |      | 1.2  |      | mA   |

| Processor and peripheral curren                                 | ts                                                                                                                                                                |      | 1    |      |      |

| ARM <sup>®</sup> Cortex-M3, RAM, and flash memory               | 25°C, 1.8 V memory and 1.25<br>V core<br>ARM <sup>®</sup> Cortex-M3 running at 12<br>MHz from crystal oscillator<br>Radio and all peripherals off                 |      | 8.0  |      | mA   |

| ARM <sup>®</sup> Cortex-M3, RAM, and flash memory               | 25°C, 1.8 V memory and 1.25<br>V core<br>ARM <sup>®</sup> Cortex-M3 running at 24<br>MHz from crystal oscillator<br>Radio and all peripherals off                 |      | 9.0  |      | mA   |

| ARM <sup>®</sup> Cortex-M3, RAM, and flash memory sleep current | 25°C, 1.8 V memory and 1.25<br>V core<br>ARM <sup>®</sup> Cortex-M3 clocked at 12<br>MHz from the crystal oscillator<br>Radio and all peripherals off             |      | 4.0  |      | mA   |

| ARM <sup>®</sup> Cortex-M3, RAM, and flash memory sleep current | 25°C, 1.8 V memory and 1.25<br>V core<br>ARM <sup>®</sup> Cortex-M3 clocked at 6<br>MHz from the high frequency<br>RC oscillator<br>Radio and all peripherals off |      | 2.0  |      | mA   |

| Serial controller current                                       | For each controller at maximum data rate                                                                                                                          |      | 0.2  |      | mA   |

| General purpose timer current                                   | For each timer at maximum clock rate                                                                                                                              |      | 0.1  |      | mA   |

#### Table 8. DC electrical characteristics (continued)

| Parameter                                                                                                             | Conditions                                                                                                   | Min. | Тур. | Max. | Unit |

|-----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|------|------|------|------|

| General purpose ADC current                                                                                           | At maximum sample rate, DMA enabled                                                                          |      | 1.1  |      | mA   |

| Rx current                                                                                                            |                                                                                                              |      |      |      |      |

| Radio receiver, MAC, and baseband                                                                                     | ARM <sup>®</sup> Cortex-M3 sleeping                                                                          |      | 20.0 |      | mA   |

| Total RX current ( = $I_{Radio receiver}$ ,<br>MAC and baseband, CPU + $I_{RAM}$ , and<br>Flash memory )              | VDD_PADS = $3.0 \text{ V}, 25^{\circ}\text{C},$<br>ARM <sup>®</sup> Cortex-M3 running at 12<br>MHz           |      | 27.0 |      | mA   |

|                                                                                                                       | VDD_PADS = 3.0 V, 25°C,<br>ARM <sup>®</sup> Cortex-M3 running at 24<br>MHz                                   |      | 28.0 |      | mA   |

| Boost mode total RX current ( =<br>IRadio receiver, MAC and baseband,<br>CPU+ IRAM, and Flash memory )                | VDD_PADS = 3.0 V, 25°C,<br>ARM <sup>®</sup> Cortex-M3 running at 12<br>MHz                                   |      | 28.0 |      | mA   |

|                                                                                                                       | VDD_PADS = 3.0 V, 25°C,<br>ARM <sup>®</sup> Cortex-M3 running at 24<br>MHz                                   |      | 29.0 |      | mA   |

| Tx current                                                                                                            |                                                                                                              |      |      |      |      |

| Radio transmitter, MAC, and baseband                                                                                  | 25°C and 1.8 V core; max.<br>power out (+3 dBm typical)<br>ARM <sup>®</sup> Cortex-M3 sleeping               |      | 26.0 |      | mA   |

|                                                                                                                       | VDD_PADS = 3.0 V, 25°C;<br>maximum power setting<br>(+7dBm); ARM <sup>®</sup> Cortex-M3<br>running at 24 MHz |      | 40.0 |      | mA   |

| Total Tx current(= I <sub>Radio transmitter,</sub><br>MAC and baseband, CPU + I <sub>RAM</sub> , and<br>Flash memory) | VDD_PADS = 3.0 V, 25°C;<br>+3dBm power setting; ARM <sup>®</sup><br>Cortex-M3 running at 24 MHz              |      | 32.0 |      | mA   |

|                                                                                                                       | VDD_PADS = 3.0 V, 25°C;<br>0dBm power setting; ARM <sup>®</sup><br>Cortex-M3 running at 24 MHz               |      | 29.5 |      | mA   |

|                                                                                                                       | VDD_PADS = 3.0 V, 25°C;<br>minimum power setting; ARM <sup>®</sup><br>Cortex-M3 running at 24 MHz            |      | 24.5 |      | mA   |

Table 8.

DC electrical characteristics (continued)

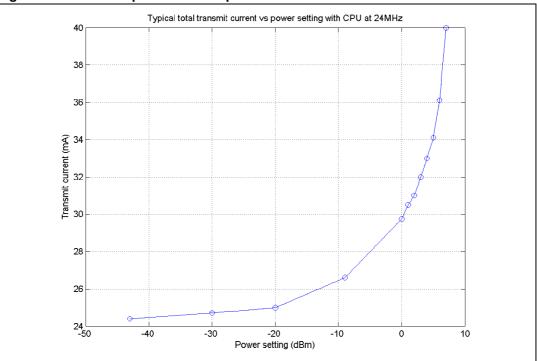

*Figure 4* shows the variation of current in transmit mode (with the ARM<sup>®</sup> Cortex-M3 running at 24 MHz).

Figure 4. Transmit power consumption

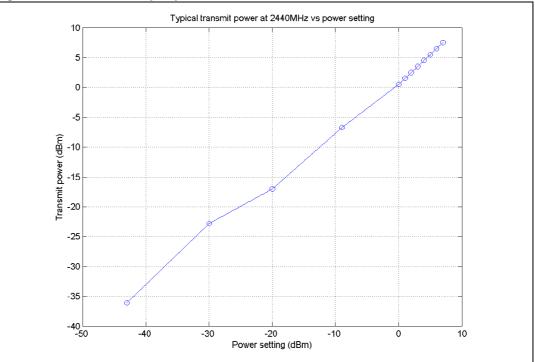

Figure 5. Transmit output power

Doc ID 15851 Rev 1

# 2.5 Digital I/O specifications

*Table 9* lists the digital I/O specifications for the STM32W. The digital I/O power (named VDD\_PADS) comes from three dedicated pins (Pins 23, 28 and 37). The voltage applied to these pins sets the I/O voltage.

| Parameter                                                             | Conditions                                                                                      | Min.                   | Тур. | Max.                   | Unit       |

|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|------------------------|------|------------------------|------------|

| Voltage supply (Regulator Input)                                      | VDD_PADS                                                                                        | 2.1                    |      | 3.6                    | V          |

| Low Schmitt switching threshold                                       | V <sub>SWIL</sub><br>Schmitt input threshold<br>going from high to low                          | 0.42 x<br>VDD_PADS     |      | 0.50 x<br>VDD_PADS     | V          |

| High Schmitt switching threshold                                      | V <sub>SWIH</sub><br>Schmitt input threshold<br>going from low to high                          | 0.62 x<br>VDD_PADS     |      | 0.80 x<br>VDD_PADS     | V          |

| Input current for logic 0                                             | IIL                                                                                             |                        |      | -0.5                   | μ <b>A</b> |

| Input current for logic 1                                             | I <sub>IH</sub>                                                                                 |                        |      | +0.5                   | μ <b>A</b> |

| Input pull-up resistor value                                          | R <sub>IPU</sub>                                                                                | 24                     | 29   | 34                     | kΩ         |

| Input pull-down resistor value                                        | R <sub>IPD</sub>                                                                                | 24                     | 29   | 34                     | kΩ         |

| Output voltage for logic 0                                            | V <sub>OL</sub><br>(I <sub>OL</sub> = 4 mA for standard<br>pads, 8 mA for high current<br>pads) | 0                      |      | 0.18 x<br>VDD_PADS     | V          |

| Output voltage for logic 1                                            | V <sub>OH</sub><br>(I <sub>OH</sub> = 4 mA for standard<br>pads, 8 mA for high current<br>pads) | 0.82 x<br>VDD_PADS     |      | VDD_PADS               | V          |

| Output source current (standard current pad)                          | I <sub>OHS</sub>                                                                                |                        |      | 4                      | mA         |

| Output sink current (standard current pad)                            | I <sub>OLS</sub>                                                                                |                        |      | 4                      | mA         |

| Output source current<br>high current pad: PA6, PA7,<br>PB6, PB7, PC0 | I <sub>ОНН</sub>                                                                                |                        |      | 8                      | mA         |

| Output sink current<br>high current pad: PA6, PA7,<br>PB6, PB7, PC0   | I <sub>OLH</sub>                                                                                |                        |      | 8                      | mA         |

| Total output current (for I/O<br>Pads)                                | I <sub>OH</sub> + I <sub>OL</sub>                                                               |                        |      | 40                     | mA         |

| Input voltage threshold for OSC32A                                    |                                                                                                 | 0.2 x<br>VDD_PADS      |      | 0.8 x<br>VDD_PADS      | ۷          |

| Input voltage threshold for<br>OSCA                                   |                                                                                                 | 0.2 x<br>VDD_PADS<br>A |      | 0.8 x<br>VDD_PADS<br>A | V          |

Table 9. Digital I/O specifications

## 2.6 Non-RF system electrical characteristics

*Table 10* lists the non-RF system level characteristics for the STM32W.

| Parameter                           | Conditions                                                                                                                                                               | Min. | Тур. | Max. | Unit |

|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| System wake time<br>from deep sleep | From wakeup event to first ARM <sup>®</sup> Cortex-<br>M3 instruction running from 6MHz internal<br>RC clock<br>Includes supply ramp time and oscillator<br>startup time | _    | 100  | -    | μs   |

| Shutdown time going into deep sleep | From last ARM <sup>®</sup> Cortex-M3 instruction to deep sleep mode                                                                                                      | Ι    | 5    | _    | μs   |

Table 10.

Non-RF system electrical characteristics

## 2.7 RF electrical characteristics

#### 2.7.1 Receive

Table 11 lists the key parameters of the integrated IEEE 802.15.4 receiver on the STM32W.

Note: Receive measurements were collected with ST's STM32W Ceramic Balun Reference Design (Version A0) at 2440 MHz. The Typical number indicates one standard deviation above the mean, measured at room temperature (25 °C). The Min and Max numbers were measured over process corners at room temperature

| Parameter                                            | Conditions                                              | Min. | Тур. | Max. | Unit |

|------------------------------------------------------|---------------------------------------------------------|------|------|------|------|

| Frequency range                                      |                                                         | 2400 |      | 2500 | MHz  |

| Sensitivity (boost mode)                             | 1% PER, 20 byte packet<br>defined by IEEE 802.15.4-2003 |      | -100 | -95  | dBm  |

| Sensitivity                                          | 1% PER, 20 byte packet<br>defined by IEEE 802.15.4-2003 |      | -99  | -94  | dBm  |

| High-side adjacent channel rejection                 | IEEE 802.15.4 signal at -82<br>dBm                      |      | 35   |      | dB   |

| Low-side adjacent channel rejection                  | IEEE 802.15.4 signal at -82<br>dBm                      |      | 35   |      | dB   |

| 2 <sup>nd</sup> high-side adjacent channel rejection | IEEE 802.15.4 signal at -82<br>dBm                      |      | 43   |      | dB   |

| 2 <sup>nd</sup> low-side adjacent channel rejection  | IEEE 802.15.4 signal at -82<br>dBm                      |      | 43   |      | dB   |

| Channel rejection for all other channels             | IEEE 802.15.4 signal at -82<br>dBm                      |      | 40   |      | dB   |

| 802.11g rejection centered at +12<br>MHz or -13 MHz  | IEEE 802.15.4 signal at -82<br>dBm                      |      | 35   |      | dB   |

| Maximum input signal level for correct operation     |                                                         | 0    |      |      | dBm  |

Table 11. Receive characteristics

| Parameter                                                           | Conditions                         | Min. | Тур. | Max. | Unit |

|---------------------------------------------------------------------|------------------------------------|------|------|------|------|

| Co-channel rejection                                                | IEEE 802.15.4 signal at -82<br>dBm |      | -6   |      | dBc  |

| Relative frequency error<br>(2x40 ppm required by IEEE<br>802.15.4) |                                    | -120 |      | +120 | ppm  |

| Relative timing error<br>(2x40 ppm required by IEEE<br>802.15.4)    |                                    | -120 |      | +120 | ppm  |

| Linear RSSI range                                                   | As defined by IEEE 802.15.4        | 40   |      |      | dB   |

| RSSI Range                                                          |                                    | -90  |      | -30  | dBm  |

Table 11.

Receive characteristics (continued)

#### 2.7.2 Transmit

*Table 12* lists the key parameters of the integrated IEEE 802.15.4 transmitter on the STM32W.

Note: Transmit measurements were collected with ST's STM32W Ceramic Balun Reference Design (Version A0) at 2440 MHz. The Typical number indicates one standard deviation above the mean, measured at room temperature (25 °C). The Min and Max numbers were measured over process corners at room temperature

| Parameter                                 | Conditions                                            | Min. | Тур.           | Max. | Unit |

|-------------------------------------------|-------------------------------------------------------|------|----------------|------|------|

| Maximum output power (boost mode)         | At highest power setting                              |      | 7              |      | dBm  |

| Maximum output power                      | At highest power setting                              | 0    | 3              |      | dBm  |

| Minimum output power                      | At lowest power setting                               |      | -32            |      | dBm  |

| Error vector magnitude                    | As defined by IEEE 802.15.4, which sets a 35% maximum |      | 5              | 15   | %    |

| Carrier frequency error                   |                                                       | -40  |                | +40  | ppm  |

| Load impedance for optimum transmit power |                                                       |      | 200+j90<br>TBC |      | ?    |

| PSD mask relative                         | 3.5 MHz away                                          | -20  |                |      | dB   |

| PSD mask absolute                         | 3.5 MHz away                                          | -30  |                |      | dBm  |

Table 12. Transmit characteristics

## 2.7.3 Synthesizer

Table 13 lists the key parameters of the integrated synthesizer on the STM32W.

Table 13.

Synthesizer characteristics

| Parameter                     | Conditions                                                                                 | Min. | Тур. | Max. | Unit   |

|-------------------------------|--------------------------------------------------------------------------------------------|------|------|------|--------|

| Frequency range               |                                                                                            | 2400 |      | 2500 | MHz    |

| Frequency resolution          |                                                                                            |      | 11.7 |      | kHz    |

| Lock time                     | From off, with correct VCO DAC setting                                                     |      |      | 100  | μs     |

| Relock time                   | Channel change or RX/TX<br>turnaround (IEEE 802.15.4<br>defines 192 µs turnaround<br>time) |      |      | 100  | μs     |

| Phase noise at 100 kHz offset |                                                                                            |      | -71  |      | dBc/Hz |

| Phase noise at 1 MHz offset   |                                                                                            |      | -91  |      | dBc/Hz |

| Phase noise at 4 MHz offset   |                                                                                            |      | -103 |      | dBc/Hz |

| Phase noise at 10 MHz offset  |                                                                                            |      | -111 |      | dBc/Hz |

# **3** Package characteristics

### 3.1 Package mechanical data

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK<sup>®</sup> is an ST trademark.

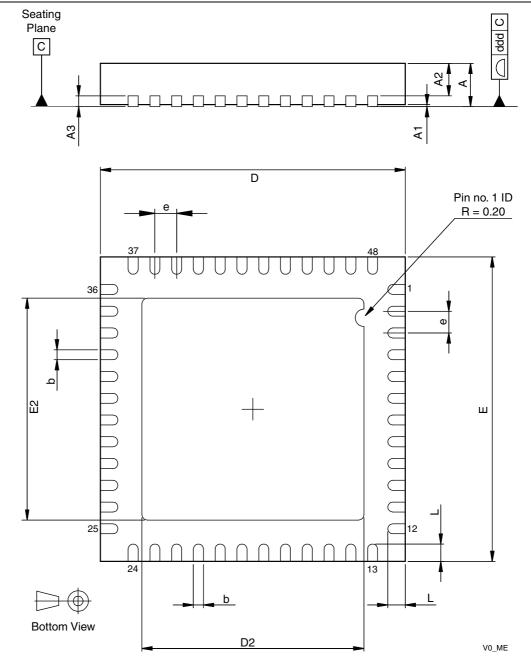

Figure 6. VFQFPN48 7x7mm package outline

57

| able 14. |             |       | age meenan | ical uata |                       |        |

|----------|-------------|-------|------------|-----------|-----------------------|--------|

| O h l    | Millimeters |       |            |           | Inches <sup>(1)</sup> |        |

| Symbol   | Min.        | Тур.  | Max.       | Min.      | Тур.                  | Max.   |

| Α        | 0.800       | 0.900 | 1.000      | 0.0315    | 0.0354                | 0.0394 |

| A1       |             | 0.020 | 0.050      |           | 0.0008                | 0.0020 |

| A2       |             | 0.650 | 1.000      |           | 0.0256                | 0.0394 |

| A3       |             | 0.250 |            |           | 0.0098                |        |

| b        | 0.180       | 0.230 | 0.300      | 0.0071    | 0.0091                | 0.0118 |

| D        | 6.850       | 7.000 | 7.150      | 0.2697    | 0.2756                | 0.2815 |

| D2       | 2.250       | 4.700 | 5.250      | 0.0886    | 0.1850                | 0.2067 |

| E        | 6.850       | 7.000 | 7.150      | 0.2697    | 0.2756                | 0.2815 |

| E2       | 2.250       | 4.700 | 5.250      | 0.0886    | 0.1850                | 0.2067 |

| е        | 0.450       | 0.500 | 0.550      | 0.0177    | 0.0197                | 0.0217 |

| L        | 0.300       | 0.400 | 0.500      | 0.0118    | 0.0157                | 0.0197 |

| ddd      |             |       | 0.080      |           |                       | 0.0031 |

### Table 14. VFQFPN48 7x7mm package mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

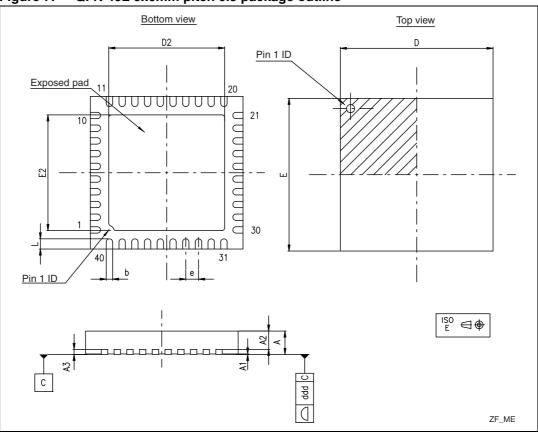

Figure 7. QFN 40L 6x6mm pitch 0.5 package outline

| Symbol | millimeters inches <sup>(1)</sup> |       |       |        |        |        |

|--------|-----------------------------------|-------|-------|--------|--------|--------|

| Symbol | Min Typ Max                       |       | Min   | Тур    | Max    |        |

| Α      | 0.800                             | 0.900 | 1.000 | 0.0315 | 0.0354 | 0.0394 |

| A1     |                                   | 0.020 | 0.050 |        | 0.0008 | 0.0020 |

| A2     |                                   | 0.720 | 1.070 |        | 0.0283 | 0.0421 |

| A3     |                                   | 0.200 |       |        | 0.0079 |        |

| b      | 0.180                             | 0.250 | 0.300 | 0.0071 | 0.0098 | 0.0118 |

| D      | 5.900                             | 6.000 | 6.100 | 0.2323 | 0.2362 | 0.2402 |

| D2     | 4.500                             | 4.550 | 4.700 | 0.1772 | 0.1791 | 0.1850 |

| E      |                                   | 6.000 |       |        | 0.2362 |        |

| E2     | 4.500                             | 4.550 | 4.700 | 0.1772 | 0.1791 | 0.1850 |

| е      |                                   | 0.500 |       |        | 0.0197 |        |

| L      | 0.350                             | 0.400 | 0.450 | 0.0138 | 0.0157 | 0.0177 |

| ddd    |                                   |       | 0.080 |        |        | 0.0031 |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

# 4 Ordering information scheme

| Example:                                 | STM32 | W | 108 | С | В | U | 6 | x |

|------------------------------------------|-------|---|-----|---|---|---|---|---|

| Device family                            |       |   |     |   |   |   |   |   |

| STM32 = ARM-based 32-bit microcontroller |       |   |     |   |   |   |   |   |

| Product type                             |       |   |     |   |   |   |   |   |

| W = wireless system-on-chip              |       |   |     |   |   |   |   |   |

| Sub-family                               |       |   |     |   |   |   |   |   |

| 108 = IEEE 802.15.4 specification        |       |   | ]   |   |   |   |   |   |

| Pin count                                |       |   |     |   |   |   |   |   |

| H = 40  pins                             |       |   |     |   |   |   |   |   |

| C = 48 pins                              |       |   |     |   |   |   |   |   |

| Code size                                |       |   |     |   |   |   |   |   |

| B = 128 Kbytes                           |       |   |     |   |   |   |   |   |

| Package                                  |       |   |     |   |   |   |   |   |

| U = QFN                                  |       |   |     |   |   |   |   |   |

| Temperature range                        |       |   |     |   |   |   |   |   |

| 6 = -40 °C to +85 °C                     |       |   |     |   |   |   | I |   |

| Firmware version                         |       |   |     |   |   |   |   |   |

| "Blank" = Open platform                  |       |   |     |   |   |   |   |   |

"Blank" = Open platform 1 = Ember ZigBee stack

2 = ST ZigBee stack

3 = RF4CE stack

4 = IEEE 802.15.4 media access control

For a list of available options (speed, package, etc.) or for further information on any aspect of this device, please contact your nearest ST sales office.

# 5 Revision history

#### Table 16. Document revision history

| Date        | Revision | Changes          |

|-------------|----------|------------------|

| 20-Aug-2009 | 1        | Initial release. |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2009 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

Doc ID 15851 Rev 1