# L9659

## Octal squib driver ASIC for safety application

## Features

- 8 deployment drivers with SPI selectable firing current and times

- Capability to deploy the squib with 1.2 A (min)/2 ms, 1.75 A (min)/1.0 ms and 1.75 A (min)/0.65 ms between VRES of 7 V to 37 V

- Capability to deploy the squib with 1.5 A (min)/2 ms between VRES of 7 V to 25 V

- Firing capability to deploy all channels simultaneously

- Independently controlled high-side and lowside MOS for diagnosis

- Analog output available for resistance measurement

- Squib short to ground, short to battery and MOS diagnostic available on SPI register

- Capability to deploy the squib the low side MOS is shorted to ground

- 4 fire enable inputs

- 5.5 MHz SPI interface

- Low voltage internal reset

- 2 kV ESD capability on all pins

- Package: LQFP64

#### Table 1.Device summary

- Technology: ST proprietary BCD5 (0.65 µm)

- RoHS compliant

## Description

The L9659 is intended to deploy up to 8 squibs. Squib drivers are sized to deploy 1.2 A minimum for 2 ms, 1.75 A minimum for 1 ms and 1.75 A minimum for 0.65 ms during load dump along with 1.5 A minimum for 2 ms for VRES voltages less than 25 V.

Full diagnostic capabilities of the squib interface are provided.

| Order code | Amb. temp range, °C | Package | Packing       |

|------------|---------------------|---------|---------------|

| L9659      | -40 to +95          | LQFP64  | Tray          |

| L9659TR    | -40 to +95          | LQFP64  | Tape and reel |

## Contents

| 1    | Bloc | k diagra  | am and pin description                                            | 5        |

|------|------|-----------|-------------------------------------------------------------------|----------|

|      | 1.1  | Block     | diagram                                                           | 5        |

|      | 1.2  | Pin de    | scription                                                         | 5        |

|      | 1.3  | Applica   | ation schematic                                                   | 8        |

| 2    | Elec | trical sp | pecifications                                                     | 9        |

|      | 2.1  | Absolu    | Ite maximum ratings                                               | 9        |

|      | 2.2  | Absolu    | Ite maximum degraded operating ratings                            | 10       |

|      | 2.3  | Opera     | ting ratings                                                      | 10       |

|      | 2.4  | Electri   | cal characteristics                                               | 11       |

|      |      | 2.4.1     | General                                                           | 11       |

|      |      | 2.4.2     | Electrical characteristics - Squib deployment drivers and diagnos | stics 12 |

|      |      | 2.4.3     | SPI timing                                                        | 17       |

| 3    | Fund | ctional o | description                                                       | 19       |

|      | 3.1  | Overvi    | ew                                                                | 19       |

|      | 3.2  | Gener     | al functions                                                      | 19       |

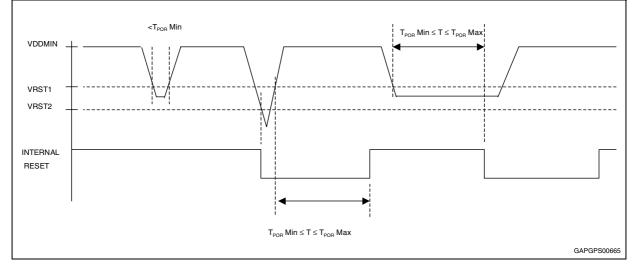

|      |      | 3.2.1     | Power on reset (POR)                                              | 19       |

|      |      | 3.2.2     | RESETB                                                            | 19       |

|      |      | 3.2.3     | Reference resistor                                                | 20       |

|      |      | 3.2.4     | Loss of ground                                                    | 20       |

|      |      | 3.2.5     | VRESx capacitance                                                 | 20       |

|      |      | 3.2.6     | Supply voltages                                                   | 20       |

|      |      | 3.2.7     | Ground connections                                                |          |

|      | 3.3  | Serial    | peripheral interface (SPI)                                        | 21       |

|      |      | 3.3.1     | SPI pin descriptions                                              | 21       |

|      | 3.4  | Squib     | drivers                                                           | 22       |

|      |      | 3.4.1     | Firing                                                            | 22       |

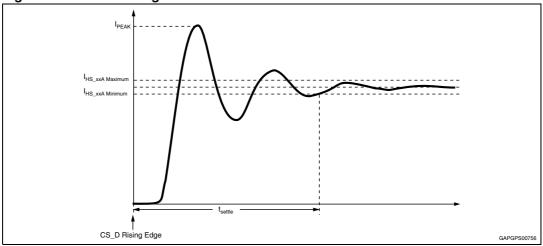

|      |      | 3.4.2     | Firing current measurement                                        | 25       |

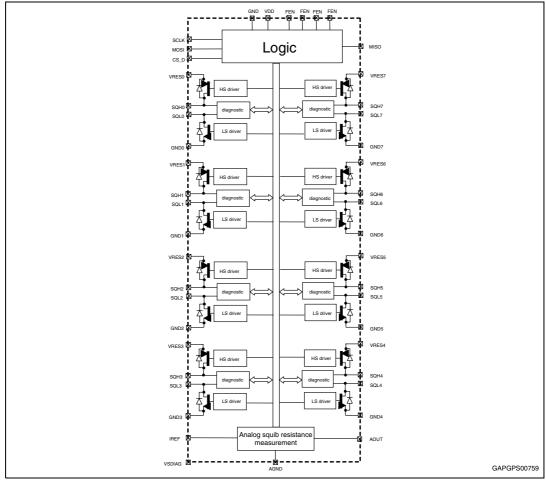

|      |      | 3.4.3     | Fire enable (FEN) function description                            | 26       |

|      |      | 3.4.4     | Squib diagnostics                                                 | 27       |

|      |      | 3.4.5     | SPI register definition for squib functions                       | 31       |

| 4    | Pack | cage inf  | ormation                                                          | 49       |

| 5    | Revi | sion his  | story                                                             | 50       |

| 2/51 |      |           | Doc ID 022048 Rev 1                                               |          |

| 2/01 |      |           |                                                                   |          |

## List of tables

| Device summary                                                           | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin description                                                          | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Absolute maximum ratings                                                 | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Absolute maximum degraded operating ratings                              | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Squib deployment drivers and diagnostics - DC electrical characteristics | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Features that are accessed/controlled for the SPI                        | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| •                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Diagnostic mode 3 VRESx selection                                        | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Command description summary                                              | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| •                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Deployment mode 2 bit definition                                         | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| •                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Diagnostic mode LS FET selection.                                        | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| •                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Diagnostic mode VRESx selection                                          | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| DEPLOY_STATUSx flag and the DEPLOY_SUCCESSx flag conditions              | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| MOSI monitor mode 2 Bit definition                                       | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Document revision history                                                | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                          | Device summary.<br>Pin description .<br>Absolute maximum ratings .<br>Absolute maximum degraded operating ratings .<br>Operating ratings .<br>General - DC electrical characteristics .<br>Squib deployment drivers and diagnostics - DC electrical characteristics .<br>Squib deployment drivers and diagnostics - DC electrical characteristics .<br>SPI timing - DC electrical characteristics .<br>Features that are accessed/controlled for the SPI .<br>SPI MOSI/MISO response .<br>How faults shall be interpreted .<br>Diagnostic Mode HSS selection .<br>Diagnostic mode 3 VRESx selection .<br>MISO responses to various events .<br>Command description summary .<br>Configuration mode 1 .<br>Configuration mode 2 .<br>Deployment mode 2 bit definition .<br>Diagnostic mode LS FET selection .<br>Diagnostic mode HSS selection .<br>Diagnostic mode J bit definition .<br>DEPLOY_STATUSx flag and the DEPLOY_SUCCESSx flag conditions.<br>MOSI monitor mode 2 bit definition .<br>MOSI monitor mode 3 bit definition .<br>Decument revision history .<br>Document revision history . |

# List of figures

| Figure 1.  | Block diagram                                 | 5 |

|------------|-----------------------------------------------|---|

| Figure 2.  | Application schematic                         | 3 |

| Figure 3.  | MOS settling time and turn-on time 2 16       | 3 |

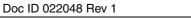

| Figure 4.  | SPI timing diagram                            | 3 |

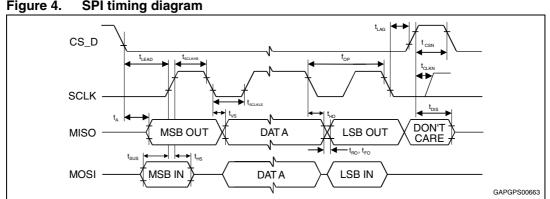

| Figure 5.  | MISO loading for disable time measurement     | 3 |

| Figure 6.  | POR timing                                    | 9 |

| Figure 7.  | Deployment drivers diagram                    | 3 |

| Figure 8.  | Driver activation timing diagram              | 4 |

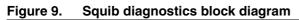

| Figure 9.  | Squib diagnostics block diagram               | 7 |

| Figure 10. | LQFP64 mechanical data and package dimensions | 9 |

## 1 Block diagram and pin description

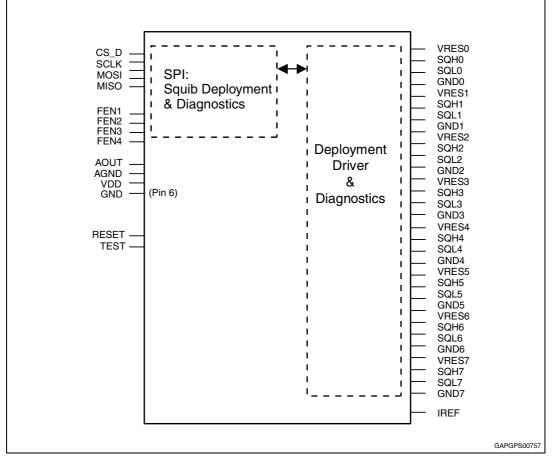

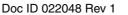

## 1.1 Block diagram

## Figure 1. Block diagram

## 1.2 Pin description

## Table 2.Pin description

| Pin # | Pin name | Description                      | I/O type | Reset state |

|-------|----------|----------------------------------|----------|-------------|

| 1     | MISO     | SPI data out                     | Output   | Hi-Z        |

| 2     | NC       | No connect                       | -        | -           |

| 3     | FEN1     | Fire enable for channels 0 and 1 | Input    | Pulldown    |

| 4     | FEN2     | Fire enable for channels 2 and 3 | Input    | Pulldown    |

| 5     | RESETB   | Reset pin                        | Input    | Pullup      |

| 6     | GND      | Ground (analog & digital)        | -        | -           |

| 7     | VDD      | VDD supply voltage               | Input    | -           |

| Pin # | Pin name | Description                              | I/O type | Reset state |

|-------|----------|------------------------------------------|----------|-------------|

| 8     | FEN3     | Fire enable for channels 4 and 5         | Input    | Pulldown    |

| 9     | FEN4     | Fire enable for channels 6 and 7         | Input    | Pulldown    |

| 10    | NC       | No connect                               | -        | -           |

| 11    | NC       | No connect                               | -        | -           |

| 12    | CS_D     | SPI chip select for deployment driver    | Input    | Pullup      |

| 13    | MOSI     | SPI data in                              | Input    | Hi-Z        |

| 14    | NC       | No connect                               | -        | -           |

| 15    | NC       | No connect                               | -        | -           |

| 16    | SCLK     | SPI clock                                | Input    | Hi-Z        |

| 17    | GND4     | Power ground for loop channel 4          | -        | -           |

| 18    | SQL4     | Low side driver output for channel 4     | Output   | Pulldown    |

| 19    | SQH4     | High side driver output for channel 4    | Output   | Hi-Z        |

| 20    | VRES4    | Reserve voltage for loop channel 4       | Input    | -           |

| 21    | VRES5    | Reserve voltage for loop channel 5       | Input    | -           |

| 22    | SQH5     | High side driver output for channel 5    | Output   | Hi-Z        |

| 23    | SQL5     | Low side driver output for channel 5     | Output   | Pulldown    |

| 24    | GND5     | Power ground for loop channel 5          | -        | -           |

| 25    | GND6     | Power ground for loop channel 6          | -        | -           |

| 26    | SQL6     | Low side driver output for channel 6     | Output   | Pulldown    |

| 27    | SQH6     | High side driver output for channel 6    | Output   | Hi-Z        |

| 28    | VRES6    | Reserve voltage for loop channel 6       | Input    | -           |

| 29    | VRES7    | Reserve voltage for loop channel 7       | Input    | -           |

| 30    | SQH7     | High side driver output for channel 7    | Output   | Hi-Z        |

| 31    | SQL7     | Low side driver output for channel 7     | Output   | Pulldown    |

| 32    | GND7     | Power ground for loop channel 7          | -        | -           |

| 33    | TEST     | Test pin                                 | Input    | Pulldown    |

| 34    | VSDIAG   | Supply for deployment driver diagnostics | Input    | -           |

| 35    | NC       | No connect                               | -        | -           |

| 36    | Reserved | Factory testmode output                  | -        | -           |

| 37    | Reserved | Factory testmode output                  | -        | -           |

| 38    | NC       | No connect                               | -        | -           |

| 39    | NC       | No connect                               | -        | -           |

| 40    | NC       | No connect                               | -        | -           |

| 41    | NC       | No connect                               | -        | -           |

| 42    | NC       | No connect                               | -        | -           |

Table 2.

Pin description (continued)

6/51

| Pin # | Pin name | Description                           | I/O type | Reset state |

|-------|----------|---------------------------------------|----------|-------------|

| 43    | NC       | No connect                            | -        | -           |

| 44    | NC       | No connect                            | -        | -           |

| 45    | NC       | No connect                            | -        | -           |

| 46    | IREF     | External current reference resistor   | Output   | -           |

| 47    | AGND     | Ground reference for AOUT             | -        | -           |

| 48    | AOUT     | Analog output for loop diagnostics    | Output   | Hi-Z        |

| 49    | GND3     | Power ground for loop channel 3       | -        | -           |

| 50    | SQL3     | Low side driver output for channel 3  | Output   | Pulldown    |

| 51    | SQH3     | High side driver output for channel 3 | Output   | Hi-Z        |

| 52    | VRES3    | Reserve voltage for loop channel 3    | Input    | -           |

| 53    | VRES2    | Reserve voltage for loop channel 2    | Input    | -           |

| 54    | SQH2     | High side driver output for channel 2 | Output   | Hi-Z        |

| 55    | SQL2     | Low side driver output for channel 2  | Output   | Pulldown    |

| 56    | GND2     | Power ground for loop channel 2       | -        | -           |

| 57    | GND1     | Power ground for loop channel 1       | -        | -           |

| 58    | SQL1     | Low side driver output for channel 1  | Output   | Pulldown    |

| 59    | SQH1     | High side driver output for channel 1 | Output   | Hi-Z        |

| 60    | VRES1    | Reserve voltage for loop channel 1    | Input    | -           |

| 61    | VRES0    | Reserve voltage for loop channel 0    | Input    | -           |

| 62    | SQH0     | High side driver output for channel 0 | Output   | Hi-Z        |

| 63    | SQL0     | Low side driver output for channel 0  | Output   | Pulldown    |

| 64    | GND0     | Power ground for loop channel 0       | -        | -           |

Table 2.Pin description (continued)

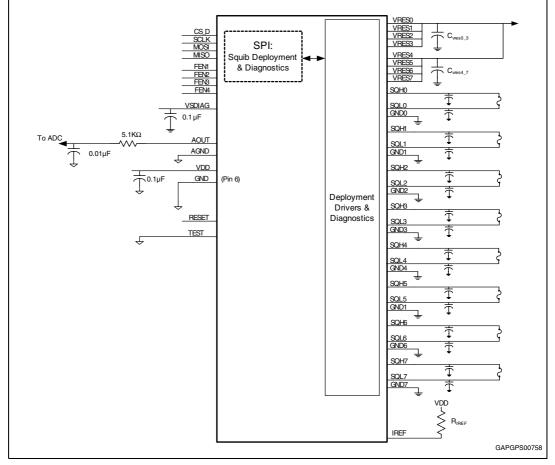

## 1.3 Application schematic

## 2 Electrical specifications

## 2.1 Absolute maximum ratings

The following maximum ratings are continuous absolute ratings; exceeding any one of these values may cause permanent damage to the integrated circuit.

Table 3.Absolute maximum ratings

| Symbol                         | Parameter                                                                                                             | Value                 | Unit            |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------|

| V <sub>DD</sub> <sup>(1)</sup> | Supply voltage                                                                                                        | - 0.3 to 5.5          | V               |

| V <sub>SDIAG</sub>             | Supply voltage for squib diagnostics                                                                                  | - 0.3 to 40           | V               |

| VRESx                          | VRES voltage (VRES0, VRES1, VRES2, VRES3, VRES4, VRES5, VRES6, VRES7)                                                 | - 0.3 to 40           | V               |

| SQHx                           | Squib high side drivers (SQH0, SQH1, SQH2, SQH3, SQH4, SQH5, SQH6, SQH7)                                              | - 0.6 to 40           | V               |

| SQLx                           | Squib low side drivers (SQL0, SQL1, SQL2, SQL3, SQL4, SQL5, SQL6, SQL7)                                               | - 0.3 to 40           | V               |

| TEST                           | Test pin                                                                                                              | -0.3 to 40            | V               |

| VI                             | Discrete input voltage (RESETB, CS_D, SCLK, MOSI,<br>FEN1, FEN2, FEN3, FEN4, IREF)                                    | - 0.3 to 5.5          | V               |

| Vo                             | Discrete output voltage (MISO, AOUT)                                                                                  | - 0.3 to 5.5          | V               |

| AGND                           | Analog output reference                                                                                               | -0.3 to 5.5           | V               |

| GNDx                           | Ground (GND0, GND1, GND2, GND3, GND4, GND5, GND6, GND7)                                                               | -0.3 to 5.5           | V               |

| T <sub>j</sub> <sup>(2)</sup>  | Maximum steady-state junction temperature                                                                             | 150                   | °C              |

| T <sub>amb</sub>               | Ambient temperature                                                                                                   | -40 to 95             | °C              |

| T <sub>stg</sub>               | Storage temperature                                                                                                   | -65 to 150            | °C              |

| R <sub>th j amb</sub>          | Thermal resistance junction to ambient (on FR-4 board)                                                                | 46                    | °C/W            |

|                                | naximum ratings are up to 48 hours; exceeding any one of these v<br>cause permanent damage to the integrated circuit. | alues for longer than | a total time of |

| V <sub>DD</sub>                | Supply voltage                                                                                                        | - 0.3 to 6.0          | V               |

| VI                             | Discrete input voltage (RESETB, CS_D, SCLK, MOSI,<br>FEN1, FEN2, FEN3, FEN4, IREF)                                    | - 0.3 to 6.0          | V               |

| V <sub>O</sub>                 | Discrete output voltage (MISO, AOUT)                                                                                  | - 0.3 to 6.0          | V               |

| AGND                           | Analog output reference                                                                                               | -0.3 to 6.0           | V               |

| GNDx                           | Ground (GND0, GND1, GND2, GND3, GND4, GND5, GND6, GND7)                                                               | -0.3 to 6.0           | V               |

| T <sub>j</sub> <sup>(2)</sup>  | Maximum steady-state junction temperature                                                                             | 150                   | °C              |

| Tamb                           | Ambient temperature                                                                                                   | -40 to 95             | °C              |

| T <sub>stg</sub>               | Storage temperature                                                                                                   | -65 to 150            | °C              |

| R <sub>th j amb</sub>          | Thermal resistance junction to ambient (on FR-4 board)                                                                | 46                    | °C/W            |

1. Exceeding a  $V_{\text{DD}}$  of 5.1V during a deployment may cause damage

2. To allow for deployment the maximum steady state junction temperature cannot exceed 130°C. Under the operating ratings defined in section 2.3 the steady state junction temperature will not exceed 130°C.

## 2.2 Absolute maximum degraded operating ratings

Under the following deviations to the ratings indicated in *Section 2.3* the L9659 performance will be degraded and not meet the electrical characteristics outlined in *Section 2.4*. At minimum the SPI and diagnostics will function but not meet specified electrical parameters.

| Symbol             | Parameter                                                                              | Value               | Unit |

|--------------------|----------------------------------------------------------------------------------------|---------------------|------|

| $V_{DD}$           | Supply voltage                                                                         | 4.5 to 5.5          | V    |

| V <sub>SDIAG</sub> | Supply voltage for squib diagnostics                                                   | 7 to 40             | V    |

| V <sub>RES</sub>   | VRES voltage (VRES0, VRES1, VRES2, VRES3, VRES4, VRES5, VRES6, VRES7)                  | 7 to 40             | V    |

| VI                 | Discrete input voltage (RESETB, DEPEN, CS_D, SCLK, MOSI, FEN1, FEN2, FEN3, FEN4, IREF) | - 0.3 to (VDD +0.3) | V    |

| V <sub>O</sub>     | Discrete output voltage (MISO, AOUT)                                                   | -0.3 to (VDD + 0.3) | V    |

| Тj                 | Junction temperature                                                                   | -40 to 150          | °C   |

| Table 4. | Absolute maximum degraded operating ratings |

|----------|---------------------------------------------|

|          | Absolute maximum degraded operating ratings |

Note: The above is provided for informational purposes only and will result in degraded operation. Under the above conditions the SPI will be functional as well as diagnostics, though the electrical performance may not conform to the parameters outlined in Section 2.4. Firing requirements as indicated in Section 2.4 may not be met with the conditions above.

## 2.3 Operating ratings

#### Table 5.Operating ratings

| Symbol                | Parameter                                                                       | Value                           | Unit |

|-----------------------|---------------------------------------------------------------------------------|---------------------------------|------|

| V <sub>DD</sub>       | Supply voltage                                                                  | 4.9 to 5.1                      | V    |

| V <sub>SDIAG</sub>    | Supply voltage for squib diagnostics                                            | 7 to 37                         | V    |

| V <sub>RESx</sub>     | VRES voltage (VRES0, VRES1, VRES2, VRES3, VRES4, VRES5, VRES6, VRES7)           | 7 to 37                         | V    |

| VI                    | Discrete input voltage (RESETB, CS_D, SCLK, MOSI, FEN1, FEN2, FEN3, FEN4, IREF) | - 0.3 to (V <sub>DD</sub> +0.3) | V    |

| V <sub>O</sub>        | Discrete output voltage (MISO, AOUT)                                            | -0.3 to (VDD + 0.3)             | V    |

| T <sub>amb</sub>      | Ambient temperature                                                             | -40 to 95                       | °C   |

| R <sub>Th j-amb</sub> | Thermal resistance junction to ambient (on FR-4 board)                          | 46                              | °C/W |

### Comments:

VSDIAG supply will provide power for squib resistance and HSS diagnostics

VDD will be used for all internal functions as well as short to battery/ground and high squib resistance diagnostics.

## 2.4 Electrical characteristics

## 2.4.1 General

$\begin{array}{l} 4.9 \ V \leq V_{DD} \leq 5.1 \ V; \ 7 \ V \leq V_{RESX} \leq 37 \ V; \ 7 \ V \leq V_{SDIAG} \leq 37 \ V; \ FEN1 = FEN2 = FEN3 = \\ FEN4 = V_{DD}; \ R\_REF = 10 \ k\Omega, \ \pm 1 \ \%, \ 100 \ PPM; \ -40 \ ^\circ C \leq T_A \leq +95 \ ^\circ C; \ unless \ other \ specified. \end{array}$

Table 6.

General - DC electrical characteristics

| Symbol                         | Parameter                                                                 | Test condition                                                                       | Min. | Тур. | Max. | Unit        |

|--------------------------------|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------|------|------|------|-------------|

| Osc                            | Internal oscillator<br>frequency                                          | Tested with 10K , 1%, 100ppm Iref resistor                                           | 4.75 | -    | 5.25 | MHz         |

| V <sub>RST1</sub>              | Internal voltage reset VDD<br>after de-glitch time (tpor)<br>See Figure 7 | VDD level for L9659 to report reset<br>condition -deployment drivers are<br>disabled | 4.0  | -    | 4.5  | v           |

| V <sub>RST2</sub>              | Internal voltage reset VDD with no de-glitch time See                     | Guaranteed by design                                                                 | 2.1  | -    | 3.0  |             |

| t <sub>POR</sub>               | POR De-glitch timer                                                       | Timer for VRST1                                                                      | 5    | -    | 25   | μs          |

|                                |                                                                           | No squib diagnostics. No deployment.                                                 | -    | -    | 15   | 17 mA<br>35 |

| I <sub>DD</sub>                | Input current VDD                                                         | Resistance measurement diagnostics with no fault condition present.                  | -    | -    | 17   |             |

|                                |                                                                           | Short to -0.3V on SQL; VRCM active                                                   | -    | -    | 35   |             |

|                                |                                                                           | During deployment                                                                    | -    | -    | 15   |             |

| R <sub>IREF_H</sub>            | Resistance threshold IREF                                                 | -                                                                                    | -    | -    | 60.0 | kΩ          |

| R <sub>IREF_L</sub>            |                                                                           | -                                                                                    | 2.0  | -    | -    | kΩ          |

| $V_{\text{IH}\_\text{RESETB}}$ |                                                                           | -                                                                                    | -    | -    | 2.0  | V           |

| $V_{IL\_RESETB}$               | Input voltage threshold<br>RESETB                                         | -                                                                                    | 0.8  | -    | -    | V           |

| V <sub>HYS_RST</sub>           |                                                                           | -                                                                                    | 100  | -    | 300  | mV          |

| V <sub>IH_TEST</sub>           | Input voltage threshold<br>TEST                                           | Guaranteed by design                                                                 | -    | 3.2  | -    | v           |