### Four channel valve driver

Data brief

### **Features**

- Four low-side output drivers with protection diagnostic

- 2 PWM controlled channels (0.2  $\Omega$  typ.)

- 2 current controlled channels with 6 % accuracy (0.3  $\Omega$  typ.)

- All outputs with 35 V zener clamp

- Programmable channel timer

- Clock monitor

- Integrated recirculation diodes

- Serial peripheral interface with 16 bits, up to 5 MHz with diagnosis

- Battery compatible supply voltage

- Detailed load diagnosis

- Overload protection

- Open load

- Undercurrent

- Undervoltage

- Temperature warning and shutdown

- Power or signal GND loss

- Freewheeling diode loss

- Silent valve driver test

## **Description**

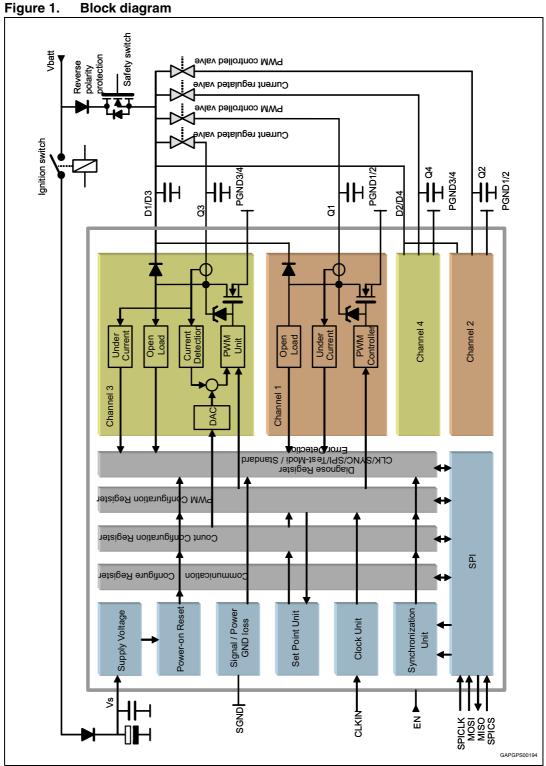

The L9374 is a four channel low side driver with integrated recirculation diodes. The switching of the channels is programmable via a SPI (serial peripheral interface). The main time base is given by an external clock via CLKin. The clock unit monitors this external clock and provides the system clock for all timings.

A synchronization unit is used to monitor the SPI communication and provides a sync signal for the channel activation.

The output duty cycle for each channel can be programmed individually and will be activated by the set point unit. Is possible to program two output duty cycles per channel with a block of 16 SPI commands as well as an individual duration

time for each channel actuation. Both information are stored in the PWM and in the counter configuration register respectively.

The PWM controller translates the programmed digital duty cycle value in a PWM signal which controls the output.

For the current controlled channels the target current value is programmed. It is also possible to program two different target currents. The target current is compared with the real load current. The output duty cycle is then calculated with an arithmetic logic unit. As base for the calculation a load model is used respecting the resistivity of the load, the supply voltage as well as the internal recirculation path. To check the plausibility of the current controller all measured and calculated values are available and accessible via SPI.

All channels are equipped with a load diagnostic. This allows to detect an open load in off condition as well as an under current in on condition. The power stage is protected against over current and over temperature. A weak connection in power ground or in the recirculation path is monitored. All monitored functions can be read out in a serial diagnostic protocol dedicated for each channel via SPI.

Table 1. Device summary

| Order code | Package    | Packing       |

|------------|------------|---------------|

| L9374LF    | PowerSO-36 | Tube          |

| L9374TRLF  | PowerSO-36 | Tape and reel |

L9374 **Block diagram**

#### **Block diagram** 1

L9374 Pins description

# 2 Pins description

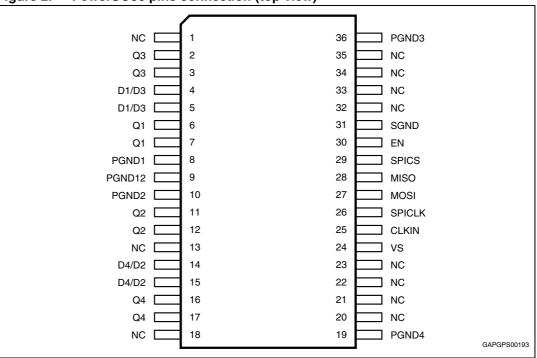

Figure 2. PowerSO36 pins connection (top view)

Table 2. Pins description

| Pin # | PwSO36 | Description                             |

|-------|--------|-----------------------------------------|

| 1     | PGND   | Not connected/Power ground.             |

| 2     | Q3     | Output.                                 |

| 3     | Q3     | Output.                                 |

| 4     | D1/D3  | Free wheeling diode.                    |

| 5     | D1/D3  | Free wheeling diode.                    |

| 6     | Q1     | Output.                                 |

| 7     | Q1     | Output.                                 |

| 8     | PGND1  | Power ground of the output driver 1& 2. |

| 9     | PGND12 | Power ground of the output driver 1& 2. |

| 10    | PGND2  | Power ground of the output driver 1& 2. |

| 11    | Q2     | Output.                                 |

| 12    | Q2     | Output.                                 |

| 13    | N.C.   | Not connected.                          |

| 14    | D4/D2  | Free wheeling diode.                    |

| 15    | D4/D2  | Free wheeling diode.                    |

| 16    | Q4     | Output.                                 |

Pins description L9374

Table 2. Pins description (continued)

| Pin # | PwSO36 | Description                                |

|-------|--------|--------------------------------------------|

| 17    | Q4     | Output.                                    |

| 18    | PGND   | Not connected/Power ground.                |

| 19    | PGND4  | Power ground of the output driver 4.       |

| 20    | N.C.   | Not connected.                             |

| 21    | N.C.   | Not connected.                             |

| 22    | N.C.   | Not connected.                             |

| 23    | N.C.   | Not connected.                             |

| 24    | VS     | Supply pin.                                |

| 25    | CLKIN  | Input for precise clock.                   |

| 26    | SPICLK | SPI communication clock.                   |

| 27    | MOSI   | Master Out Slave In for SPI communication. |

| 28    | MISO   | Master In Slave Out for SPI communication. |

| 29    | SPICS  | SPI chip select.                           |

| 30    | EN     | Enable.                                    |

| 31    | SGND   | Signal ground.                             |

| 32    | N.C.   | Not connected.                             |

| 33    | N.C.   | Not connected.                             |

| 34    | N.C.   | Not connected.                             |

| 35    | N.C.   | Not connected.                             |

| 36    | PGND3  | Power ground of the output driver 3.       |

#### 3 **Absolute maximum ratings**

Table 3. **Absolute maximum ratings**

| Symbol                                                                                                        | Parameter                                                                                                          | Min        | Max        | Unit |

|---------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|------------|------------|------|

| V <sub>s</sub>                                                                                                | Supply voltage                                                                                                     | -0.3       | 38         | V    |

| V <sub>Dx</sub>                                                                                               | Freewheeling diode voltage                                                                                         | -0.3       | 35         | V    |

| V <sub>Qx</sub>                                                                                               | Output voltage                                                                                                     | -0.3       | 35         | V    |

| V <sub>EN</sub> V <sub>SPICLK</sub> V <sub>SPICS</sub> V <sub>MOSI</sub> V <sub>MISO</sub> V <sub>CLKIN</sub> | Enable voltage SPI clock voltage SPI chip select voltage SPI MOSI voltage SPI MISO voltage SPI clock input voltage | -0.3       | 6          | V    |

| I <sub>Q1; 2</sub>                                                                                            | Output current at reversal voltage                                                                                 |            | -4         | А    |

| I <sub>Q3; 4</sub>                                                                                            | Output current at reversal voltage                                                                                 |            | -2         | Α    |

| I <sub>EN_CL</sub> I <sub>SPICLK_CL</sub> I <sub>SPICS_CL</sub> I <sub>MOSI_CL</sub> I <sub>CLKIN_CL</sub>    | Input clamping currents (static) Input clamping currents (dynamic)                                                 | - 3<br>-10 | + 3<br>+10 | mA   |

Definition:

Current from outside into the L9374-> " + "

Current from L9374 towards external components -> " - "

Transients beyond this limit will cause currents into ESD Warning:

structures which must be limited externally to ±10 mA

(maximum energy to be dissipated: 2 mJ).

ESD susceptibility

# 4 ESD susceptibility

## 4.1 HBM

ESD susceptibility HBM according to EIA/JESD 22-A 114B otherwise defined.

Table 4. HBM

| Pin                                           | Condition                                                  | Min | Max | Unit |

|-----------------------------------------------|------------------------------------------------------------|-----|-----|------|

| All Pins                                      | -                                                          | ± 2 | -   | kV   |

| Output pins D <sub>X</sub> ; Q <sub>X</sub> ; | PGND12, PGND3, PGND4, LGND and GND are connected together. | ± 4 | -   | kV   |

## 4.2 MM

ESD susceptibility according to EIA/JESD22-A115-A

Table 5. MM

| Parameter          | Condition | Min   | Max | Unit |

|--------------------|-----------|-------|-----|------|

| Machine model (MM) | All pins  | ± 250 | -   | V    |

L9374 Package information

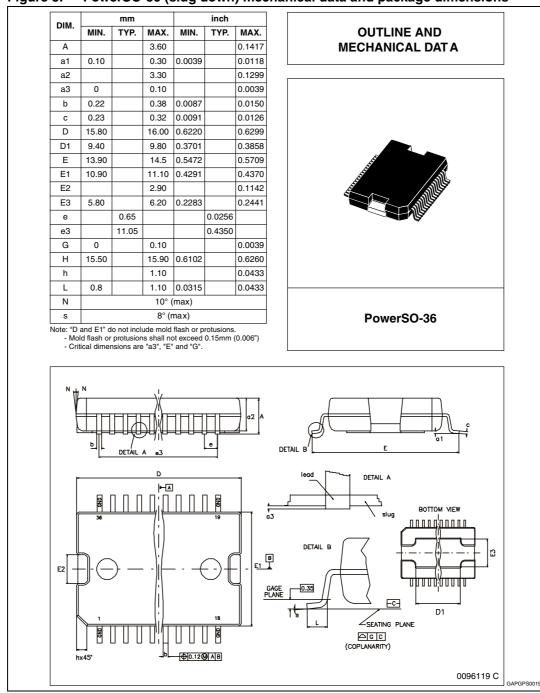

## 5 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: <u>www.st.com</u>.

$\mathsf{ECOPACK}^{\mathbb{R}}$  is an ST trademark.

Figure 3. PowerSO-36 (slug down) mechanical data and package dimensions

Revision history L9374

# 6 Revision history

Table 6. Document revision history

| Date        | Revision | Changes                                                                                                                                                                            |

|-------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 04-Jun-2007 | 1        | Initial release.                                                                                                                                                                   |

| 31-Jul-2007 | 2        | Updated Section 1: Block diagram, Section 2: Pins description and Section 4: ESD susceptibility.                                                                                   |

| 20-May-2009 | 3        | Updated Figure 5: PowerSSO-36 (exposed pad) mechanical data and package dimensions on page 8.                                                                                      |

| 18-Mar-2011 | 4        | Modified <i>Table 1: Device summary</i> .  Removed all references to PowerSSO-36 package.  Modified <i>Section 2: Pins description</i> and <i>Section 5: Package information</i> . |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2011 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com