# AN3258 Application note

STM8A/S HSI oscillator calibration using LIN automatic resynchronization

### Introduction

Local interconnect network (LIN) is a widely used standard for communication between various nodes present inside the electronic control unit (ECU) of a vehicle. LIN sync frame, which is defined by LIN standard, is used as a reference by the LIN slave nodes for clock synchronization. Using this technique, LIN slave nodes can calibrate the variable internal RC oscillator and use it as the system clock source. Therefore, the LIN slave node application can save the cost of using crystal or resonator oscillators.

This application note describes a method to calibrate the STM8A/S high-speed internal (HSI) oscillator using the LIN automatic resynchronization feature of the LINUART/UART1 peripheral. The calibration method is also provided with a software routine. It can be downloaded from <a href="https://www.st.com">www.st.com</a>.

The user must be familiar with the LIN bus standard, STM8A/S microcontroller architecture, and the basics of C language. Detailed information about the STM8A/S microcontroller peripheral features, hardware registers, and electrical characteristics are available in the STM8A (RM0009) and STM8S (RM0016) reference manuals and the product datasheets.

October 2010 Doc ID 17825 Rev 1 1/16

Contents AN3258

# **Contents**

| Introdu | ction |                                   |

|---------|-------|-----------------------------------|

| 1       | HSI   | calibration                       |

|         | 1.1   | HSI trimming bits 5               |

|         | 1.2   | LIN automatic resynchronization 6 |

|         | 1.3   | HSI calibration method            |

|         | 1.4   | HSI calibration routine 9         |

|         | 1.5   | LIN header error handling11       |

|         | 1.6   | LIN divider update method         |

|         | 1.7   | LIN clock deviation               |

| 2       | Con   | clusion                           |

| 3       | Revi  | sion history                      |

AN3258 List of tables

# List of tables

| Table 1. | CLK_HSITRIMR values and binary two's complement representation | 6 |

|----------|----------------------------------------------------------------|---|

| Table 2. | Document revision history                                      | 5 |

List of figures AN3258

# **List of figures**

| Figure 1. | STM8A/S HSI trimming principle           | 5 |

|-----------|------------------------------------------|---|

|           | LIN header                               |   |

|           | LIN synch field measurement              |   |

| Figure 4. | HSI calibration routine flowchart        | 0 |

| Figure 5. | LDIV read/write operations when LDUM = 0 | 2 |

| Figure 6. | LDIV read/write operations when LDUM = 1 | 2 |

### 1 HSI calibration

## 1.1 HSI trimming bits

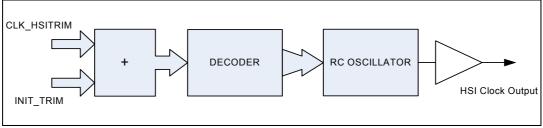

STM8A/S microcontrollers have an HSI oscillator with a nominal frequency ( $f_{HSI}$ ) of 16 MHz which is factory calibrated at an ambient temperature ( $T_A$ ) of 25 °C and a supply voltage ( $V_{CC}$ ) of 5 V. The accuracy for overall temperature and voltage range is ±5 % (please refer to the device specific datasheet) which is sufficient for many applications. For a given voltage and temperature condition, the HSI oscillator frequency can be calibrated to ±1 % or ±0.5 % by using calibration bits as described below and in *Figure 1*.

After a device reset, the factory calibration value at  $T_A = 25$  °C and  $V_{CC} = 5$  V is automatically loaded into the internal calibration register. The HSI frequency can be fine-tuned by writing the calibration bits present in the HSI clock calibration trimming register ( $CLK\_HSITRIMR$ ). The maximum number of calibration bits present is either three or four depending on the device. The calibration bits provide an additional trimming value which is added to the factory calibration value to fine-tune the HSI output frequency. The additional trimming value, written in the trimming bits, is interpreted as a signed value with two's complement representation ( $see\ Table\ 1$ ). In the case of three trimming bits, this additional trimming value can vary from -4 (100b) to 3 (011b) and in the case of four trimming bits, this additional trimming value varies from -7 (1001b) to 7 (0111b). Thus, the additional trimming value can be added or subtracted to the factory calibration value. An increase in the trimming value causes a decrease in the HSI frequency. The frequency change per step is  $\pm 1$  % or  $\pm 0.5$  % depending on the device and number of trimming bits used (three or four). Some devices can use either three or four trimming bits which are programmable via the HSITRIM option byte.

Figure 1. STM8A/S HSI trimming principle

Table 1. CLK\_HSITRIMR values and binary two's complement representation

| 3-bit trimming value |                               | 4-bit            | trimming value                |

|----------------------|-------------------------------|------------------|-------------------------------|

| Decimal value        | Binary two's complement value | Decimal<br>value | Binary two's complement value |

| 3                    | 011b                          | 7                | 0111b                         |

| 2                    | 010b                          | 6                | 0110b                         |

| 1                    | 001b                          | 5                | 0101b                         |

| 0                    | 000b                          | 4                | 0100b                         |

| -1                   | 111b                          | 3                | 0011b                         |

| -2                   | 110b                          | 2                | 0010b                         |

| -3                   | 101b                          | 1                | 0001b                         |

| -4                   | 100b                          | 0                | 0000b                         |

|                      |                               | -1               | 1111b                         |

|                      |                               | -2               | 1110b                         |

|                      |                               | -3               | 1101b                         |

|                      |                               | -4               | 1100b                         |

|                      |                               | -5               | 1011b                         |

|                      |                               | -6               | 1010b                         |

|                      |                               | -7               | 1001b                         |

# 1.2 LIN automatic resynchronization

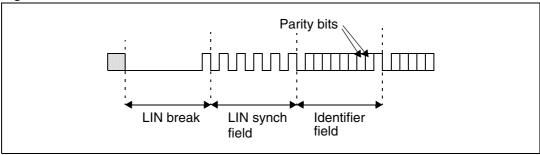

In the LIN standard, the master node initiates the communication by sending a LIN message header to the slave node. The LIN message header sent by the master node comprises three fields (see *Figure 2*):

- Break field

- Sync field

- Identifier field

- frame identifier

- parity

The break field is at least 13 nominal bit times the dominant value followed by a break delimiter. The sync field is a byte with a data value of 0x55. The identifier field consists of two subfields: the frame identifier and the parity. Bits 0 to 5 are frame identifier and bits 6 to 7 are the parity.

Figure 2. LIN header

Usually, the master node uses a crystal or resonator oscillator to generate the correct baud rate. The sync field byte is used by the slave node to synchronize with the master clock.

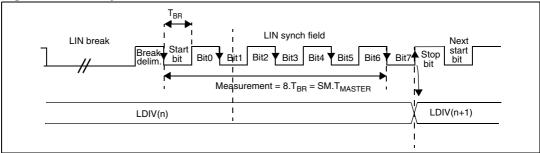

The STM8A/S LINUART peripheral has an automatic resynchronization feature which makes use of the sync byte field to synchronize with the master baud rate. The automatic resynchronization feature measures the sync byte field and automatically adjusts the slave baud rate generator after each LIN sync field reception from the master node (see *Figure 3*).

Figure 3. LIN synch field measurement

After each LIN break reception, the time duration between five falling edges on the LIN Rx pin is sampled on the  $f_{MASTER}$  clock. The result of this measurement is stored in an internal 19-bit register called SM which is not user accessible. Then, the LIN baud rate divider (LDIV) is automatically updated at the end of the fifth falling edge.

Note:

$f_{MASTER}$  and  $T_{MASTER}$  are the respective system clock frequency and time period of the STM8A/S slave node (please refer to the clock tree figure in the STM8A and STM8S reference manuals) and should not be considered as the frequency of the master node.

### 1.3 HSI calibration method

This section explains how to calibrate the HSI oscillator using the LIN automatic resynchronization feature described above. The automatic resynchronization feature updates the LIN baud rate divider (LDIV) after each LIN sync field reception. The calibration method uses the updated LDIV factor to calculate the HSI frequency variation, under current conditions, using the equations below.

#### **Equation 1**

$$f_{HSIDIV^{""}} = \frac{f_{HSI}}{HSIDIV}$$

Where,  $f_{HSI}$  = nominal HSI frequency of 16 MHz and HSIDIV is the HSI prescaler factor programmed in the CLK\_CKDIVR register.

The LIN baud rate is programmed by software after writing the LDIV\_NOM value into the BRR1 and BRR2 registers.

#### **Equation 2**

Baudrate =

$$\frac{f_{MASTER}}{LDIV_NOM}$$

As slave node uses the HSI clock as  $f_{MASTER}$ ,  $f_{MASTER} = f_{HSIDIV}$

#### **Equation 3**

$$LDIV\_NOM = \frac{f_{MASTER}}{Baudrate}$$

#### **Equation 4**

```

f_{MESASURED} = LDIV_MEAS \times Baudrate

```

After the LIN sync field reception, the LIN baud rate divider is measured by the automatic resynchronization (LDIV\_MEAS) and it is automatically loaded into the BRR1 and BRR2 registers. These actions keep the same baud rate under varying HSI oscillator frequency conditions. The LDIV\_MEAS factor multiplied by the baud rate gives the current HSI frequency (f<sub>MEASURED</sub>).

Where, LDIV\_MEAS = LDIV measured after automatic resynchronization.

The difference between the  $f_{\mbox{\scriptsize REFERENCE}}$  and  $f_{\mbox{\scriptsize MEASURED}}$  gives the variation of HSI oscillator frequency.

#### **Equation 5**

$$\Delta_{\text{FREQUENCY}} = f_{\text{MASTER}} - f_{\text{MEASURED}}$$

Where,  $\Delta_{FREQUENCY}$  is the HSI oscillator frequency variation.

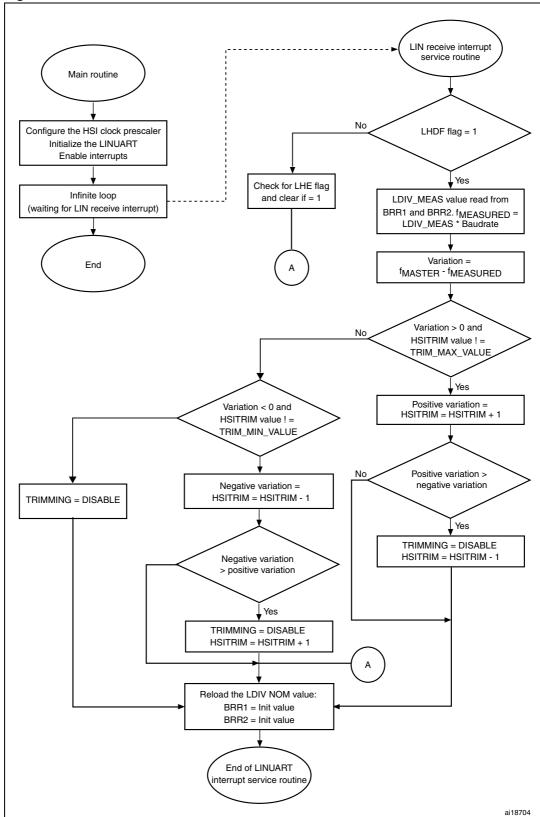

### 1.4 HSI calibration routine

The calibration routines are written in C language. They include STM8A/S firmware library functions.

The calibration routine starts with the configuration of the HSI clock prescaler value bits, HSIDIV[1:0], in the CLK\_CKDIVR register. The value programmed in the software example is HSIDIV[1:0] = 00 which means,  $f_{HSIDIV} = f_{HSI/1} = 16$  MHz. The HSI trimming bits, HSITRIM[3:0] or HSITRIM[2:0], in the CLK\_HSITRIMR register are kept at reset value.

The LINUART peripheral is initialized at baud rate 19200 bps, 8 data bits, 1 stop bit and no parity. LINUART is configured in slave mode (LSLV bit =1) with the automatic resynchronization feature enabled (LASE bit = 1) and the LIN divider update method (LDUM) bit = 0. Both LIN header detection(LHDIEN) and LIN receiver (RIEN) interrupts are enabled. The LINEN bit is set to enable the LIN mode.

When a valid LIN header is received by the LIN slave, the LIN receive interrupt is generated. Inside the interrupt service routine, if the LIN header detection flag (LHDF) is set, LDIV\_MEAS is read from the BRR1 and BRR2 registers (see *Figure 4*). Using *Equation 4*,  $f_{MEASURED}$  is calculated. The variation of the HSI oscillator frequency ( $\Delta_{FREQUENCY}$ ) is calculated by using *Equation 5*.

Depending on whether the  $\Delta_{\text{FREQUENCY}}$  is positive or negative, the trimming value (as described in *Section 1.1: HSI trimming bits*) is written to increase or decrease the HSI oscillator frequency by one trimming step. When the next sync frame is received, the procedure is repeated to check and calibrate the HSI oscillator until the trimming value reaches the upper/lower limit or until the measured  $\Delta_{\text{FREQUENCY}}$  is greater than the value measured with the previous trimming value. The maximum number of valid LIN headers required to calibrate the HSI oscillator is four if three trimming bits are used and eight if four trimming bits are used.

Figure 4. HSI calibration routine flowchart

# 1.5 LIN header error handling

It is possible that slave node receives an invalid LIN header or a LIN header with an error. In this case, the LIN header detection flag (LHDF) is not set and the corresponding LIN header detection interrupt does not occur but, the LIN header error (LHE) flag is set.

A LIN header error may occur under the following conditions:

- 1. The break delimiter is too short.

- 2. The sync field is not equal to 0x55 or the deviation error in the sync field is outside the LIN specification which allows a clock deviation of up to 14 % between the slave and master oscillators

- 3. The framing error occurs in the sync field or the identifier field.

- 4. A LIN header reception timeout occurs.

In the case of a LIN header error detection (LHE bit set), the LHE bit is cleared inside the interrupt service routine and the software waits for the new valid LIN header.

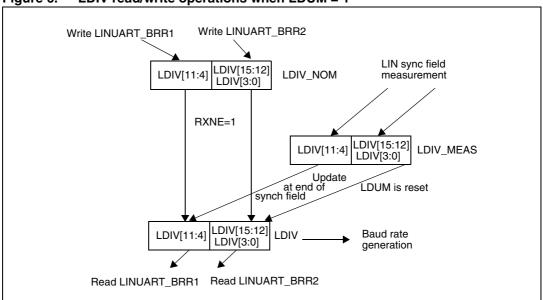

# 1.6 LIN divider update method

Three registers are managed internally by the LINUART/UART1 peripheral for the automatic update of the LIN divider (LDIV). They are:

- 1. LDIV\_NOM which stores the value written by software in the LINUART\_BRR1 and LINUART\_BRR2 registers.

- 2. LDIV\_MEAS which stores the value of the LIN sync field measurement.

- 3. LDIV which stores the value which is used to generate the baud rate.

The LDIV can be updated from the LDIV\_MEAS register after the LIN sync field measurement or from the LDIV\_NOM register after a software write in LINUART\_BRR1.

If LASE =1, the LDIV\_MEAS is loaded automatically into LDIV after each LIN sync field measurement. The loading from LDIV\_NOM into LDIV depends on the LDUM bit setting.

If LDUM = 1, the LDIV\_NOM value is loaded automatically into LDIV register at the end of character reception (RXNE =1).

If LDUM =0, the LDIV\_NOM value is loaded into LDIV after a software write into LINUART BRR1.

If the loading from LDIV\_MEAS and LDIV\_NOM into LDIV occurs at the same time, LDIV\_NOM has the priority.

In *Figure 5*, the software example has been implemented with (LDUM = 0). After the LIN reception of the LIN header interrupt and the execution of the calibration routine, the LDIV is loaded with LDIV\_NOM by writing the LINUART\_BRR1.

Write LINUART\_BRR1 Write LINUART\_BRR2 LIN sync field LDIV[15:2] LDIV[3:0] LDIV[11:4] LDIV NOM measurement Write LINUART\_BRR LDIV[15:12] LDIV[11:4] LDIV MEAS LDIV[3:0] Update at end of synch field LDIV[15:12] LDIV[7:0] Baud rate LDIV[3:0] generation Read LINUART\_BRR1 Read LINUART\_BRR2

Figure 5. LDIV read/write operations when LDUM = 0

In the case of LDUM = 1 (see *Figure 6*), the LDUM bit has to set by software before the LIN checksum reception. In this way, the LDIV\_NOM is loaded into LDIV at the end of character reception.

### 1.7 LIN clock deviation

LIN clock deviations may be caused by the following sources:

1. Deviation due to transmitter error (DTRA): The transmitter can be either a master or a slave (in the case of a slave listening to the response of another slave).

- 2. Error due to the LIN synch measurement performed by the receiver (DMEAS).

- 3. Error due to the baud rate quantization of the receiver (DQUANT).

- 4. Deviation of the local oscillator of the receiver (DREC): This deviation can occur during the reception of one complete LIN message assuming that the deviation was compensated at the beginning of the message.

- Deviation due to the transmission line (DTCL) which is generally due to the transceivers.

Total clock deviation = DTRA + DMEAS + DQUANT + DREC + DTCL

If the LINUART is to receive a character correctly, the total deviation should be <3.75 %. For more details, please refer to the STM8A (RM0009) and STM8S (RM0016) reference manuals.

Conclusion AN3258

# 2 Conclusion

The calibration method described in this application note allows the LIN slave nodes to calibrate and operate with the HSI internal oscillator (16 MHz) under variable temperature and voltage conditions.

AN3258 Revision history

# 3 Revision history

Table 2. Document revision history

| Date        | Revision | Changes         |

|-------------|----------|-----------------|

| 05-Oct-2010 | 1        | Initial release |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2010 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

16/16 Doc ID 17825 Rev 1