## Driver for double flash LED with I<sup>2</sup>C interface

#### Introduction

This application note is dedicated to the design of a flash LED driver using the STCF05 device, which is a boost current mode converter with an I<sup>2</sup>C interface and internal current source. The schematic, functional description, recommendations for PCB layout and external components selection are also discussed in this application note. The STCF05 device is designed to drive two LEDs in series with a total forward voltage from 5.3 V to 10.2 V.

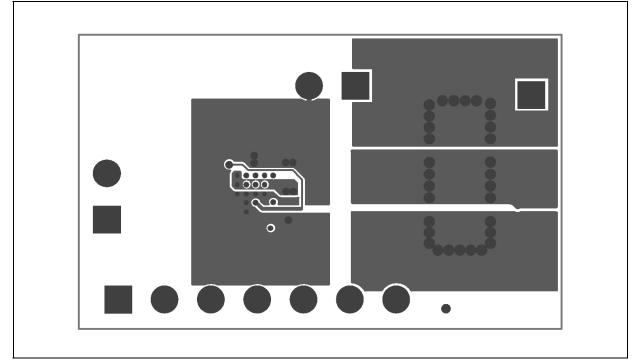

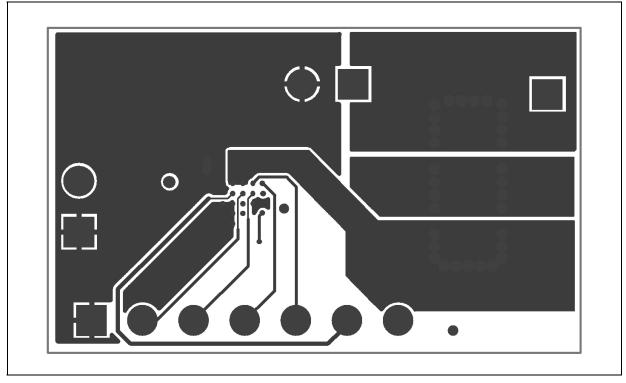

## Figure 1. Demonstration board STCF05 v3: optimized for smallest PCB area (24 mm<sup>2</sup>)

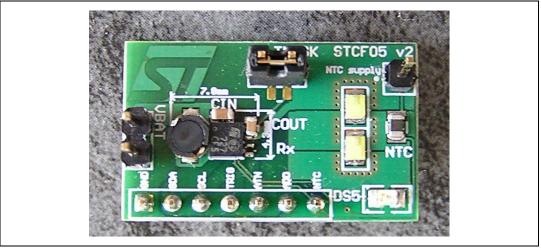

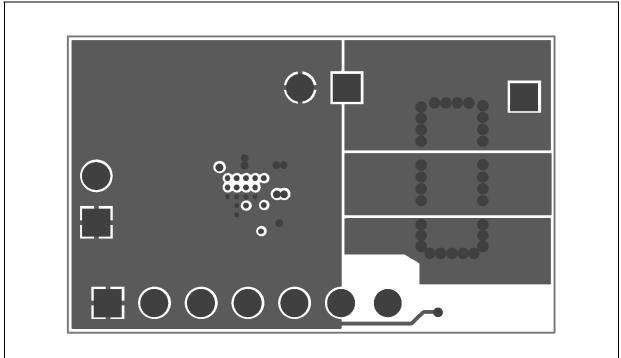

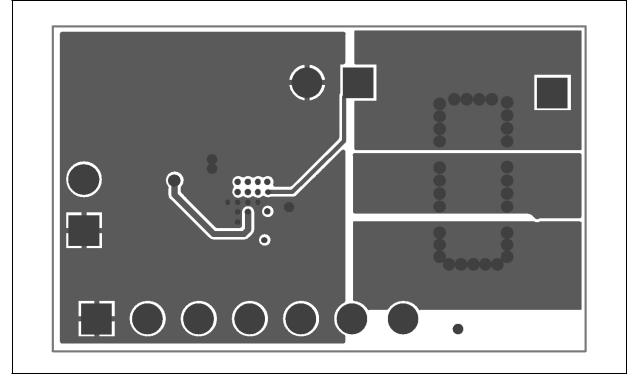

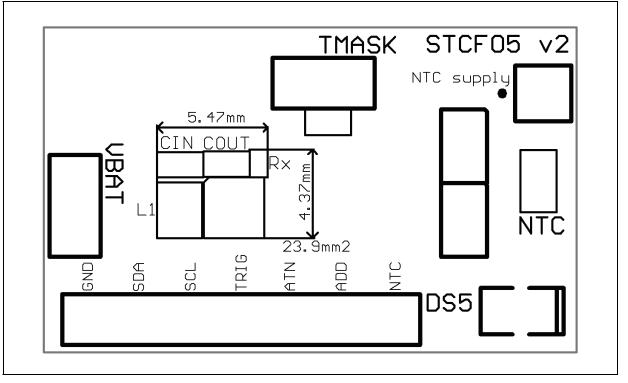

Figure 2. Demonstration board STCF05 v2: optimized for best efficiency

57

## Contents

| 1 | Scher              | natic de  | escription                                                                                 |  |  |  |  |  |  |

|---|--------------------|-----------|--------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 2 | Selec              | tion of e | external components 5                                                                      |  |  |  |  |  |  |

|   | 2.1                | Input an  | d output capacitor selection 5                                                             |  |  |  |  |  |  |

|   | 2.2                | Inductor  | selection                                                                                  |  |  |  |  |  |  |

|   | 2.3                | LED sel   | ection                                                                                     |  |  |  |  |  |  |

|   | 2.4                | NTC and   | d RX resistor selection 5                                                                  |  |  |  |  |  |  |

| 3 | РСВ с              | design    |                                                                                            |  |  |  |  |  |  |

|   | 3.1                | PCB de    | sign rules                                                                                 |  |  |  |  |  |  |

|   | 3.2                | PCB lay   | out                                                                                        |  |  |  |  |  |  |

|   |                    | 3.2.1     | Four-layer PCB with 33.54 mm <sup>2</sup> application area using VLF4014AT-1R0N2R2 coil 8  |  |  |  |  |  |  |

|   |                    | 3.2.2     | Four-layer PCB with 23.9 mm <sup>2</sup> application area using VLS252012T-1R0N1R7 coil 11 |  |  |  |  |  |  |

| 4 | Intern             | al regis  | ters                                                                                       |  |  |  |  |  |  |

| 5 | Operation modes 15 |           |                                                                                            |  |  |  |  |  |  |

|   | 5.1                | SHUTD     | OWN mode                                                                                   |  |  |  |  |  |  |

|   | 5.2                | SHUTD     | OWN mode with NTC feature activated 15                                                     |  |  |  |  |  |  |

|   | 5.3                | READY     | mode NTC                                                                                   |  |  |  |  |  |  |

|   | 5.4                | Torch m   | ode                                                                                        |  |  |  |  |  |  |

|   | 5.5                | Flash m   | ode                                                                                        |  |  |  |  |  |  |

| 6 | STATI              | JS regis  | ster and ATN pin                                                                           |  |  |  |  |  |  |

| 7 | Readi              | ng and    | writing to the STCF05 registers through the I <sup>2</sup> C bus 20                        |  |  |  |  |  |  |

|   | 7.1                | Writing t | to a single register 20                                                                    |  |  |  |  |  |  |

|   | 7.2                | Writing t | to multiple registers with incremental addressing                                          |  |  |  |  |  |  |

|   | 7.3                | Reading   | from a single register 21                                                                  |  |  |  |  |  |  |

|   | 7.4                | Reading   | from multiple registers with incremental addressing 22                                     |  |  |  |  |  |  |

| 8 | Exam               | ples of   | register setup for each mode                                                               |  |  |  |  |  |  |

2/30

| 9 | Revis | ion history                                           | 29 |

|---|-------|-------------------------------------------------------|----|

|   | 8.5   | Example 5: flash pulse longer than 1.5 s              | 27 |

|   | 8.4   | Example 4: red-eye reduction (multiple short flashes) | 25 |

|   | 8.3   | Example 3: auxiliary LED running at 10 mA for 500 ms  | 25 |

|   | 8.2   | Example 2: 15 mA torch                                | 24 |

|   | 8.1   | Example 1: 400 mA flash with 700 ms duration          | 23 |

## **1** Schematic description

The STCF05 flash LED driver has a high operational frequency (1.8 MHz) which allows the use of small-sized external components.

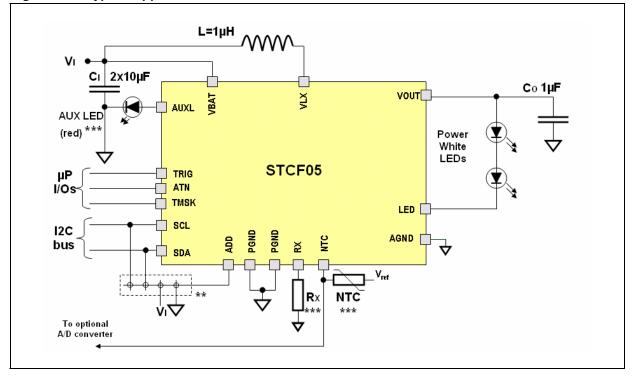

Figure 3. Typical application schematic

\*\*: Connect to  $V_I$ , GND, SDA or SCL to choose one of the four different I<sup>2</sup>C slave addresses.

\*\*\*: Optional components to support auxiliary functions.

## 2 Selection of external components

## 2.1 Input and output capacitor selection

It is recommended to use ceramic capacitors with low ESR as input and output capacitors. It is also recommended to use 10  $\mu$ F/6.3 V as a minimum value for the input capacitor, and 1  $\mu$ F/16 V as the optimal value for the output capacitor to achieve a good stability of the device, for a supply range varying from a low input voltage (2.5 V) to the maximum ratings of output power.

Note: See recommended components in Table 1.

## 2.2 Inductor selection

A thin shielded inductor with a low DC series resistance of winding is recommended for this application. To achieve a good efficiency in step-up mode, we recommend using an inductor with a DC series resistance  $R_{DCL} = R_D / 10 [\Omega; \Omega, 1]$ , where  $R_D$  is the dynamic resistance of the LED [ $\Omega; \Omega, 1$ ].

For nominal operation, the peak inductor current can be calculated by the formula:

$I_{PEAK} = [(I_{OUT} / \eta) + (V_{OUT} - V_{IN}) \times V_{IN^2}) / (2 \times L \times F \times V_{OUT^2})] \times V_{OUT} / V_{IN}$

Where:

- I<sub>PEAK</sub> Peak inductor current

- $I_{OUT}$  Current sourced at the  $V_{OUT}\text{pin}$

- $\eta$  Efficiency of the STCF05

- $V_{OUT}~$  Output voltage at the  $V_{OUT} pin$

- V<sub>IN</sub> Input voltage at the V<sub>BAT</sub>pin

- L Inductance value of the inductor

- F Switching frequency

- Note: See recommended components in Table 1.

## 2.3 LED selection

Any string of LEDs with a cumulative forward voltage ranging from 5.3 to 10.2 V is compatible with the STCF05. The total LED spread must be taken into account when calculating the minimum and maximum voltage of the LEDs that must be inside the 5.3-10.2 voltage range. It is possible to set the level of the LED current to flash mode and torch mode by setting the corresponding registers through the I<sup>2</sup>C interface.

Note: See recommended components in Table 1.

## 2.4 NTC and R<sub>X</sub> resistor selection

Optionally, the STCF05 uses a negative thermistor (NTC) to sense the LED temperature, as well as an R<sub>X</sub> resistor and an external voltage reference in order to use the NTC feature. Refer to *Figure 3: Typical application schematic* for more details.

Once the NTC feature is activated through the  $l^2C$ , the internal switch connects the  $R_X$  resistor to the NTC; this creates a voltage divider supplied by the external reference voltage connected to the NTC.

If the temperature of the NTC thermistor rises as a result of the heat dissipated by the LED, the voltage on the NTC pin increases. When this voltage exceeds 0.56 V, the NTC\_W bit in the STATUS register is set to High, and the ATN pin is set to Low to inform the microcontroller that the LED is becoming hot. The NTC\_W bit is cleared by reading the STATUS register.

If the voltage on the NTC pin rises further and exceeds 1.2 V, the NTC\_H bit in the STATUS register is set to High, and the ATN pin is set to Low to inform the microcontroller that the LED is too hot, and the device switches automatically to READY mode to avoid damaging the LED. This status is latched until the microcontroller reads the STATUS register. Reading the STATUS register clears the NTC\_H bit.

The selection of the NTC and  $R_X$  resistor values strongly depends on the power dissipated by the LED and all the components surrounding the NTC thermistor, and on the cooling capabilities of each specific application. The  $R_X$  and NTC values in *Table 1* work well for the demonstration board presented in this application note. A real-life application may require a different type of NTC thermistor to achieve optimal thermal protection.

The procedure to activate the NTC feature is described in *Section 5.2: SHUTDOWN mode with NTC feature activated*.

| Component      | Manufacturer | Part number                      | Value  | Size               |

|----------------|--------------|----------------------------------|--------|--------------------|

| C <sub>1</sub> | TDK          | C1608X5R0J106M                   | 10 µF  | 0603               |

| C <sub>O</sub> | TDK          | C1608X5R1A105M                   | 1 µF   | 0603               |

| I              | ТДК          | VLF4014AT-1R0N2R2 <sup>(1)</sup> |        | 3.7 x 3.5 x 1.2 mm |

|                | IDK          | VLS252012T-1R0N1R7 (2)           | 1 µH   | 2.5 x 2 x 1.2 mm   |

| NTC            | Murata       | NCP21WF104J03RA                  | 100 kΩ | 0805               |

| R <sub>X</sub> | Rohm         | MCR01MZPJ15K                     | 15 kΩ  | 0402               |

| LED            | Luxeon LED   | 2x LXCL-PWF1                     |        | 0805               |

| AUXLED         | Rohm         | SML-210VT                        |        | 0805               |

Table 1.List of components

1. Used in v2 version to achieve best efficiency.

2. Used in v3 version, when low application area down to 23.9 mm<sup>2</sup> is preferred.

## 3 PCB design

## 3.1 PCB design rules

The STCF05 is a powerful switching device that operates with low input voltages and a high duty cycle. The PCB must be designed in line with switched mode power supply design rules. The power tracks (or wires on the demonstration board) must be as short as possible and wide enough, because of the large currents involved. It is recommended to use a 4-layer PCB to get the best performance. All external components must be placed as close as possible to STCF05. All high-energy switched loops should be as small as possible to reduce EMI.

Most of the LEDs need to be cooled efficiently. This can be achieved by using a dedicated copper area on the PCB. Refer to the selected LED's reference guide to design the proper heatsink. In case a modification of any PCB layer should be required, it is highly recommended to use enough vias. Place the NTC resistor as close as possible to the LED for good temperature sensing. A direct connection between GND and PGND is necessary to achieve a correct output current value. No LED current should flow through this track. Vias connecting the STCF05 pins to the copper tracks (if used) must be 0.1 mm in diameter. It is recommended to use the filled vias.

It is possible to route the STCF05 device with a total PCB area of 23.9 mm<sup>2</sup> using the TDK inductor VLS252012 1  $\mu$ H value. When using the VLF4014AT, the application area is increased by 9.6 mm<sup>2</sup>, and the efficiency of the application is improved up to 85%.

57

## 3.2 PCB layout

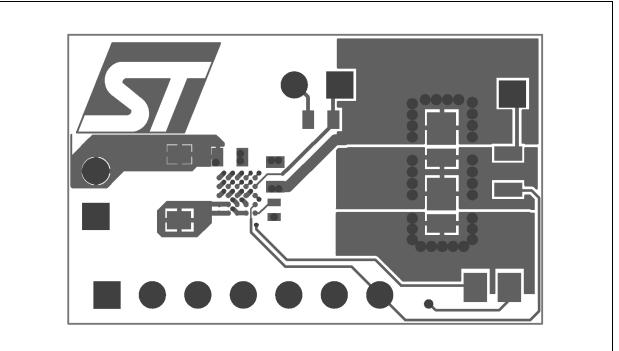

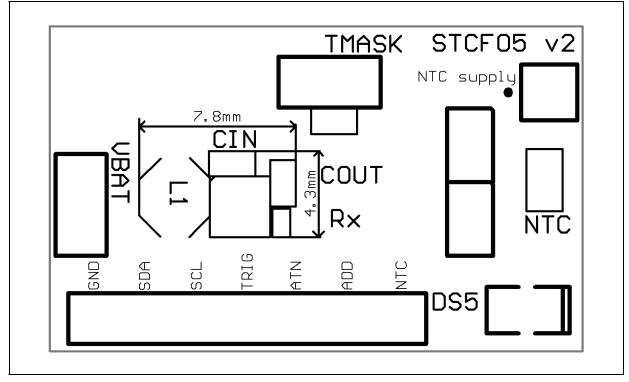

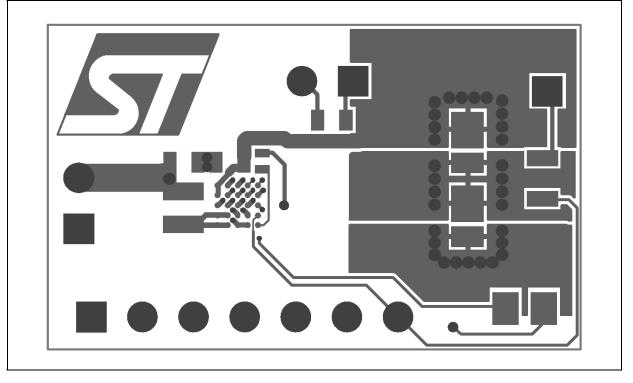

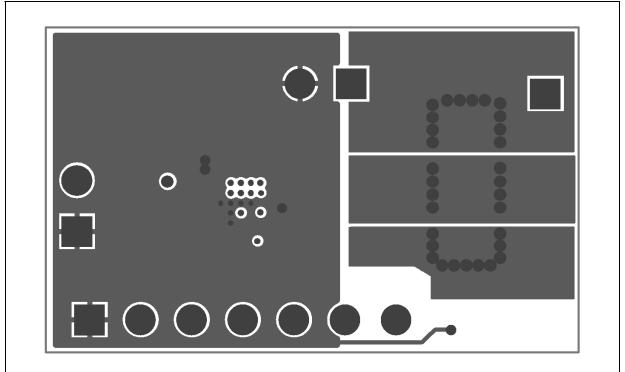

# 3.2.1 Four-layer PCB with 33.54 mm<sup>2</sup> application area using VLF4014AT-1R0N2R2 coil

Figure 4. Top layer

#### Figure 5. Middle layer 1

#### Figure 6. Middle layer 2

#### Figure 7. Bottom layer

#### Figure 8. Top overlay

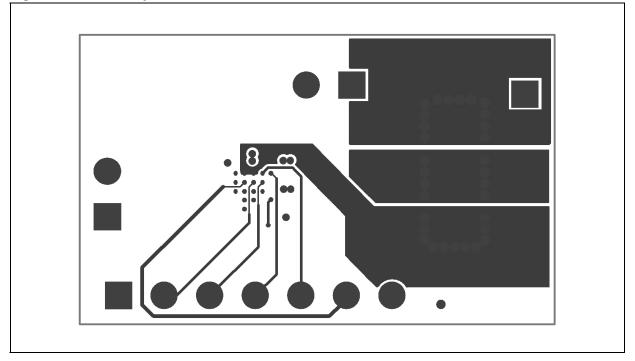

# 3.2.2 Four-layer PCB with 23.9 mm<sup>2</sup> application area using VLS252012T-1R0N1R7 coil

#### Figure 9. Top layer

#### Figure 10. Middle layer 1

57

Figure 12. Bottom layer

#### Figure 13. Top overlay

## 4 Internal registers

The STCF05 has four internal registers: COMMAND, DIMMING, AUX\_LED and STATUS. The STATUS register is read-only.

The COMMAND register can be accessed in any operating mode. All the other registers can be accessed in any mode, except in SHUTDOWN mode. When the device enters SHUTDOWN mode, the DIMMING, AUX\_LED and STATUS registers are cleared. The COMMAND register value remains untouched when entering SHUTDOWN mode. *Table 2* shows the accessibility of each register in all operation modes.

| Pogistor | Address |              | Мо         | de         |            | Shutdown  | Power-ON    |  |

|----------|---------|--------------|------------|------------|------------|-----------|-------------|--|

| Register | Address | Shutdown     | Ready      | Torch      | Flash      | value     | reset value |  |

| COMMAND  | 00      | Read/Write   | Read/Write | Read/Write | Read/Write | Untouched | Cleared     |  |

| DIMMING  | 01      | Inaccessible | Read/Write | Read/Write | Read/Write | Cleared   | Cleared     |  |

| AUX_LED  | 02      | Inaccessible | Read/Write | Read/Write | Read/Write | Cleared   | Cleared     |  |

| STATUS   | 03      | Inaccessible | Read-only  | Read-only  | Read-only  | Cleared   | Cleared     |  |

Table 2. Accessibility of internal registers

## 5 Operation modes

## 5.1 SHUTDOWN mode

SHUTDOWN mode is entered after a power-ON reset. This mode is mainly used to decrease the power consumption of the device. During this mode, only the I<sup>2</sup>C interface is active. The only thing which can be done in SHUTDOWN mode is to access the COMMAND register. Entering SHUTDOWN mode by writing to the COMMAND register will abort any running operation and clear the values of the DIMMING, AUX\_LED and STATUS registers. The COMMAND register value is not affected by entering SHUTDOWN mode.

The following data must be written to the COMMAND register to enter SHUTDOWN mode.

Table 3. COMMAND register data to enter SHUTDOWN mode

|         | PWR_ON | TRIG_EN | TCH_ON | NTC_ON | FTIM_3 | FTIM_2 | FTIM_1 | FTIM_0 |

|---------|--------|---------|--------|--------|--------|--------|--------|--------|

| CMD_REG | 0      | х       | х      | х      | х      | х      | х      | х      |

|         | MSB    |         |        |        |        |        |        | LSB    |

#### 5.2 SHUTDOWN mode with NTC feature activated

When this operation mode is activated, the microcontroller can still monitor the NTC voltage through its A/D converter, while the STCF05 remains in SHUTDOWN mode and therefore saves power.

The following data must be written to the COMMAND register to enter SHUTDOWN mode with NTC activated.

| Table 4. | COMMAND register data to enter SHUTDOWN mode with NTC activated |

|----------|-----------------------------------------------------------------|

|----------|-----------------------------------------------------------------|

|         | PWR_ON | TRIG_EN | TCH_ON | NTC_ON | FTIM_3 | FTIM_2 | FTIM_1 | FTIM_0 |

|---------|--------|---------|--------|--------|--------|--------|--------|--------|

| CMD_REG | 0      | х       | х      | 1      | х      | х      | х      | х      |

|         | MSB    |         |        |        |        |        |        | LSB    |

#### 5.3 READY mode NTC

The READY mode allows the user to access all the internal registers. The NTC feature can be activated in this mode and the temperature of the LED can be sensed by the A/D converter of the microcontroller.

The following data must be written to the COMMAND register to enter READY mode.

Table 5.

COMMAND register data to enter READY mode with NTC activated

|         | PWR_ON | TRIG_EN | TCH_ON | NTC_ON | FTIM_3 | FTIM_2 | FTIM_1 | FTIM_0 |

|---------|--------|---------|--------|--------|--------|--------|--------|--------|

| CMD_REG | 1      | 0       | 0      | 0      | х      | х      | х      | х      |

|         | MSB    |         |        |        |        |        |        | LSB    |

|         | PWR_ON | TRIG_EN | TCH_ON | NTC_ON | FTIM_3 | FTIM_2 | FTIM_1 | FTIM_0 |

|---------|--------|---------|--------|--------|--------|--------|--------|--------|

| CMD_REG | 1      | 0       | 0      | 1      | х      | х      | х      | х      |

|         | MSB    |         |        |        |        |        |        | LSB    |

Table 6. COMMAND register data to enter READY mode

As soon as the NTC feature is activated, the internal switch connects the NTC resistor to the RX resistor, there by creating a voltage divider. The voltage on this divider can be, if desired, monitored by the A/D converter of the microcontroller. An external voltage reference must be connected to the NTC to use this feature. The bits NTC\_W and NTC\_H of the STATUS register will not be properly set if there is no external reference voltage connected to the NTC.

If the NTC feature is not going to be used, neither the negative thermistor nor the external reference needs to be connected. In this case, it is recommended to ground the RX pin. As the NTC feature is automatically activated during the flash and torch mode, leaving the RX pin floating could lead to unwanted interruptions of the light due to non-defined voltages on the RX pin.

#### 5.4 Torch mode

This mode is intended to be used for low light intensities. The LED current in torch mode can be adjusted in a range from 15 mA up to 120 mA.

The torch mode is activated by writing the following data to the COMMAND register.

|         | PWR_ON | TRIG_EN | TCH_ON | NTC_ON | FTIM_3 | FTIM_2 | FTIM_1 | FTIM_0 |

|---------|--------|---------|--------|--------|--------|--------|--------|--------|

| CMD_REG | 1      | 0       | 1      | х      | х      | х      | х      | Х      |

|         | MSB    |         |        |        |        |        |        | LSB    |

Table 7.

COMMAND register data to enter torch mode

The DIMMING register value (TDIM) must be set as well, unless it has already been set during a previous operation. If the TDIM register is not set, then the default output current value will be at the minimum.

As soon as the torch mode is activated, it remains active until a new mode is entered by writing new data to the COMMAND register.

If the torch mode was terminated by entering READY or flash mode, it can be restarted by writing the corresponding data to the COMMAND register only, because entering any of the READY and flash modes does not influence the TDIM value. If the torch mode was terminated by entering SHUTDOWN mode, then the TDIM value must be set again during the restart of the torch mode because entering the SHUTDOWN mode clears the TDIM value.

As soon as the torch mode is activated, the NTC feature is automatically activated too so as to protect the LED from overheating. The NTC feature will be activated even if the NTC\_ON bit in the COMMAND register is set to zero.

#### 5.5 Flash mode

This mode is intended to be used for high light intensities. The LED current in flash mode can be adjusted up to 400 mA with the input voltage ranging from 2.5 to 5.5 V.

The flash mode is activated by writing the following data to the COMMAND register.

|         |        | -       |        |        |        |        |        |        |

|---------|--------|---------|--------|--------|--------|--------|--------|--------|

|         | PWR_ON | TRIG_EN | TCH_ON | NTC_ON | FTIM_3 | FTIM_2 | FTIM_1 | FTIM_0 |

| CMD_REG | 1      | 1       | х      | х      | х      | х      | х      | х      |

|         | MSB    |         |        |        |        |        |        | LSB    |

Table 8.

COMMAND register data to enter flash mode

The DIMMING register value (FDIM) must be written in order to set the desired flash current, while the FTIM\_0 ~ 3 are used to set a maximum time duration for the flash. Values from 0 ~15 correspond to 0 ~1.5 s (100 ms steps). This allows a better safety of the system providing a certain turn-off of the flash even in case of application software problems.

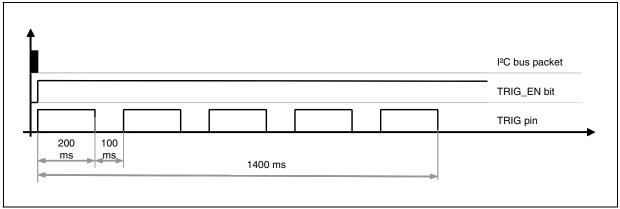

The activation of the flash mode requires the TRIG pin to be High. The flash mode is active only when the TRIG\_EN bit in the COMMAND register is set to 1 and the TRIG pin is High. This gives the user the possibility to choose between a soft and a hard triggering of the flash mode.

The soft triggering is done by writing data to the internal registers only, while the TRIG pin is permanently kept High, for example by connecting it to  $V_{BAT}$ . This saves one pin of the microcontroller, which can be used for a different purpose, but this way of triggering is less accurate than the hard one. The second disadvantage of this solution is that the flash duration can only be set in discrete steps of the internal timer (1 step = approx. 100 ms).

Hard triggering of the flash mode requires the microcontroller to manage the TRIG pin. The COMMAND and DIMMING registers are loaded with data before the TRIG pin is set to High. This allows the user to avoid the I<sup>2</sup>C bus latency. The flash mode then starts as soon as the TRIG pin is set to High. It takes typically about 0.7 ms to ramp-up the LED current to the adjusted value. This time may vary according to the LED current value and the battery voltage.

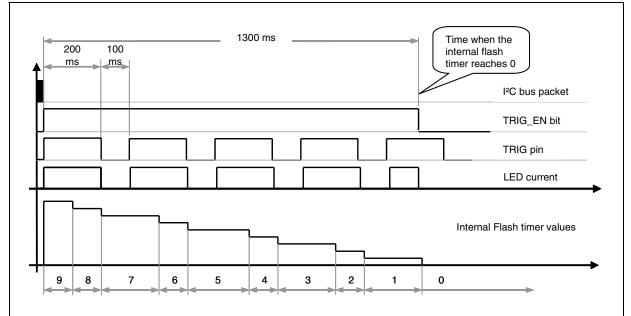

If the TRIG pin is kept High for more than the FTIM value, the internal timer reaches zero and the flash mode is terminated. As soon as the flash is timed out, the ATN pin is pulled down for 11 µs to inform the microcontroller that the STATUS register has been updated and that the flash is over. If the TRIG pin is set to Low before the internal timer reaches zero, the flash mode will be interrupted and can be restarted by setting the TRIG pin High again. The internal timer is stopped while the TRIG pin is Low. This means that the user can split the flash into several pulses of a total length equal to the FTIM value. *Figure 14* shows the splitting of the flash into several shorter pulses. The cumulative length of all the pulses is determined by the FTIM value. *Figure 14* shows the case for

FTIM = 9 (900 ms flash time). The cumulative time when the TRIG pin is High is 1000 ms (5 pulses 200 ms long). The last flash pulse will be100 ms long only. The reason is that the internal flash timer reaches zero and the TRIG\_EN bit is set to 0.

Figure 14. Splitting the flash pulse into several shorter pulses

Hard triggering therefore allows a smooth setting of the flash duration. The resolution is about 8.8 µs. The minimum flash duration is limited by the ramp-up time of the LED current and the maximum is limited by the FTIM value. If it is necessary to make a flash pulse longer then the maximum allowed by FTIM, then it is necessary to reload the COMMAND register before the internal timer reaches zero (start a new flash before the previous one elapses). See Section 8.5: Example 5: flash pulse longer than 1.5 s for more details.

## 6 STATUS register and ATN pin

#### Table 9.STATUS register bits

| Ī | Bit name | LED_S | F_RUN | LED_F | NTC_W | NTC_H | OT_F | OC_F | VOUTOK_N |

|---|----------|-------|-------|-------|-------|-------|------|------|----------|

|   |          | MSB   |       |       |       |       |      |      | LSB      |

Refer to the STCF05 datasheet for a detailed description of each bit.

| Table 10. | Effect of the STATUS register bits on the operation of the device |

|-----------|-------------------------------------------------------------------|

|-----------|-------------------------------------------------------------------|

| Bit Name                            | LED_S | F_RUN<br>STAT_REG | LED_O<br>STAT_REG | NTC_W<br>STAT_REG | NTC_H<br>STAT_REG | OT_F<br>STAT_REG | OC_F<br>STAT_REG | VOUTOK_N<br>STAT_REG |

|-------------------------------------|-------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|----------------------|

| Default<br>value                    | 0     | 0                 | 0                 | 0 0               |                   | 0                | 0                | 0                    |

| Latched <sup>(1)</sup>              | YES   | NO                | YES               | YES               | YES               | YES              | No               | YES                  |

| Forces<br>READY<br>mode<br>when set | NO    | NO                | YES               | NO                | YES               | YES              | NO               | YES                  |

| Sets ATN<br>LOW when<br>set         | YES   | NO                | YES               | YES               | YES               | YES              | NO               | YES                  |

1. YES means that the bit is set by internal signals and is reset to its default value by an I<sup>2</sup>C read operation of STAT\_REG. NO means that the bit is set and reset by internal signals in real-time.

When the status register is latched, reading and writing to the registers is still possible, but the bits TRIG\_EN and TCH\_ON in the COMMAND register and AUXL register cannot be changed until the device is unlatched. It is necessary to read the STATUS register to unlatch the device.

The ATN pin is also pulled down when the internal timer reaches zero in flash mode. In this case, the ATN pin is pulled down for 11  $\mu$ s only. It is recommended to connect the ATN pin to the interrupt input of the microcontroller. If it is not connected to the interrupt input, the ATN pin should be polled fast enough not to miss the 11  $\mu$ s pulse; for example, by a programming loop which is entered after the start of flash mode. This loop will run until the ATN pin goes Low. It is recommended to make a timeout of such a loop.

# 7 Reading and writing to the STCF05 registers through the I<sup>2</sup>C bus

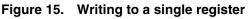

## 7.1 Writing to a single register

Writing to a single register starts with a START bit followed by the 7-bit device address of the STCF05. The 8<sup>th</sup> bit is the R/W bit, which is 0 in this case. R/W = 1 means a reading operation. The master then waits for an acknowledgement from the STCF05. The 8-bit address of the desired register is sent afterwards to the STCF05. It is also followed by an acknowledge pulse. The last transmitted byte is the data that is going to be written into the register. It is followed again by an acknowledge pulse from the STCF05. The master then generates a STOP bit and the communication is over. The whole cycle is represented in *Figure 15*.

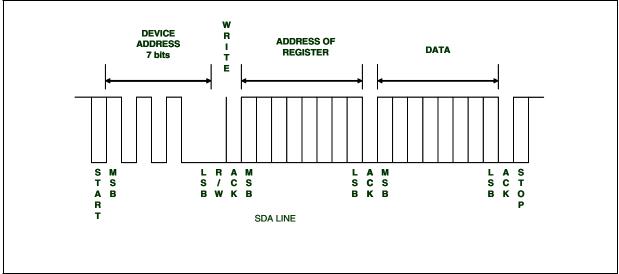

## 7.2 Writing to multiple registers with incremental addressing

It would be unpractical to send several times the device address and the address of the register when writing to multiple registers. The STCF05 supports writing to multiple registers with incremental addressing. When data is written to a register, the register address is automatically incremented (by one), and therefore the next data can be sent without resending the device address and the register address (see *Figure 16*).

#### Figure 16. Writing to multiple register

## 7.3 Reading from a single register

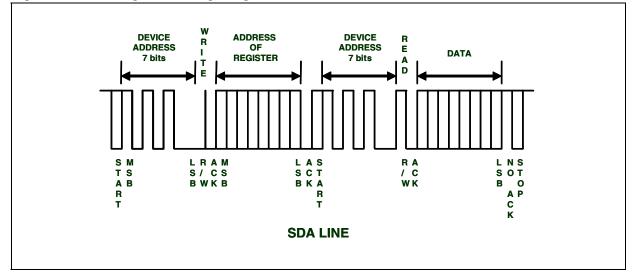

The reading operation starts with a START bit followed by the 7-bit device address of the STCF05. The 8<sup>th</sup> bit is the R/W bit, which is 0 in this case. The STCF05 confirms the receiving of the address + R/W bit by an acknowledge pulse. The address of the register which should be read is then sent and confirmed by another acknowledge pulse from the STCF05. The master then generates another START bit and sends the device address followed by the R/W-bit, which is now 1. The STCF05 confirms the receiving of the address + R/W-bit by an acknowledge pulse, and starts to send data to the master. No acknowledge pulse from the master is required after receiving the data. The master then generates a STOP bit to terminate the communication.

#### Figure 17. Reading from a single register

## 7.4 Reading from multiple registers with incremental addressing

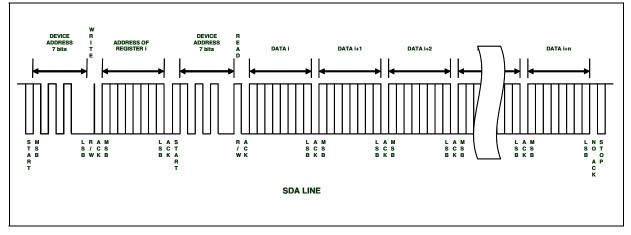

Reading from multiple registers starts in the same way as reading from a single register. As soon as the first register is read, the register address is automatically incremented. If the master generates an acknowledge pulse after receiving the data from the first register, then reading from the next register can start immediately without having to resend the device and register addresses. The last acknowledge pulse before the STOP bit is not required.

#### Figure 18. Reading from multiple registers

## 8 Examples of register setup for each mode

| LDIM (hex)       | 0  | 1  | 2  | 3  | 4  | 5  | 6  | 7   | 8   | 9   | А   | В   | С   |

|------------------|----|----|----|----|----|----|----|-----|-----|-----|-----|-----|-----|

| TDIM (hex)       | 0  | 1  | 2  | 3  | 4  | 5  | 6  | 7   |     |     |     |     |     |

| FDIM(hex)        |    |    |    |    |    | 0  | 1  | 2   | 3   | 4   | 5   | 6   | 7   |

| LED current [mA] | 15 | 20 | 30 | 45 | 60 | 75 | 90 | 120 | 160 | 200 | 240 | 320 | 400 |

| Internal step    | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8   | 9   | 10  | 11  | 12  | 13  |

Table 11. Torch and flash mode dimming register settings

## 8.1 Example 1: 400 mA flash with 700 ms duration

The value of FDIM (4 bits) must be set to 0x7 to set-up the current source to the chosen value (*Table 11*).

The flash duration timer can be set from 100 ms up to 1500 ms in 100 ms steps. If the desired flash duration is 700 ms the FTIM value (4 bits) must be se to 0x7.

The PWR\_ON bit of the command register must be set to 1.

The TRIG\_EN bit of the command register must be set to 1.

The TCH\_ON bit of the command register must be set to 0.

The NTC\_ON bit of the command register can be set to any value because NTC is automatically ON when the flash mode is active. Setting this bit to 0 will not switch off the NTC.

| Table 12. | COMMAND register data to enter flash mode |

|-----------|-------------------------------------------|

|-----------|-------------------------------------------|

| CMD_REG | PWR_ON | TRIG_EN | TCH_ON | NTC_ON | FTIM_3 | FTIM_2 | FTIM_1 | FTIM_0 |

|---------|--------|---------|--------|--------|--------|--------|--------|--------|

|         | 1      | 1       | х      | Х      | 0      | 1      | 1      | 1      |

|         | MSB    |         |        |        |        |        |        | LSB    |

#### Table 13. DIMMING register data for flash mode

| DIM_REG | N/A | TDIM_2 | TDIM_1 | TDIM_0 | N/A | FDIM_2 | FDIM_1 | FDIM_0 |

|---------|-----|--------|--------|--------|-----|--------|--------|--------|

|         | 0   | 0      | 0      | 0      | 0   | 1      | 1      | 1      |

|         | MSB |        |        |        |     |        |        | LSB    |

Four bytes must be written to the STCF05 to make a flash.

Table 14.

I<sup>2</sup>C data packet for activating flash mode

| Byte | Hex |   | _ | _ | Bin | ary | _ | _ | _ | Comment                      |

|------|-----|---|---|---|-----|-----|---|---|---|------------------------------|

| 1    | 62  | 0 | 1 | 1 | 0   | 0   | 0 | 1 | 0 | Device address + R/W bit     |

| 2    | 00  | 0 | 0 | 0 | 0   | 0   | 0 | 0 | 0 | Command register address     |

| 3    | D7  | 1 | 1 | 0 | 1   | 0   | 1 | 1 | 1 | Data of the command register |

| 4    | 07  | 0 | 0 | 0 | 0   | 0   | 1 | 1 | 1 | Data of the dimming register |

## 8.2 Example 2: 15 mA torch

The value of TDIM (4 bits) must be set to 0x0 to set-up the current source to the chosen value.

The PWR\_ON bit of the command register must be set to 1.

The TRIG\_EN bit of the command register must be set to 1.

The TCH\_ON bit of the command register must be set to 0.

The NTC\_ON bit of the command register can be set to any value because NTC is automatically ON when the torch mode is active. Setting this bit to 0 will not switch off the NTC.

| Table 15. | COMMAND register data for torch mode |

|-----------|--------------------------------------|

|-----------|--------------------------------------|

| CMD_REG | PWR_ON | TRIG_EN | TCH_ON | NTC_ON | FTIM_3 | FTIM_2 | FTIM_1 | FTIM_0 |

|---------|--------|---------|--------|--------|--------|--------|--------|--------|

|         | 1      | 0       | 1      | 1      | 0      | 0      | 0      | 0      |

|         | MSB    |         |        |        |        |        |        | LSB    |

#### Table 16. DIMMING register data for torch mode

| DIM_REG | N/A | TDIM_2 | TDIM_1 | TDIM_0 | N/A | FDIM_2 | FDIM_1 | FDIM_0 |

|---------|-----|--------|--------|--------|-----|--------|--------|--------|

|         | 0   | 0      | 0      | 0      | 0   | 0      | 0      | 0      |

|         | MSB |        |        |        |     |        |        | LSB    |

Four bytes must be written to the STCF05 to run the torch mode.

#### Table 17.I<sup>2</sup>C data packet to activate torch mode

| Byte | Hex |   |   |   | Bin | ary |   |   |   | Comment                      |

|------|-----|---|---|---|-----|-----|---|---|---|------------------------------|

| 1    | 62  | 0 | 1 | 1 | 0   | 0   | 0 | 1 | 0 | Device address + R/W bit     |

| 2    | 00  | 0 | 0 | 0 | 0   | 0   | 0 | 0 | 0 | Command register address     |

| 3    | B0  | 1 | 0 | 1 | 1   | 0   | 0 | 0 | 0 | Data of the command register |

| 4    | 00  | 0 | 0 | 0 | 0   | 0   | 0 | 0 | 0 | Data of the dimming register |

The duration of the torch mode is "unlimited". Torch mode is terminated by setting the TCH\_ON bit in the COMMAND register to 0.

Termination of the torch mode can be done by writing the following data to the STCF05.

Table 18.

I<sup>2</sup>C data packet for terminating torch mode

| Byte | Hex |   |   |   | Bin | ary |   |   |   | Comment                      |

|------|-----|---|---|---|-----|-----|---|---|---|------------------------------|

| 1    | 62  | 0 | 1 | 1 | 0   | 0   | 0 | 1 | 0 | Device address + R/W bit     |

| 2    | 00  | 0 | 0 | 0 | 0   | 0   | 0 | 0 | 0 | Command register address     |

| 3    | 80  | 1 | 0 | 0 | 0   | 0   | 0 | 0 | 0 | Data of the command register |

Terminating torch mode puts the STCF05 into READY mode.

## 8.3 Example 3: auxiliary LED running at 10 mA for 500 ms

The STCF05 must be in READY mode (both TRIG\_EN and TCH\_ON set to 0) to activate the auxiliary LED.

A 10 mA output current will be reached when AUXI is set to 0x8.

AUXT must be set to 0x5 to obtain a 500 ms duration of the auxiliary LED lighting.

#### Table 19. COMMAND register data for AUX\_LED

| CMD_REG | PWR_ON | TRIG_EN | TCH_ON | NTC_ON | FTIM_3 | FTIM_2 | FTIM_1 | FTIM_0 |

|---------|--------|---------|--------|--------|--------|--------|--------|--------|

|         | 1      | 0       | 0      | 0      | 0      | 0      | 0      | 0      |

|         | MSB    |         |        |        |        |        |        | LSB    |

#### Table 20. AUX\_LED register data

| AUX_LED | AUXI_3 | AUXI_2 | AUXI_1 | AUXI_0 | AUXT_3 | AUXT_2 | AUXT_1 | AUXT_0 |

|---------|--------|--------|--------|--------|--------|--------|--------|--------|

|         | 1      | 0      | 0      | 0      | 0      | 1      | 0      | 1      |

|         | MSB    |        |        |        |        |        |        | LSB    |

Writing the following three bytes to the STCF05 puts the device into READY mode. This can be skipped if READY mode is already activated.

Table 21. I<sup>2</sup>C data packet for activating READY mode

| Byte | Hex |   |   |   | Bin | ary |   |   |   | Comment                      |

|------|-----|---|---|---|-----|-----|---|---|---|------------------------------|

| 1    | 62  | 0 | 1 | 1 | 0   | 0   | 0 | 1 | 0 | Device address + R/W bit     |

| 2    | 00  | 0 | 0 | 0 | 0   | 0   | 0 | 0 | 0 | Command register address     |

| 3    | 80  | 1 | 0 | 0 | 0   | 0   | 0 | 0 | 0 | Data of the command register |

Writing the following three bytes to the STCF05 activates the auxiliary LED for the desired time.

Table 22. I<sup>2</sup>C data packet for activating AUX\_LED

| Byte | Hex |   |   |   | Bin | ary |   |   |   | Comment                            |

|------|-----|---|---|---|-----|-----|---|---|---|------------------------------------|

| 1    | 62  | 0 | 1 | 1 | 0   | 0   | 0 | 1 | 0 | Device address + R/W bit           |

| 2    | 02  | 0 | 0 | 0 | 0   | 0   | 0 | 1 | 0 | Auxiliary LED register address     |

| 3    | 85  | 1 | 0 | 0 | 0   | 0   | 1 | 0 | 1 | Data of the Auxiliary LED register |

## 8.4 Example 4: red-eye reduction (multiple short flashes)

There are two ways of reducing red eye. The first one is to use hardware triggering of the flashes through the TRIG pin. This is the most suitable and recommended solution, as it reduces the usage of the I<sup>2</sup>C bus and the length of each flash pulse can be adjusted continuously. The second solution is to use the software triggering feature, which means a periodical reloading of the COMMAND register. This will however increase traffic on the I<sup>2</sup>C bus and the flashes can only have a set length, adjustable in 100 ms steps only.

Suppose the targeted value of the flash current is 400 mA. The task is to make five flashes of 200 ms each with a pause of 100 ms between each one.

The setting of the reference voltage is identical to the one in *Example 1*.

The flash timer (FTIM) will be set to 0xF, which represents 1.5 s.

#### Table 23. COMMAND register data for flash mode

| CMD_REG | PWR_ON | TRIG_EN | TCH_ON | NTC_ON | FTIM_3 | FTIM_2 | FTIM_1 | FTIM_0 |

|---------|--------|---------|--------|--------|--------|--------|--------|--------|

|         | 1      | 1       | 0      | 1      | 1      | 1      | 1      | 1      |

|         | MSB    |         |        |        |        |        |        | LSB    |

#### Table 24. DIMMING register data for flash mode

| DIM_REG | N/A | TDIM_2 | TDIM_1 | TDIM_0 | N/A | FDIM_2 | FDIM_1 | FDIM_0 |

|---------|-----|--------|--------|--------|-----|--------|--------|--------|

|         | 0   | 0      | 0      | 0      | 0   | 1      | 1      | 1      |

|         | MSB |        |        |        |     |        |        | LSB    |

Table 25 shows the data packet to be sent.

Table 25.

I<sup>2</sup>C data packet for activating flash mode

| Byte | Hex |   |   |   | Bin | ary |   |   |   | Comment                      |

|------|-----|---|---|---|-----|-----|---|---|---|------------------------------|

| 1    | 62  | 0 | 1 | 1 | 0   | 0   | 0 | 1 | 0 | Device address + R/W bit     |

| 2    | 00  | 0 | 0 | 0 | 0   | 0   | 0 | 0 | 0 | Command register address     |

| 3    | DF  | 1 | 1 | 0 | 1   | 1   | 1 | 1 | 1 | Data of the command register |

| 4    | 07  | 0 | 0 | 0 | 0   | 0   | 1 | 1 | 1 | Data of the dimming register |

*Figure 19* shows the TRIG pin and the I<sup>2</sup>C bus timings.

#### Figure 19. Multiple flashes handled by TRIG pin

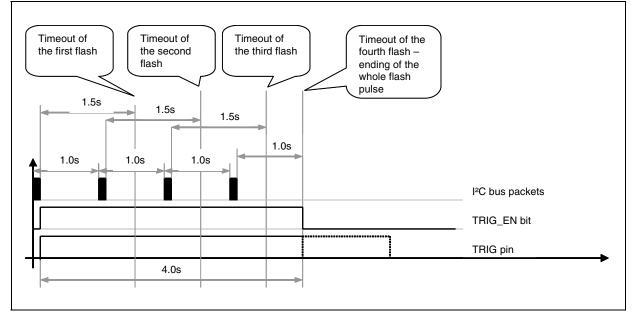

#### 8.5 Example 5: flash pulse longer than 1.5 s

Suppose the targeted value of the flash current is 240 mA. The task is to make a single flash pulse with a 4-second duration.

FTIM must be reloaded into the COMMAND REGISTER before the internal flash timer reaches zero. This guarantees that the flash will continue and not stop after 1.5 seconds.

The first packet must also contain the DIMMING REGISTER data if this data is different from that which was used in the previous operation.

#### Packet 1

Sets flash mode with a 1.5 s duration and the proper dimming.

Table 26. I<sup>2</sup>C data packet for activating flash mode

| Byte | Hex |   |   |   | Bin | ary |   |   |   | Comment                      |

|------|-----|---|---|---|-----|-----|---|---|---|------------------------------|

| 1    | 62  | 0 | 1 | 1 | 0   | 0   | 0 | 1 | 0 | Device address + R/W bit     |

| 2    | 00  | 0 | 0 | 0 | 0   | 0   | 0 | 0 | 0 | Command register address     |

| 3    | DF  | 1 | 1 | 0 | 1   | 1   | 1 | 1 | 1 | Data of the command register |

| 4    | 05  | 0 | 0 | 0 | 0   | 0   | 1 | 0 | 1 | Data of the dimming register |

#### Packet 2

Sets flash mode with a 1.5 s duration. Dimming data is not reset since it is the same as for *Packet 1*.

Table 27.

2<sup>nd</sup> I<sup>2</sup>C data packet for restart of flash mode

| Byte | Hex |   |   |   | Bin | ary |   |   |   | Comment                      |

|------|-----|---|---|---|-----|-----|---|---|---|------------------------------|

| 1    | 62  | 0 | 1 | 1 | 0   | 0   | 0 | 1 | 0 | Device address + R/W bit     |

| 2    | 00  | 0 | 0 | 0 | 0   | 0   | 0 | 0 | 0 | Command register address     |

| 3    | DF  | 1 | 1 | 0 | 1   | 1   | 1 | 1 | 1 | Data of the command register |

#### Packet 3

Sets flash mode with a 1.5 s duration. Dimming remains the same.

Table 28.

3<sup>rd</sup> I<sup>2</sup>C data packet for restart of flash mode

| Byte | Hex |   |   |   | Bin | ary |   |   |   | Comment                      |

|------|-----|---|---|---|-----|-----|---|---|---|------------------------------|

| 1    | 62  | 0 | 1 | 1 | 0   | 0   | 0 | 1 | 0 | Device address + R/W bit     |

| 2    | 00  | 0 | 0 | 0 | 0   | 0   | 0 | 0 | 0 | Command register address     |

| 3    | DF  | 1 | 1 | 0 | 1   | 1   | 1 | 1 | 1 | Data of the command register |

#### Packet 4

Sets flash mode with a 1 s duration. Dimming remains the same.

|      |     | U ut | nu pi |   | 1010 | Sturt | nuoi | 1 1110 | ac |                              |

|------|-----|------|-------|---|------|-------|------|--------|----|------------------------------|

| Byte | Hex |      |       |   | Bin  | ary   |      |        |    | Comment                      |

| 1    | 62  | 0    | 1     | 1 | 0    | 0     | 0    | 1      | 0  | Device address + R/W bit     |

| 2    | 00  | 0    | 0     | 0 | 0    | 0     | 0    | 0      | 0  | Command register address     |

| 3    | DA  | 1    | 1     | 0 | 1    | 1     | 0    | 1      | 0  | Data of the command register |

| Table 29. | 4 <sup>th</sup> I <sup>2</sup> C data packet to restart flash mode |

|-----------|--------------------------------------------------------------------|

|-----------|--------------------------------------------------------------------|

*Figure 20* provides more details on the timing of the I<sup>2</sup>C bus packets.

The solution described in *Example 5* uses a software termination of the flash pulse (it is timed out by the internal timer.) The flash pulse could also be terminated by setting the TRIG pin to low after 4 seconds. In this case, the fourth packet could be the same as packets 2 and 3, because the timing of the flash is done by the TRIG pin and it is not necessary to change the value of FTIM in the COMMAND REGISTER.

This method of periodical reloading of the COMMAND REGISTER can be used to achieve a continuous flash light. However, it is highly recommended to guarantee an efficient cooling of both the LED and the chip, otherwise the light can be interrupted by activation of the thermal protections.

## 9 Revision history

#### Table 30.Document revision history

| Date        | Revision | Changes          |

|-------------|----------|------------------|

| 10-Jun-2009 | 1        | Initial release. |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2009 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com