# AN1724 APPLICATION NOTE

# Conversion Guide, uPSD3200 to uPSD3300 Series

#### Overview

The uPSD family currently consists of two series, uPSD3200 and uPSD3300. Both are available in the same kind of packages, but there are a few differences in pin definitions. This document describes the differences and suggests methods to easily migrate designs from the uPSD3200 series to uPSD3300. You can implement simple techniques on your printed circuit board to accept either a uPSD3200 or a uPSD3300 during manufacturing.

Pin differences will be presented two categories:

- 1. Mandatory pin function changes for all applications

- 2. Conditional pin function changes depending on the application.

There are also differences in SFRs and interrupt vectors, which may impact firmware depending on the application. These differences are identified to help you migrate your firmware.

For simplicity, the uPSD3200 series will be referred in this document as 3200, and the Turbo uPSD3300 series will be referred to as 3300.

# **Contents**

| 1  | Sum   | ary of Differences 3                      |  |  |  |  |  |

|----|-------|-------------------------------------------|--|--|--|--|--|

| 2  | Sum   | mary of new uPSD3300 functions4           |  |  |  |  |  |

| 3  | Pin I | Definitions 6                             |  |  |  |  |  |

| 4  | Man   | datory PIN Changes10                      |  |  |  |  |  |

|    | 4.1   | 52-pin Devices (see Figure 1 and 2)       |  |  |  |  |  |

|    | 4.2   | 80-pin Devices (see Figure 3 and 4)       |  |  |  |  |  |

|    | 4.3   | PC Layout Suggestions                     |  |  |  |  |  |

| 5  | Con   | ditional PIN Changes14                    |  |  |  |  |  |

|    | 5.1   | PWM                                       |  |  |  |  |  |

|    |       | 5.1.1 52-pin Devices (see Figure 1 and 2) |  |  |  |  |  |

|    |       | 5.1.2 80-pin Devices (See Figure 3 and 4) |  |  |  |  |  |

|    |       | 5.1.3 PC Layout Suggestion for PWM14      |  |  |  |  |  |

|    | 5.2   | ADC                                       |  |  |  |  |  |

|    |       | 5.2.1 Reassigned ADC Channel Numbers      |  |  |  |  |  |

|    |       | 5.2.2 ADC Voltage Scaling                 |  |  |  |  |  |

|    |       | 5.2.3 ADC Reference Voltage               |  |  |  |  |  |

|    | 5.3   | LVD 16                                    |  |  |  |  |  |

| 6  | Spec  | cial Function Register (SFR) Differences  |  |  |  |  |  |

| 7  | Inter | rupt Vector Differences                   |  |  |  |  |  |

| 8  | Con   | Conclusion                                |  |  |  |  |  |

| 9  | Con   | Contact Information                       |  |  |  |  |  |

| 10 | Revi  | sion history                              |  |  |  |  |  |

# 1 Summary of Differences

- MCU CORE VOLTAGE: The 3300 MCU core requires a 3.3V supply, even when used in a 5V system. This means two separate supplies (5V V<sub>DD</sub> and 3.3V V<sub>CC</sub>) are required in a 5V system, but just one supply (3.3V V<sub>CC</sub>) is required for a 3.3V system. In contrast, 3200 devices use only a single V<sub>CC</sub> supply, which is 5V V<sub>CC</sub> for 5V devices, or 3.3V V<sub>CC</sub> for 3.3V devices.

- MCU CORE: The 3200 MCU requires 12 clocks per instruction but the 3300 uses just 4 clocks. The 3300 does not have an optional 12-clock operation mode. NO modifications are needed to 3200 firmware for standard 8032 functions unless timing was established with software loops. Modifications ARE required for firmware controlling some peripherals when migrating to 3300.

- PWM: The five 8-bit PWM channels of the 3200 are implemented with the Programmable Counter Array (PCA) in the 3300, which has six 16-bit timer/counter modules. There are new SFRs, and some PWM pin number assignments have changed on the 3300.

- ADC: The four 8-bit ADC channels of the 3200 are implemented using four of the eight 10-bit ADC channels on the 3300. There are new SFRs, but there are no ADC input pin number changes. The ADC reference voltage (V<sub>REF</sub>) input pin is not available on 52-pin 3300 devices and V<sub>REF</sub> is shared internally with the 3.3V V<sub>CC</sub> core supply. 80-pin 3300 devices do have an ADC V<sub>REF</sub> pin, and its max input voltage is V<sub>CC</sub> (3.3V). The max input voltage on any 3300 ADC input is V<sub>CC</sub> (3.3V) even in a 5V system.

- LVD: Both 5V and 3.3V 3300 devices have Low-Voltage Detect (LVD) trip point set for the 3.3V V<sub>CC</sub> supply level (2.5V). This must be considered when designing 5V system.

- WATCHDOG: The watchdog timer is enabled after reset on 3200 devices, but it is disabled after reset on 3300 devices.

- I/O Characteristics: The 3.3V 3300 devices have 5V tolerant I/O on ports 1, 3, and 4, but ports A,B,C, and D are not 5V tolerant. The 3.3V 3200 devices do not have any 5V tolerant I/O.

- UART and I<sup>2</sup>C: Minor changes to SFR definitions.

- USB and DDC: No USB or DDC interfaces are on the 3300.

# 2 Summary of new uPSD3300 functions

Listed below are new functions on the 3300 that were not available on the 3200. Obviously there is no direct migration path for these new functions since the 3200 does not have them. However, you should be aware of the new functions so you can plan to take advantage of them.

- SPI: An SPI bus master interface is provided on the 3300.

- ADC: Eight 10-bit ADC inputs are provided, compared to only four 8-bit ADC inputs on the 3200.

- IrDA: The 2<sup>nd</sup> UART channel supports IrDA protocol, which be connected directly to an IR transceiver.

- PCA: The Programmable Counter Array unit has six 16-bit timer/counter (TC) modules that can be used for PWM, Capture/Compare, Timers, or Counters. Three of the six TC modules can operate from one time base, and the other three TC modules can operate from another time base if desired. These six TC modules are in addition to the standard three 16-bit timer units inside the 8032 MCU core, bringing a total of nine 16-bit timer/counters. The 3200 provides only the three standard 16-bit 8032 timers.

- MCU Core: The 3300 Turbo MCU core has a six-deep instruction prefetch queue and a four-way branching address cache to increase performance. Code in smaller localities operate very fast. No special firmware is required to take advantage of the prefetch queue or branching cache, other than writing to an SFR to enable these features. Be aware that firmware timing loops will not be accurate because of the non-deterministic nature of pipeline and cache architecture. Please use one of the many hardware timer modules to create timing functions, not firmware loops.

- MCU Core: The 3300 Turbo MCU core includes dual data pointers to speed data transfers

of XDATA. The pointers can auto-increment and auto-decrement, providing rapid data

movement from source to destination locations. The 3200 has one only data pointer.

- JTAG Debug: The JTAG port now functions as a debug port in addition to In-System Programming (ISP). This eliminates the need for conventional hardware In-Circuit Emulation (ICE) tools.

- **Debug:** The 3300 has a dedicated debug input/output pin. As an output, it can signal that a specified debug event has occurred, as an input it can trigger a debug event to begin (breakpoint, trace, and so forth).

- MCU Clock: 3.3V 3300 devices can be clocked up to 40MHz, unlike 3.3V 3200 with 24MHz max.

- MCU Clock: 8032 MCU clock can be divided internally for lower power operation. The MCU may change the clock divider ratio on-the-fly using SFRs. This affects the MCU only, not peripheral clocks.

- Cross-Bar I/O: Peripheral functions on Port 1 are also available on Port 4 (cross-bar switch), providing more flexibility. There is no need to sacrifice one peripheral function when two functions are available on a single pin, just use the other port.

- **High Current I/O:** Eight I/O pins on Port 4 are each capable of sinking or sourcing 10mA, for both 3.3V and 5.0V 3300. In contrast, 3.3V 3200 pins are capable of sinking 4mA each, 5V 3200 sink 8mA each.

- **5V Tolerant I/O:** The following pins are 5V tolerant on 3.3V, 52-pin 3300 devices: P1.1 through P1.7, P3.1 through P3.7, P4.1 through P4.7, and RESET\_IN\_. On 3.3V, 80-pin 3300 devices, the following pins are also 5V tolerant: MCU\_AD0 through MCU\_AD7,

5//

MCU\_A8 through MCU\_A11, RD\_, WR\_, and \_PSEN. In contrast, 3.3V 3200 devices had no 5V tolerant I/O pins.

Note:

**Note:** The PSD functions have NOT changed at all from 3200 to 3300. These functions include PLD, memory mapping, memory management (code space vs. data space, and paging), Flash memories, SRAM memory, PSD I/O. All changes in the 3300 are related to the MCU and not the PSD.

577

3 Pin Definitions AN1724

# 3 Pin Definitions

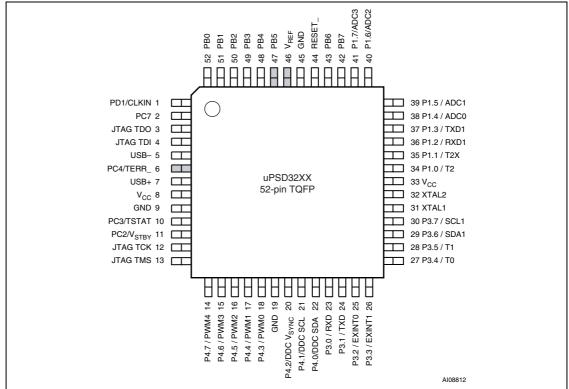

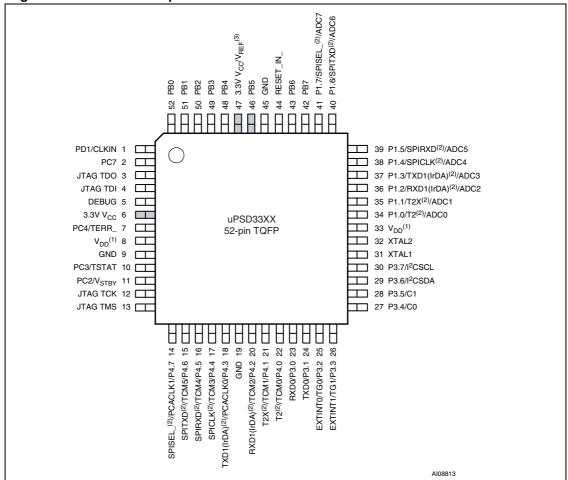

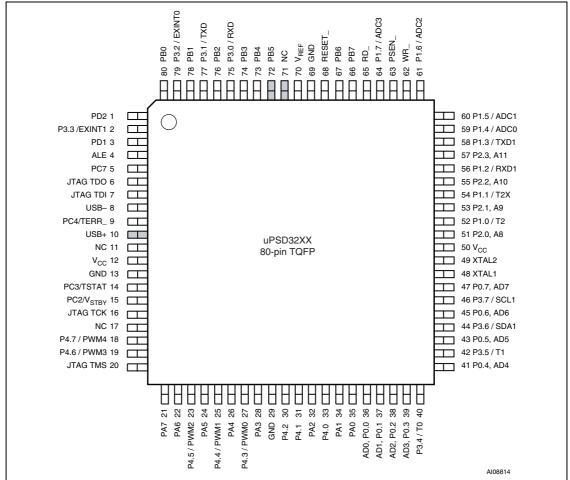

Figure 1, Figure 2., Figure 3., and Figure 4. show pin assignments of the 3200 and 3300 devices in both 52-pin and 80-pin TQFP packages. Please see the 3200 and 3300 data sheets for detailed pin function descriptions and physical dimensions of packages. Pins requiring mandatory changes during migration are darkened in the figures.

Figure 1. uPSD3200 52-pin TQFP Pin Definition

AN1724 3 Pin Definitions

Figure 2. uPSD3300 52-pin TQFP Pin Definition

- Note: 1 For 5V applications,  $V_{DD}$  must be connected to 5.0V source. For 3.3V applications,  $V_{DD}$  must be connected to 3.3V source.

- 2 These signals can be used on one of two different ports (Port 1 or Port 4) for flexibility. Default is Port 1.

- 3  $V_{REF}$  and 3.3V  $V_{CC}$  are shared. ADC channels must use 3.3V as  $V_{REF}$  for 52-pin package.

3 Pin Definitions AN1724

Figure 3. uPSD3200 80-pin TQFP Pin Definition

AN1724 3 Pin Definitions

Figure 4. uPSD3300 80-pin TQFP Pin Definition

Note: 1 For 5V applications,  $V_{DD}$  must be connected to 5.0V source. For 3.3V applications,  $V_{DD}$  must be connected to 3.3V source.

2 These signals can be used on one of two different ports (Port 1 or Port 4) for flexibility. Default is Port 1

4 Mandatory PIN Changes AN1724

# 4 Mandatory PIN Changes

There are some pin changes that are absolutely required when migrating from the 3200. These changes are a result of the additional voltage source required by the 3300 MCU core, and are highlighted as dark colored pins in *Figure 1*, *Figure 2*., *Figure 3*., and *Figure 4*. above.

# 4.1 52-pin Devices (see Figure 1 and Figure 2.)

#### Pins 46 and 47

- The function of pins 46 and 47 have swapped. The signal PB5 was on pin 47 for the 3200, but now is on pin 46 for the 3300. Pin 47 on the 3300 must always be connected to 3.3V V<sub>CC</sub> supply.

- The ADC V<sub>REF</sub> (voltage reference) input was on pin 46 for the 3200, but is now on pin 47 for the 3300.

- V<sub>REF</sub> on pin 47 of the 3300 is shared internally with 3.3V V<sub>CC</sub> for either 3.3V and 5V 3300 devices. This means no external ADC voltage reference is available, and ADC signal inputs should be scaled to 3.3V V<sub>CC</sub> for their maximum range, even when using a 5V 3300 device.

#### Pins 6 and 7

- The function of pin 6 (PC4) on 3200 devices has moved to pin 7 on the 3300.

- The function of Pin 7 (USB+) on 3200 devices is not needed on the 3300 since USB is not available.

- Pin 6 on the 3300 is now  $V_{CC}$  and must always be connected to a 3.3V  $V_{CC}$  supply.

#### Pin 5

- Pin 5 (USB-) on the 3200 must be pulled up to  $V_{CC}$ , regardless if USB is used or not. The pull-up resistor value for 3.3V 3200 devices is 2KΩ, the pull-up value for 5V 3200 devices is 7.5KΩ.

- The function of pin 5 (USB-) on 3200 devices is not needed on the 3300 since USB is not available.

- Pin 5 on 3300 devices now functions as a Debug input/output, and does not need a pull up to  $V_{\rm CC}$ .

#### V<sub>CC</sub> and V<sub>DD</sub>

- In a 3.3V system using a 3.3V 3300 device, pins 6, 8, 33, 47 must be connected to a 3.3V V<sub>CC</sub> source.

- In a 5V system, using a 5V 3300 device, pins 6 and 47 should be connected to a 3.3V

V<sub>CC</sub> source, and pins 8 and 33 should be connected to a 5.0V V<sub>DD</sub> source.

# 4.2 80-pin Devices (see *Figure 3* and *Figure 4*.)

#### Pins 71 and 72

The function of pins 71 and 72 have swapped. The signal PB5 was on pin 72 for the 3200, but now is on pin 71 for the 3300. Pin 72 on the 3300 must always be connected to 3.3V V<sub>CC</sub> supply.

#### Pin 10

- Pin 10 is the USB+ signal on 3200 devices equipped with USB. Ideally, this pin was not connected to anything before migrating to 3300. USB is not available on the 3300.

- Pin 10 must always be connected to 3.3V V<sub>CC</sub> on the 3300.

#### Pin 8

- Pin 8 (USB-) on the 3200 must be pulled up to  $V_{CC}$ , regardless if USB is used or not. The pull-up resistor value for 3.3V 3200 devices is 2KΩ, the pull-up value for 5V 3200 devices is 7.5KΩ.

- The function of pin 8 (USB-) on 3200 devices is not needed on the 3300 since USB is not available.

- Pin 8 on 3300 devices now functions as a Debug input/output, and does not need a pull up to V<sub>CC</sub>.

#### V<sub>CC</sub> and V<sub>DD</sub>

- In a 3.3V system using a 3.3V 3300 device, pins 10, 12, 50, 72 must connect to 3.3V V<sub>CC</sub> source.

- In a 5V system, using a 5V 3300 device, pins 10 and 72 should be connected to a 3.3V V<sub>CC</sub> source, and pins 12 and 50 should be connected to a 5.0V V<sub>DD</sub> source.

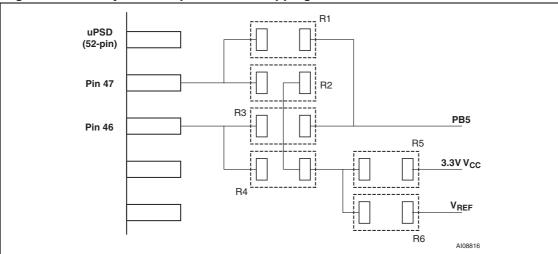

# 4.3 PC Layout Suggestions

You can plan your printed circuit board layout in anticipation of migrating from the 3200 to the 3300 by using simple and low cost techniques. One method involves the use of zero ohm  $(0\Omega)$  resistors (either surface-mount or thru-hole) and multiple circuit traces on the printed circuit board. The idea is to install or not install these  $0\Omega$  resistors at the time of board manufacture depending on which uPSD is installed.

For example, *Figure 5* shows how you can use this method to handle the swapped functions of pins 46 and 47 on the 52-pin uPSD. If a 3200 device is installed, resistor positions R1, R4, and R6 would be populated with  $0\Omega$  resistors during manufacturing while leaving R2, R3, and R5 blank. If a 3300 devices is installed, resistors R2, R3, and R5 are populated and R2, R4, and R6 are blank. A similar method can be used for an 80-pin device, using pins 71 and 72 instead of pins 46 and 47, respectively.

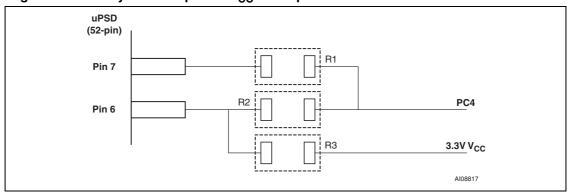

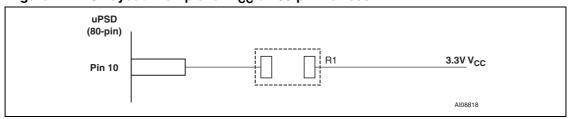

Figure 6 illustrates one way to handle the differing functions of pins 6 and 7 on the 52-pin uPSD. Pin 7 is USB+ on some 3200 devices, and it is assumed USB is not used in the 3200 application, meaning pin 7 was not connected to anything prior to migration to 3300. For this example, when a 3300 device is installed during manufacturing, a 0Ω resistor is installed at positions R1 and R3, leaving R2 blank. When a 3200 is installed, R2 gets a 0Ω resistor and R1 and R3 are blank. For 80-pin uPSDs, the signal PC4 does not change pin numbers when migrating from 3200 to 3300 devices, so a simpler method is shown in *Figure 7*. When an 80-pin 3300 device is installed, R1 is populated, but RI is blank when an 80-pin 3200 is installed.

**5**//

Figure 5. PC Layout Example for Pin Swapping

Figure 6. PC Layout Example for V<sub>CC</sub> on 52-pin Devices

Figure 7. PC Layout Example for V<sub>CC</sub> on 80-pin Devices

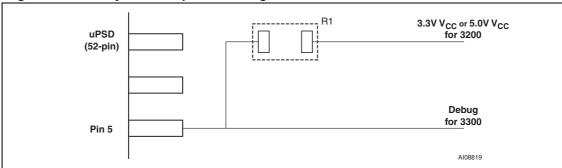

Figure 8 illustrates one way to handle the Debug signal on pin 5 of 52-pin 3300 device. There is a conflict here because it is required to have a pull-up resistor on pin 5 of the 3200 (7.5KΩ on 5V 3200 devices, or 2KΩ on 3.3V 3200 devices), but pin 5 should have no pull-up on 3300 applications. A simple method using a 0Ω resistor is shown. When a 3200 device is installed, R1 is populated with the appropriate pull-up resistor during manufacturing. When a 3300 device is installed, R1 is blank. A similar method can be used for an 80-pin device using pin 8 instead of pin 5.

The Debug signal is only for laboratory use and typically will be routed to a test point on the circuit board.

Figure 8. PC Layout Example for Debug Pin

**5**//

# 5 Conditional PIN Changes

There are some pin changes that may or may not apply to your design, depending on your application. These changes must be considered when migrating to the 3300 and you have used the PWM or ADC peripherals of the 3200. There is also a conditional change regarding the use of the Low-Voltage Detect (LVD) feature in 5V 3300 devices.

## 5.1 **PWM**

There are five PWM outputs on the 3200, and six PWM outputs on the 3300. If you have used any of PWM outputs PWM1, PWM2, or PWM3, on the 3200 then there are no pin changes when migrating to the 3300. However, if you have used PWM outputs PWM0 or PWM4 on the 3200, then you will have to connect to different pins on the 3300.

The Programmable Counter Array (PCA) on the 3300 has six Timer/Counter I/O pins, labeled TCM0 through TCM5, that can be used for PWM outputs, and the PCA also has two clock input pins labeled PCACLK0 and PCACLK1. These eight PCA pins are all on Port 4. It is the two PCA clock input pins of the 3300 that conflict with the PWM0 and PMW4 pin assignments of the 3200.

## 5.1.1 52-pin Devices (see Figure 1 and Figure 2.)

If you are using up to three of the five PWM outputs on the 3200, do not use outputs PMW0 or PWM4, instead use outputs PWM1, PWM2, or PWM3 and there will be no pin conflicts when migrating to the 3300.

If you are using four or more PWM outputs on the 3200, then PWM0 on pin 18, or PWM4 on pin 14, will have to be moved to one of the one of following pins on the 3300: pins 15, 16, 17, 20, 21, or 22.

## 5.1.2 80-pin Devices (See Figure 3 and Figure 4.)

If you are using up to three of the five PWM outputs on the 3200, do not use outputs PMW0 or PWM4, instead use outputs PWM1, PWM2, or PWM3 and there will be no pin conflicts when migrating to the 3300.

If you are using four or more PWM outputs on the 3200, then PWM0 on pin 27 or PWM4 on pin 18 will have to be moved to one of the one of following pins on the 3300: pins 19, 23, 25, 30, 31, or 33.

## 5.1.3 PC Layout Suggestion for PWM

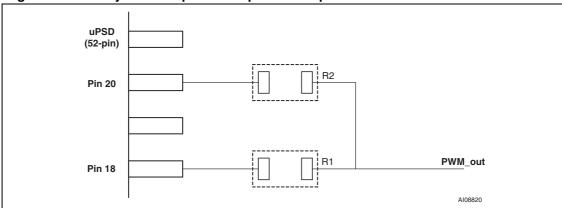

Figure 9 is an example of how to move PWM output PWM0 on a 3200 device to PCA output TCM2 on a 3300 device (52-pin). When a 3200 is installed, R1 is populated with a  $0\Omega$  resistor and R2 is blank. When a 3300 is installed, only R2 is populated. A similar method can be used for an 80-pin device using pins 27 and 30 instead of pins 18 and 20 respectively.

Figure 9. PC Layout Example to Swap PWM Outputs

### 5.2 ADC

## 5.2.1 Reassigned ADC Channel Numbers

The 3200 has four ADC inputs (8-bit resolution), and the 3300 has eight ADC inputs (10-bit resolution). The physical ADC input pin number numbers have not been changed, but the logical ADC channel numbers change when migrating from 3200 to 3300. This means no changes to PC board are required, but MCU firmware must change to account for different channel numbers. Firmware changes must occur anyway because there are SFR changes, identified in the next section. *Table 1* refers to 52-pin uPSD devices, *Table 2* refers to 80-pin uPSD devices.

Table 1. Reassigned ADC Channel Numbers, 52-pin uPSD

| <del>_</del>         | <u> </u>      |               |

|----------------------|---------------|---------------|

| Pin # on 52-pin TQFP | 3200 Device   | 3300 Device   |

| 38                   | ADC Channel 0 | ADC Channel 4 |

| 39                   | ADC Channel 1 | ADC Channel 5 |

| 40                   | ADC Channel 2 | ADC Channel 6 |

| 41                   | ADC Channel 3 | ADC Channel 7 |

Table 2. Reassigned ADC Channel Numbers, 80-pin uPSD

| Pin # on 80-pin TQFP | 3200 Device   | 3300 Device   |

|----------------------|---------------|---------------|

| 59                   | ADC Channel 0 | ADC Channel 4 |

| 60                   | ADC Channel 1 | ADC Channel 5 |

| 61                   | ADC Channel 2 | ADC Channel 6 |

| 64                   | ADC Channel 3 | ADC Channel 7 |

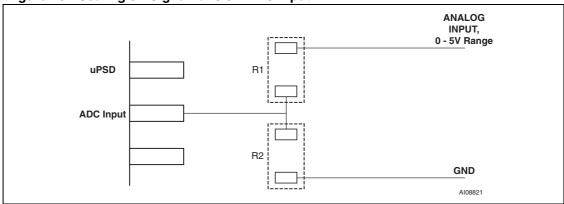

## 5.2.2 ADC Voltage Scaling

For all 3300 devices, both 3.3V and 5V, the maximum input voltage level on any of the eight ADC inputs is the MCU core voltage,  $V_{CC}$  (3.6V maximum). This means that if 5V signals are to be sampled in a 5V 3300 system, they must be scaled down to 3.3V  $V_{CC}$ . In contrast, for 5V

577

3200 devices, if 5V signals are sampled, they do not have to be scaled down because the max ADC input voltage is 5V  $V_{CC}$  (5.5V max).

Figure 10 illustrates one way to scale a 0-5V analog signal down to 0-3.3V when a 3300 device is used. For example, if a 3300 device is installed, resistor R1 is populated with a 332KΩ resistor, and R2 is populated with a 665KΩ resistor. Precision 1% resistors are recommended. Alternately, if a 3200 is installed, R1 is populated with a 0Ω resistor and R2 is left blank because no scaling is needed.

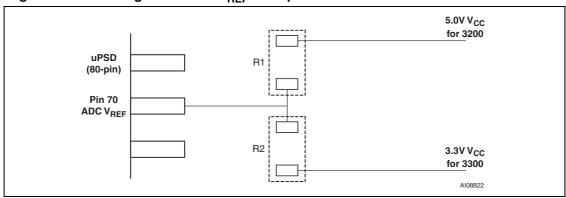

## 5.2.3 ADC Reference Voltage

The maximum ADC reference voltage ( $V_{REF}$ ) allowed on the 3300 is the MCU core voltage,  $V_{CC}$  (3.6V max), for both 3.3V and 5V 3300 devices. In contrast, for 5V 3200 devices the maximum ADC reference voltage is 5V  $V_{CC}$  (5.5V max). *Figure 11* shows one method to switch the source for  $V_{REF}$  during manufacturing if needed. If a 5V 3200 is installed, R1 populated with a  $0\Omega$  resistor and R2 is blank. If a 5V 3300 is installed, only R2 gets the  $0\Omega$  resistor. This ONLY applies to 80-pin uPSD devices, because 52-pin 3300 devices do not have a  $V_{REF}$  input as discussed in the mandatory pin change section above and *Figure 5*.

Figure 10. Scaling 5V Signal for 3.3V ADC Input

Figure 11. Switching Sources of V<sub>REF</sub> in 80-pin uPSD Devices

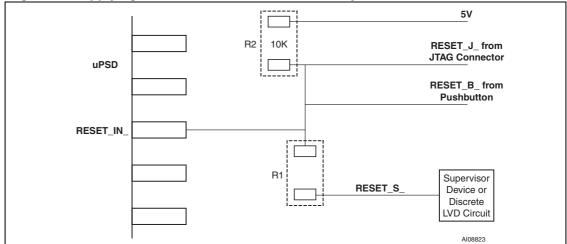

## 5.3 LVD

The Low Voltage Detect (LVD) circuitry on all 3300 (both 3.3V and 5V devices) will generate an internal reset signal whenever the MCU 3.3V  $V_{\rm CC}$  voltage level dips below 2.5V. This is fine for

3.3V systems using a 3.3V 3300 device. However, for 5V systems using a 5V 3300 device, it is recommended to use an external LVD circuit to drive the RESET\_IN\_ pin if it is desired to monitor the 5.0V  $V_{DD}$  system supply in addition to the 3.3V  $V_{CC}$  supply. Regarding the 3200, there is no problem with 5V devices because the LVD circuitry has an internal trip point at 4.0V.

RESET\_IN\_ is an active-low, open-drain, 5V tolerant input. RESET\_IN\_ is located at pin 44 on 52-pin devices, or pin 68 on 80-pin devices.

Figure 12 illustrates a scheme that may be used when migrating from a 5V 3200 device to a 5V 3300 device. In this example, R1 is populated with a  $0\Omega$  resistor only when a 3300 is installed, but R1 is left blank when a 3200 is used (supervisor device is optional when 3200 is used). R2 is always populated with a 10K resistor. Since the pin RESET\_IN\_ is open-drain, it may be driven by multiple open-drain sources.

**Suggestion:** If a real-time clock (RTC) is needed in the system, choose an RTC that also has an LVD reset output so you can use it as shown in *Figure 12*. There are many devices available from ST at www.st.com/nyram.

Reminder: An external LVD circuit is not needed for 3.3V 3300 devices in a 3.3V system.

Figure 12. Applying External LVD Circuit to 3300 5V System

# 6 Special Function Register (SFR) Differences

The are a number of SFRs in the 3200 that have changed compared to the 3300. There are also a number of new SFRs in the 3300 to control new peripherals and features. None of the standard 8032 SFRs have changed (those defined in standard Intel 8032 architecture). *Figure 13* shows all the 3300 SFRs. Those with a black background and white letters indicate 3300 SFRs that have changed from the 3200 definition. Those with a gray background and black letters are new SFRs in the 3300.

Please see 3300 data sheet for detailed description of new and changed SFRs. For convenience, listed below is summary the differences for those SFRs that have changed function or location (the SFRs with black background in Figure 13, page 19). Please adjust your firmware for the changes.

- 87: PCON

- New POR Bit to determine source of last reset.

- 91: P3SF1

- Used to be P1SF1. P1SF1 now has new meaning since it is linked to P4SF1. See the 3300 data sheet.

- 96: ADAT1

- Now different because 3300 has 10-bit ADC, not 8-bit ADC.

- 97: ACON

- New bits to control ADC interrupt.

- New bit to access eight ADC channels instead of four channels.

- A7/A8: ICA/IA

- New Interrupt Enable bits for Debug, ADC, SPI, and PCA.

- B7/B8: IPA/IP

- New Interrupt priority bits for Debug, ADC, SPI, and PCA.

- D8/D9: SCON1/SBUF1

- 2nd UART control and data buffer. Same function as 3200, but new SFR address location in 3300.

- DC: S1CON

- STO and STA Bits do not have to be cleared by software as they did in 3200. 3300

has hardware (silicon) to assist, which improves I<sup>2</sup>C performance and reduces

software overhead.

- DD: S1STA

- More efficient use of Bits INTR and ACK\_REP\_ for I<sup>2</sup>C.

Figure 13. SFRs in the 3300

| SFR<br>Addr | SFR Register Name |          |          |          |          |          | SFR<br>Addr |          |         |

|-------------|-------------------|----------|----------|----------|----------|----------|-------------|----------|---------|

| F8          |                   | CCON0    |          | CCON2    | CCON3    |          |             |          | FF      |

| F0          | В                 |          |          |          |          |          |             |          | F7      |

| E8          |                   |          |          |          |          |          |             |          | EF      |

| E0          | ACC               |          |          |          |          |          |             |          | E7      |

| D8          | SCON1             | SBUF1    |          | S1SETUP  | S1CON    | S1STA    | S1DAT       | S1ADR    | DF      |

| D0          | PSW               |          | SPICLKD  | SPISTAT  | SPITDR   | SPIRDR   | SPICON0     | SPICON1  | D7      |

| C8          | T2CON             |          | RCAP2L   | RCAP2H   | TL2      | TH2      | IRDACON     | DSTAT    | CF      |

| C0          | P4                | CAPCOML3 | САРСОМН3 | CAPCOML4 | САРСОМН4 | CAPCOML5 | CAPCOMH5    | PWMF1    | C7      |

| В8          | IP                |          | PCACL1   | PCACH1   | PCACON1  | TCMMODE3 | TCMMODE4    | TCMMODE5 | BF      |

| В0          | P3                | CAPCOMH1 | CAPCOML2 | CAPCOMH2 | PWMF0    |          |             | IPA      | В7      |

| A8          | ΙE                | TCMMODE0 | TCMMODE1 | TCMMODE2 | CAPCOML0 | САРСОМН0 | WDTKEY      | CAPCOML1 | AF      |

| Α0          | P2                |          | PCACL0   | PCACH0   | PCACON0  | PCASTA   | WDRST       | IEA      | A7      |

| 98          | SCON0             | SBUF0    |          |          |          | BUSCON   | DIR         | DVR      | 9F      |

| 90          | P1                | P3SFS    | P4SFS0   | P4SFS1   | ADCPS    | ADAT0    | ADAT1       | ACON     | 97      |

| 88          | TCON              | TMOD     | TLO      | TL1      | TH0      | TH1      | P1SFS0      | P1SFS1   | 8F      |

| 80          | P0                | SP       | DPL      | DPH      |          | DPTC     | DPTM        | PCON     | 87      |

|             |                   | KEY:     | SAME     | CHAN     | NGED     | NEW      |             |          | AI08824 |

**577**

# 7 Interrupt Vector Differences

There are new interrupt vectors for the 3300, and some interrupt priority levels have changed. *Table 3* compares interrupt vectors of the 3200 and 3300 and their relative priorities. Please adjust your firmware accordingly.

Table 3. Interrupt Vector tables and Priority

| Interrupt Source | 3300<br>Priority | 3300 Vector<br>Address (hex) | 3200<br>Priority | 3200 Vector<br>Address (hex) |

|------------------|------------------|------------------------------|------------------|------------------------------|

| JTAG Debug       | 0 (high)         | 0063                         | N/A              | N/A                          |

| External INT0    | 1                | 0003                         | 0                | 0003                         |

| Timer0           | 2                | 000B                         | 2                | 000B                         |

| External INT1    | 3                | 0013                         | 4                | 0013                         |

| Timer1           | 4                | 001B                         | 6                | 001B                         |

| UART0            | 5                | 0023                         | 8                | 0023                         |

| Timer2 + EXF2    | 6                | 002B                         | 9                | 002B                         |

| SPI              | 7                | 0053                         | N/A              | N/A                          |

| I <sup>2</sup> C | 9                | 0043                         | 3                | 0043                         |

| ADC              | 10               | 003B                         | N/A              | N/A                          |

| PCA              | 11               | 005B                         | N/A              | N/A                          |

| UART1            | 12 (low)         | 004B                         | 1                | 004B                         |

| USB              | N/A              | N/A                          | 7                | 0033                         |

| DDC              | N/A              | N/A                          | 5                | 003B                         |

AN1724 8 Conclusion

# 8 Conclusion

The differences and suggestions for methods to easily migrate designs from the uPSD3200 series to uPSD3300 allow the user to implement simple techniques on your printed circuit board to accept either a uPSD3200 or a uPSD3300 during manufacturing.

For questions about this process or current information on ST Flash uPSD products, please consult our pages on the world wide web: www.st.com/micropsd.

9 Contact Information AN1724

# 9 Contact Information

If you have any questions or suggestions concerning the matters raised in this document, please send them to the following electronic mail addresses:

apps.psd@st.com ask.memory@st.com (for application support) (for general inquiries)

Please remember to include your name, company, location, telephone number, and fax number.

AN1724 10 Revision history

# 10 Revision history

|   | Date         | Revision | Changes          |

|---|--------------|----------|------------------|

| Ī | 23-June-2005 | 1        | Initial release. |

**577**

10 Revision history AN1724

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners

© 2005 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com