# AN1526 APPLICATION NOTE

## ST7FLITE0 QUICK REFERENCE NOTE

by Microcontroller Division Applications

#### INTRODUCTION

The ST7FLITE0 extends the lower end of the ST7 range, designed to fit applications with state-of-the-art features in a very small package.

ST7FLITE0 8-bit MCUs have many cost-saving features and they come with low-cost tools, providing a complete package to reduce both design and final application costs to the absolute minimum.

This application note highlights some small but very important aspects of the ST7FLITE0 that users should not overlook when reading the datasheet.

Sections 2 and 3 contain helpful pointers and a table to help you start working with ST7FLITE0 and its related tools.

Table 1. ST7Lite0 Features

| Program memory           | 1.5 Kbytes Flash (single voltage)                                                                                              |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| RAM                      | 128 bytes                                                                                                                      |

| Data EEPROM              | ST7FLITE05: no Data EEPROM<br>ST7FLITE09: 128 bytes Data EEPROM                                                                |

| Package                  | SO16 (.150) or DIP16                                                                                                           |

| Number of I/O pins       | 13 (including 6 high current pins)                                                                                             |

| Vdd range                | 2.4V - 5.5V                                                                                                                    |

| Temperature range        | -40°C to +85°C                                                                                                                 |

| IDDmax in RUN mode       | 5mA                                                                                                                            |

| LVD                      | 3 levels (Standard)                                                                                                            |

| Clock sources            | Internal RC (1MHz) +/- 1% PLLx4 (2.4V <v<sub>dd&lt;3.3V) PLLx8 (3.3V<v<sub>dd&lt;5.5V)</v<sub></v<sub>                         |

| A/D                      | 8 bits with fixed gain - Op-Amp<br>5 channels                                                                                  |

| Timers                   | Autoreload Timer: 1 12-bit PWM channel, Output Compare function Lite Timer: Watchdog, Real Time Clock, Input Capture functions |

| Communication peripheral | SPI                                                                                                                            |

| Special features         | Read-out protection, In-Circuit Programmming (ICP), In Application Programming (IAP)                                           |

AN1526/0503 1/26

## **Table of Contents**

| INTRODUCTION                                                                                                                                                                                                                                                         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 ST7FLITE0 KEY ADVANTAGES                                                                                                                                                                                                                                           |

| 1.1 LOW-COST 8-BIT MICROCONTROLLER SOLUTION                                                                                                                                                                                                                          |

| 1.2 AREA OPTIMIZATION                                                                                                                                                                                                                                                |

| 1.3 HIGH ACCURACY INTERNAL 1MHZ RC OSCILLATOR4                                                                                                                                                                                                                       |

| 1.4 8-BIT A/D CONVERTER WITH INPUT VOLTAGE AMPLIFIER (X8)4                                                                                                                                                                                                           |

| 1.5 TRUE E2PROM DATA 5                                                                                                                                                                                                                                               |

| 1.6 SAFE PROTECTION AGAINST PIRACY ON DATA E2PROM AND FLASH 5                                                                                                                                                                                                        |

| 1.7 IN-CIRCUIT PROGRAMMING AND IN-APPLICATION PROGRAMMING CAPABILI-<br>TIES 6                                                                                                                                                                                        |

| 2 ST7LITE0 DEVELOPMENT TOOLS7                                                                                                                                                                                                                                        |

| 2.1 SOFTWARE TOOLS       7         2.1.1 ST7 Visual Debug IDE - Reference: STVD7       7         2.1.2 STVD7 Simulator       7         2.1.3 C Compiler toolchains from Cosmic and Metrowerks       7         2.1.4 ST7 Visual Programmer - Reference: STVP7       7 |

| 2.2 HARDWARE TOOLS 8                                                                                                                                                                                                                                                 |

| 2.2.1 In-Circuit Debugging Kit - Reference: ST7FLITE0-INDART82.2.2 ST Emulator - Reference: ST7MDT10-EMU382.2.3 ST Programming tool - Reference: ST7MDT10-EPB92.2.4 ST Graphic Design and Debug - Reference: STREALIZER-II9                                          |

| 3 START TODAY                                                                                                                                                                                                                                                        |

| 4 ST7FLITE0 8-BIT MCU - EASY REFERENCE                                                                                                                                                                                                                               |

## 1 ST7FLITE0 KEY ADVANTAGES

#### 1.1 LOW-COST 8-BIT MICROCONTROLLER SOLUTION

The ST7FLITE0 is a small low-cost microcontroller, embedding many analog functions. It therefore allows you to save board area and the cost of external components. There is no need for:

- external ceramic resonator for accurate oscillators (see 3.2)

- external E<sup>2</sup>data (see 3.4)

- external reset circuitry

- external LVD circuitry

- PCB rework for SW update

- large PCB

#### 1.2 AREA OPTIMIZATION

ST7FLITE0 gives you the choice of two small 16-pin packages. You can take advantage of this to save area on your PCB.

SO16: 6x9.9mm

DIP16:10.92x19.18mm

ST7FLITE0 actual-size footprint of 16-Pin SO Package - Typical: 6mm wide, 9.9mm long

## 1.3 HIGH ACCURACY INTERNAL 1MHZ RC OSCILLATOR

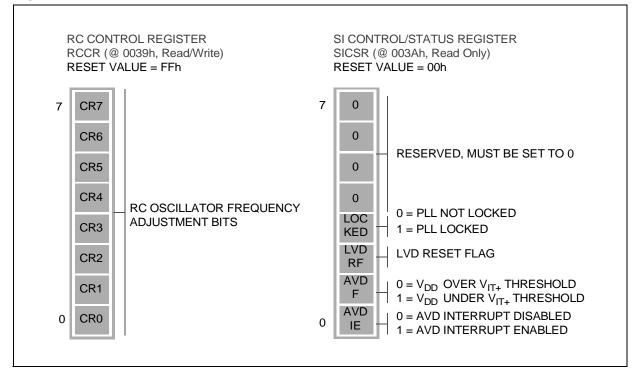

The ST7Flite0 contains an internal RC oscillator with an accuracy of 1% for a given device, temperature and voltage. It must be calibrated to obtain the frequency required in the application. This is done by software writing a calibration value in the RCCR (RC Control Register).

Whenever the ST7FLITE0 microcontroller is reset, the RCCR returns to its default value (FFh), i.e. each time the device is reset, the calibration value must be loaded in the RCCR. Predefined calibration values are stored in E<sup>2</sup>PROM for 3.0 and 5V VDD supply voltages at 25°C, as shown in the following table.

| RCCR  | Conditions                                     | ST7FLITE09<br>Address | ST7FLITE05<br>Address |

|-------|------------------------------------------------|-----------------------|-----------------------|

| RCCR0 | $V_{DD} = 5V$ $T_A = 25$ °C $f_{RC} = 1$ MHz   | 1000h and<br>FFDEh    | FFDEh                 |

| RCCR1 | $V_{DD} = 3V$ $T_A = 25$ °C $f_{RC} = 700$ kHz | 1001h and<br>FFDFh    | FFDFh                 |

If the voltage or temperature conditions change in the application, the frequency may need to be recalibrated.

Refer to AN1324 "Calibrating The RC Oscillator of the ST7FLITE0 MCU using the Mains" for information on how to calibrate the RC frequency using an external reference signal.

## Decoupling capacitor for stable oscillator

Vdd and Gnd levels impact the stability of the 1% internal RC of the ST7FLITE0. To reach the most stable oscillation, use decoupling capacitors between Vdd and Gnd pins, at values recommended in the datasheet.

#### RCCR calibration locations can be Write Protected

The STVP or InDART tools allow you to prevent unintentional write access to the RCCR calibration locations.

## 1.4 8-BIT A/D CONVERTER WITH INPUT VOLTAGE AMPLIFIER (X8)

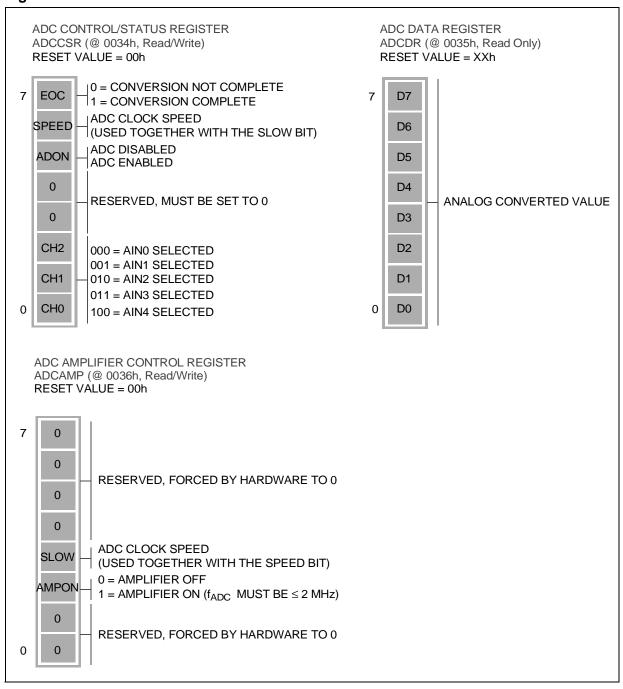

The 8-bit A/D converter allows up to 5 channels with multiplexed inputs.

You can take advantage of its internal fixed-gain amplifier (x8) for zooming on low voltage inputs. For Vdd=5V, the ADC can therefore convert from 0V to 250mV. In this case the ADC ideal resolution is 2.4mV, equivalent to a 11-bit resolution with input range from 0V to Vdd.

4/26

## 1.5 TRUE E<sup>2</sup>PROM DATA

The ST7FLITE09 contains an Electrically Erasable Programmable Read-Only Memory which can be used as a non volatile back-up for storing data. It allows up to 300K Write/Erase cycles at 25°C.

#### **Main Features**

- Up to 32 Bytes programmed in the same cycle

- mono-voltage EEPROM (charge pump)

- Chained erase and programming cycles

- Internal control of the global programming cycle duration

- WAIT mode management

- Read-out protection against piracy

## **Useful Tips:**

## ST7FLITE05: Emulate Data E<sup>2</sup>PROM with program area

For devices with no Data E<sup>2</sup>PROM, you can emulate Data EEPROM with the XFlash Memory.

For more information, refer to:

AN1477: Emulated Data EEPROM with XFlash memory

#### 1.6 SAFE PROTECTION AGAINST PIRACY ON DATA E2PROM AND FLASH

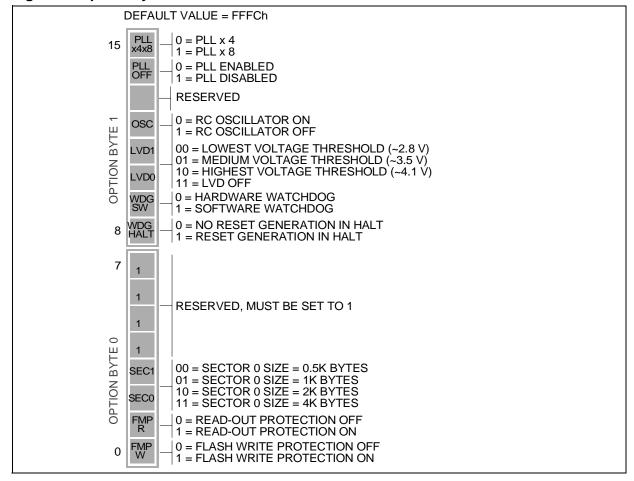

Data stored in the E<sup>2</sup>PROM memory, as well as the program memory, are protected against read-out piracy. This is managed by the option bit "Read-out protection". Removing this option by erasing the option byte will cause the whole memory to be erased first.

Flash program memory can also be protected against re-write operation by option bit "Flash Write protection". When this option is selected, the program memory can never be erased or programmed again.

#### 1.7 IN-CIRCUIT PROGRAMMING AND IN-APPLICATION PROGRAMMING CAPABILITIES

In addition to using a programming tool, the two following modes allow you to program your ST7LITE0 without removing it from your PCB.

ICP: In-Circuit-Programming: The ICP is the ability to program the Flash memory (FLASH sectors 0 and 1, option byte row and data EEPROM) of a microcontroller using ICC (In-Circuit Communication) protocol while the device is already plugged-in to the application, but application is not running.

IAP: In-Application-Programming: The IAP is the ability to re-program the FLASH memory (FLASH sector 1 and data EEPROM) of a microcontroller while the device is already plugged-in to the application and the application is running. As sector 0 contains the software driver to be able to re-program, it is write protected, therefore not reprogrammable.

In ICP minimum configuration, only 3 wires are needed (ICCCLK, ICCDATA, RESET). The user may also use it as a basis to develop its own debugging tool.

#### **Programming time:**

ICP allows 1kbytes to be programmed/erased in 160ms.

Typical measurements: 1.5k Flash programming time: 315ms

For more information, refer to the Programming Manuals:

- . ST7 Flash Programming Reference Manual

- . ST7 ICC Protocol Reference Manual

#### **Useful Tips:**

## Sector 0 size configurable by Option Byte

As sector 0 is not re-programmable in IAP programming mode, you may take advantage of configuring its size to optimize Program Memory.

By Option Byte, sector 0 size can be set at 0.5 Kbytes, 1 Kbytes, or 1.5 Kbytes.

## 2 ST7LITE0 DEVELOPMENT TOOLS

Table 2 shows a summary of available tools for each function.

**Table 2. Available Tools**

|          | SIMULATE           | EMULATE       | DEBUG<br>&<br>PROGRAM                              | GRAPHIC<br>DESIGN &<br>DEBUG | PROGRAM      |

|----------|--------------------|---------------|----------------------------------------------------|------------------------------|--------------|

| SOFTWARE | STVD7<br>Simulator | STVD7         | STVD7 (included in<br>ST7FLITE0-INDART<br>package) | ST-REALIZERII                | STVP7        |

| HARDWARE | no need            | ST7MDT10-EMU3 | ST7FLITE0-INDART                                   | no need                      | ST7MDT10-EPB |

Note: Third-party C-compiler tool chains can be used with STVD7 interface.

#### 2.1 SOFTWARE TOOLS

#### 2.1.1 ST7 Visual Debug IDE - Reference: STVD7

Visual interface for C or Assembler coding, compile, download and debug with ST7 Emulators or ST7FLITE0-INDART.

Web: http://mcu.st.com → ST7

#### 2.1.2 STVD7 Simulator

Stand-alone tool which allows to write code, compile, and simulate an ST7FLITE0 with your PC your ST7FLITE0.

Web: http://mcu.st.com → ST7

## 2.1.3 C Compiler toolchains from Cosmic and Metrowerks

- Free evaluation version limited to 1K

- Low-cost lite C compiler limited to 8K

This compilers can be embedded in STVD7 IDE interface, or used through dedicated graphical interfaces.

Web: Cosmic Software Inc.: www.cosmic-software.com

Metrowerks: www.metrowerks.com

## 2.1.4 ST7 Visual Programmer - Reference: STVP7

Visual Interface allowing to program Flash, Data E<sup>2</sup>PROM, and option bytes. This is the software part of the whole programming tool package. See 4.2.3 for more details.

#### 2.2 HARDWARE TOOLS

## 2.2.1 In-Circuit Debugging Kit - Reference: ST7FLITE0-INDART

ST7FLITE0-INDART includes a full-featured experiment board, an in-circuit programming utility, and all tools required to develop custom embedded applications, at low cost. 100% of electrical characteristics are guaranteed by use of a standard chip, not bondout chip.

ST7FLITE0-INDART contains STVD7 graphical interface, C compiler and assembler.

Debugging capabilities: Real-time emulation, breakpoints, step capabilities, read/write memory and registers.

Programming capabilities: Blank-check, Program, Read, Verify Flash, E<sup>2</sup>PROM memory and Option Bytes.

#### Notes:

- 1. It can be ordered from ST, or directly from Softec. Softec reference: inDART-ST7FLITE0

- 2. No power supply is delivered with this kit. A typical 5V may be used.

Web: http://www.softecmicro.com/indart-st7flite0.html

e-mail: info@softecmicro.com

#### 2.2.2 ST Emulator - Reference: ST7MDT10-EMU3

Advanced development tool including:

- Real-time emulator (Advanced breakpoints management (through Bus Event Machine), 256K real-time trace recording, read/write on the fly through Watch and Memory windows, Performance analysis)

- STVD7 User Interface

- Set of probes for Lite family packages.

- Parallel interface cable to PC

- Power Supply

**Note:** the ST Emulator cannot program parts. Therefore, a separate device programmer is required (as ST7 Programming tool (see 4.2.3))

Web: http://mcu.st.com → ST7

## 2.2.3 ST Programming tool - Reference: ST7MDT10-EPB

Main features: Blank-check, Program, Read, Verify Flash, E<sup>2</sup>PROM memory and Option Bytes.

ICP programming mode is supported. All Lite0 packages included.

This is done through **STVP7: ST7 Visual Programmer**. Visual Interface allowing to program Flash, Data E<sup>2</sup>PROM, and option bytes.

Web: http://mcu.st.com → ST7

## 2.2.4 ST Graphic Design and Debug - Reference: STREALIZER-II

The ST Realizer allows you to graphically design applications for the ST7 microcontroller family, without any prerequisite knowledge in assembler programming. With a single click, using the powerful graphics editor and compiler, you can generate complete software applications for the ST7FLite0.

Main features: schematic-based Design, Analysis, Simulator for debugging

Web: http://mcu.st.com → ST7

#### **3 START TODAY**

- 1) Go to ST's website (http://mcu.st.com) and download:

- STVD7 software

#### and these items:

- ASM/LYN software

- Cosmic C compiler Demo software

- Metrowerks C compiler software

- ST Visual Programmer

- 2) Install all software and follow "Getting Started" in STVD7.

- 3) Copy certain files for the "Getting Started" example and create your own project in STVD7.

- 4) Order tools:

- EMU ST's or inDART

- EPB

- C compiler Cosmic or Metrowerks

## 4 ST7FLITE0 8-BIT MCU - EASY REFERENCE

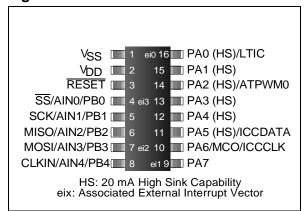

Figure 1. Pinout

**Table 3. Device Summary**

| Features               | ST7FLITE09                                                                        | ST7FLITE05 |  |  |

|------------------------|-----------------------------------------------------------------------------------|------------|--|--|

| Program Memory (Bytes) | 1.5K FLASH                                                                        | 1.5K FLASH |  |  |

| RAM/Stack (Bytes)      | 128/64                                                                            | 128/64     |  |  |

| Data EEPROM<br>(Bytes) | 128                                                                               | -          |  |  |

| Peripherals            | Lite Timer w/ Watchdog, Autore<br>load Timer w/ 1<br>PWM, SPI, 8-bit ADC w/ Op-Am |            |  |  |

| Operating Supply       | 2.4 V                                                                             | to 5.5 V   |  |  |

| CPU Frequency          | 1 MHz RC 1% PLL x4/8MHz                                                           |            |  |  |

| Operating Temperature  | -40 C to +85 C (-40 C to +105/125<br>C Optional)                                  |            |  |  |

**Table 4. Pin Chart**

| Pin | Name             | Main Function         | Alternate Function                                  |

|-----|------------------|-----------------------|-----------------------------------------------------|

| 1   | V <sub>SS</sub>  | Ground                |                                                     |

| 2   | V <sub>DD</sub>  | Main Power Supply     |                                                     |

| 3   | RESET            | Top-Priority Non Mask | cable Interrupt (active low)                        |

| 4   | SS/AIN0/PB0      | PORT B0               | ADC Analog Input 0 or SPI Slave Select (active low) |

| 5   | SCK/AIN1/PB1     | PORT B1               | ADC Analog Input 1 or SPI Serial Clock              |

| 6   | MISO/AIN2/PB2    | PORT B2               | ADC Analog Input 2 or SPI Master In/Slave Out Data  |

| 7   | MOSI/AIN3/PB3    | PORT B3               | ADC Analog Input 3 or SPI Master Out/Slave In Data  |

| 8   | CLKIN/AIN4/PB4   | PORT B4               | ADC Analog Input 4 or External Clock Input          |

| 9   | PA7              | PORT A7               |                                                     |

| 10  | PA6 /MCO/ICCCLK  | PORT A6               | Main Clock Output or In-Circuit Communication Clock |

| 11  | PA5 (HS)/ICCDATA | PORT A5               | In-Circuit Communication Data                       |

| 12  | PA4 (HS)         | PORT A4               |                                                     |

| 13  | PA3 (HS)         | PORT A3               |                                                     |

| 14  | PA2 (HS)/ATPWM0  | PORT A2               | Auto-Reload Timer PWM0                              |

| 15  | PA1 (HS)         | PORT A1               |                                                     |

| 16  | PA0 (HS)/LTIC    | PORT A0               | Lite Timer Input Capture                            |

**Table 5. Instruction Set**

| Mnemonic       | Description                       | Operation                                                | Dest.       | Source | Flags         |

|----------------|-----------------------------------|----------------------------------------------------------|-------------|--------|---------------|

| ADC d, s       | Add with carry, s to d            | $d \leftarrow d + s + C$                                 | А           | mem    | H, N, Z, C    |

| ADD d, s       | Add s to d                        | $d \leftarrow d + s$                                     | А           | mem    | H, N, Z, C    |

| AND d, s       | Logical AND (d with s)            | $d \leftarrow d \text{ AND } s$                          | А           | mem    | N, Z          |

| BCP s, d       | Bit compare A, mem                | $\{N, Z\} \leftarrow s AND d$                            | А           | mem    | N, Z          |

| BRES d, b      | Bit reset d                       | $d \leftarrow d \text{ AND } (2^b)$                      | mem         | -      | -             |

| BSET d, b      | Bit set d                         | $d \leftarrow d OR (2^b)$                                | mem         | -      | -             |

| BTJF d, b, rel | Jump if bit is false (0)          | $PC \leftarrow PC + rel \ IF \ (d \ AND \ (2^b)) = 0$    | mem         | -      | С             |

| BTJT d, b, rel | Jump if bit is true (1)           | $PC \leftarrow PC + rel \ IF \ (d \ AND \ (2^b)) \neq 0$ | mem         | -      | С             |

| CALL d         | Call subroutine                   | PUSH (PC + length); PC ← d                               | mem         | -      | -             |

| CALLR d        | Call subroutine relative          | $PUSH (PC + length); PC \Leftarrow PC + d$               | mem         | -      | -             |

| CLR d          | Clear d                           | $d \leftarrow 0$                                         | reg,<br>mem | -      | N = 0, Z = 1  |

| CP d, s        | Arithmetic compare                | $\{N, Z, C\} \Leftarrow TEST (d - s)$                    | reg         | mem    | N, Z, C       |

| CPL d          | Logical complement of d           | $d \leftarrow d XOR FFh$                                 | reg,<br>mem | -      | N, Z, C = 1   |

| DEC d          | Decrement d                       | d ← d - 1                                                | reg,<br>mem | -      | N, Z          |

| HALT           | Halt                              | I ← 0                                                    | -           | -      | I = 0         |

| INC d          | Increment d                       | d ← d + 1                                                | reg,<br>mem | -      | N, Z          |

| IRET           | Interrupt routine return          | POP CC, A, X, PC                                         | -           | -      | H, I, N, Z, C |

| JP d           | Absolute jump                     | PC ← d                                                   | mem         | -      | -             |

| JRA d          | Jump relative always              | $PC \leftarrow PC + d$                                   | mem         | -      | -             |

| JRT d          | Jump relative if true             | $PC \Leftarrow PC + d$                                   | mem         | -      | -             |

| JRF d          | Never jump                        | -                                                        | mem         | -      | -             |

| JRIH d         | Jump Relative if Port INT pin = 1 | PC ← PC + d IF interrupt line high                       | mem         | -      | -             |

| JRIL d         | Jump Relative if Port INT pin = 0 | $PC \Leftarrow PC + d IF interrupt line low$             | mem         | -      | -             |

| JRH d          | Jump Relative if H = 1            | $PC \Leftarrow PC + d IF H = 1$                          | mem         | -      | -             |

| JRNH d         | Jump Relative if H = 0            | $PC \leftarrow PC + d IF H = 0$                          | mem         | -      | -             |

| JRM d          | Jump Relative if I = 1            | PC ← PC + d IF I = 1                                     | mem         | -      | -             |

| JRNM d         | Jump Relative if I = 0            | $PC \leftarrow PC + d IF I = 0$                          | mem         | -      | -             |

| JRMI d         | Jump Relative if N = 1            | PC ← PC + d IF N = 1                                     | mem         | -      | -             |

| JRPL d         | Jump Relative if N = 0            | $PC \leftarrow PC + d IF N = 0$                          | mem         | -      | -             |

| JREQ d         | Jump Relative if Z = 1            | $PC \leftarrow PC + d IF Z = 1$                          | mem         | -      | -             |

| JRNE d         | Jump Relative if Z = 0            | $PC \leftarrow PC + d IF Z = 0$                          | mem         | -      | -             |

## **Table 5. Instruction Set**

| Mnemonic | Description                             | Operation                                | Dest.       | Source      | Flags         |

|----------|-----------------------------------------|------------------------------------------|-------------|-------------|---------------|

| JRC d    | Jump Relative if C = 1                  | PC ← PC + d IF C = 1                     | mem         | -           | -             |

| JRNC d   | Jump Relative if C = 0                  | $PC \leftarrow PC + d IF C = 0$          | mem         | -           | -             |

| JRULT d  | Jump Relative if C = 1                  | PC ← PC + d IF C = 1                     | mem         | -           | -             |

| JRUGE d  | Jump Relative if C = 0                  | $PC \Leftarrow PC + d IF C = 0$          | mem         | -           | -             |

| JRUGT d  | Jump Relative if $(C + Z) = 0$          | $PC \Leftarrow PC + d IF (C OR Z) = 1$   | mem         | -           | -             |

| JRULE d  | Jump Relative if (C + Z) = 1            | $PC \Leftarrow PC + d IF (C OR Z) = 0$   | mem         | -           | -             |

| LD d, s  | Load s in d                             | $d \leftarrow s$                         | reg,<br>mem | mem,<br>reg | N, Z          |

| MUL d, s | Multiply d by s                         | $d:s \leftarrow d * s$                   | A, X, Y     | A, X, Y     | H = 0, C = 0  |

| NEG d    | Negate d (logical 2-complement)         | $d \leftarrow (d \text{ XOR FFh}) + 1$   | reg,<br>mem | -           | N, Z, C       |

| NOP      | No operation                            | -                                        | -           | -           | -             |

| OR d, s  | Logical OR (d with s)                   | $d \Leftarrow d \ OR \ s$                | Α           | mem         | N, Z          |

| POP d    | Pop from the Stack                      | d ← (++SP)                               | reg, CC     | -           | H, I, N, Z, C |

| PUSH d   | Push onto the Stack                     | (SP) ← d                                 | -           | reg, CC     | -             |

| RCF      | Reset carry flag                        | $C \Leftarrow 0$                         | 1           | -           | C = 0         |

| RET      | Subroutine return                       | POP PC                                   | -           | -           | -             |

| RIM      | Reset interrupt mask                    | I ← 0                                    | -           | -           | I = 0         |

| RLC d    | Rotate left through carry               | C ← 7   0                                | reg,<br>mem | -           | N, Z, C       |

| RRC d    | Rotate right through carry              | (C)→[7]   0                              | reg,<br>mem | -           | N, Z, C       |

| RSP      | Reset Stack pointer                     | SP ← reset value                         | -           | -           | -             |

| SBC d, s | Subtract s from d with carry            | $d \leftarrow d - s - C$                 | Α           | mem         | N, Z, C       |

| SCF      | Set carry flag                          | C ← 1                                    | -           | -           | C = 1         |

| SIM      | Set interrupt mask                      | I ← 1                                    | -           | -           | I = 1         |

| SLA d    | Shift left arithmetic (equal to SLL 1)  | C ← 7                                    | reg,<br>mem | -           | N, Z, C       |

| SLL d    | Shift left logical                      | C ← 7                                    | reg,<br>mem | -           | N, Z, C       |

| SRA d    | Shift right arithmetic (equal to SRL 1) |                                          | reg,<br>mem | -           | N, Z, C       |

| SRL d    | Shift right logical                     | $0 \rightarrow 7 \qquad 0 \rightarrow C$ | reg,<br>mem | -           | N = 0, Z, C   |

| SUB d, s | Subtract s from d                       | $d \leftarrow d - s$                     | Α           | mem         | N, Z, C       |

| SWAP d   | Swap nibbles                            | d (7:4) ⇔ d (3:0)                        | reg,<br>mem | -           | N, Z          |

| TNZ d    | Test for negative and zero              | $\{N, Z\} \leftarrow TEST (d)$           | reg,<br>mem | -           | N, Z          |

**Table 5. Instruction Set**

| Mnemonic | Description                     | Operation                                                                 | Dest. | Source | Flags |

|----------|---------------------------------|---------------------------------------------------------------------------|-------|--------|-------|

| TRAP     | Software trap                   | $PC \Leftarrow PC + 1$ ; PUSH PC, X, A, CC; $PC \Leftarrow trap \ vector$ | -     | -      | I = 1 |

| WFI      | Wait for interrupt              | I ← 0                                                                     | -     | -      | I = 0 |

| XOR d, s | Logical exclusive OR (d with s) | $d \leftarrow d XOR s$                                                    | Α     | mem    | N, Z  |

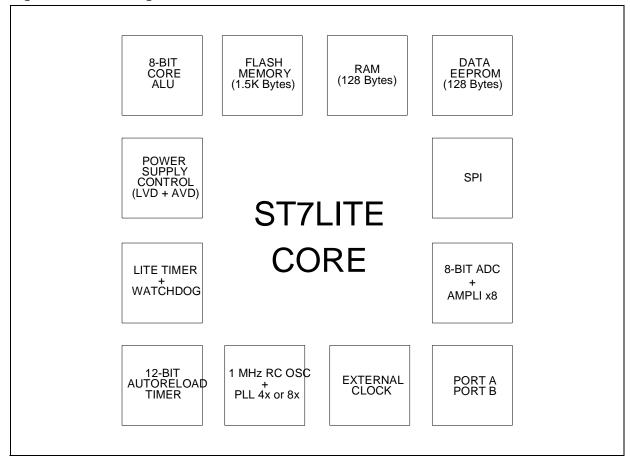

Figure 2. Block Diagram

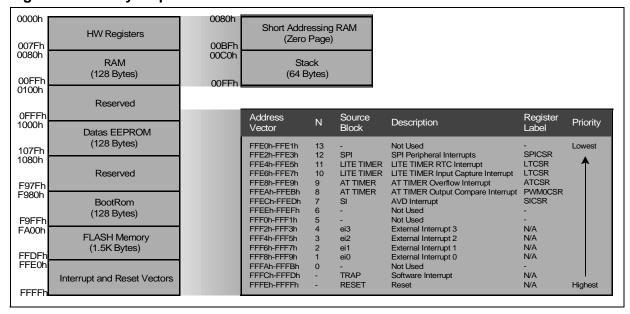

Figure 3. Memory Map

Figure 4. Option Bytes

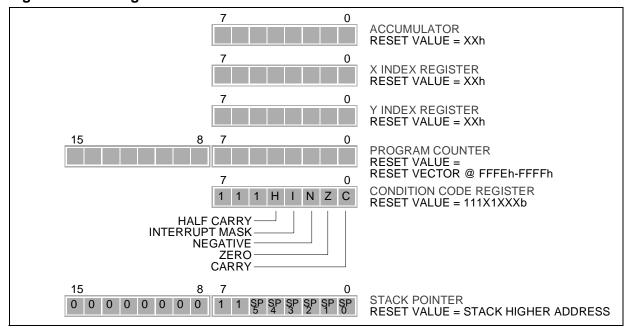

Figure 5. CPU Registers

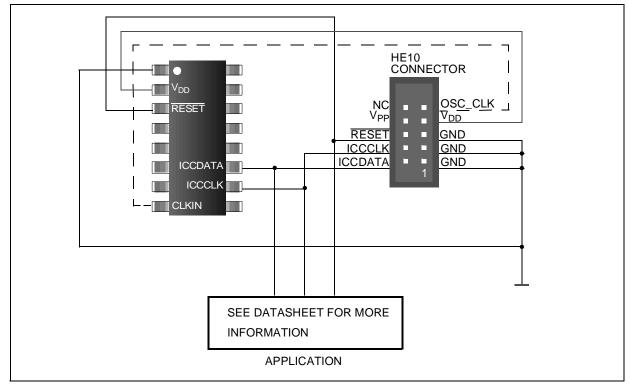

Figure 6. Typical In-Circuit Programming Interface

47/

**Table 6. Port Implementation**

| Standard Ports      |   |   | Interrupt Ports                    |     |    |

|---------------------|---|---|------------------------------------|-----|----|

| (PA6:1, PB4, PB2:0) |   |   | (PA7, PA0, PB3, PB0, with Pull-Ups |     |    |

| Mode DDR OR         |   |   | Mode                               | DDR | OR |

| Floating Input      | 0 | 0 | Floating Input                     | 0   | 0  |

| Pull-Up Input       | 0 | 1 | Pull-Up Interrupt Input            | 0   | 1  |

| Open Drain Output   | 1 | 0 | Open Drain Output                  | 1   | 0  |

| Push-Pull Output    | 1 | 1 | Push-Pull Output                   | 1   | 1  |

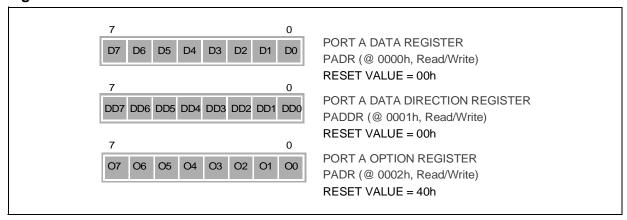

## Figure 7. Port A

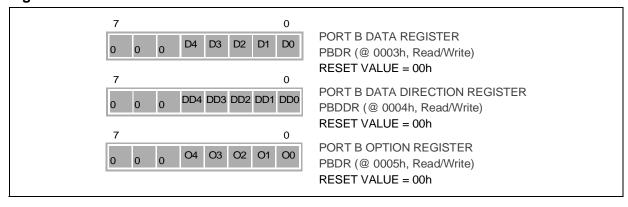

Figure 8. Port B

47/

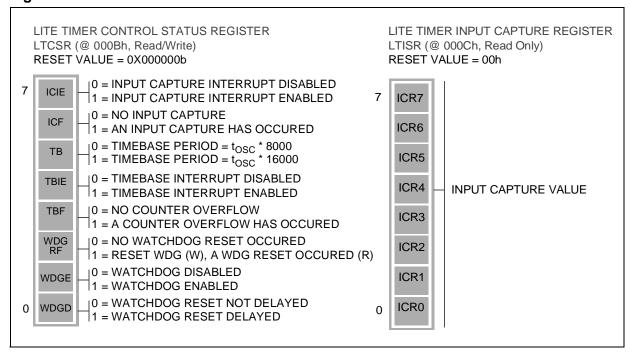

Figure 9. Lite Timer

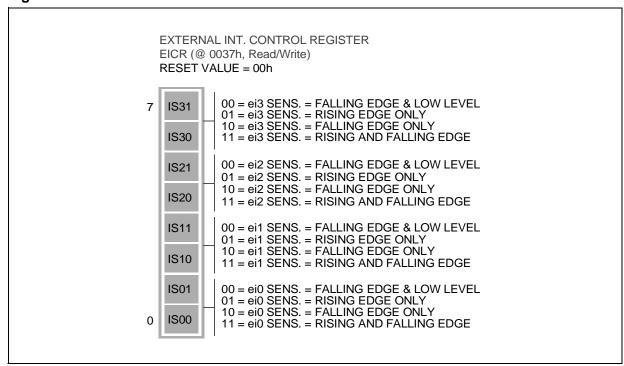

Figure 10. ITC

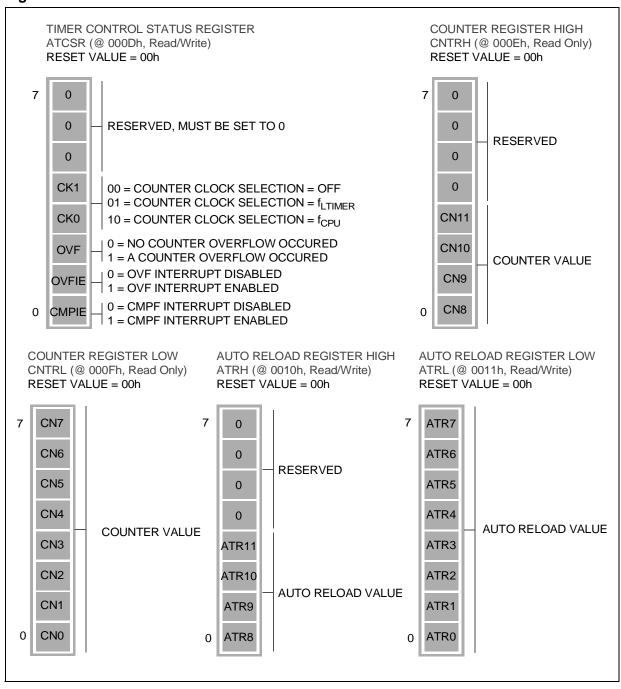

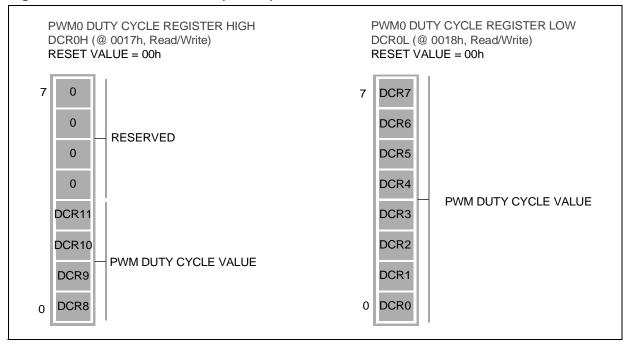

Figure 11. Auto Reload Timer

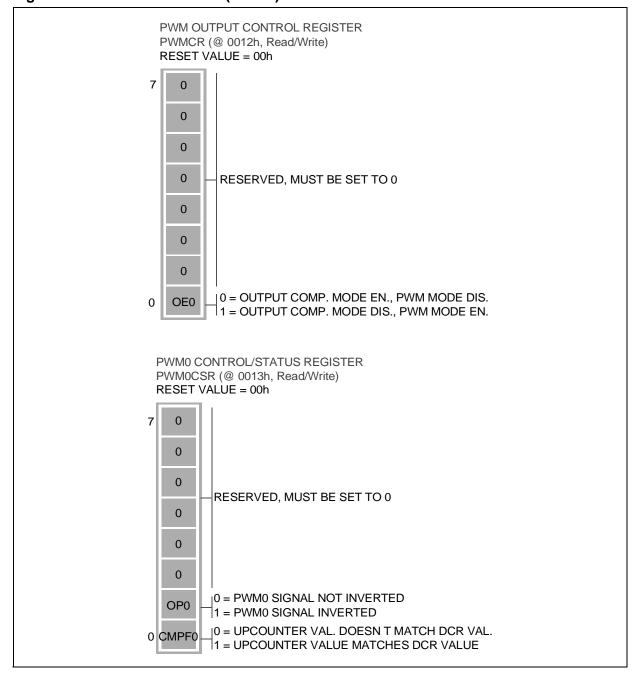

Figure 12. Auto Reload Timer (cont'd)

Figure 13. Auto Reload Timer (cont'd)

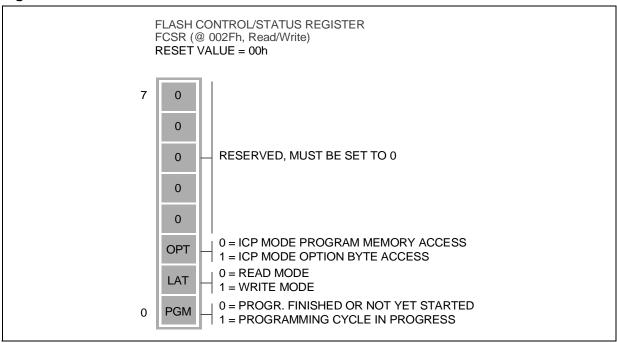

Figure 14. FLASH

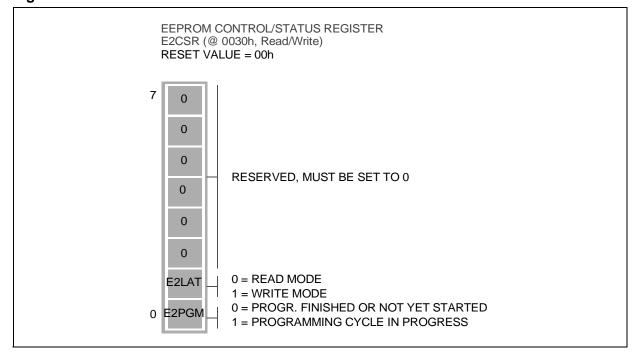

Figure 15. EEPROM

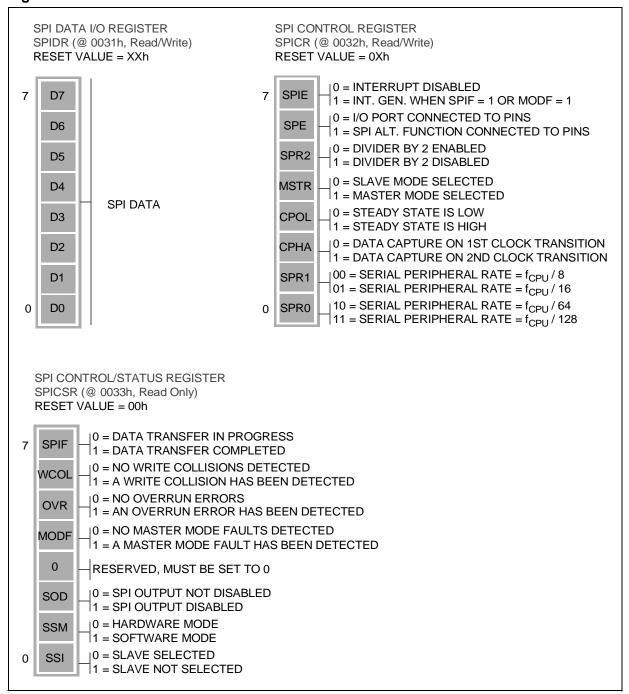

## Figure 16. SPI

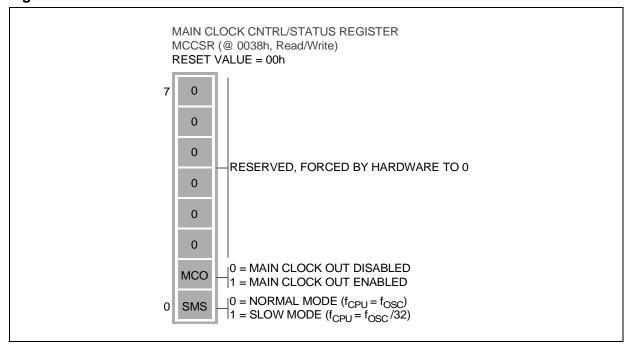

Figure 17. MCC

Figure 18. Clock and Reset

## Figure 19. ADC

"THE PRESENT NOTE WHICH IS FOR GUIDANCE ONLY AIMS AT PROVIDING CUSTOMERS WITH INFORMATION REGARDING THEIR PRODUCTS IN ORDER FOR THEM TO SAVE TIME. AS A RESULT, STMICROELECTRONICS SHALL NOT BE HELD LIABLE FOR ANY DIRECT, INDIRECT OR CONSEQUENTIAL DAMAGES WITH RESPECT TO ANY CLAIMS ARISING FROM THE CONTENT OF SUCH A NOTE AND/OR THE USE MADE BY CUSTOMERS OF THE INFORMATION CONTAINED HEREIN IN CONNEXION WITH THEIR PRODUCTS."

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without the express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics

©2003 STMicroelectronics - All Rights Reserved.

Purchase of I<sup>2</sup>C Components by STMicroelectronics conveys a license under the Philips I<sup>2</sup>C Patent. Rights to use these components in an I<sup>2</sup>C system is granted provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips.

STMicroelectronics Group of Companies

Australia - Brazil - Canada - China - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - U.S.A.

http://www.st.com