# AN1172 Application note

# A logic-level transient-voltage protected AC switch

#### Introduction

Home appliances such as washing machines, refrigerators and dishwashers employ a lot of low power loads such as valves, door lock systems, dispensers or drain pumps. Since these loads are powered by the mains in ON / OFF mode, they were initially controlled by relays. Recently, relays have been replaced by triacs, due to their smaller size and lower driving energy. Nevertheless triacs don't fulfill alone the new requirements that users now need and are used with others components.

Power switches must now be directly driven by a microcontroller unit (MCU) and must be robust to withstand the A.C. line transients so that systems may fall into line with electromagnetic compatibility (EMC) standards. ACSs (for Alternating Current Switches) have been designed with this goal mind, i.e. to offer logic level and more robust semiconductor devices.

On the other hand, ACSs have been developed adopting a functional integration approach. They can be used directly between a MCU and the load. An external protection or a buffer circuit are not required since these are already integrated on the die. This considerably reduces the overall electronic board size. Moreover, the array of ACSs allows one device to control the various loads typically required in a washer appliance.

*Table 1.* gives the RMS current of loads that can be controlled by ACS402-5SB4 or ACS108-5SA/N, in ON / OFF control mode.

Table 1. ACS108 and ACS402 targeted loads

| Load                                      | I <sub>RMS</sub> (A) | Power<br>Factor | (dl <sub>out</sub> /dt)c<br>(A/ms) | (dV <sub>out</sub> /dt)c<br>(V/µs) | Turn-off delay<br>(ms) |

|-------------------------------------------|----------------------|-----------------|------------------------------------|------------------------------------|------------------------|

| Door Lock                                 | <0.3                 | 1               | 0.15                               | 0.15                               | <10                    |

| Lamp                                      | <0.8                 | 1               | 0.4                                | 0.15                               | <20                    |

| Relay, Valve,<br>Dispenser,<br>Micromotor | <0.1                 | >0.7            | <0.05                              | <2                                 | <10                    |

| Pump                                      | <0.2                 | >0.2            | <0.1                               | <10                                | <10                    |

| Fan                                       | <0.6                 | >0.2            | <0.3                               | <10                                | <20                    |

Contents AN1172

# **Contents**

| 1 | ACS  | ACS triggering mode                     |  |  |  |  |  |

|---|------|-----------------------------------------|--|--|--|--|--|

|   | 1.1  | Negative gate current                   |  |  |  |  |  |

|   | 1.2  | New layout possibilities                |  |  |  |  |  |

| 2 | Indu | ctive loads on/off control5             |  |  |  |  |  |

|   | 2.1  | Valves and relays 5                     |  |  |  |  |  |

|   | 2.2  | Pumps and Fans ON / OFF control         |  |  |  |  |  |

| 3 | Resi | Resistive loads on/off control          |  |  |  |  |  |

|   | 3.1  | Inrush current                          |  |  |  |  |  |

|   | 3.2  | Transient junction temperature          |  |  |  |  |  |

|   | 3.3  | Light bulb flashover                    |  |  |  |  |  |

| 4 | Elec | Electromagnetic compatibility standards |  |  |  |  |  |

|   | 4.1  | IEC 61000-4-5 standard                  |  |  |  |  |  |

|   | 4.2  | IEC 61000-4-4 standard                  |  |  |  |  |  |

AN1172 ACS triggering mode

# 1 ACS triggering mode

### 1.1 Negative gate current

The ACS silicon structure is different from the triac one. For instance, the gate embeds a diode junction. Then the gate current can only circulate in one direction, from the COM pin to the Gate one. A peak reverse voltage (VGM) of this junction is also defined in the ACS data sheet.

In order to sink a current from the gate by a microcontroller output port, the supply voltage positive terminal must be connected to the drive reference, i.e. the COM pin of ACSs (see *Figure 1.*).

An interesting benefit of such a connection is that the ACS is not fired when the MCU is at reset state. Indeed, in this case, all the MCU port pins are at high level. This means that the gate resistors are all connected to the COM terminal. No spurious triggering can then occur.

It should be noticed that for a direct switch / MCU connection, the MCU current capability is not the only point to check to decide if the buffer circuit can be removed. Actually, the transistor, used to amplify the MCU current in order to control the gate, also play an overvoltage protection role. Annex B gives the gate voltage limits between which the MCU output port will be not stressed. It is also shown that with ACSs, the gate voltage remains inside these limits even with worst cases of dl/dt gradients at turn-on.

0 **AC MAINS** Valve / PUMP Ν etc. lout G Com Vg Vdd М1  $\bigwedge$  D1 R M2 D2 Vss **MCU**

Figure 1. Gate / MCU connection

ACS triggering mode AN1172

## 1.2 New layout possibilities

It has already been said that ACS silicon structure is different from the triac, according to the gate operation. A second difference is that ACS have been developed in an integration goal.

To allow different cells to be associated in one single package or controlled by one single drive die, the common drive reference voltage must be connected to the back of the die. Indeed, each die bottom is electrically linked to the other ones by the frame. This is achieved by the ACS silicon structure, where an integrated level shifter allows both thyristors to be controlled by means of a gate voltage referenced at the back of the die (COM pin). (See *References*, 1.).

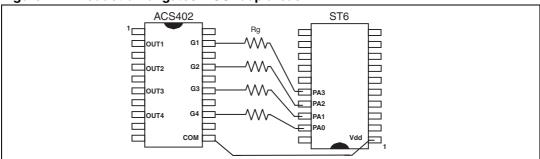

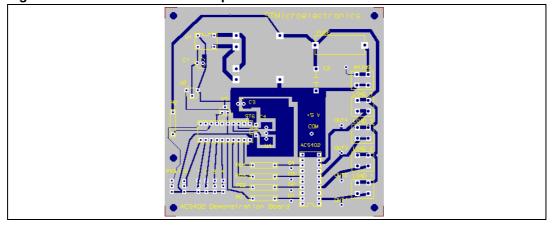

Thanks to ACSs arrays, the copper tracks count is reduced since the different COM pins are connected together inside the package. This also allows smaller gate / MCU copper tracks loop areas, and so increases the EMI immunity of the overall electronic board. *Figure 2*. shows an example of connection between an ACS402-5SB4 and an ST62xx, both in DIL20 packages.

Figure 2. Reduction of gate / MCU loop areas

A particular benefit of such a pin out appears with Surface Mount Devices (SMD). In this case, the tab pin is the COM one. The copper surface used to perform a heat-sink can then be used as a supply voltage bus. It allows new layout possibilities and, above all, a miniaturization of the Printed Circuit Board (PCB). Indeed, unlike triacs, the heat-sink areas are at the same voltage and so can be regrouped (see *Figure 3*.). The heatsink area therefore depends on the maximum amount of dissipated power at the same time, by all the switches put on it. So, the number of switches which will conduct at the same time and their conduction time should be known.

PCB required for ACSs

PCB required for Triacs

Figure 3. Printed circuit area reduction thanks to ACSs in SOT223 packages

## 2 Inductive loads on/off control

### 2.1 Valves and relays

#### 2.1.1 Turn-off overvoltages are clamped by ACSs

Valves and relays are both electromagnetic systems. In the case of AC high voltage operation, their windings present a high series resistance (a few  $k\Omega$ ) and a high series inductance (tens of Henry). Hence, they absorb a low RMS current (typically, 10 to 50 mA). In this case, the current rate of decrease is low and an automatic switch turn-off may result, when its current becomes lower than the holding level (see *References*, 2.). There may be an over-voltage due to the fact that there is still some current through the inductive load. The inductive energy thus creates a back electromotive voltage which tends to force the switch to conduct. If this over-voltage is not clamped, it can exceed the device breakdown level and damage it.

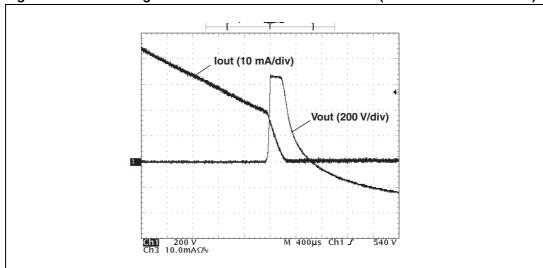

ACSs are over-voltage self-protected. They can sustain their holding current in such an operating mode, as shown in *Figure 4*.

Figure 4. ACS voltage and current waveforms at turn-off (230 V 35 mA RMS valve)

During clamping periods, the inductive energy is dissipated both in the silicon die and the series resistance of the load. The worst case appears when the load inductance is the highest, i.e. for electromagnet loads.

In annex C, a theoretical analysis is performed with a 0.1 power factor load and an RMS current lower than 40 mA (value which never appears in practice where, for such RMS currents, the power factor is always higher than 0.7). Then, it is demonstrated that, even in this worst case scenario, the transient junction temperature remains below  $160^{\circ}$ C. And the clamping period time ( $t_{cl}$ ) always lasts less than 1 ms. Such a thermal stress is suitable for ACSs dies thanks to their reliable planar technology.

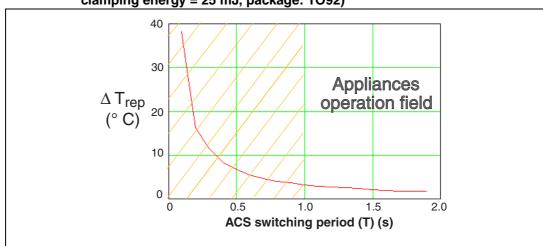

#### 2.1.2 Maximum switching frequency

As far as thermal management involving clamping phases is concerned, a maximum load commutation frequency must be defined to avoid excessive device heating. *Figure 5.* gives the maximum supplementary temperature rise due to recurrent clampings, versus the ACS switching period (see *Appendix C*). This value is given for a 230 V - 50 Hz mains voltage (110 V mains is less stressing), for the worst case of load (power factor = 0.1, peak load current =  $i_H$  max) and for the maximum  $V_{CL}$  and  $i_H$  values (800 V and 60 mA respectively). In this case, the energy absorbed by the die equals 25 mJ.

The chosen package is the TO92 one (ACS108-5SA device) because it presents the highest Rth value, among ACS packages on offer (DIL20, TO92, SOT223, DIL8).

It can be seen that this temperature elevation can be neglected (<  $4^{\circ}$  C) as long as the control frequency is less than one Hertz. Such a value is suitable for most appliance applications where loads are at most controlled once per second. For that reason, in ACS data-sheets, the maximum allowed current is given for a 1 Hertz maximum frequency 0.1 minimum load power factor. Turn-off dissipated power is then reviewed for a wide range of application needs.

This enables us to conclude that no varistor is needed across ACSs to clamp the loads inductive energy at turn-off, even with electromagnets which are the highest inductive loads in Appliances.

Figure 5. Supplementary temperature elevation due to repetitive clampings (@ clamping energy = 25 mJ, package: TO92)

## 2.2 Pumps and Fans ON / OFF control

#### 2.2.1 Application requirements for (dl/dt)c and (dV/dt)c

There is a higher risk that a triac or an ACS will fail to turn-off when both the load current rate of decrease and the reapplied voltage rate across the device are steep (see References, 3.). This risk increases as the junction temperature increases. The maximum current decreasing rate that ACS can switch off, called (dl/dt)c is defined for a maximum reapplied voltage rate, called (dV/dt)c, and for its maximum  $T_i$ .

Pumps and Fans are, for the most part, induction or permanent magnet motors. Their series inductance is in the range of one Henry, and their winding resistance equals a few hundred Ohm. Their power factor is low. Hence, after switch turn-off, the reapplied voltage across it is high and appears with a high rate of increase (as described in *Equation 1* where L and cosp are the inductance and power factor of the load, V the mains RMS voltage and C is the ACS capacitance value).

#### **Equation 1**

$$\left( dV \, / \, dt \right) c_{(V/\mu s)} \cong V_{(V)} \sqrt{2} \sin \phi \, \frac{10^{-6}}{\sqrt{L_{(H)} C_{(F)}}} \label{eq:constraint}$$

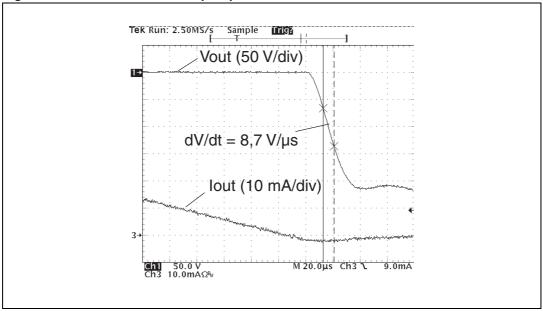

*Figure 6.* shows that the (dV/dt)c rate for an ACS402-5 die without any snubber, controlling a 230 V 220 mA pump, is lower than 10 V/ $\mu$ s. The measure will be similar with an ACS108-5 die because it presents the same capacitance value as an ACS402-5.

*Equation 2* shows that the current rate of decrease is almost half the RMS current (0.44 ratio for a 50 Hz mains frequency and 0.53 for 60 Hz).

#### **Equation 2**

$$\label{eq:continuity} \left(dI/dt\right)\!c_{(A/ms)} \cong \sqrt{2}\;I_{RMS(A)}2\pi\;f_{(Hz)}10^{-3}$$

To summarize, it can be said that the worst case commutation appears with pumps or fans. In this case, the stress that ACSs must withstand is:

#### **Equation 3**

$$\begin{cases} \left(dI/\,dt\right)c_{(A/ms)}\cong 0.5\ I_{RMS(A)}\\ \left(dV/\,dt\right)c\leq 10\ V/\mu s \end{cases}$$

#### 2.2.2 ACS asymmetrical turn-off behavior

As shown in Figure 7., ACSxxx-5 behaves differently depending on the current direction before switch-off. This asymmetrical behavior is very lower for ACSxxx-6 and ACS110/ACS120 devices where the (dl/dt)c parameter is guite similar for both polarities.

(dl/dt)c (mA/ms) 800 700 lout>0 lout<0 600 500 400 300 0 200 0 100 2 4 8 6 10 12 (dVdt)c (V/µs)

ACS402-5 and ACS108-5 (dl/dt)c typical ability versus reapplied (dV/dt)c Figure 7. rate @ Tj = 110°C

For a 200 mA RMS current pump (see case 1 in Figure 7.), the turn-off will be performed whatever the current sign is. The maximum turn-off delay is then one half-cycle (10 ms for 50 Hz mains frequency).

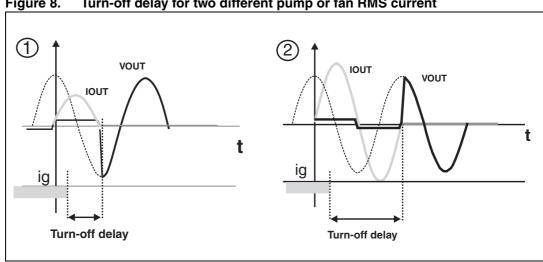

On the other hand, for a 200 - 600 mA RMS pump (see case 2 in Figure 7.) and for a 110° C junction temperature, the switch-off will only be achieved when the current reaches zero with a negative sign. Therefore, in this case, the turn-off delay time can reach up to 20 ms for 50 Hz line frequency (Figure 8.).

Figure 8. Turn-off delay for two different pump or fan RMS current

### 3 Resistive loads on/off control

#### 3.1 Inrush current

In most systems, resistive loads are thermal effective. For example, light bulbs emit light when their filament is hot enough. New types of door-lock actuators have emerged in which the bolt move is due to a thermal expansion of a metallic part or a wax.

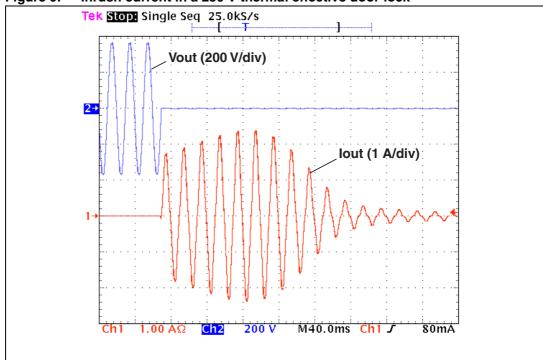

All these loads can be characterized by a very low resistance value in cold state. Consequently, when the switch is turned on, there is a high inrush current. For low power light bulbs, the inrush current lasts on average 10 ms. The worst scenario is in the case of thermal door-locks. *Figure 9.* shows a typical inrush current in such loads.

Figure 9. Inrush current in a 230 V thermal effective door-lock

# 3.2 Transient junction temperature

With such current shapes at turn-on, thermal calculation must be carried out in order to choose the right package or heat-sink so as to avoid exceeding the maximal junction temperature (110° C).

To perform the calculus, the current shape must be simplified. Let us work on the hypothesis that the current average waveform of *Figure 9*. is similar to a 2 A peak 0.18 s time long sinus shape.

Then, the average conduction and gate current losses in the ACS are given by the following relationship:

#### **Equation 4**

$$P_{av} = r_{d} I_{RMS}^{2} + V_{t0} I_{RMS} \frac{2\sqrt{2}}{\pi} + V_{gt} I_{g}$$

Then, according to ACS108-5 or ACS402-5 specifications, we find:  $P_{av}$  = 1.76 W.

For a  $t_p$  long dissipated power pulse, the peak junction temperature ( $T_{j peak}$ ) is given by *Equation 5*, where  $T_{io}$  is the initial  $T_{i}$  value.

#### **Equation 5**

$$T_{j peak} = T_{jo} + Zth(t_p) \cdot P_{av}$$

Since the thermal impedance values at 0.18 s for TO92 and DIL20 packages are 22.5 and 8° C/W respectively, it can be said that the junction temperature elevation, at the end of the inrush current period, is 40° C for a TO92 package and 14° C for a DIL20 package.

So, the maximal junction temperature before door lock switch-on should be at most 96° C for ACS402-5SB4 (DIL20) and 70° C for ACS108-5SA (TO92), in order to keep  $T_{j peak}$  below  $T_{j max}$  (110 °C).

For washing systems, as the door lock start may appear at the beginning of a washing cycle, we suppose that  $T_{jo}$  equals at worst the maximal ambient temperature, i.e.  $70^{\circ}$  C. So, in this respect, both ACS devices are convenient for door lock operation.

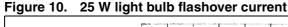

# 3.3 Light bulb flashover

Another point should be highlighted when driving a light bulb with a silicon switch. Indeed, at the lamp life time end, the filament breaks itself. This results on a flashover across the gas, included in the bulb. Then, the overall filament can be can short circuited by the flashover, and the load current is not limited. *Figure 10.* gives the typical overcurrent measured when a 25 W lamp fails. This current can exceed the i<sup>2</sup>.t capability of the ACS and destroy it.

To avoid destroying the ACSs at each lamp flashover, a power resistor can be added in series with the light.

This resistor (R) is rated in order to limit the ACS current to its  $I_{TSM}$  value (10 A for a 10 ms half sinus conduction). R is calculated as following:

#### **Equation 6**

$$R = \frac{230\sqrt{2}}{10} = 33\,\Omega$$

The power dissipated by the resistor is linked on the load RMS current, and so on the load power  $(P_L)$ . Here we have :

#### **Equation 7**

$$P = R \cdot (P_L / V)^2 = 33 \times (25 / 230)^2 = 0.39 W$$

A 33  $\Omega$  1/2 W resistor is sufficient.

*Figure 11.* gives the overcurrent measured with such a resistor during the flashover of a 25 W light bulb.

Figure 11. Flashover current limited by a 33  $\Omega$  1/2 W resistor

# 4 Electromagnetic compatibility standards

#### 4.1 IEC 61000-4-5 standard

#### 4.1.1 Standard requirements

The IEC 61000-4-5 standard has been established to check if systems can always work after there has been a voltage surge super-imposed to the mains. A standard voltage waveform has been chosen which embodies typical over-voltages due to thunder or disconnection of running inductive loads from the line.

Two kinds of surges must be applied:

- 1. **Line to Ground surge:** in this case the maximum voltage surge is 4 kV (for aerial power network), but the energy is absorbed by the Y2 capacitors (connected between lines and ground) of the mains filter.

- 2. **Line to Neutral surge:** in this case the maximum voltage surge is 2 kV (for aerial power network, N.B: 1 kV is required for public power network) and is applied across the power device and the load controlled by this one.

A Line to Neutral over-voltage is then:

- entirely absorbed by the load if the power switch is ON;

- 2. entirely held by the semiconductor device if it appears while the switch is at off-state.

As the Line to Neutral surge can appear at peak mains voltage, the overall amount of voltage can reach 2.4 kV. This will be higher than the break-down level of the silicon devices used in appliances. Then, in order to prevent components destruction, designers use a varistor connected across silicon devices. The overvoltage is limited below the breakdown level of the power semiconductor and the surge energy is absorbed by the metal-oxyde component.

#### 4.1.2 ACS behavior during IEC 61000-4-5 test

When a surge appears when an ACS is OFF, the mains over-voltage is first clamped by the device. But an excessive energy surge can raise the ACS current above its breakover level. Then, the switch turns on in break over mode. Such an event is particularly stressful on the semiconductor especially so if the current and its rate of increase are both high. The worst case occurs for ACS driving low resistance, non inductive loads.

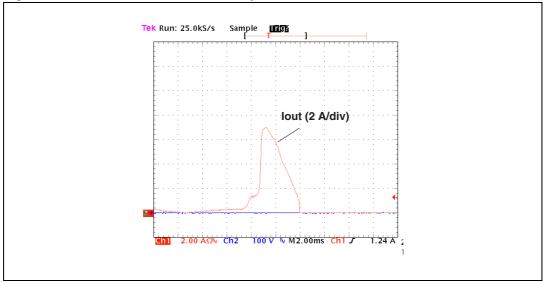

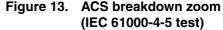

For example, *Figure 12*. and *Figure 13*. have been recorded with a thermal active door lock system at low temperature. The 2 kV surge is super-imposed to the 230 V - 50 Hz mains and synchronized with its peak value, as shown on *Figure 12*. *Figure 13*. highlights the device turn-on in this mode. As the load was previously off, its resistance is cold and equals 150  $\Omega$ . In this case, the current rises at a rate of 100 A/ $\mu$ s and reaches 15 A. Such transient surges would damage triacs, but not ACSs which are designed to turn-on in breakover mode. No more varistor is then needed in parallel across ACSs unlike triacs. The difference between ACS and Triac + Varistor is that, with the ACS, the load is switched on during a half or one mains cycle. This can be accepted as such events happen a few times in the system's life.

Reliability tests are carried out on production batches to check the ACS robustness towards IEC 61000-4-5. A standard surge generator is used directly across a load and an ACS. The load is a 150  $\Omega$  resistor, including a 3  $\mu$ H parasitic inductance, to simulate a cold door-lock.

The applied surge is fixed at +/- 2,4 kV in order to be equivalent to a 2 kV over-voltage applied at the peak mains voltage, with the same bias.

Figure 12. 2 kV surge on the mains (IEC 61000-4-5 test)

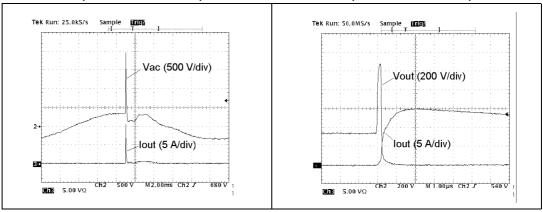

#### 4.2 IEC 61000-4-4 standard

#### 4.2.1 2.1: Standard requirements

For IEC 61000-4-4 tests, two different stressing ways are demanded. One is to apply the bursts to the Line, Neutral or Ground through 33 nF capacitors. In this case, the bursts are entirely absorbed by the mains filter, which is always present at the input of electronic systems. The second IEC 61000-4-4 stressing mode is to apply the bursts through a typical 100 pF capacitor (realized by an aluminum sheet), directly to the I/O ports of the system.

The I/O port test is in fact required for systems where there are control wires, as for computers (wires between keyboard and central unit). But appliance manufacturers apply similar test to check if their products can withstand fast voltage transients.

The standard requires that for burst voltages up to 2 kV, the system must operate without problem. However, triacs can then turn-on due to high dV/dt rates. In this case, a snubber must be added to smooth these rates. Designers must then manage with the following trade-off:

- Reduce dV/dt rates: the snubber capacitance must be high and the snubber resistance must be low;

- 2. **Reduce the dl/dt rate at turn-on:** the snubber capacitance must be low and the snubber resistance must be high.

#### 4.2.2 Snubber removal thanks to ACSs

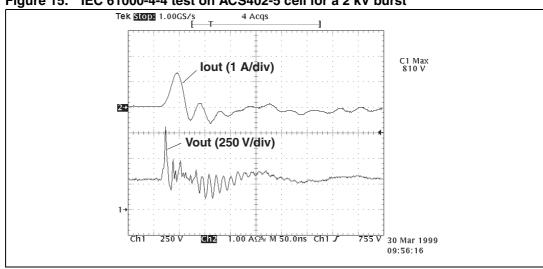

I/O tests have been carried out on an electronic board including an ACS402, where the gates are short-circuited to the COM in order to avoid parasitic turn-on due to MCU bad operations. The system under test is embodied by this board. The I/O wires are then the OUT pins of each ACS cell (which are connected to the loads), plus the Line and Neutral wires. The trial diagram is shown in *Figure 14*.

5/

Figure 14. IEC 61000-4-4 test synopsis

Figure 15. shows the OUT-COM voltage measured during a 2 kV IEC 61000-4-4 test (N.B.: 1 kV is required for public power network). We see that in spite of capacitive current due to high dV/dt rates, the ACS does not turn-on. The semiconductor switch withstanding to IEC 61000-4-4 depends on its dV/dt capability. ACS devices present dV/dt characteristics ten times greater than both same current and sensibility ratings triacs. For example, a 10 mA maximum 0.2A  $i_{ct}$  ACS has a minimum dV/dt capability of 500 V/ $\mu$ s (@  $T_i$  = 110 °C).

It can also be seen that the ACS voltage overflows its breakdown value given for a 50 Hz sine wave (810 V is reached in spite of 650 V breakdown value). In fact, the voltage rate of increase is so high that the silicon device has not enough time to begin to clamp. A higher value than its  $V_{CL}$  value can then be reached.

Figure 15. IEC 61000-4-4 test on ACS402-5 cell for a 2 kV burst

To sum up, it can be said that ACSs, thanks to their high dV/dt capability, improve the overall electronic board robustness towards fast line transients without any snubber. But it must be kept in mind that the mains filter Y2 capacitors play also a role in sustaining IEC 61000-4-4 tests, by derivating some part of the bursts energy. The typical values of these capacitors are 2.2 nF.

AN1172 Conclusion

# Conclusion

ACS retains the well-known advantages of the triac (high AC voltage blocking capability, current bidirectionality) and adds high over-voltage robustness and the increased reliability and compactness that appliance manufacturers now need.

Thanks to the clamping capability and robust break-over characteristics of the ACS structure, the protection circuits that are usually connected in parallel with the triacs, are no longer required. The varistor removal increases automatically the reliability of the electronic board. And the snubber removal allows designers to be free with the dV/dt at off state and dl/dt at turn-on trade-off when choosing an R-C circuit.

In addition, the triac gate-drive transistor and its associated resistors are also redundant because ACS devices have built-in logic level drive circuits that allow the power switch to be safely driven from any MCU output pin capable of sinking 20 mA without over-stressing the micro-controller output.

Hence, the typical component count falls from eight with triacs, down to two with ACSs (see *Figure 16*.).

The new ACS devices represent a real breakthrough in the design of power switches for home appliances. The enhanced performance, for example their robust off-state and logic level drive, allied to their inherent compactness will open new perspectives in the design of compact and reliable electronic power controllers.

ACS VCC MCU MCU

Figure 16. Component count reduction thanks to ACS

# References

- 1. P.Rault, "Triacs for Home Appliances: present and future", PCIM forum, Honk Kong, pp. 57-65, 1998.

- E.Leblanc, "Thyristors and Triacs, an Important Parameter: the Holding Current", Application Note n°302, STMicroelectronics, February 1989.

- 3. P.Rault, "Improvement in the Triac commutation", Application Note n°439, STMicroelectronics, May 1992.

- 4. SCR Manual, General Electric, 6th Edition, 1979.

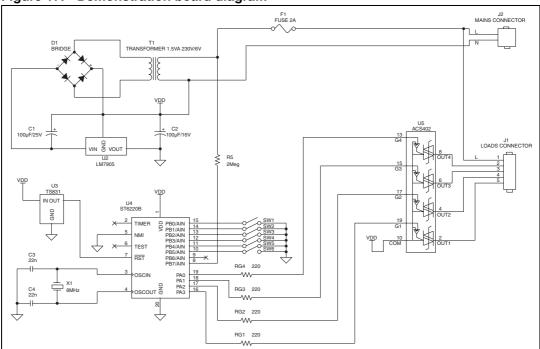

#### **Appendix A ACS402 demonstration Board**

Figure 17. shows the electronic diagram of a demonstration board used to illustrate ACS402 / ST6 compatibility. Note that the reset, power supply and oscillator circuits are given as examples. Other solutions are also possible. For instance, ST6 and ST7 microcontrollers with integrated reset circuits can be used.

The main features are:

- V<sub>DD</sub> is connected to the Neutral;

- $V_{DD}$  is the reference voltage of each ACS402 cell, which are all connected together in the DIL20 package;

- each ACS402 cell is driven directly from a Port A I/O pin, which can sink up to 20 mA.

Figure 17. Demonstration board diagram

Figure 18. Demonstration board printed circuit

# Appendix B ESD diode conduction due to kick-back

An over-voltage can appear across the gate and COM (or A1 for triacs) terminals at high turn-on di/dt rates. This effect is called the "kick-back". It is due to the high density current at turn-on which causes high conduction voltage drop. Since the conduction begins around the gate area, the forward voltage is in part applied to the gate.

This gate spike is clamped by the micro-controller internal electrostatic discharge (ESD) diodes, which can be damaged if conduction lasts for too long.

In order to prevent ESD diodes conduction, their voltage must remain negative. When considering *Figure 1*. at ACS turn-on, i.e. when the push transistor M1 is off and the pull transistor M2 is on, a circulating current will never occur through D2 if the current  $i_R$  remains positive. This yields *Equation B1*.

#### **Equation B1**

$$R \cdot I_R = -V_{M2} + V_S + V_q > 0$$

As M2 is conducting, its voltage drop can be neglected. Thus, the previous relation gives:

#### **Equation B2**

$$V_a > -V_S$$

If D1 conducts, this means that the supply voltage is held by M2, neglecting D1 drop voltage. This MOS transistor is thus in a linear mode. Its current equals its saturating level, called  $i_{sat}$ .

Now, since  $i_{sat}$  current is necessarily higher than the  $V_s/R$  ratio (in order to secure the microcontroller operation), we can write the following relationship:

#### **Equation B3**

$$V_{D1} = V_g - R \cdot i_{sat} < V_g - V_S$$

A sufficient condition to ensure that VD1 remains below zero is that  $V_g$  remains below  $V_s$ . This condition, plus *Equation B2*, gives the following safety rule for no ESD diode conduction:

#### **Equation B4**

-

$$V_S < V_g < +V_S$$

Vg (5 V/div)

+5 V

lout (5 A/div)-5 V

dl/dt = 110 A/μs

lout (5 A/div)-5 V

LA2 (5 A/div)

LA2 (5 A/div)

LA2 (5 A/div)

LA3,5 V

LA4 (5 A/div)

LA5 V

LA5.00 AΩN S00ns Ch4 3.33 A

Figure 19. Kick-back test with ACS402 Figure 20. Kick-back test with Z0109 triac

To compare the kick-back effect of triacs and ACSs, a special test circuit has been defined. It consists on turning on the switch with a 10nF capacitor connected directly across the A1-A2 or OUT-COM terminals. The capacitor is charged at 300 V. *Figure 19.* and *Figure 20.* show the experimental results obtained with such a testing method, for a positive bias voltage.

A Z0109 (0.8 A IRMS 10 mA igt ST triac) doesn't fulfill with *Equation B4*, for  $V_{GA1}$  voltage reaches 13.5 V with a 65 A/µs dl/dt rate. This is largely above the supply voltage. With the ACS402, the maximum  $V_g$  voltage is 1.5 V, and is still within the limits of *Equation B4* despite a dl/dt which is twice as big as with the Z0109.

ACS / MCU interface would then be secured even at turn-on at peak mains voltage or on a short-circuit.

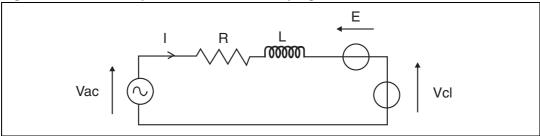

# Appendix C How to calculate the junction temperature during clamping periods

### C.1 Dissipated power evaluation

It should be kept in mind that the load inductive energy is not entirely absorbed by the die at clamping. Another part is dissipated by the Joule effect in the load resistor or absorbed by the mains. A way to accurately evaluate the clamping energy is then to estimate the ACS current waveform, versus the time. The energy is then calculated by integrating this waveform and the product of the clamping voltage along the turn-off period.

Figure 21. Electric equivalent circuit at clamping

Let us consider a typical AC load equivalent circuit shown in *Figure 21*. The load current during the clamping time is given by the following relationship.

#### **Equation C1**

$$i(t) = \frac{V_{cl} + E - Vac}{R} \left( e^{-\frac{R}{L}(t-t_0)} - 1 \right) + i(t_0) \cdot e^{-\frac{R}{L}(t-t_0)}$$

It is difficult to evaluate the influence of E in a general way. Its sign depends on its phase towards the current and the value of the holding current. But, it can be said that the back electromotive force has little influence for most universal and synchronous motors in which impedances are high and E is close to zero. Furthermore, for all other loads, such as passive loads or asynchronous motors, the b.e.m.f E is null. For this reason, let us neglect its value. Let  $\cos \phi$  be the load power factor and V the RMS mains voltage. Since the clamping occurs near the zero crossing current, the value of the main voltage at  $t_0$ , for a positive current, is given by the relationship C.2.

#### **Equation C2**

$$Vac = -V_{\sqrt{2 \cdot |1 - \cos^2 \varphi|}}$$

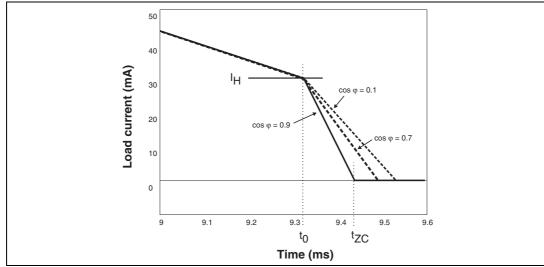

Figure 22. shows the current waveforms calculated with such an hypothesis, and assuming that the holding current does not depend on the current rate of decrease. The junction temperature influence on the  $i_H$  and  $V_{cl}$  levels is also not considered. Then,  $i(t_0)$ , in Equation C1, is equal to the  $i_H$  value given for a 25°C junction temperature (ex: around 30 mA for an ACS402-5 or an ACS108-5). The ACS clamping voltage is taken equal to 700 V. Calculations are carried out for 100 mA RMS loads with different power factors, and for a 230 V 50 Hz mains voltage.

Figure 22. Current waveform during clamping phase for 100mA / 230V RMS loads

Considering *Figure 22*., we can see that the load current is always inferior to a linearly decreasing current beginning at  $(i_H, t_0)$  point and ending at  $(0, t_{ZC})$ . Furthermore, the temperature elevation due to a rectangular power pulse is always superior to the one due to a decreasing triangular power pulse of same average value (see *References*, 3.).

So, a pessimistic way to calculate the junction temperature is to simplify the clamping losses shape by a constant power pulse of  $V_{cl}.I_H/2$  value and  $t_{ZC}-t_0$  time long. The energy absorbed by the die during a clamping event ( $E_{CL}$ ) depends on two ACS parameters ( $V_{cl}$  and  $I_H$ ) and on the clamping duration:

#### **Equation C3**

$$\mathsf{E}_{\mathsf{CL}} = \frac{1}{2} \mathsf{V}_{\mathsf{cl}} \, \mathsf{I}_{\mathsf{H}} \, \big( \mathsf{t}_{\mathsf{ZC}} - \mathsf{t}_{\mathsf{o}} \big)$$

# C.2 Transient maximum junction temperature

The clamping time is given by *Equation C1*, which gives way to the following one.

#### **Equation C4**

$$t_{zc} - t_0 \frac{L}{R} ln \left[ 1 + \frac{R}{V_{cl} + E - Vac} i_H \right]$$

Neglecting the on-state dissipated power in front of clamping dissipated power, the junction temperature rise at the end of the clamping phase is:

#### **Equation C5**

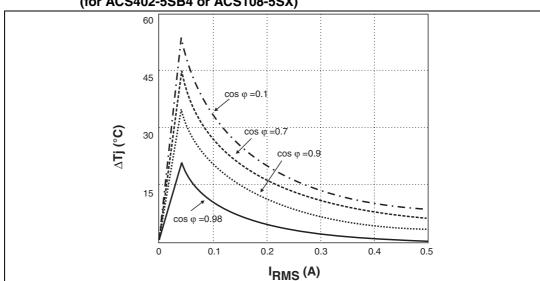

$$\Delta T_{j} = Zth(t_{zc} - t_{o}) \cdot \frac{1}{2} V_{cl} I_{H}$$

Figure 23. shows the maximum  $\Delta T_j$  reached for different load RMS currents and power factors. Calculations are similar whatever the package is (TO92, DIL20, SOT223), because in such a range of times, the Zth is only due to the die area.

Note that  $\Delta Tj$  first increases. On this curve part, the load peak current is lower than the  $i_H$  level (taken equal to its worst value: 60 mA). So, when the load RMS current increases, the turned-off current increases too. When the load peak current becomes higher than  $i_H$ ,  $\Delta T_j$  decreases because of the load series inductance decrease (here the turn-off current is constant and equals  $i_H$ ).

Figure 23. Supplementary temperature rise at clamping depending on load nature (for ACS402-5SB4 or ACS108-5SX)

It can be concluded that, if the junction temperature was 110° C before turn-off, the maximum transient temperature can reach 160° C. As these events last less than one ms (refer to *Figure 22*.), such junction temperatures can be permitted.

# C.3 Repetitive clampings

To evaluate heating due to repetitive clampings, *Equation C6* can be used, assuming that the clampings occur at a constant period T and that the conduction losses can be neglected in front of the previous ones.

#### **Equation C6**

$$\Delta T_{\text{rep}} = \frac{1}{2} V_{\text{cl}} I_{\text{H}} \cdot \left[ \frac{t_{\text{ZC}} - t_0}{T} Rth + \left( 1 - \frac{t_{\text{ZC}} - t_0}{T} \right) Zth(T + t_{\text{ZC}} - t_0) - Zth(T) + Zth(t_{\text{ZC}} - t_0) \right]$$

In practice T (above 1s) is very much higher than the clamping duration. *Equation C6* can then be simplified to the following one.

#### **Equation C7**

$$\Delta T_{\text{rep}} = \frac{1}{2} \, V_{\text{cl}} \, I_{\text{H}} \cdot \frac{t_{\text{ZC}} - \, t_{\text{0}}}{T} \, \text{Rth}$$

Revision history AN1172

# **Revision history**

Table 2. Document revision history

| Date        | Revision | Changes                                                                                                                   |

|-------------|----------|---------------------------------------------------------------------------------------------------------------------------|

| 10-Jun-1999 | 1        | Initial release.                                                                                                          |

| 11-May-2006 | 2        | Reformatted to current standard. <i>Figure 1.</i> , <i>Figure 6.</i> , <i>Figure 17.</i> , and <i>Figure 18.</i> updated. |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZE REPRESENTATIVE OF ST, ST PRODUCTS ARE NOT DESIGNED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS, WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2006 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com