# HOW TO MINIMIZE THE ST7 POWER CONSUMPTION

By MCD Application Team

# **1 INTRODUCTION**

The purpose of this document is to explain the different low power modes available on ST7 devices and the ways to minimise power consumption. Many applications will have strict power requirements, and there are several methods of lowering the rate of power consumption without sacrificing performance. Calculating the predicted power use is important to characterize the system's power supply requirements. The ST7 can be put into one of several low power modes by setting some bits in some registers. The utility of these low power modes depends on the specific application.

The basic explanation of this note is based on ST72F324, but is applicable to all ST7 general purpose devices. Please refer section "Examples" to see more information on additional devices (ST7FLITE0).

# **2 POWER CONSUMPTION FACTORS**

CMOS digital logic device power consumption is affected by supply voltage and clock frequency. These parameters can be adjusted to realize power savings, and are readily controlled by the designer. In CMOS digital logic devices, power consumption is directly proportional to clock frequency and power supply squared.

# $power = CV^2 f$

where: C is CMOS load capacitance, V is supply voltage, and f is clock frequency.

The amount of current used in CMOS logic is directly proportional to the voltage of the power supply. Thus, power consumption may be reduced by lowering the supply voltage to the device. Power consumption depends on the number of active peripherals. The greater the number of active peripherals, the more power will be consumed. Power consumption also depends on, whether the oscillator is On or Off and whether the CPU is On or Off. It also depends on PLL On/Off, CSS enabled/disabled and LVD On/Off.

Power Consumption is based on which mode a particular application is running. For example, in ST7, "HALT" mode is the lowest power consumption mode without availability of Real Time Clock and "ACTIVE-HALT" mode is the lowest power consumption mode with Real Time Clock available. To reduce the power consumption, clock frequency can be reduced whenever fast processing is not required by the application.

| 1 INTF | RODU                                                                                                                                           | CTION .                                                                                                                                                                                         |                                                                                                                                                         |                                                                                                                    | • • • •                               |      |             |               |       |         |                                       |                                       | •••                                   | •••                                                 | •••                                   | • • •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1                                                                                           |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|---------------------------------------|------|-------------|---------------|-------|---------|---------------------------------------|---------------------------------------|---------------------------------------|-----------------------------------------------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| 2 POV  | VER C                                                                                                                                          | ONSUM                                                                                                                                                                                           |                                                                                                                                                         | I FAC                                                                                                              | TOR                                   | S.   |             |               |       |         |                                       |                                       |                                       |                                                     | ••                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1                                                                                           |

| 3 POV  | VER N                                                                                                                                          | IANAGE                                                                                                                                                                                          | MENT                                                                                                                                                    | MO                                                                                                                 | DES                                   |      |             |               |       | • • • • |                                       |                                       |                                       |                                                     | • •                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4                                                                                           |

| 3.1    | STAN                                                                                                                                           | NDARD I                                                                                                                                                                                         |                                                                                                                                                         | ODE                                                                                                                |                                       |      |             |               |       | • • • • |                                       |                                       |                                       |                                                     | • •                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4                                                                                           |

| 3.2    | SLO                                                                                                                                            | N MODE                                                                                                                                                                                          |                                                                                                                                                         |                                                                                                                    |                                       |      |             |               |       |         |                                       |                                       |                                       |                                                     | • • •                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4                                                                                           |

| 3.3    | WAIT                                                                                                                                           | MODE                                                                                                                                                                                            |                                                                                                                                                         |                                                                                                                    |                                       |      |             |               |       |         |                                       |                                       |                                       |                                                     |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4                                                                                           |

| 3.4    | SLO                                                                                                                                            | N WAIT                                                                                                                                                                                          | MODE                                                                                                                                                    |                                                                                                                    |                                       |      |             |               |       |         |                                       |                                       |                                       |                                                     |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5                                                                                           |

| 3.5    | ACTI                                                                                                                                           | VE-HAL                                                                                                                                                                                          | т мог                                                                                                                                                   | DE.                                                                                                                |                                       |      |             |               |       |         |                                       |                                       |                                       |                                                     |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5                                                                                           |

| 3.6    | HAL                                                                                                                                            | r mode                                                                                                                                                                                          |                                                                                                                                                         |                                                                                                                    |                                       |      |             |               |       |         |                                       |                                       |                                       |                                                     |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5                                                                                           |

| 3.7    | SUM                                                                                                                                            | MARY.                                                                                                                                                                                           |                                                                                                                                                         |                                                                                                                    |                                       |      |             |               |       |         |                                       |                                       |                                       |                                                     |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 6                                                                                           |

| 4 EXA  | MPLE                                                                                                                                           | S                                                                                                                                                                                               |                                                                                                                                                         |                                                                                                                    |                                       |      |             |               |       |         |                                       |                                       |                                       |                                                     |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 6                                                                                           |

| 5 POV  | VER N                                                                                                                                          | IANAGE                                                                                                                                                                                          | MENT                                                                                                                                                    | TIPS                                                                                                               |                                       |      |             |               |       |         |                                       |                                       |                                       |                                                     |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 6                                                                                           |

|        |                                                                                                                                                |                                                                                                                                                                                                 |                                                                                                                                                         |                                                                                                                    |                                       |      |             |               |       |         |                                       |                                       |                                       |                                                     |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                             |

| 6 APP  | ENDI                                                                                                                                           | X A: ST7                                                                                                                                                                                        | 2F324                                                                                                                                                   | STA                                                                                                                | NDA                                   | RD E | EXAN        | /PLE          | ES    |         |                                       |                                       |                                       |                                                     |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7                                                                                           |

|        |                                                                                                                                                | X A: ST7<br>MPLE 1:                                                                                                                                                                             |                                                                                                                                                         |                                                                                                                    |                                       |      |             |               |       |         |                                       |                                       |                                       |                                                     |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                             |

|        | <b>EXAI</b><br>6.1.1                                                                                                                           | <b>X A: ST7</b><br><b>MPLE 1:</b><br>Measurer<br>Consump<br>6.1.2.1<br>6.1.2.2<br>6.1.2.3<br>6.1.2.4<br>6.1.2.5<br>6.1.2.6                                                                      | STAT<br>ment C<br>otion<br>Run M<br>Slow I<br>Slow I<br>Slow-'<br>Active                                                                                | IC MI<br>onfigu<br>Iode<br>Mode<br>Mode<br>Vait I<br>-Halt                                                         | EASU<br>ration                        | JREN | /ENT        | 「<br><br><br> |       |         | · · · · · · · · · · · · · · · · · · · | · · · · · · · · · · · · · · · · · · · | · · · · · · · · · · · · · · · · · · · | · · · · · · · · · · · · · · · · · · ·               | · · · · · · · · · · · · · · · · · · · | • • • •<br>• • • •<br>• • • •<br>• • • •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 7<br>7<br>7<br>8<br>8<br>9<br>10                                                            |

|        | <b>EXAI</b><br>6.1.1<br>6.1.2                                                                                                                  | MPLE 1:<br>Measurer<br>Consump<br>6.1.2.1<br>6.1.2.2<br>6.1.2.3<br>6.1.2.4<br>6.1.2.5                                                                                                           | STAT<br>ment C<br>otion<br>Run M<br>Slow I<br>Slow I<br>Slow-'<br>Active<br>Halt M                                                                      | IC MI<br>onfigu<br>Iode<br>Mode<br>Mode<br>Vait I<br>-Halt<br>Iode                                                 | EASU<br>ration<br>                    | JREN | <b>/ENT</b> | r             |       |         | · · · · · · · · · · · · · · · · · · · | · · · · · · · · · · · · · · · · · · · | · · · · · · · · · · · · · · · · · · · | • • • •<br>• • • •<br>• • • •<br>• • • •<br>• • • • |                                       | • • • •<br>• • • •<br>• • • •<br>• • • •<br>• • • •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 7<br>7<br>7<br>8<br>8<br>9<br>10<br>10                                                      |

| 6.1    | <ul> <li>EXAI</li> <li>6.1.1</li> <li>6.1.2</li> <li>6.1.3</li> <li>EXAI</li> <li>6.2.1</li> </ul>                                             | MPLE 1:<br>Measurer<br>Consump<br>6.1.2.1<br>6.1.2.2<br>6.1.2.3<br>6.1.2.3<br>6.1.2.4<br>6.1.2.5<br>6.1.2.6                                                                                     | STAT<br>ment C<br>Dion<br>Run M<br>Slow I<br>Wait M<br>Slow-'<br>Active<br>Halt M<br>on<br>Active<br>Halt M<br>on<br>Ment C<br>Dion<br>Wait M<br>Slow-' | IC MI<br>onfigu<br>Iode<br>Mode<br>Mode<br>Vait I<br>-Halt<br>Iode<br><br>ICAT<br>Mode<br>Wait I                   | ASU<br>ration<br>Mode<br>Mode         | JREN | /ENT        | RIOD          |       | /AKE    |                                       |                                       | · · · · · · · · · · · · · · · · · · · | · · · · · · · · · · · · · · · · · · ·               | ••••                                  | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 7<br>7<br>8<br>8<br>9<br>.10<br>.10<br>.10<br>.10<br>.11<br>.11<br>.11<br>.12<br>.12<br>.12 |

| 6.1    | <ul> <li>EXAI</li> <li>6.1.1</li> <li>6.1.2</li> <li>6.1.3</li> <li>EXAI</li> <li>6.2.1</li> <li>6.2.2</li> </ul>                              | <b>MPLE 1:</b><br>Measurer<br>Consump<br>6.1.2.1<br>6.1.2.2<br>6.1.2.3<br>6.1.2.3<br>6.1.2.4<br>6.1.2.5<br>6.1.2.6<br>Conclusion<br><b>MPLE 2:</b><br>Measurer<br>Consump<br>6.2.2.1<br>6.2.2.2 | STAT<br>ment C<br>Connection<br>Run M<br>Slow I<br>Wait M<br>Slow-V<br>Active<br>Halt M<br>on<br>Ment C<br>Dion<br>Slow-V<br>Mait M<br>Slow-V           | IC MI<br>onfigu<br>lode<br>Mode<br>Mode<br>Vait I<br>-Halt<br>lode<br><br>ICAT<br>onfigu<br>Mode<br>Wait I<br>lode | ASU<br>ration<br>Mode<br>Mode<br>Mode | JREN | /ENT        | RIOD          | DIC W | /AKE    |                                       |                                       | ••••                                  | · · · · · · · · · · · · · · · · · · ·               |                                       | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 7<br>7<br>8<br>9<br>.10<br>.10<br>.10<br>.11<br>.11<br>.11<br>.12<br>.12<br>.13             |

| 6.1    | <ul> <li>EXAI</li> <li>6.1.1</li> <li>6.1.2</li> <li>6.1.3</li> <li>EXAI</li> <li>6.2.1</li> <li>6.2.2</li> <li>6.2.3</li> <li>EXAI</li> </ul> | <b>MPLE 1:</b><br>Measurer<br>Consump<br>6.1.2.1<br>6.1.2.2<br>6.1.2.3<br>6.1.2.4<br>6.1.2.5<br>6.1.2.6<br>Conclusion<br><b>MPLE 2:</b><br>Measurer<br>Consump<br>6.2.2.1<br>6.2.2.2<br>6.2.2.3 | STAT<br>ment C<br>Nun M<br>Slow I<br>Vait M<br>Slow-'<br>Active<br>Halt M<br>on<br>Ment C<br>Dion<br>Slow-'<br>Halt M<br>Slow-'<br>Halt M               | IC MI<br>onfigu<br>Node<br>Mode<br>Nait I<br>-Halt<br>Iode<br>Mait I<br>Iode<br>Wait I<br>Iode                     | ASU<br>ration<br>Mode<br>Mode<br>Mode | VITH | AENT        | RIOD          |       | /AKE    | E-UP                                  | • • • • • • • • • • • • • • • • • • • | · · · · · · · · · · · · · · · · · · · | · · · · · · · · · · · · · · · · · · ·               | · · · · · · · · · · · · · · · · · · · | • • • •<br>• •<br>• • •<br>• •<br>• • •<br>• • | 7<br>7<br>8<br>9<br>10<br>10<br>10<br>11<br>11<br>11<br>12<br>12                            |

# HOW TO MINIMIZE THE ST7 POWER CONSUMPTION

|                | Application                                                                                                                                                                 |                                  |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

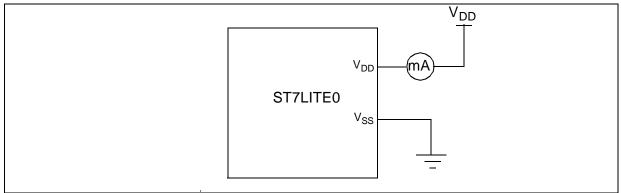

| 7 APPEND       | IX B: ST7FLITE0 STANDARD EXAMPLES                                                                                                                                           | 16                               |

| 7.1 EXA        | MPLE 1: STATIC MEASUREMENT                                                                                                                                                  | 16                               |

|                | Measurement ConfigurationConsumption7.1.2.1 Run Mode7.1.2.2 Slow Mode7.1.2.3 Wait Mode7.1.2.4 Slow-Wait Mode7.1.2.5 Active-Halt Mode7.1.2.6 Halt Mode                       | 16<br>17<br>17<br>18<br>18<br>19 |

| 7.1.3          |                                                                                                                                                                             |                                  |

| 7.2 EXA        | MPLE 2: APPLICATION WITH PERIODIC WAKE-UP                                                                                                                                   | 19                               |

| 7.2.2          | Measurement Configuration         Consumption         7.2.2.1         Wait Mode         7.2.2.2         Slow-Wait Mode         7.2.2.3         Halt Mode         Conclusion | 20<br>20<br>21<br>21             |

| -              |                                                                                                                                                                             |                                  |

| 7.3.1<br>7.3.2 | MPLE 3: APPLICATION WITH PERIODIC WAKEUP AND WATCHDOG         Measurement Configuration         Application         Conclusion                                              | 23                               |

# **3 POWER MANAGEMENT MODES**

The ST7 can run in the following six main modes:

#### 3.1 STANDARD RUN MODE

This mode is the normal operation of any MCU, where

$f_{CPU} = f_{OSC2} = f_{OSC}/2$  (when PLL is disabled by OPTION BYTE).

$f_{OSC2} = f_{OSC}^{*2}$  (when PLL is enabled by OPTION BYTE).

So, the consumption varies depending on whether the PLL is disabled or enabled.

#### 3.2 SLOW MODE

This mode is controlled by three bits in the MCCSR register: the SMS bit which enables or disables Slow mode and two CPx bits which select the internal slow frequency ( $f_{CPU}$ ).

In this mode, the master clock frequency  $(f_{OSC2})$  can be divided by 2, 4, 8 or 16.

The CPU and peripherals are clocked at this lower frequency (f<sub>CPU</sub>). The configuration for clock frequency is:

$f_{CPU} = f_{OSC2} / 2, 4, 8, 16$

= f<sub>OSC</sub> / 4, 8, 16 or 32 (when PLL is disabled by OPTION BYTE).

#### Uses:

- To reduce the power consumption by decreasing the internal clock in the device.

- To adapt the internal clock frequency to the available supply voltage.

# 3.3 WAIT MODE

In this mode, the CPU is stopped and the peripherals are still running at standard f<sub>CPU</sub>. It is selected by calling the 'WFI' instruction. All peripherals remain active.

During WAIT mode, the I[1:0] bits in the CC register are forced to '10', to enable all interrupts. All other registers and memory remain unchanged. The MCU remains in WAIT mode until an interrupt or RESET occurs, whereupon the Program Counter branches to the starting address of the interrupt or Reset service routine. The MCU will remain in WAIT mode until a Reset or an Interrupt occurs, causing it to wake up.

#### Uses:

- To place the MCU in low power consumption mode by stopping the CPU.

- External interrupt capability with all peripherals remaining active

#### 3.4 SLOW WAIT MODE

In this mode, the CPU is stopped and the peripherals are still running at the  $f_{CPU}$  defined for SLOW mode. It is activated when entering WAIT mode while the device is already in SLOW mode.

#### Uses:

- To place the MCU simultaneously in Slow mode and Wait mode to reduce the power consumption.

#### **3.5 ACTIVE-HALT MODE**

In this mode, the CPU and the peripherals are stopped, but the oscillator is still running. Peripherals clocked with an external clock source can still be active.

It is selected by calling the "HALT" instruction when the MCCSR - OIE bit is set. "HALT" forces the I[1:0] bits in the CC register to '10' to enable interrupts. The CPU clock is stopped till a Reset or MCC/RTC or CSS or other specific interrupt occurs.

To wake-up from ACTIVE-HALT, a Reset or MCC/RTC or CSS or other specific interrupt must occur. Before servicing an interrupt, the CC register is pushed on the stack. The I[1:0] bits in the CC register are set to the current software priority level of the interrupt routine and recovered when the CC register is popped. The safeguard against staying locked in ACTIVE-HALT mode is provided by the oscillator interrupt.

As soon as the interrupt capability of one of the oscillators is selected (MCCSR.OIE bit set), entering ACTIVE-HALT mode while the Watchdog is active does not generate a RESET. Because the watchdog remains active, this means that the MCU cannot spend more than a defined delay in ACTIVE-HALT mode.

#### Uses:

- To place the MCU in the lowest power consumption mode with Real Time Clock available.

- The CPU and Peripherals (Peripheral clocked with external clock source can still be active) are OFF.

- To keep a wake-up time base, the Real Time Clock Main Clock Controller is running.

#### 3.6 HALT MODE

In this mode, the oscillator is turned off. Peripherals clocked with an external clock source can still be active. Halt mode is selected by calling a "HALT" Instruction while the MCCSR - OIE bit is cleared. "HALT" forces the I[1:0] bits in the CC register to '10' to enable interrupts.

The CPU clock is stopped till a Reset or a specific interrupt (with "exit from Halt" capability) occurs. To wake-up the MCU from Halt mode (when the Watchdog is active or when the Watchdog is inactive and the WDGHALT option bit is disabled.), a Reset or specific interrupt must occur. Before servicing an interrupt, the CC register is pushed on the stack. The I[1:0] bits in the CC register are set to the current software priority level of the interrupt routine and recovered when the CC register is popped. When the Watchdog is active and the WDGHALT option bit is enabled, a Watchdog reset is generated.

#### Uses:

- To place the MCU in the lowest power consumption mode without Real Time Clock.

- The CPU and Peripherals (Peripheral clocked with external clock source can still be active) are OFF.

#### 3.7 SUMMARY

|             | Oscillator/CPU/Peripheral Status |     |             |               |                  |                   |  |

|-------------|----------------------------------|-----|-------------|---------------|------------------|-------------------|--|

| ST7 Modes   | Oscillator                       | CPU | Peripherals | RTC           | MCCSR-OIE<br>Bit | MCCSR-<br>SMS Bit |  |

| Run         | On                               | On  | On          | Available     | Х                | Reset             |  |

| Slow        | On                               | On  | On          | Available     | Х                | Set               |  |

| Wait        | On                               | Off | On          | Available     | Х                | Reset             |  |

| Slow-Wait   | On                               | Off | On          | Available     | Х                | Set               |  |

| Active-Halt | On                               | Off | Off         | Available     | Set              | Х                 |  |

| Halt        | Off                              | Off | Off         | Not Available | Reset            | Х                 |  |

#### Table 1. Summary Table

# 4 EXAMPLES

This section provides standard methods to achieve minimum power consumption in a particular ST7 application for following different microcontrollers, which can be used as a reference during application development. For user reference it also provides data values measured in lab for described applications presented as examples for different devices. CLICK on required device to see more information on

- Appendix A: ST72F324 Standard Examples

- Appendix B: ST7FLITE0 Standard Examples

**Note:** The values provided in this application note are typical only, measured on a small number of devices.

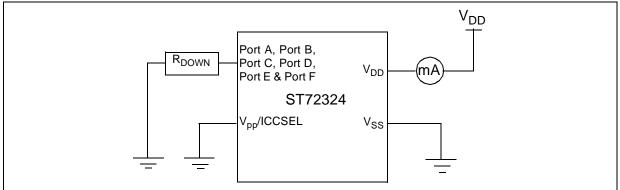

# **5 POWER MANAGEMENT TIPS**

- If you are not using the ADC, SPI, SCI or timers in the application, switch them off.

- All the port pins should be push pull output at low level.

- All I/O ports should be connected to an external pull-up or pull-down to avoid leakage due to floating inputs.

- Use Wait mode if you need external interrupt capability in low power mode and if peripherals are to be remain active.

- Use the appropriate V<sub>DD</sub> value. The V<sub>DD</sub> value must not be greater than the required value because higher the V<sub>DD</sub> value, the more power will be consumed.

- Configure the OSCRANGE[2:0] option bits for the minimum frequency range. For example, if you use 8 MHz oscillator frequency, you must select the OSCRANGE[2:0] option bits for medium speed resonator 4/8 MHz, not for high speed resonator 8/16 MHz.

# 6 APPENDIX A: ST72F324 STANDARD EXAMPLES

This section provides examples of how to minimise the consumption in a particular ST7 application for device ST72F324.(Use ST72F324 datasheet for a reference)

# 6.1 EXAMPLE 1: STATIC MEASUREMENT

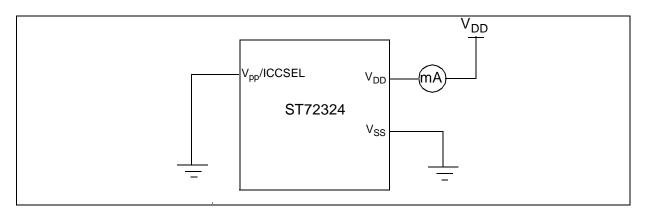

This example provides a static method of measuring the current consumed by the microcontroller in different modes and without any I/O activity. The measurement is done using the following configuration.

# 6.1.1 Measurement Configuration

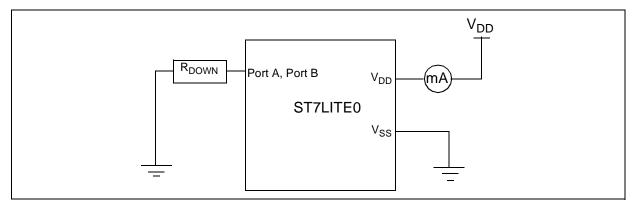

- All ports have been set as Push-Pull Outputs at low level.

- All other peripherals are in reset configuration.

- After this, MCU is put into different modes by calling different instructions and by setting some bits (in the MCCSR register).

- In Option Byte, PLL\*2 is disabled, CSS is also disabled and LVD is Off.

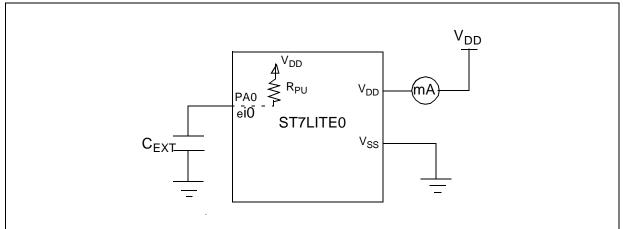

# Figure 1. Hardware Setup

#### 6.1.2 Consumption

67/

The consumption mainly depends on the mode selected and the CPU frequency.

# 6.1.2.1 Run Mode

#### Methodology:

A resonator oscillator is used with  $f_{osc}$  at 4 / 8 MHz. PLL\*2 is disabled (So,  $f_{osc2}$  is  $f_{osc}$ /2). All peripherals are in reset configuration except the ports. So, the SMS bit in the MCCSR is reset to 0. The CP1 and CP0 bits in the MCCSR are also reset to 0 and hence  $f_{CPU}$  is  $f_{osc2}$ . All ports are set as Push-Pull Outputs with low level.

#### **Measurements:**

# Table 2. Consumption I<sub>DD</sub> (RUN Mode) at T<sub>A</sub> = + 25 °C

| f <sub>OSC</sub> (MHz) | f <sub>CPU</sub> (MHz) | I <sub>DD</sub> at V <sub>DD</sub> = 4.5 V | I <sub>DD</sub> at V <sub>DD</sub> = 5 V | I <sub>DD</sub> at V <sub>DD</sub> = 5.5 V |

|------------------------|------------------------|--------------------------------------------|------------------------------------------|--------------------------------------------|

| 4                      | 2                      | 3.90 mA                                    | 4.38 mA                                  | 4.91 mA                                    |

| 8                      | 4                      | 5.88 mA                                    | 6.67 mA                                  | 7.42 mA                                    |

#### 6.1.2.2 Slow Mode

**Methodology:** A resonator oscillator is used with  $f_{osc}$  at 4 / 8 MHz. PLL\*2 is disabled. So,  $f_{osc2}$  is  $f_{osc}/2$ . All peripherals are in reset configuration except the ports and the SMS bit in the MCCSR is set to 1. The CP1 and CP0 bits in the MCCSR are set to an appropriate value. Hence  $f_{CPU}$  is  $f_{osc}/4$ ,  $f_{osc}/8$ ,  $f_{osc}/16$ ,  $f_{osc}/32$ . All ports are set as Push-Pull Outputs with low level.

#### **Measurements:**

#### Table 3. Consumption I<sub>DD</sub> (SLOW Mode) at T<sub>A</sub> = + 25 °C

| f <sub>OSC</sub> (MHz) | f <sub>CPU</sub> (MHz) | I <sub>DD</sub> at V <sub>DD</sub> = 4.5 V | I <sub>DD</sub> at V <sub>DD</sub> = 5 V | $I_{DD}$ at $V_{DD}$ = 5.5 V |

|------------------------|------------------------|--------------------------------------------|------------------------------------------|------------------------------|

| 4                      | 0.125                  | 1.33 mA                                    | 1.51 mA                                  | 1.70 mA                      |

| 4 / 8                  | 0.25                   | 1.67 mA                                    | 1.93 mA                                  | 2.18 mA                      |

| 4/8                    | 0.5                    | 2.25 mA                                    | 2.54 mA                                  | 2.88 mA                      |

| 4/8                    | 1                      | 2.87 mA                                    | 3.25 mA                                  | 3.64 mA                      |

| 8                      | 2                      | 3.88 mA                                    | 4.46 mA                                  | 4.95 mA                      |

#### 6.1.2.3 Wait Mode

**Methodology:** A resonator oscillator is used with  $f_{osc}$  at 4 / 8 MHz. PLL\*2 is disabled. So,  $f_{osc2}$  is  $f_{osc}/2$ . All peripherals are in reset configuration except the ports. So, the SMS bit in the MCCSR is reset to 0. The CP1 and CP0 bits in the MCCSR are also reset to 0 and hence  $f_{CPU}$  is  $f_{osc2}$ . All ports are set as Push-Pull Outputs with low level.

**47/**

| Measurements:                                                       |  |

|---------------------------------------------------------------------|--|

| Table 4. Consumption $I_{DD}$ (Wait Mode) at $T_A = +25 \text{ °C}$ |  |

| f <sub>OSC</sub> (MHz) | f <sub>CPU</sub> (MHz) | I <sub>DD</sub> at V <sub>DD</sub> = 4.5 V | I <sub>DD</sub> at V <sub>DD</sub> = 5 V | I <sub>DD</sub> at V <sub>DD</sub> = 5.5 V |

|------------------------|------------------------|--------------------------------------------|------------------------------------------|--------------------------------------------|

| 4                      | 2                      | 3.49 mA                                    | 3.91 mA                                  | 4.39 mA                                    |

| 8                      | 4                      | 5.20 mA                                    | 5.92 mA                                  | 6.62 mA                                    |

# 6.1.2.4 Slow-Wait Mode

**۲**۲/

**Methodology:** A resonator oscillator is used with  $f_{osc}$  at 4 / 8 MHz. PLL\*2 is disabled. So,  $f_{osc2}$  is  $f_{osc}/2$ . All peripherals are in reset configuration except the ports and the SMS bit in the MCCSR is set to 1. The CP1 and CP0 bits in the MCCSR are set to an appropriate value. Hence  $f_{CPU}$  is  $f_{osc}/4$ ,  $f_{osc}/8$ ,  $f_{osc}/16$ ,  $f_{osc}/32$ . All ports are set as Push-Pull Outputs with low level.

| f <sub>OSC</sub> (MHz) | f <sub>CPU</sub> (MHz) | I <sub>DD</sub> at V <sub>DD</sub> = 4.5 V | I <sub>DD</sub> at V <sub>DD</sub> = 5 V | $I_{DD}$ at $V_{DD}$ = 5.5 V |

|------------------------|------------------------|--------------------------------------------|------------------------------------------|------------------------------|

| 4                      | 0.125                  | 1.28 mA                                    | 1.44 mA                                  | 1.63 mA                      |

| 4/8                    | 0.25                   | 1.59 mA                                    | 1.85 mA                                  | 2.10 mA                      |

| 4 / 8                  | 0.5                    | 2.12 mA                                    | 2.45 mA                                  | 2.77 mA                      |

| 4 / 8                  | 1                      | 2.69 mA                                    | 3.02 mA                                  | 3.39 mA                      |

| 8                      | 2                      | 3.56 mA                                    | 3.99 mA                                  | 4.39 mA                      |

# Measurements: Table 5. Consumption $I_{DD}$ (Slow-Wait Mode) at $T_A = + 25$ °C

#### 6.1.2.5 Active-Halt Mode

**Methodology:** A resonator oscillator is used with  $f_{osc}$  at 4 / 8 MHz. PLL\*2 is disabled. So,  $f_{osc2}$  is  $f_{osc}/2$ . All peripherals are in reset configuration except the ports. All ports are set as Push-Pull Outputs with low level. The MCCSR-OIE bit is set to 1 and the TB1 & TB0 of MCCSR bits are set to 1. The MCC/RTC interrupt is used as the wake-up interrupt. The oscillator is ON, so the total consumption also includes the oscillator consumption.

#### **Measurements:**

# Table 6. Consumption I<sub>DD</sub> (Active-Halt Mode) at T<sub>A</sub> = + 25 °C

| f <sub>OSC</sub> (MHz) | $I_{DD}$ at $V_{DD}$ = 4.5 V | $I_{DD}$ at $V_{DD}$ = 5 V | I <sub>DD</sub> at V <sub>DD</sub> = 5.5 V |

|------------------------|------------------------------|----------------------------|--------------------------------------------|

| 4                      | 1.06 mA                      | 1.20 mA                    | 1.36 mA                                    |

| 8                      | 1.19 mA                      | 1.35 mA                    | 1.53 mA                                    |

# 6.1.2.6 Halt Mode

**Methodology:** A resonator oscillator is used with  $F_{osc}$  at 4 / 8 MHz. PLL\*2 is disabled. So,  $F_{osc2}$  is  $F_{osc}/2$ . All peripherals are in reset configuration except the ports. All ports are set as Push-Pull Outputs with low level.

#### **Measurements:**

#### Table 7. Consumption I<sub>DD</sub> (Halt Mode) at T<sub>A</sub> = + 25 °C

| f <sub>OSC</sub> (MHz) | I <sub>DD</sub> at V <sub>DD</sub> = 4.5 V | I <sub>DD</sub> at V <sub>DD</sub> = 5 V | I <sub>DD</sub> at V <sub>DD</sub> = 5.5 V |

|------------------------|--------------------------------------------|------------------------------------------|--------------------------------------------|

| 4                      | 0.1 μΑ                                     | 0.1 μΑ                                   | 0.1 μA                                     |

| 8                      | 0.1 μA                                     | 0.1 μΑ                                   | 0.1 µA                                     |

# 6.1.3 Conclusion

Current consumption depends on V<sub>DD</sub>. Consumption increases with the increase of V<sub>DD</sub> and  $f_{OSC}$ . In Active-Halt mode, the time base for the MCC/RTC interrupt does not affect the current consumption in this particular application. The oscillator is ON in Active-Halt mode, so the total consumption also includes the oscillator consumption. In Halt mode, current consumption is independent of V<sub>DD</sub> and  $f_{OSC}$ .

# 6.2 EXAMPLE 2: APPLICATION WITH PERIODIC WAKE-UP

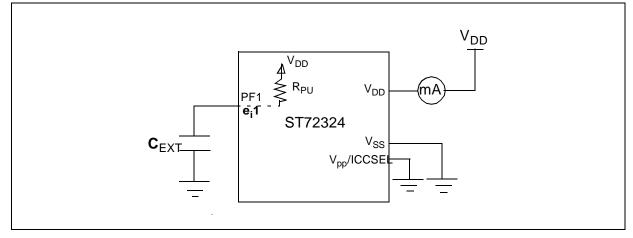

This example provides a method for measuring the average current consumed by the micro in different modes while it cycles continuously through "wake-up" and "sleep" periods. The measurement is done using the following configuration.

#### 6.2.1 Measurement Configuration

- The PF1 port (through which an external interrupt is applied to MCU) is configured as pull up interrupt.

- The sensitivity of the interrupt is configured as rising edge.

- Then the capacitor is charged and immediately the MCU is put into the corresponding mode (Wait, Slow-Wait, Halt) by calling a "WFI" or "HALT" instruction and setting some bits.

- As soon as the capacitor charges to 0.7V<sub>DD</sub>, the MCU recognizes it as external interrupt and comes out of low power mode.

- The capacitor is then discharged by setting the PF1 port to Push-Pull Output at low level and a small delay is then provided to let the capacitor discharge fully before charging it the next time.

- The MCU is again put into the corresponding low power mode and the same process is repeated. The current consumption is measured in continuous interrupted mode.

- In Option Byte, PLL\*2 is disabled, CSS is also disabled and LVD is Off.

#### Figure 2. Hardware Setup

# 6.2.2 Consumption

57/

The consumption mainly depends on how frequently the MCU wakes up from different low power modes. The Wake-Up time in turn depends upon the RC time constant. The value of the  $C_{ext}$  is fixed but the internal pull up resistance value varies depending upon the power supply of the MCU.  $R_{PU}$  decreases with the increase of  $V_{DD}$ .

The variation of  $R_{PU}$  with temperature and  $V_{DD}$  is given in the datasheet.

#### 6.2.2.1 Wait Mode

**Methodology:** A resonator oscillator is used with  $f_{osc}$  at 4 / 8 MHz. PLL\*2 is disabled. So,  $f_{osc2}$  is  $f_{osc}/2$ . All peripherals are in reset configuration except the ports. So, the SMS bit in the MCCSR is reset to 0. The CP1 and CP0 bits in the MCCSR are also reset to 0 and hence  $F_{CPU}$  is  $f_{osc2}$ . IS21 bit of EICR is cleared and IS20 bit of EICR is set to 1. All Ports are in Push-Pull Output with low level except PF1 (which is used for charging and discharging the capacitor).

# Measurements: Table 8. Consumption $I_{DD}$ (Wait Mode) for $C_{ext} = 1$ uF at $T_A = +25$ °C

| f <sub>OSC</sub> (MHz) | f <sub>CPU</sub> (MHz) | I <sub>DD</sub> at V <sub>DD</sub> = 4.5 V | I <sub>DD</sub> at V <sub>DD</sub> = 5 V | $I_{DD}$ at $V_{DD}$ = 5.5 V |