June 1995

# SuperSPARC™

DATA SHEET

Highly Integrated 32-Bit RISC Microprocessor

## **DESCRIPTION**

The STP1020A is a new member of the SuperSPARC family of microprocessor products. Like its predecessors (STP1020N and STP1020) this new part is fully SPARC version 8 compliant and is completely upward compatible with the earlier SPARC version 7 implementations running over 8500 SPARC applications and development tools.

The STP1020A is a highly integrated, high performance superscalar microprocessor designed using a state-of-the-art BiCMOS process. Through this high integration the entire processor subsystem which consists of integer and floating point execution units, memory management unit (MMU), large level-1 instruction and data caches (total of 36 KBytes of cache memory), and the bus interface unit for supporting two different buses (MBus and VBus) are implemented on a single chip. This high level of integration reduces the cost of the processor subsystem and increases the overall system reliability by reducing the total number of devices required in the system.

#### **Features**

- High performance superscalar engine with 50/60 MHz operating frequency

- Large register window (8 windows / 136 registers)

- On-chip SPARC reference MMU

- · High performance IEEE754 floating-point unit

- Large on-chip instruction/data caches (20 KByte I-cache and 16 KByte D-cache)

- · Large store buffer

- · Hardware integer multiply and divide

- · Cache coherency support for multi-processing

- Support of interface is VBus or MBus

- Built-In Self Test (BIST) logic

- Full JTAG interface (IEEE1149.1)

#### Benefits

- Delivers 73/87 SpecInt92, 84/100 SpecFp92 and 136/163 Dhrystone MIPS

- Fewer loads/stores, fast procedure calls/context switches

- · Support for virtual memory and protection

- Increased performance for floating-point intensive applications

- Increased performance for variety of applications by decoupling processor from slower main memory

- · Reduces processor wait cycles on store operations

- · Increased performance for many applications

- Allows a wide range of scalable systems to be built

- MBus mode allows direct interface to MBus. VBus mode allows interface to an external cache controller and different buses

- · Provides quick check of device integrity

- Provides better testability at the board/system level

. . . . . . .

## TYPICAL STP1020A APPLICATIONS

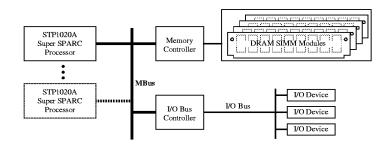

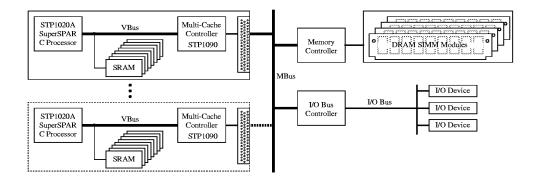

The STP1020A is intended for use in a broad range of applications from uniprocessor desktop machines to large multiprocessor servers. Uniprocessor and multiprocessor systems can be built with STP1020A processor either in direct MBus mode or in VBus mode with the use of an external cache controller ((MXCC) STP1090). The STP1090 external cache controller supports multiprocessor configurations using either MBus or XBus interfaces with up to 2 MBytes of secondary cache.

A block diagram of a system with STP1020A interfacing directly to MBus is shown in Figure 1.

Figure 1. Typical STP1020A Uniprocessor / Multiprocessor MBus System

Figure 2 shows an STP1020A based system using external cache controller, STP1090.

Figure 2. Typical STP1020A Uniprocessor / Multiprocessor System with External Cache

Sun Microsystems, Inc

#### PROCESSOR MICROARCHITECTURE

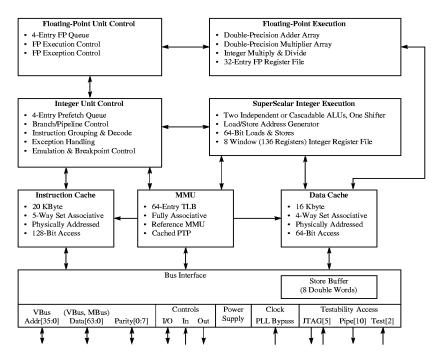

Figure 3 shows an overview of the STP1020A processor microarchitecture. The SuperScalar Integer Execution Unit performs instruction grouping and then decodes/ executes arithmetic, shift, branch, and load/ store instructions. There are 3 ALUs in the Integer Execution Unit which are dynamically configured as two independent or cascadable ALUs depending on the instruction stream.

The Floating-Point Unit consists of the floating-point register file, double precision adder/ multiplier arrays, and the control logic. This unit also performs integer multiply/ divide operation. The Memory Management Unit performs virtual to physical address translations. It consists of a 64-entry fully associative TLB with hardware table walk for TLB miss processing.

The STP1020A has separate on-chip instruction and data caches that provide fast access to code and data. The 20 KByte instruction cache is a 5-way set-associative and allows fetching 4 instructions on every access using a 128 bit wide bus. The data cache is 16 KBytes and is 4-way set-associative. Both caches are physical caches.

The STP1020A supports two different bus protocols: VBus and MBus. When MBus is selected, the STP1020A can be connected directly to MBus in either uniprocessor or multiprocessor configuration.

Figure 3. STP1020A SuperSPARC Functional Block Diagram

Sun Microsystems, Inc.

When VBus is selected, the STP1020A can be used with an external cache controller chip, STP1090, in uniprocessor or multiprocessor configuration. STP1090 chip supports both MBus or XBus interfaces and up to 2 MBytes of external cache. It is possible to design a different external cache controller which interfaces to yet another bus.

The STP1020A also integrates BIST (Built-In-Self-Test) logic, JTAG interface, and has features that support system and software debugging including hardware break-points.

#### MODES OF OPERATION

The STP1020A allows the system designer to select one of the two modes of operation. This selection is designed-in by statically connecting the  $\overline{CCMODE}$  pin to Ground or  $V_{CC}$ . When the  $\overline{CCMODE}$  pin is tied to Ground, the STP1020A operates with VBus interface. When the  $\overline{CCMODE}$  pin is pulled high, the part operates with MBus interface. The selection of MBus or VBus is visible to software in MCNTL register as the "mb" bit.

VBus is a non-multiplexed synchronous bus. It is especially tailored to provide an efficient connection between the STP1020A, the STP1090(the external cache controller), and the external cache memories made up of synchronous SRAMs. It has a 36-bit address bus, and a 64-bit data bus. All transactions on the VBus are synchronized with the STP1020A clock. The arbiter for the VBus transactions is integrated on the STP1090 chip. The STP1090 supports up to 2 MBytes of external cache and multiprocessing.

In the VBus mode, the STP1020A provides an ADDR20 signal besides the ADDR20 signal. The STP1020N, STP1020 do not drive this signal. The ADDR20 is now driven out on a pin that used to be spare3. The ADDR20 is useful in systems that incorporate 2 MB of external cache, and its integration onto the CPU eliminates an external inverter.

MBus is a SPARC International standard bus designed to function as a processor-independent bus between one or more processors and memory. It is a 64-bit multiplexed high-performance bus. It is fully synchronous with all the transfers controlled by an MBus clock. It supports block transfers in sizes up to 128 bytes with a peak transfer rate of 320 MBytes/s. All transactions on the MBus are arbitrated by an external arbiter. The arbitration algorithm is not included in the MBus definition to allow flexibility in system design. MBus is defined for uniprocessor and multiprocessor systems. The uniprocessor form of MBus is termed "Level1", and the multiprocessor version is called "Level2".

Sun Microsystems, Inc

## **VBus Mode Signals Description**

$Table\ 1$  provides a description of all the STP1020A signals in the VBus mode of operation. The supply voltage signals are described in  $Table\ 3$ .

TABLE 1: Pin Descriptions - VBus Interface ( $\overline{\text{CCMODE}} = L$ )

| Signal     | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| ADDR[35:0] | I/O  | Physical address bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| ADDR20     | 0    | Inverted physical address ADDR20. Eliminates an external inverter for 2MB cache systems.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| ARDY       | I    | This signal is an input to indicate that system logic is prepared to accept another address or bus cycle. This signal is active low.  H = System not ready.  L = System ready.                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| BURST      | О    | This signal is used to indicate that the current address on the bus is part of a burst bus cycl  H = Part of multi-cycle burst.  L = Not part of multi-cycle burst.                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| BUSREQ     | О    | Indicates VBus request by the processor.  H = VBus not requested.  L = VBus requested.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| CCHBL      | 0    | This signal indicates that the current transaction is internally cacheable.  H = Noncacheable transaction.  L = Cacheable transaction.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| CCMODE [1] | I    | Cache controller mode. Selects the operation of the STP1020A for stand-alone operation, or for operation with a cache controller (such as the STP1090). The operation of the store buffer, data cache operation and the bus interface (VBus or MBus) are selected from this signal. This signal must be statically asserted and not changed during normal operation.  H = MBus interface of operation is selected, data cache operates copy-back.  L = VBus interface of operation is selected, data cache operates write-through.                                                                          |  |  |  |

| CMDS       | I/O  | Command strobe. Indicates the beginning of a bus cycle.  When the STP1020A is not in bus master mode, as indicated by WGRT and RGRT being asserted, CMDS is used as an input to initiate external snoop transaction (including invalidates and demaps).  H = Not a command word.  L = VBus command word on ADDR35-ADDR00, CCHBL, CSA, DEMAP, LDST, SIZE1-SIZE0, SU, RD and WR.  When the STP1020A is a bus master, it asserts this signal for the first cycle of VBus transactions.  H = Not a command word.  L = VBus command word on ADDR35-ADDR00, CCHBL, CSA, DEMAP, LDST, SIZE1-SIZE0, SU, RD, and WR. |  |  |  |

| CSA        | О    | This signal indicates that the current bus transaction is a control space access. It is asserted for the address space identifier (ASI) transactions to ASI space 0x02.  H = Normal memory of ASI access.  L = Control space access (to ASI 0x02).                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

Sun Microsystems, Inc.

TABLE 1: Pin Descriptions - VBus Interface ( $\overline{CCMODE} = L$ ) (Continued)

| Signal                   | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DATA[63:00]              | Ι/O  | Data bus.                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| DEMAP                    | I/O  | Asserted with CMDS to indicate demap cycle. As an input indicates an external demap cycle. When output:  H = Normal command word.  L = demap cycle system (system should remove TLB entries matching request).  When input:  H = Non-demap cycle.  L = Demap cycle from system. The TLB entries matching request will be removed.                                                                                                                      |

| DPAR[0:7] <sup>[1]</sup> | I/O  | Data bus parity. When parity is enabled (by setting the parity bits in the MCNTL register), even parity is generated and checked. When parity is disabled, odd parity is generated but parity is not checked. DPAR0 is parity for bits DATA63-DATA56, etc., as listed:  DPAR0: DATA63-DATA56  DPAR1: DATA55-DATA48  DPAR2: DATA47-DATA40  DPAR3: DATA39-DATA32  DPAR4: DATA31-DATA24  DPAR5: DATA23-DATA16  DPAR6: DATA15-DATA08  DPAR7: DATA07-DATA00 |

| ERROR                    | O    | This signal indicates that the STP1020A has entered an error mode state and will take a watch-dog reset trap.  H = Normal operation.  L = Error mode.                                                                                                                                                                                                                                                                                                  |

| ESB                      | О    | Execution strobe output.  H = Programmed breakpoint event is occurring.  L = Inactive.                                                                                                                                                                                                                                                                                                                                                                 |

| IRL[3:0]                 | I    | Interrupt request level. This field specifies the level of the highest priority interrupt request that is currently pending. If IRL3-IRL0 = 0000, no interrupts are pending.  Level 15 (IRL3-IRL0 = 1111) is a NMI (disable all traps)  Level 14 Highest maskable interrupt  Level 1 Lowest maskable interrupt  Level 0 No interrupts pending                                                                                                          |

| LDST                     | O    | This signal indicates an atomic load/store (LDSTUB, LDSTUBA, SWAP or SWAPA) operation. It is equivalent to the logical OR of $\overline{RD}$ and $\overline{WR}$ signals. $H = No \ LDST.$ $L = Atomic \ Load/Store \ (LDST) \ cycle.$                                                                                                                                                                                                                 |

Sun Microsystems, Inc

TABLE 1: Pin Descriptions - VBus Interface ( $\overline{CCMODE} = L$ ) (Continued)

| Signal         | Туре |                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                       | I                          | Description                                                                                                    |  |  |

|----------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|----------------------------------------------------------------------------------------------------------------|--|--|

| MEXC           | I    | This signal is acknowledge                                                                                                                                                                              |                                                                                                                                                                                                                                                                       | RRDY or WI                 | RDY and with RETRY to indicate the type of                                                                     |  |  |

|                |      | MEXC                                                                                                                                                                                                    | RRDY/WRDY                                                                                                                                                                                                                                                             | RETRY                      | Description                                                                                                    |  |  |

|                |      | 1<br>1<br>1<br>0<br>0<br>0                                                                                                                                                                              | 1<br>0<br>0<br>1<br>1<br>0                                                                                                                                                                                                                                            | 1<br>0<br>1<br>0<br>1<br>0 | No Reply Retry Data Transfer Complete Undefined Error (UD) Bus Error (BE) Timeout Error (TO) Reserved Reserved |  |  |

| ŌE             | I/O  | used as an in H = SRAN                                                                                                                                                                                  | , this signal con<br>put to prevent b<br>M outputs disab<br>A outputs enable                                                                                                                                                                                          | us collisions<br>les.      | elined output enable of external cache SRAM. It is .                                                           |  |  |

| PEND           | I    | H = Syste                                                                                                                                                                                               | This signal indicates that at least one outstanding write operation has not completed.  H = System has no incomplete write operations outstanding from this processor.  L = System has write operations that were issued by this processor that are not yet complete. |                            |                                                                                                                |  |  |

| PIPE9          | 0    | H = A valid memory reference occurred in the EO stage of the previous clock cycle.  L = No valid memory reference occurred in the EO stage of the previous clock cycle.                                 |                                                                                                                                                                                                                                                                       |                            |                                                                                                                |  |  |

| PIPE8          | 0    | H = A valid floating-point operation occurred in the EO stage of the previous clock cycle.  L = No valid floating point operation occurred in the EO stage of the previous clock cycle.                 |                                                                                                                                                                                                                                                                       |                            |                                                                                                                |  |  |

| PIPE7          | 0    | H = A valid control transfer instruction was executed in the EO stage of the previous clock cycle.  L = No valid control transfer instruction was executed in the EO stage of the previous clock cycle. |                                                                                                                                                                                                                                                                       |                            |                                                                                                                |  |  |

| PIPE 6         | 0    | was in the                                                                                                                                                                                              | DO stage.                                                                                                                                                                                                                                                             |                            | e available when the group currently at the WB stag                                                            |  |  |

| PIPE5          | 0    | H = The p                                                                                                                                                                                               |                                                                                                                                                                                                                                                                       | held by the                | data cache (generally processing a cache miss).                                                                |  |  |

| PIPE4          | 0    | 1 -                                                                                                                                                                                                     | ipeline is being<br>ipeline is not be                                                                                                                                                                                                                                 | -                          | FPU (either queue is full or dependencies).<br>the FPU.                                                        |  |  |

| PIPE3          | 0    | 1                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                       |                            | age of the previous cycle was taken.<br>age of the previous cycle was not taken.                               |  |  |

| PIPE2<br>PIPE1 | 0    | Indicates the                                                                                                                                                                                           | PE1 Instruction                                                                                                                                                                                                                                                       | ructions in the            | e EO stage of the current cycle.                                                                               |  |  |

| PIPE0          | 0    | 1                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                       | _                          | n or interrupt being signalled in the current cycle. n or interrupt being signalled in the current cycle.      |  |  |

Sun Microsystems, Inc.

TABLE 1: Pin Descriptions - VBus Interface ( $\overline{CCMODE} = L$ ) (Continued)

| Signal             | Туре | Description                                                                                                                                                                                                                                              |

|--------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PLLBYP [1]         | I    | This pin is used to bypass the internal phase lock loop. When this pin is asserted, the external clock input will be routed directly to internal clock distribution with no delay compensation.                                                          |

|                    |      | H = PLL enabled. Normal operation.                                                                                                                                                                                                                       |

|                    |      | L = PLL disabled. No clock delay compensation.                                                                                                                                                                                                           |

| RD                 | I/O  | STP1020A drives $\overline{RD}$ to qualify addresses on the VBus as READ cycles. It is also asserted with $\overline{WR}$ for swap cycles and with $\overline{DEMAP}$ for demap cycles. An an input, used for internal SRAM test only.                   |

|                    |      | H = Not a read cycle.                                                                                                                                                                                                                                    |

|                    |      | $L = Read$ (or load/store with $\overline{WR}$ and $\overline{LDST}$ low) cycle.                                                                                                                                                                         |

| RESET              | I    | Reset. This causes an external reset for the STP1020A. At power-on, RESET must be held low for at least 100 ms to all allow the PLL to stabilize. If the PLL is known to be stable, RESET may be asserted for as short as 8 cycles. See reset operation. |

|                    |      | H = Normal operation.                                                                                                                                                                                                                                    |

|                    |      | L = The STP1020A is externally reset.                                                                                                                                                                                                                    |

| RETRY              | I    | This signal is encoded along with RRDY or WRDY and with MEXC to indicate the type of acknowledgment. See MEXC table for description.                                                                                                                     |

| RGRT               | I    | This signal indicates that the STP1020A has been given a grant to use the VBus for read operations.                                                                                                                                                      |

|                    |      | H = VBus not available for read operations.                                                                                                                                                                                                              |

|                    |      | L = VBus available for read operations.                                                                                                                                                                                                                  |

| RRDY               | I    | This signal indicates that incoming read data is valid. RRDY may be connected to WRDY when only a single ready signal is required. This signal is encoded with MEXC and RETRY. See MEXC table for description.                                           |

| SIZE1              | 0    | These bits indicate the transfer size of the current transaction.                                                                                                                                                                                        |

| SIZE0              |      | 00 = Byte                                                                                                                                                                                                                                                |

|                    |      | 01 = Half word                                                                                                                                                                                                                                           |

|                    |      | 10 = Word                                                                                                                                                                                                                                                |

|                    |      | 11 = Doubleword                                                                                                                                                                                                                                          |

| spare[2:0]         | I    | Not used. Should be tied high or left floating during normal chip operations.                                                                                                                                                                            |

| SRMTST [1]         | I    | Reserved: Factory test pin. It must be connected to V <sub>CC</sub> for normal operation.                                                                                                                                                                |

| <u>SU</u>          | 0    | This signal indicates that the current bus transaction is a supervisor transaction.                                                                                                                                                                      |

|                    |      | H = User (unprivileged) transaction.                                                                                                                                                                                                                     |

|                    |      | L = Supervisor (privileged) transaction.                                                                                                                                                                                                                 |

| TCK [1]            | I    | JTAG test clock input.                                                                                                                                                                                                                                   |

| TDI                | I    | JTAG test data input.                                                                                                                                                                                                                                    |

| TDO                | О    | JTAG test data output.                                                                                                                                                                                                                                   |

| TEST [1]           | I    | This pin can be used for board level testing.                                                                                                                                                                                                            |

|                    | -    | H = Normal operation.                                                                                                                                                                                                                                    |

|                    |      | L = All outputs except ESB and TDO are placed in a high-impedance state.                                                                                                                                                                                 |

| TMS <sup>[1]</sup> | I    | JTAG test mode select input.                                                                                                                                                                                                                             |

|                    |      | 1                                                                                                                                                                                                                                                        |

Sun Microsystems, Inc

TABLE 1: Pin Descriptions - VBus Interface ( \( \overline{CCMODE} = L \) (Continued)

| Signal            | Туре | Description                                                                                                                                                                                                                                                                                                                          |

|-------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TRST [1]          | I    | JTAG reset input.                                                                                                                                                                                                                                                                                                                    |

| VCLK              | I    | Primary clock source.                                                                                                                                                                                                                                                                                                                |

| VPLLRC            | I    | Phase locked loop filter capacitor. This pin should be connected to an external $0.1\mu F$ capacitor to ground.                                                                                                                                                                                                                      |

| WE[0:7]           | O    | These signals directly control the write enable signals of synchronous SRAM used for external cache. These signals are driven only when asserted; otherwise, they are tri-state WE bit ordering corresponds to the big-endian convention (i.e. WEO is the write enable for byte 0) (DATA63-DATA56).  H = SRAM read.  L = SRAM write. |

| WEE               | I    | This pin is used to control the assertion of WE7-WE0 signals.  H = May not drive WE7-WE0.  L = May drive WE7-WE0.                                                                                                                                                                                                                    |

| WR                | I/O  | STP1020A drives WR to qualify addresses on the bus as write cycle. It is asserted with RD for swaps as well as demap cycles. An an input, this signal is used to qualify invalidation requests.  H = Not a write cycle.  L = Write (or load/store with RD and LDST low) cycle.                                                       |

| WRDY              | I    | This signal indicates that incoming read data is valid. WRDY may be connected to RRDY when only a single ready signal is required. The signal is encoded with MEXC and RETRY. See MEXC table for description.                                                                                                                        |

| WGRT              | I    | This signal grants the STP1020A bus access for write operations. WGRT may be connected to RGRT when only a single grant line is required.  H = VBus not available for write operations.  L = VBus available for write operations.                                                                                                    |

| nu <sup>[1]</sup> |      | Not used in the VBus interface.                                                                                                                                                                                                                                                                                                      |

<sup>1.</sup> These pins are pulled inactive with weak internal resistive pull-ups.

Sun Microsystems, Inc.

## MBus Mode Signals Description

*Table 2* provides a description of all the STP1020A signals in the MBus mode of operation. The supply voltage signals are described in *Table 3*.

TABLE 2: Pin Descriptions - MBus Interface ( $\overline{\text{CCMODE}} = \text{H}$ )

| Signal     | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AERR [1]   | 0    | In error mode, the STP1020A will perform an automatic watchdog reset. Error mode is entered when any exception is taken with traps disabled (PSR.ET=0). This signal is driven only when asserted; otherwise, it is in tri-state.  H = Normal operation.  L = Error Mode.                                                                                                                                                                                                                                                              |

| CCMODE [2] | I    | Cache controller mode. Selects the operation of the STP1020A for stand-alone operation, or for operation with a cache controller (such as the STP1090). The operation of the store buffer, data cache operation and the bus interface (VBus or MBus) are selected from this signal. This signal must be statistically asserted and not changed during normal operation.  H = MBus interface of operation is selected, data cache operates copy-back.  L = VBus interface of operation is selected, data cache operates write-through. |

| CLK        | I    | Primary clock source.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ESB        | O    | Execution strobe output.  H = Programmed breakpoint event is occurring.  L = Inactive.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| MAD[63:00] | I/O  | Multiplexed Command/Data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| MAS        | I/O  | MBus address strobe. Asserted by the bus master when an MBus command word (containing address and control information) is on MAD63-MAD00.  H = No command word.                                                                                                                                                                                                                                                                                                                                                                       |

|            |      | L = MBus command word on MAD63-MAD0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| МВВ        | ΙΛΟ  | MBus busy. Asserted when there is any active transaction on MBus.  H = MBus free.  L = MBus busy.                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| MBG        | I    | MBus grant. This is a dedicated (not bussed) signal from the MBus arbiter to this bus master.  H = Not granted. The STP1020A may not initiate an MBus transaction.  L = Granted. The STP1020A may initiate an MBus transaction as soon as MBus is free.                                                                                                                                                                                                                                                                               |

| MBR        | O    | MBus request. This is a dedicated (not bussed) signal from the STP1020A to the MBus arbiter.  H = No request.  L = Requesting to initiate a transaction on MBus.                                                                                                                                                                                                                                                                                                                                                                      |

Sun Microsystems, Inc

TABLE 2: Pin Descriptions - MBus Interface ( $\overline{CCMODE} = H$ ) (Continued)

| Signal                  | Туре | Type Description                                                                                                                                                                                                                                                                                                                                      |                                          |                            |                                                                                                                                           |  |  |

|-------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| MERR                    | I    | MBus error. En<br>of error respons                                                                                                                                                                                                                                                                                                                    |                                          | with MRDY                  | and $\overline{\text{MRTY}}$ to indicate acknowledge type (the type                                                                       |  |  |

|                         |      | MERR                                                                                                                                                                                                                                                                                                                                                  | MRDY                                     | MRTY                       | Description                                                                                                                               |  |  |

|                         |      | H<br>H<br>H<br>L<br>L<br>L                                                                                                                                                                                                                                                                                                                            | H<br>H<br>L<br>L<br>H<br>H<br>L<br>L     | H<br>L<br>H<br>L<br>H<br>L | Idle Cycle Relinquish and Retry Valid Data Transfer Reserved Bus Error (ERROR1) Timeout Error (ERROR2) Uncorrectable Error (ERROR3) Retry |  |  |

| MID[3:0] <sup>[1]</sup> | I    | 1                                                                                                                                                                                                                                                                                                                                                     |                                          |                            | MBus device. Usually hardwired by the system. MID: MID: MID: MID: MID: MID: MID: MID:                                                     |  |  |

| MIH                     | I/O  | it owns. Memor                                                                                                                                                                                                                                                                                                                                        | y responds<br>ory inhibit.<br>emory. The | to this signal             | cache when it notices a coherent read of cache block by ignoring the request.                                                             |  |  |

| MIRL[3:0]               | I    | Interrupt request level. This field specifies the level of the highest priority interrupt request that is currently pending. If MIRL3-MIRL0 = 0000, no interrupts are pending.  Level 15 (MIRL3-MIRL0 = 1111) is a NMI (disable all traps)  Level 14 Highest maskable interrupt  Level 1 Lowest maskable interrupt  Level 0 No interrupts are pending |                                          |                            |                                                                                                                                           |  |  |

| MRDY                    | I/O  | MBus ready. En                                                                                                                                                                                                                                                                                                                                        |                                          |                            | $\overline{R}$ and $\overline{MRTY}$ to indicate acknowledgment type (the RR description.                                                 |  |  |

| MRTY                    | I    | MBus retry. En-<br>type of error res                                                                                                                                                                                                                                                                                                                  |                                          |                            | and MRDY to indicate acknowledgment type (the RR description.                                                                             |  |  |

| MSH [1]                 | I/O  | Memory shared<br>it is caching. Bo<br>H = No shari<br>L = Shared d                                                                                                                                                                                                                                                                                    | oth caches w                             |                            | cache when it notices a coherent read of a cache blockdata as shared.                                                                     |  |  |

| PEND [2]                | I    | least one outsta<br>H = System l                                                                                                                                                                                                                                                                                                                      | nding write<br>nas no write              | operation has              | s interface only. It indicates to the STP1020A that at some some some some some some some some                                            |  |  |

| PIPE9                   | 0    |                                                                                                                                                                                                                                                                                                                                                       | -                                        |                            | red in the EO stage of the previous clock cycle.<br>rred in the EO stage of the previous clock cycle.                                     |  |  |

| PIPE8                   | 0    | 1                                                                                                                                                                                                                                                                                                                                                     |                                          | •                          | occurred in the EO stage of the previous clock cycle occurred in the EO stage of the previous clock cycle                                 |  |  |

Sun Microsystems, Inc.

TABLE 2: Pin Descriptions - MBus Interface ( $\overline{CCMODE} = H$ ) (Continued)

| Signal             | Type | Description                                                                                                                                                                                                                                                                                                               |

|--------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIPE7              | 0    | <ul> <li>H = A valid control transfer instruction was executed in the EO stage of the previous clock cycle.</li> <li>L = No valid control transfer instruction was executed in the EO stage of the previous clock cycle.</li> </ul>                                                                                       |

| PIPE6              | О    | <ul> <li>H = Indicates that no instructions were available when the group currently at the WB stage was in the D0 stage.</li> <li>L = Indicates that one or more instructions were available in this group.</li> </ul>                                                                                                    |

| PIPE5              | 0    | <ul> <li>H = The pipeline is being held by the data cache (generally processing a cache miss).</li> <li>L = The pipeline is not being held by the data cache.</li> </ul>                                                                                                                                                  |

| PIPE4              | 0    | H = The pipeline is being held by the FPU (either queue is full or dependencies).<br>L = The pipeline is not being held by the FPU.                                                                                                                                                                                       |

| PIPE3              | 0    | H = Indicates that the branch in EO stage of the previous cycle was taken.  L = Indicates that the branch in EO stage of the previous cycle was not taken.                                                                                                                                                                |

| PIPE2<br>PIPE1     | 0    | Indicates the number of instructions in the EO stage of the current cycle:    PIPE2 - PIPE1                                                                                                                                                                                                                               |

| PIPE0              | 0    | H = Indicates that there is an exception or interrupt being signalled in the current cycle.  L = Indicates that there is no exception or interrupt being signalled in the current cycle.                                                                                                                                  |

| PLLBYP [2]         | I    | This pin is used to bypass the internal phase lock loop. When this pin is asserted, the external clock input will be routed directly to internal clock distribution with no delay compensation.  H = PLL enabled. Normal operation.  L = PLL disabled. No clock delay compensation.                                       |

| RSTIN              | I    | Reset In. This causes an external reset for the STP1020A. At power-on, RSTIN must be held low for at least 100 ms to all allow the PLL to stabilize. If the PLL is known to be stable, RSTIN may be asserted for as short as 8 cycles. See reset operation.  H = Normal operation.  L = The STP1020A is externally reset. |

| spare3             | 0    | Not used. Leave floating.                                                                                                                                                                                                                                                                                                 |

| spare[2:0]         | I    | Not used. Should be tied high or left floating during normal chip operation.                                                                                                                                                                                                                                              |

| TCK <sup>[2]</sup> | I    | JTAG test clock input.                                                                                                                                                                                                                                                                                                    |

| TDI [2]            | I    | JTAG test data input.                                                                                                                                                                                                                                                                                                     |

| TDO                | 0    | JTAG test data output.                                                                                                                                                                                                                                                                                                    |

| TEST [2]           | I    | This pin can be used for board level training.  H = Normal operation.  L = All outputs except ESB and TDO are placed in a high-impedance state.                                                                                                                                                                           |

| TMS [2]            | I    | JTAG test mode select input.                                                                                                                                                                                                                                                                                              |

Sun Microsystems, Inc

TABLE 2: Pin Descriptions - MBus Interface ( \( \overline{\colon} \) (Continued)

| Signal            | Туре | Description                                                                                                     |

|-------------------|------|-----------------------------------------------------------------------------------------------------------------|

| TRST              | I    | JTAG test reset input.                                                                                          |

| VPLLRC            | I    | Phase locked loop filter capacitor. This pin should be connected to an external $0.1\mu F$ capacitor to ground. |

| nu <sup>[2]</sup> | I/O  | Not used for MBus.                                                                                              |

- 1. These pins have an open drain.

- 2. These pins are pulled inactive with weak internal resistive pull-ups.

Table 3 gives the description of all the supply voltages in both MBus and VBus modes of operation.

**TABLE 3: Pin Descriptions - Power Connections**

| Signal                            | Туре | Description                           |

|-----------------------------------|------|---------------------------------------|

| V <sub>CCC</sub>                  | I    | V <sub>CC</sub> for core logic.       |

| V <sub>CCCLK</sub> <sup>[1]</sup> | I    | V <sub>CC</sub> for clock and PLL.    |

| V <sub>CCCI</sub>                 | I    | V <sub>CC</sub> for input buffers.    |

| $V_{CCP}$                         | I    | V <sub>CC</sub> for peripheral logic. |

| V <sub>SSC</sub>                  | I    | Ground for core logic.                |

| V <sub>SSCLK</sub>                | I    | Ground for clock and PLL.             |

| V <sub>SSI</sub>                  | I    | Ground for input buffers.             |

| V <sub>SSP</sub>                  | I    | Ground for peripheral logic.          |

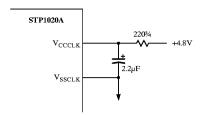

<sup>1.</sup> For stable operation of the phase lock loop (PLL), the filter circuit shown in  $Figure\ 20$  should be used.

Sun Microsystems, Inc.

## **MBUS TIMING**

The MBus read, write and invalidate operations are explained in the following section.

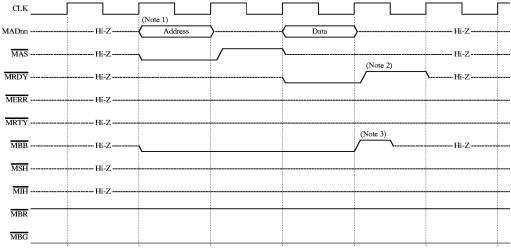

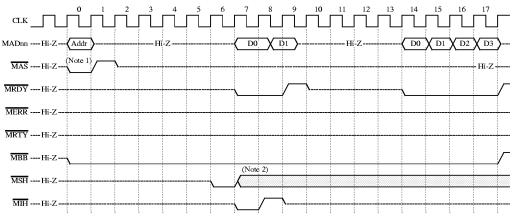

## MBus Single Read

The single read cycle transfers a byte, half-word, word, or a double-word. Big-endian word ordering is used (the least significant bytes in a word appear on the high bits of the bus according to SPARC standard). *Figure 4* shows an MBus single read operation.

- Notes: 1. MADnn lines are held to their previously driven state by system bus holders.

- 2. Control lines (MAS, MRDY, MERR, MRTY) are driven inactive for one clock before being released.

- 3.  $\overline{\text{MBB}}$  is driven high for 1/2 clock cycle before being released.

Figure 4. MBus Single Read

Sun Microsystems, Inc

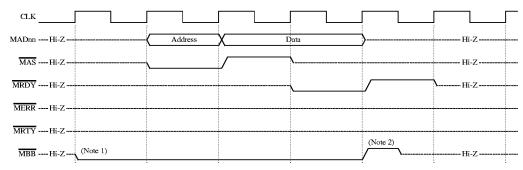

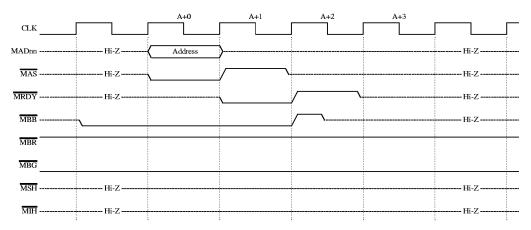

## MBus Single Write

Single write operations are queued in the STP1020A store buffer. As soon as the STP1020A receives a bus grant, the transactions will be issued on the bus. The processor will not wait during this time, unless the buffer fills. Bytes, half-words, words, and double words may all be stored, with big-endian ordering. Any errors are reported as deferred data store errors. *Figure 5* shows an MBus single write operation.

Notes: 1.  $\overline{MBB}$  is driven active one cycle before MAS during write and CI cycles.

MBB is driven inactive for 1/2 clock cycle before being released.

Figure 5. MBus Single Write

Sun Microsystems, Inc.

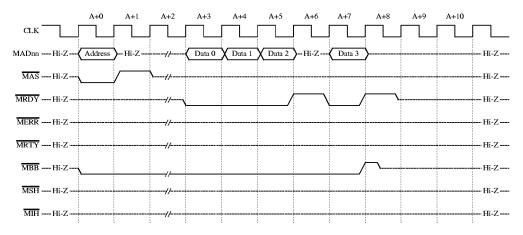

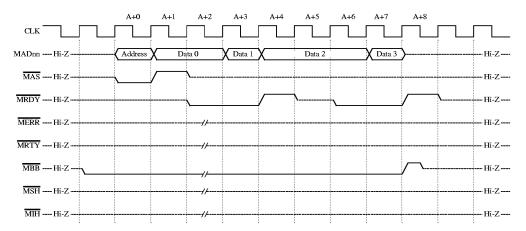

#### MBus Burst Read

Figure 6 shows a 32-byte burst read operation. A read operation can be performed on any size of data transfer that is specified by the SIZE bits. Read transactions support wrapping (critical word first ordering). Transactions involving fewer than eight bytes will have undefined data on the unused bytes.

Figure 6. MBus Burst Read

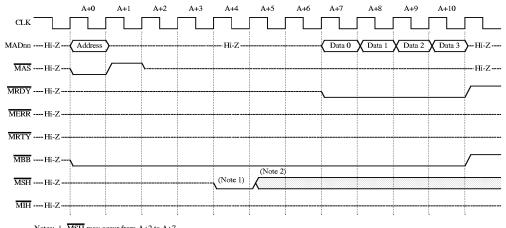

#### MBus Coherent Read

Coherent Read (CR) transactions are used to read data from the current owner. The owner may be memory or another cache. CR will be used for all on-board data cache load misses and all on-board instruction cache misses. If another cache owns the data, it will respond by asserting the MIH signal and providing the data. All CR transactions use critical-word-first ordering. The double-word that is needed first will be the starting address of the transaction. Double-words from memory must be returned in modulo 32-byte address order. Once the needed data arrives, the processor will use it immediately. Figure 7 shows an MBus coherent read of shared data. Any processor that has a valid cached copy of data referenced by CR transactions must assert the MSH signal to indicate that the information is shared. The STP1020A can accept the assertion of MSH at any time until receipt of the first data word. If the data is owned by another cache, the STP1020A will ignore any data ready responses until four cycles beyond the assertion of MIH. This allows memory controllers to begin transmitting data sooner. Mem-

Sun Microsystems, Inc

ory controllers must not respond with data until a time equal to the maximum  $\overline{\text{MIH}}$  assertion delay for any cache in the system. Figure 8 shows an MBus coherent read of owned data.

Notes: 1. MSH may occur from A+2 to A+7.

2. MSH is an open drain signal. It is not driven inactive. The system pull-up resistor returns it to an inactive level.

Figure 7. MBUS Coherent Read of Shared Data

Notes: 1. Device is not the Master.

$2. \ \overline{\text{MSH}} \ \text{is an open drain signal. It is not driven inactive. The system pull-up resistor returns it to an inactive level.}$

Figure 8. MBUS Coherent Read of Owned Data

Sun Microsystems, Inc.

#### MBus Coherent Invalidate

A Coherent Invalidate (CI) operation can only be performed on a block (32 bytes). All CI operations will be snooped by all snooping caches. If a Coherent Invalidate operation hits in a cache, that copy will be invalidated immediately, regardless of its state. Memory is responsible for the acknowledgment of the CI transaction. *Figure 9* shows a CI operation.

Figure 9. MBus Coherent Invalidate

Sun Microsystems, Inc.

#### Coherent Read and Invalidate

Since the MBus supports a write-invalidate type of cache-consistency protocol, a special Coherent Read and Invalidate (CRI) transaction that combines a CR transaction with the CI transaction was included to reduce the number of MBus Coherent transactions,. Caches that are performing CR transactions with the knowledge that they intend to immediately modify the data can issue this transaction.

Each CRI transaction will be snooped by all system caches. If the address hits and the cache does not own the block, that cache immediately invalidate its copy of this block, no matter what state the data was in. If the address hits and the cache owns the block, the block will assert  $\overline{\text{MIH}}$  and supply the data. When the data has been successfully supplied, the cache will then invalidate its copy of this block.

MSH is not driven during the CRI transaction.

#### Coherent Write and Invalidate

A Coherent Write and Invalidate transaction combines a block write transaction with a CI transaction.

Each Coherent Write and Invalidate transaction will be snooped by all system caches. If the address hits, caches will invalidate their copies of this block, no matter what state the data was in. Neither  $\overline{\text{MIH}}$  nor  $\overline{\text{MSH}}$  is asserted for Coherent Write and Invalidate transactions. *Figure 10* shows a Coherent Write and Invalidate operation.

Figure 10. MBus Coherent Write and Invalidate

Sun Microsystems, Inc.

## **VBUS TIMING**

The VBus read, write and invalidate operations are explained in the following section.

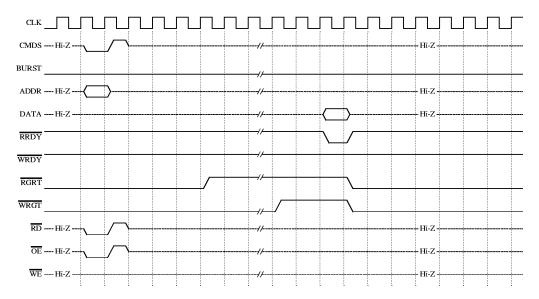

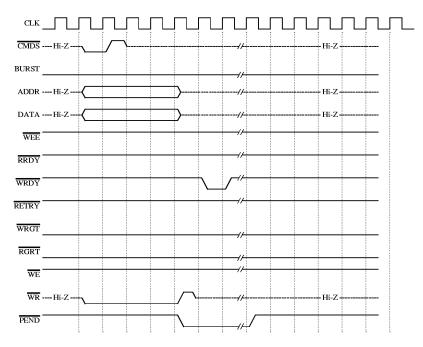

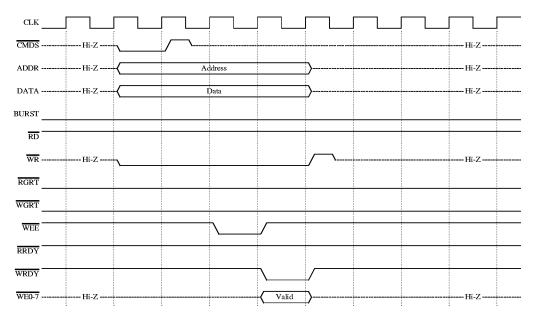

## Cache Disabled/Non-Cacheable Single Read

Figure 11 shows a single read with the cache disabled. The external cache controller (STP1090) goes to the system bus to accomplish this operation. It deasserts  $\overline{RGRT}$  to allow the STP1020A to complete pending write operations. When the data is available, the STP1090 negates grant, drives the data, and asserts  $\overline{RRDY}$ .

Figure 11. VBus Cache Disabled/Non-Cacheable Single Read

Sun Microsystems, Inc

## Cache Disabled Write (or Non-Cacheable) Write

Figure 12 shows a cache disabled write. The external cache controller (STP1090) terminates the VBus cycle by issuing a  $\overline{\text{WRDY}}$  without asserting  $\overline{\text{WEE}}$ . A non-cacheable write would be identical.

Figure 12. VBus Cache Disabled/Non-Cacheable Single Write

Sun Microsystems, Inc.

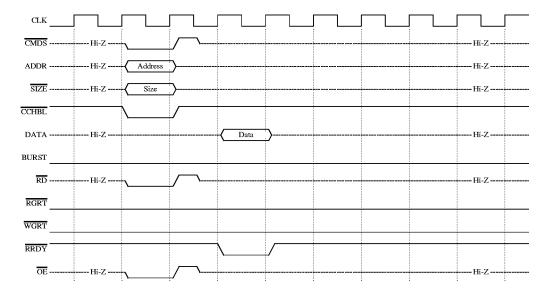

## Cacheable Single Read Hit

Figure 13 shows a read by the STP1020A of a single cacheable word with an external cache hit. STP1020A asserts the address, cycle qualifiers, and the  $\overline{OE}$  to SRAM. The STP1090 detects a tag match and issues a  $\overline{RRDY}$  at the same time that the SRAMs drive data to STP1020A. The  $\overline{OE}$  from STP1020A is delayed in the registers internal to the synchronous SRAMs, and the data is enabled two cycles after the  $\overline{OE}$  is issued to the chip. Note that the partially bussed (not driven by the STP1020A for the entire cycle) VBus control signals are actively deasserted for 1/2 cycle before being released to the bus keepers.

Figure 13. VBus Cacheable Single Read Hit

Sun Microsystems, Inc

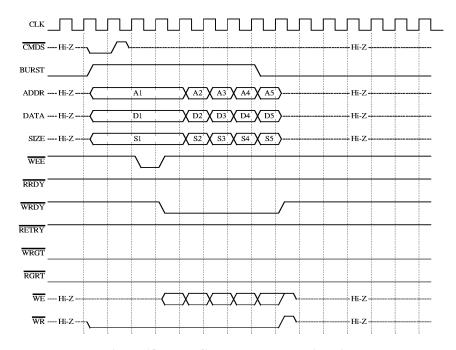

## Cacheable Single Read Miss

Figure 14 shows a cacheable single-read miss. The STP1090 detects that a tag mismatch occurs and issues a cycle to the system bus to obtain data to fill the external cache. It removes  $\overline{RGRT}$  to allow STP1020A to proceed with any write operation it may have had pending. When the system bus returns the requested data block, the STP1090 removes the bus grant to STP1020A (negates  $\overline{WGRT}$ ) to obtain access to the SRAMs. The STP1090 writes the data into the SRAMs. The STP1090 issues a  $\overline{RRDY}$  to STP1020A, as the data word requested (by STP1020A read) is driven on the DATA lines (while the data is being written into SRAMs).

Figure 14. VBus Cacheable Single Read Miss

Sun Microsystems, Inc.

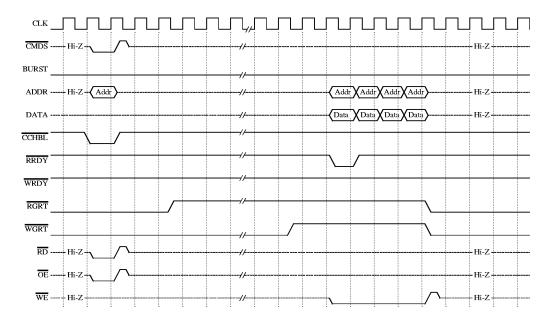

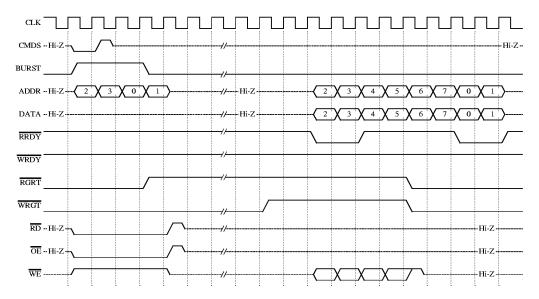

## **Burst Read Hit**

Figure 15 shows a burst-read hit. As with a cacheable single-read hit, the STP1090 functions mainly to time the cycle by asserting  $\overline{RRDY}$  as the SRAM provides the data.

Figure 15. VBus Burst Read Hit

Sun Microsystems, Inc

#### **Burst Read Miss**

Figure 16 shows a burst read miss. The external cache controller (STP1090) removes  $\overline{RRGT}$  to indicate that the cycle is in progress and that STP1020A can proceed with an outstanding write if one is pending. When the data returns from the system bus, the STP1020A writes it into the SRAM and asserts  $\overline{RRDY}$  when the requested data is on the VBus. Note that, in Figure 16, the STP1090 is in XBus configuration, and consequently the block size is 64 bytes. Only 32 bytes are sent to STP1020A, while all 64 bytes are stored in SRAM. Also note that with critical word first ordering, the data returned starts from the index into the block for the requested doubleword, continues to the last index, and then wraps from index 0 to the starting index minus 1.

Figure 16. VBus Burst Read Miss

Sun Microsystems, Inc.

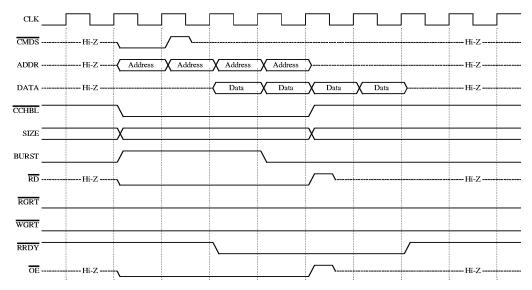

## Cacheable Single Write Hit

Figure 17 shows a cacheable single-write hit. The STP1090 asserts  $\overline{\text{WEE}}$  at the CMD + 2 cycle (i.e., two cycles after  $\overline{\text{CMDS}}$ ) to allow the assertion of the write data (DATA, DPAR) and the write strobes  $\overline{\text{(WE7-WE0)}}$ . The STP1090 asserts the  $\overline{\text{WRDY}}$  in the following cycle ( $\overline{\text{CMDS}}$  + 3).

Figure 17. VBus Cacheable Single Write Hit

Sun Microsystems, Inc.

#### Cacheable Burst Write Hit

Figure 18 shows a burst write hit. It is basically the same except that  $\overline{\text{WRDY}}$  is asserted for each data doubleword written in the burst. The STP1020A deasserts BURST one cycle before the last write. Each of the individual writes in the burst from the STP1020A may be from one to eight bytes and may be at any address within the cache block. The number of consecutive writes may be of arbitrary length. If the external cache controller (STP1090) needs the VBus while a burst write cycle is occurring, it can deassert the  $\overline{\text{WRGT}}$  signal to terminate the burst cycle prematurely. When the STP1020A reacquires the VBus, it continues the burst write from where it was interrupted.

Figure 18. VBus Cacheable Burst Write Hit

Sun Microsystems, Inc.

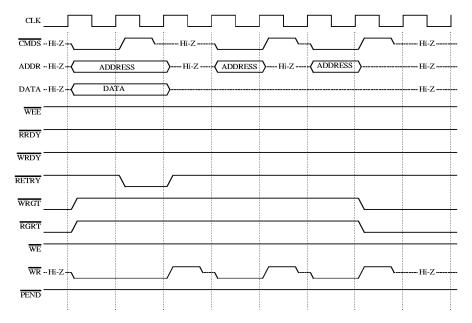

#### Cache Invalidate

Figure 19 shows an invalidate. The external cache controller (STP1090) first removes the STP1020A from the VBus by revoking the  $\overline{RGRT}$  and  $\overline{WGRT}$  bus grants; it then asserts the address,  $\overline{WR}$  and  $\overline{CMDS}$ . Multiple invalidates may occur consecutively. Invalidates may also occur when the STP1090 has obtained the VBus for SRAM reads or writes.

Figure 19. VBus Invalidation

Sun Microsystems, Inc.

#### Clock Operation

Proper clocking is essential at high operating frequencies. In order to reduce system clock skew, a phase lock loop (PLL) is implemented on-chip. For testing and other purposes, a PLL bypass mechanism is provided. When the PLLBYP signal is active (low), the PLL circuitry will be completely bypassed.

#### Phase Lock Loop Operation

The PLL operates by constantly measuring internal clock routing and gate delays and internally generating a clock that is effectively ahead of the external clock by an amount equal to the internal delay. This reduces clock skew to the internal logic. Prior to normal operation, the PLL must be allowed time to stabilize. To assure stabilization,  $\overline{\text{RESET}}$  should be active for 100 ms (milliseconds).