# 24 characters × 2 lines reflective character module RCM2030R

The RCM2030R is a reflective TN type liquid crystal module with a built-in controller/driver LSI and a display capacity of 24 characters × 2 lines.

#### Applications

Personal computers, word processors, facsimiles, telephones, etc.

#### Features

- 1) Wide viewing angle and high contrast.

- 2)  $5 \times 7$  dot character matrix with cursor.

- 3) Interfaces with 4-bit or 8-bit MPUs.

- 4) Displays up to 226 characters and special symbols.

- Custom character patterns are displayed with the character RAM.

- Abundant instruction set including clear display, cursor on/off, and character blinking.

- Compact and light weight for easy assembly to the host instrument.

- 8) Operable on single 5 V power supply.

- 9) Low power consumption.

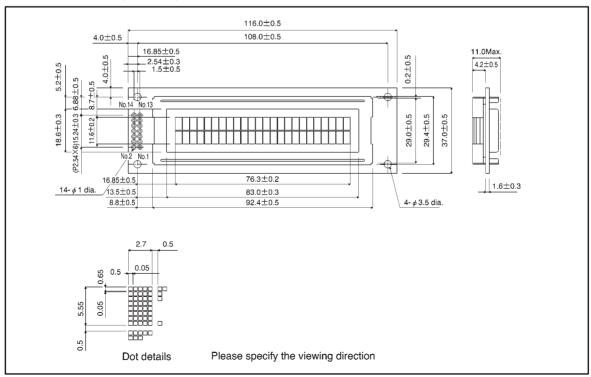

#### External dimensions (Units: mm)

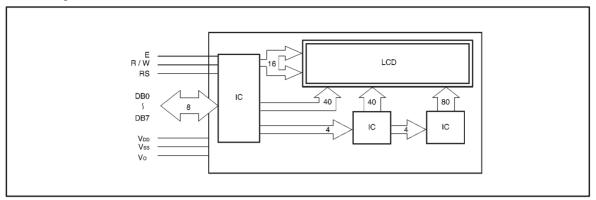

# Block diagram

## Pin assignments

| Pin no. | Signal          | Pin no. | Signal |

|---------|-----------------|---------|--------|

| 1       | Vss             | 8       | DB1    |

| 2       | V <sub>DD</sub> | 9       | DB2    |

| 3       | Vo              | 10      | DB3    |

| 4       | RS              | 11      | DB4    |

| 5       | R/W             | 12      | DB5    |

| 6       | E               | 13      | DB6    |

| 7       | DB0             | 14      | DB7    |

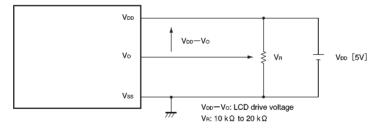

# Power supply example

Fig.1

# ●Absolute maximum ratings (Ta = 25°C)

| Parameter                  | Symbol                           | Min. | Тур. | Max.            | Unit |

|----------------------------|----------------------------------|------|------|-----------------|------|

| Logic power supply voltage | V <sub>DD</sub> -V <sub>SS</sub> | 0    | _    | 6.5             | V    |

| LCD drive voltage          | V <sub>DD</sub> -V <sub>O</sub>  | 0    | _    | 6.5             | V    |

| Input voltage              | Vin                              | Vss  | _    | V <sub>DD</sub> | V    |

| Operating temperature      | Topr                             | 0    | _    | 50              | င    |

| Storage temperature        | Tstg                             | -20  | _    | 70              | င    |

## • Electrical characteristics ( $V_{DD} = 5.0 \text{ V} \pm 0.25 \text{ V}$ , Ta = $25^{\circ}$ C)

| Parameter                 | Symbol | Min. | Тур. | Max.            | Unit | Conditions          |

|---------------------------|--------|------|------|-----------------|------|---------------------|

| Input high level voltage  | ViH    | 2.0  | _    | V <sub>DD</sub> | ٧    |                     |

| Input low level voltage   | VIL    | _    | _    | 0.8             | V    |                     |

| Output high level voltage | Vон    | 2.4  | _    | _               | V    | –lон=1.2mA          |

| Output low level voltage  | Vol    | _    | _    | 0.4             | V    | IoL=2mA             |

| Power supply current      | loo    | _    | 1.5  | 3               | mA   | V <sub>DD</sub> =5V |

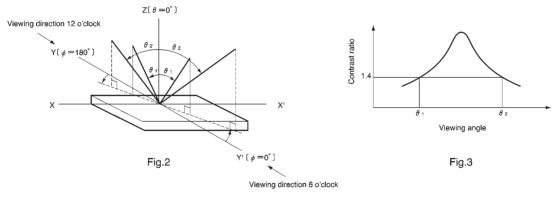

## •Optical characteristics (Ta = $25^{\circ}$ C, $\phi = 0^{\circ}$ )

| Parameter      | Symbol     | Min. | Тур. | Max. | Unit | Conditions                               |

|----------------|------------|------|------|------|------|------------------------------------------|

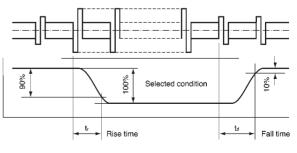

| Rise time      | tr         | _    | 100  | 250  | ms   | $\theta = 10^{\circ},  \phi = 0^{\circ}$ |

| Fall time      | td         | _    | 150  | 250  | ms   | $\theta = 10^{\circ},  \phi = 0^{\circ}$ |

| Contrast ratio | К          | _    | 3    | _    | _    | $\theta = 10^{\circ},  \phi = 0^{\circ}$ |

|                | <i>θ</i> 1 | _    | _    | 10   | deg  | φ=0°, K≥1.4                              |

| Viewing angle  | <i>θ</i> 2 | 40   | _    | _    | deg  | φ=0°, K≥1.4                              |

|                | φ          | ±30  | _    | _    | deg  | θ₁=20°, K≧1.4                            |

## (1) Definition of $\theta$ and $\phi$

(2) Definition of viewing angles  $\theta$  1 and  $\theta$  2

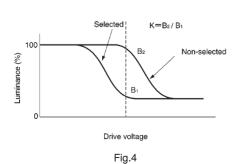

## (3) Definition of contrast ratio"K"

(4) Definition of optical response

Fig.5

# Timing chart

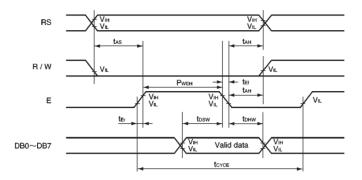

# (1) Writing

Fig. 6

| Parameter                 | Symbol      | Min. | Тур. | Max. | Unit |       |

|---------------------------|-------------|------|------|------|------|-------|

| Enable cycle time         | toyce       | 500  | _    | _    | ns   | Fig.6 |

| Enable pulse time         | Pweh        | 220  | _    | _    | ns   | Fig.6 |

| Enable rise and fall time | ter, ter    | _    | _    | 20   | ns   | Fig.6 |

| Address setup time        | tas         | 40   | _    | _    | ns   | Fig.6 |

| Address hold time         | <b>t</b> ah | 10   | _    | _    | ns   | Fig.6 |

| Data setup time           | tosw        | 60   | _    | _    | ns   | Fig.6 |

| Data hold time            | tohw        | 10   | _    | _    | ns   | Fig.6 |

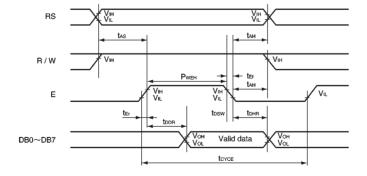

# (2) Reading

Fig. 7

| Parameter                 | Symbol      | Min. | Тур. | Max. | Unit |       |

|---------------------------|-------------|------|------|------|------|-------|

| Enable cycle time         | toyce       | 500  | _    | _    | ns   | Fig.7 |

| Enable pulse time         | Pweh        | 220  | _    | _    | ns   | Fig.7 |

| Enable rise and fall time | ter, ter    | _    | _    | 20   | ns   | Fig.7 |

| Address setup time        | tas         | 40   | _    | _    | ns   | Fig.7 |

| Address hold time         | <b>t</b> ah | 10   | _    | _    | ns   | Fig.7 |

| Data delay time           | toor        | _    | _    | 120  | ns   | Fig.7 |

| Data hold time            | tohr        | 20   | _    | _    | ns   | Fig.7 |

#### Pin functions

| Symbol          | Level | Input / output | Fun                                                                                                                                    | ction                                                                      |  |  |  |  |  |  |  |

|-----------------|-------|----------------|----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Vss             | _     | _              | GND:0V                                                                                                                                 |                                                                            |  |  |  |  |  |  |  |

| V <sub>DD</sub> | _     | _              | 5V Power supply voltage                                                                                                                |                                                                            |  |  |  |  |  |  |  |

| Vo              | _     | _              |                                                                                                                                        |                                                                            |  |  |  |  |  |  |  |

| RS              | H/L   | Input          | Register selection signal. 0: Instruction register (writing) Busy flag, address counter (reading) 1: Data register (reading / writing) |                                                                            |  |  |  |  |  |  |  |

| R/W             | H/L   | Input          | Reading (R) and writing (W) selection signal. "0": Writing MPU → LCD module "1": Reading MPU ← LCD module                              |                                                                            |  |  |  |  |  |  |  |

| Е               | H,H→L | Input          | Data reading and writing sta                                                                                                           | art signal.                                                                |  |  |  |  |  |  |  |

| DB0<br>DB3      | H/L   | Input / output |                                                                                                                                        | s are bi-directional and used<br>the MPU and the module.<br>bit operation. |  |  |  |  |  |  |  |

| DB4             | H/L   | Input / output |                                                                                                                                        | s are bi-directional and used<br>the MPU and the module.<br>busy flag.     |  |  |  |  |  |  |  |

Note: In order to be able to interface with 4-bit or 8-bit MPUs, the module supports data transfer with two transmissions of 4 bits at a time or one transmission of 8 bits at once.

<sup>(1)</sup> When the interface data length is 4 bits, data is transferred along DB4 through DB7 buses and DB0 through DB3 buses are not used. Data transferal is completed after two transfers of 4 bit data. First the upper nibble (contents of DB4 through DB7 during 8-bit interfacing) is transferred and then the lower nibble (contents of DB0 through DB3 during 8-bit interfacing) is transferred.

<sup>(2)</sup> When the interface data length is 8 bits, the data DB0 through DB7 is transferred along the eight data buses.

## Instructions

| Instruction                    |                                                                                                                                                                                                                                                                                                                                           |     |     |     | Co  | ode   |     |     |     |     | Description                                                                                                                                                                          | Execution tim                                      |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-----|-------|-----|-----|-----|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| Instruction                    | RS                                                                                                                                                                                                                                                                                                                                        | R/W | DB7 | DB6 | DB5 | DB4   | DB3 | DB2 | DB1 | DB0 | Description                                                                                                                                                                          | fcp=250kHz                                         |

| Clear display                  | 0                                                                                                                                                                                                                                                                                                                                         | 0   | 0   | 0   | 0   | 0     | 0   | 0   | 0   | 1   | Clears display and sets address 0 of DD RAM to address counter.                                                                                                                      | 1.64ms                                             |

| Home cursor                    | 0                                                                                                                                                                                                                                                                                                                                         | 0   | 0   | 0   | 0   | 0     | 0   | 0   | 1   | *   | Sets address 0 of DD RAM to address counter and returns a shifted display to original position. The contents of DD RAM are unchanged.                                                | 1.64ms                                             |

| Entry mode set                 | 0                                                                                                                                                                                                                                                                                                                                         | 0   | 0   | 0   | 0   | 0     | 0   | 1   | I/D | s   | Sets the cursor move direction and specifies whether or not to shift display. This operation occurs when reading or writing data.                                                    | 40 μs                                              |

| Display on / off control       | 0                                                                                                                                                                                                                                                                                                                                         | 0   | 0   | 0   | 0   | 0     | 1   | D   | С   | В   | Turns display on or off [D], turns cursor on or off [C], or blinks the character at the cursor position [B].                                                                         | 40 μs                                              |

| Cursor / display shift         | 0                                                                                                                                                                                                                                                                                                                                         | 0   | 0   | 0   | 0   | 1     | s/c | R/L | *   | *   | Moves cursor or shifts display without changing the DD RAM.                                                                                                                          | 40 μs                                              |

| Function set                   | 0                                                                                                                                                                                                                                                                                                                                         | 0   | 0   | 0   | 1   | DL    | N   | F   | *   | *   | Sets the interface data length [DL], number of lines displayed [N], and character font [F].                                                                                          | 40 μs                                              |

| CG RAM address set             | 0                                                                                                                                                                                                                                                                                                                                         | 0   | 0   | 1   |     |       | Α   | CG  |     | •   | Sets the CG RAM address. Data received after this is CG RAM data.                                                                                                                    | 40 μs                                              |

| DD RAM address set             | 0                                                                                                                                                                                                                                                                                                                                         | 0   | 1   |     |     |       | Add |     |     |     | Sets the DD RAM address. Data received after this is DD RAM data.                                                                                                                    | 40 μs                                              |

| Read busy flag<br>address      | 0                                                                                                                                                                                                                                                                                                                                         | 1   | BF  |     |     |       | AC  |     |     |     | Reads the busy flag signifying internal operations in progress and reads the contents of the address counter.                                                                        | 0μs                                                |

| Write data to CG or DD RAM     | 1                                                                                                                                                                                                                                                                                                                                         | 0   |     |     | ١   | Vrite | Dat | a   |     |     | Data is written from the DD RAM or CG RAM.                                                                                                                                           | 46 μs                                              |

| Read data from CG<br>or DD RAM | 1                                                                                                                                                                                                                                                                                                                                         | 1   |     |     | F   | Read  | Dat | а   |     |     | Data is read to DD RAM or CG RAM.                                                                                                                                                    | 46 μs                                              |

|                                | I/D = 1: Increment I/D = 0: Decrement S = 1: Accompanies display shift S/C = 1: Display shift S/C = 0: Cursor movement R/L = 1: Right shift R/L = 0: Left shift DL = 1: 8 bit DL = 0: 4 bit N = 1: 2 lines N = 0: 1 line F = 1: 5 × 10 dots F = 0: 5 × 7 dots BF = 1: Internal operation in progress BF = 0: Instructions can be received |     |     |     |     |       |     |     |     |     | DD RAM: Display data RAM CG RAM: Character generator RAM Ace: CG RAM address Address DD RAM address (corresponds to cursor address) AC: Address counter used for both DD and CG RAM. | Execution<br>times will<br>vary with<br>frequency. |

(Note) \* = Invalid

● Character code and corresponding character pattern

| Higher<br>4 bit<br>Lower 4 bit | 0000         | 0001             | 0010     | 0011 | 0100 | 0101 | 0110       | 0111     | 1000    | 1001     | 1010       | 1011        | 1100 | 1101       | 1110 | 1111         |

|--------------------------------|--------------|------------------|----------|------|------|------|------------|----------|---------|----------|------------|-------------|------|------------|------|--------------|

| XXXX0000                       | CGRAM<br>(0) |                  |          |      |      | :    | •          |          |         |          |            |             | -::: |            |      | <b>!</b> ":  |

| XXXX0001                       | (1)          |                  |          |      |      |      | -:::       | -:::     | ••••    |          |            |             | ::-  | <b>:</b> : |      |              |

| XXXX0010                       | (2)          |                  | 11       |      |      |      |            | F        |         |          | <b>!</b> " | ·:i*        | •    | ,x:        |      |              |

| XXXX0011                       | (3)          | :                |          | :    |      | :;   | :          | :::.     |         |          |            |             | :::  | ===        | :::. | :            |

| XXXX0100                       | (4)          |                  |          | ::   |      |      |            | ₩.       |         | .÷.      | ٠.         |             | -    |            | 11   |              |

| XXXX0101                       | (5)          |                  | ::::     | :    |      |      | <b>:::</b> | 11       | <b></b> |          | ::         | .:          |      |            |      |              |

| XXXX0110                       | (6)          |                  |          |      |      | Ņ    | #"         | i.,:     | ::::    | :::      |            |             |      |            |      | :            |

| XXXX0111                       | (7)          | $\ddot{\approx}$ |          | :    |      |      |            | 1        | 1       |          | ·;;;       |             | :::  | -:::       |      | <b>:</b>     |

| XXXX1000                       | (0)          | :::              | i.       |      |      | X    | ŀ          | ×        | .:ï.    |          | <u>-</u> i | •:::        |      | Į.         | .:   | $\mathbb{X}$ |

| XXXX1001                       | (1)          | ****             | <b>:</b> |      |      | Ÿ    |            | •:::     | #1.     | -        | :::::      | •           |      |            | •• • |              |

| XXXX1010                       | (2)          |                  | :        | ::   |      |      |            | :::      | ••••    | -        | ::::       |             | : `: | i          |      |              |

| XXXX1011                       | (3)          |                  |          | :    | K    |      | k          | -        |         | <b>.</b> | <b>:</b>   | ∄           |      |            | :::  |              |

| XXXX1100                       | (4)          | :::              | ::       | ∹.   |      | ***  | I.         |          | •       | :        | †::        | : <b>:</b>  | :    | =::        | :::- |              |

| XXXX1101                       | (5)          |                  | *****    |      | M    |      |            | <b>}</b> |         | :        |            | .: <u>;</u> | ···: | *          | #    |              |

| XXXX1110                       | (6)          | •                |          | ÷    | N    | ٠.   | 1"         |          | .==     | :::      |            |             |      | •.•        |      |              |

| XXXX1111                       | (7)          |                  |          | ::   |      |      | ::::       |          |         |          | :::        | :.!         |      |            |      |              |

#### Reset function

When you turn the power supply on using the internal reset circuit, the module automatically returns to its initial (reset) settings. At the initial settings, the following instructions are carried out.

## (1) Clear display

The busy flag remains in the busy condition (BF = 1) until initialization is completed. This takes 15 ms.

#### (2) Function set

DL = 1: 8-bit interface data length

N = 1

$F = 0: 5 \times 7$  dot matrix

(3) Display on/off control

D = 0: Display off

C = 0: Cursor off

B = 0: Blinking off

(4) Entry mode set

1/D = 1: +1 (increment)

S = 0: No shift

#### (5) Select DD RAM

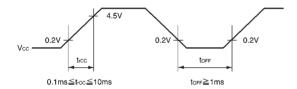

Depending on the power supply's rise and fall times when it is turned on, there may be times when the initialization cannot be completed. Therefore, be aware of the following timing relationship.

topp regulates the power supply breaks, or on and off times.

Note) When the above power supply conditions are not met, the internal reset circuit will not operate properly.