## **OVERVIEW**

The SM1126 Series are melody ICs for use in mobile telecommunications equipment. A maximum of 15 melodies can be stored in programmable ROM and one in built-in read/write SRAM.

## **FEATURES**

- 2.0 to 3.6 V supply voltage

- Maximum of 16 melody selections (15 in ROM + 1 in SRAM)

- Level hold playback mode

- External reference clock input versions and builtin RC oscillator versions available, set by masterslice option (RC oscillator versions require an external resistor and capacitor).

- Selectable clock frequencies (fixed for all melodies)

- External clock input versions (6 frequencies)

- 32.768 kHz system: 32.768, 65.536 and 131.072 kHz

- 38.4 kHz system: 38.4, 76.8 and 153.6 kHz

- Built-in RC oscillator versions (1 frequency)

131.072 kHz

- 2-pin serial data melody selection and 1-pin melody playback control

- Parity check function

- Delivery pattern alarm

- Power save function

- External clock input versions Clock gating in non-play modes

- Built-in RC oscillator versions Oscillator stopped in non-play modes

## **ORDERING INFORMATION**

| Device    | Package    |

|-----------|------------|

| SM1126××V | 8-pin VSOP |

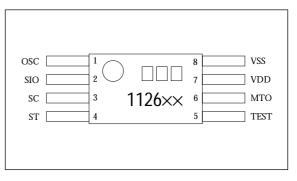

## PINOUT

(Top View)

8-pin VSOP

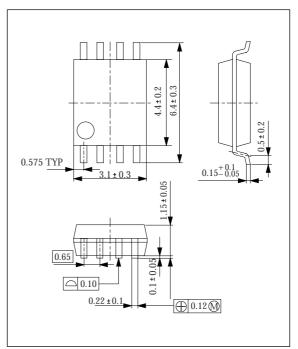

# PACKAGE DIMENSIONS

(Unit: mm)

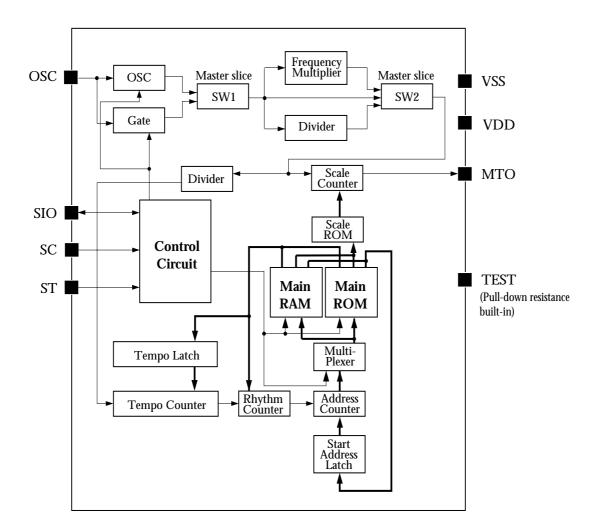

## **BLOCK DIAGRAM**

## **PIN DESCRIPTION**

| Number | Name                                                                                                          | Function                                                                                                                                                              |  |  |  |

|--------|---------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1      | OSC                                                                                                           | Built-in RC oscillator option: External resistor and capacitor connection pins<br>External clock input option: External reference clock input (gate circuit built-in) |  |  |  |

| 2      | SIO Playback control serial interface data input. During parity check, the G flag is output while ST is HIGH. |                                                                                                                                                                       |  |  |  |

| 3      | SC                                                                                                            | Playback control serial interface clock input                                                                                                                         |  |  |  |

| 4      | ST                                                                                                            | Play mode: Playback start/stop control signal input<br>Write mode: Serial interface data write control signal input                                                   |  |  |  |

| 5      | TEST                                                                                                          | Test input. Pull-down resistor built-in. Leave open or connect to VSS.                                                                                                |  |  |  |

| 6      | MTO                                                                                                           | Playback melody signal output                                                                                                                                         |  |  |  |

| 7      | VDD                                                                                                           | Supply                                                                                                                                                                |  |  |  |

| 8      | VSS                                                                                                           | Ground                                                                                                                                                                |  |  |  |

# **SPECIFICATIONS**

# **Absolute Maximum Ratings**

| Parameter                 | Symbol                           | Condition | Rating                           | Unit |

|---------------------------|----------------------------------|-----------|----------------------------------|------|

| Supply voltage range      | V <sub>DD</sub> -V <sub>SS</sub> |           | -0.3 to 5.0                      | V    |

| Input voltage range       | V <sub>IN</sub>                  |           | $V_{SS} - 0.2$ to $V_{DD} + 0.2$ | V    |

| Power dissipation         | PD                               |           | 100                              | mW   |

| Storage temperature range | T <sub>stg</sub>                 |           | -40 to 125                       |      |

| Soldering temperature     | T <sub>sld</sub>                 |           | 255                              | °C   |

| Soldering time            | t <sub>sld</sub>                 |           | 10                               | S    |

## **Recommended Operating Conditions**

$V_{SS} = 0 V$

| Parameter             | Symbol           | Condition | Rating     | Unit |

|-----------------------|------------------|-----------|------------|------|

| Supply voltage        | V <sub>DD</sub>  |           | 2.0 to 3.6 | V    |

| Operating temperature | T <sub>opr</sub> |           | -20 to 70  | °C   |

## **DC Characteristics**

$T_a = -20$  to 70 °C,  $V_{SS} = 0$  V,  $V_{DD} = 2.0$  to 3.6 V

| Deremeter                | Symbol           | Condition                                                                                                                                                                                                                            |                       | Rating  |                       | Unit   |

|--------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|---------|-----------------------|--------|

| Parameter                | Symbol           | Condition                                                                                                                                                                                                                            | min                   | typ     | max                   | Unit   |

| Supply voltage           | V <sub>DD</sub>  |                                                                                                                                                                                                                                      | 2.0                   | 3.0     | 3.6                   | V      |

| Current consumption (1)  | I <sub>DD1</sub> | Non-playback mode, T <sub>a</sub> = 25°C                                                                                                                                                                                             | -                     | _       | 0.5                   | μA     |

| Current consumption (2)  | I <sub>DD2</sub> | External clock input option: Playback mode, MTO pin open                                                                                                                                                                             | -                     | 25      | 200                   | μA     |

| Current consumption (3)  | I <sub>DD3</sub> | Built-in RC oscillator option: Playback mode,<br>MTO pin open                                                                                                                                                                        | -                     | 215     | 600                   | μA     |

|                          | V <sub>IH</sub>  | External clock input option: ST, SIO, SC and                                                                                                                                                                                         | V <sub>DD</sub> – 0.2 | -       | V <sub>DD</sub>       | V      |

| Input voltage            | V <sub>IL</sub>  | OSC pins, Built-in RC oscillator option: ST,<br>SIO and SC pins                                                                                                                                                                      | V <sub>SS</sub>       | -       | V <sub>SS</sub> + 0.2 | V      |

| Input oursont (1)        | I <sub>IH1</sub> | $V_{IH} = V_{DD}$ , $T_a = 25^{\circ}C$<br>External clock input option: ST, SIO, SC and<br>OSC pins, Built-in RC oscillator option: ST,<br>SIO and SC pins                                                                           | _                     | -       | 0.5                   | μΑ     |

| Input current (1)        | I <sub>IL1</sub> | $\label{eq:VIL} \begin{array}{l} V_{IL} = 0 \mbox{ V}, T_a = 25^{\circ}\mbox{C} \\ \mbox{External clock input option: ST, SIO, SC and} \\ \mbox{OSC pins, Built-in RC oscillator option: ST,} \\ \mbox{SIO and SC pins} \end{array}$ | _                     | _       | 0.5                   | μA     |

| Input current (2)        | I <sub>IH2</sub> | TEST pin, V <sub>IH</sub> = V <sub>DD</sub>                                                                                                                                                                                          | -                     | -       | 200                   | μA     |

| Start voltage            | V <sub>OPN</sub> | TEST pin                                                                                                                                                                                                                             | -                     | -       | 0.1                   | V      |

| Output wells as (1)      | V <sub>OH1</sub> | SIO pin, I <sub>OH1</sub> = 1 mA, V <sub>DD</sub> = 2.4 V                                                                                                                                                                            | V <sub>DD</sub> - 0.4 | -       | V <sub>DD</sub>       | V      |

| Output voltage (1)       | V <sub>OL1</sub> | SIO pin, I <sub>OL1</sub> = 1 mA, V <sub>DD</sub> = 2.4 V                                                                                                                                                                            | V <sub>SS</sub>       | -       | V <sub>SS</sub> + 0.4 | V      |

| Output voltage (2)       | V <sub>OH2</sub> | MTO pin, I <sub>OH2</sub> = 1 mA                                                                                                                                                                                                     | V <sub>DD</sub> - 0.4 | -       | V <sub>DD</sub>       | V      |

| Output voltage (2)       | V <sub>OL2</sub> | MTO pin, I <sub>OL2</sub> = 1 mA                                                                                                                                                                                                     | V <sub>SS</sub>       | -       | V <sub>SS</sub> + 0.4 | V      |

|                          |                  | Built-in RC oscillator option: NPC test board measurement, V <sub>DD</sub> = 3.0 V, R <sub>O</sub> = 82 k $\Omega$ , C <sub>O</sub> = 130 pF                                                                                         | 117.965               | 131.072 | 144.179               | kHz    |

| Frequency stability      | Δf/f             | Built-in RC oscillator option                                                                                                                                                                                                        | -                     | 0.2     | -                     | %/0.1V |

| Oscillator start voltage | V <sub>DOB</sub> | Built-in RC oscillator option                                                                                                                                                                                                        | -                     | -       | 1.6                   | V      |

| Oscillator stop voltage  | V <sub>DOS</sub> | Built-in RC oscillator option                                                                                                                                                                                                        | -                     | -       | 1.6                   | V      |

## **AC Characteristics**

$T_a = -20$  to 70 °C,  $V_{SS} = 0$  V,  $V_{DD} = 2.0$  to 3.6 V

| Parameter                      | Cymhol                                   | Condition                                                  | Rating |     |     |      |  |

|--------------------------------|------------------------------------------|------------------------------------------------------------|--------|-----|-----|------|--|

| Parameter                      | Symbol                                   | Condition                                                  | min    | typ | max | Unit |  |

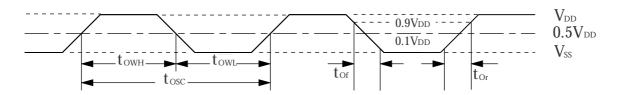

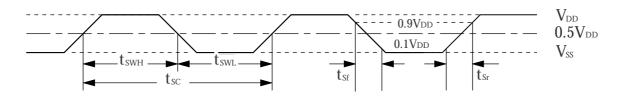

| OSC pulse cycle                | t <sub>osc</sub>                         |                                                            | 4.0    | -   | -   | μs   |  |

| OSC HIGH-level pulsewidth      | t <sub>оwн</sub>                         |                                                            | 2.0    | -   | -   | μs   |  |

| OSC LOW-level pulsewidth       | towl                                     | "OSC input pulse (external clock<br>input version)" timing | 2.0    | -   | -   | μs   |  |

| OSC pulse rise time            | t <sub>Or</sub>                          |                                                            | _      | -   | 200 | ns   |  |

| OSC pulse fall time            | t <sub>Of</sub>                          |                                                            | _      | -   | 200 | ns   |  |

| SC pulsewidth                  | t <sub>SC</sub>                          |                                                            | 4.0    | -   | -   | μs   |  |

| SC HIGH-level pulsewidth       | C HIGH-level pulsewidth t <sub>SWH</sub> |                                                            | 2.0    | -   | -   | μs   |  |

| SC LOW-level pulsewidth        | t <sub>SWL</sub>                         | "SC input pulse" timing                                    | 2.0    | -   | -   | μs   |  |

| SC pulse rise time             | t <sub>Sr</sub>                          |                                                            | _      | -   | 200 | ns   |  |

| SC pulse fall time             | t <sub>Sf</sub>                          |                                                            | _      | -   | 200 | ns   |  |

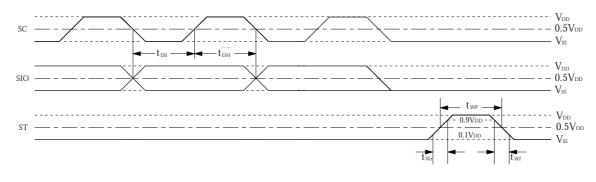

| SIO-SC setup time              | t <sub>DS</sub>                          |                                                            | 2.0    | -   | -   | μs   |  |

| SIO-SC hold time               | t <sub>DH</sub>                          |                                                            | 2.0    | -   | -   | μs   |  |

| ST input write pulsewidth      | t <sub>WP</sub>                          | "SC-SIO-ST serial input pulse"<br>timing                   | 2.0    | _   | -   | μs   |  |

| ST input write pulse rise time | t <sub>Wr</sub>                          |                                                            | _      | -   | 200 | ns   |  |

| ST input write pulse fall time | t <sub>Wf</sub>                          |                                                            | _      | -   | 200 | ns   |  |

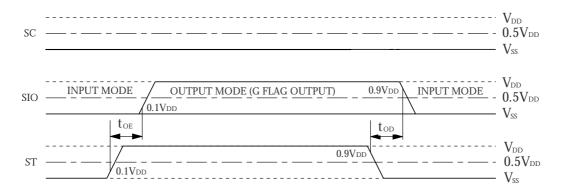

| SIO output enable delay        | t <sub>OE</sub>                          | "SIO parity check G-flag output                            | _      | -   | 600 | ns   |  |

| SIO output disable delay       | t <sub>od</sub>                          | data" timing                                               | _      | -   | 600 | ns   |  |

## OSC input pulse (external clock input version)

## SC input pulse

#### SC-SIO-ST serial input pulse

ST must be set to LOW when switching ST

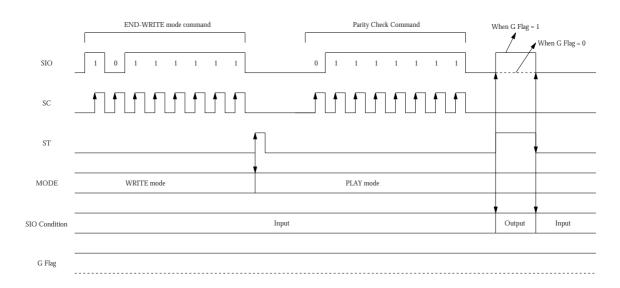

### SIO parity check G-flag output data

ST must be set to LOW when switching ST

### FUNCTIONAL DESCRIPTION

#### **Control Functions**

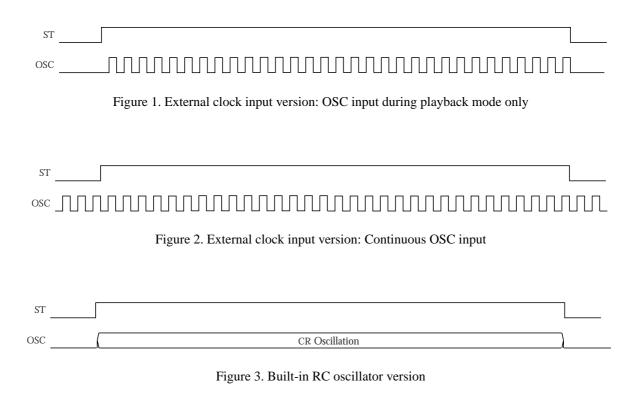

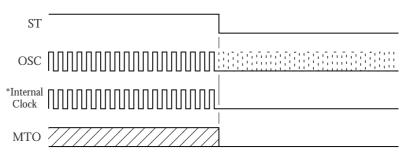

#### External reference clock

SM1126 Series devices are available in external clock input versions and built-in RC oscillator versions, set by master-slice option. In the case of the built-in RC oscillator option, an external resistor and capacitor is required for the oscillator function.

SM1126 Series devices can operate at 6 selectable reference clock frequencies. All melodies playback at the fixed speed set by the reference clock frequency. External clock input versions operate at one of 6 selectable clock frequencies, as shown in table 1. Built-in RC oscillator versions operate at only one oscillator frequencies—131.072 kHz.

| Frequency<br>system | Sel        | ectable frequenc | cies        |

|---------------------|------------|------------------|-------------|

| 32.768 kHz          | 32.768 kHz | 65.536 kHz       | 131.072 kHz |

| 38.4 kHz            | 38.4 kHz   | 76.8 kHz         | 153.6 kHz   |

Table 1. Reference clock frequencies (external clock)

#### **Power-save function**

In external clock input versions, the external reference clock input is used during playback mode only and is otherwise ignored. If a clock signal is input when not in playback mode (when ST is LOW), the gate circuit switches to cutoff the external reference clock signal from entering the device, preventing unwanted current flow.

In built-in RC oscillator versions, the oscillator is stopped when not in playback mode (when ST is LOW), preventing unwanted current flow.

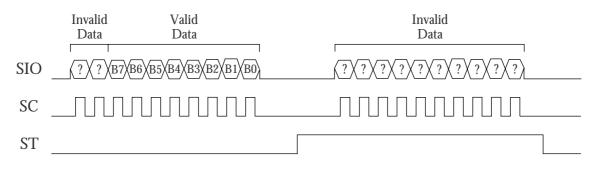

#### Serial inputs

Serial data is input on SIO in sync with the SC clock in 8-bit units when ST is LOW. Data is not accepted when ST is HIGH. When ST goes HIGH, the 8-bit data is latched. Note that if the input data exceeds 8 bits in length, the most recent 8 bits are used and any preceding bits are ignored. Data is in MSB first format.

Input data is interpreted as a command or as a data word (in write mode), depending on the current operating mode of the device. There are 3 types of commands:

- Playback start command

- SRAM write command

- End-of-write command

The SRAM write command is used to invoke write mode operation, and end-of-write command is used to return to play mode operation. In write mode, however, data is interpreted as data words to be written to SRAM.

Note that pin SIO is an output pin only when the parity check command is executed. At all other times, SIO is an input pin.

Pin SC should be LOW when either a LOW-to-HIGH or HIGH-to-LOW transition occurs on pin ST.

#### Figure 4. Serial input timing

#### **Playback control**

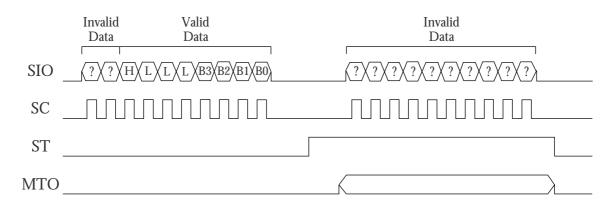

The ST pin controls the start of playback. While ST is HIGH, the melody is played repeatedly, and when ST goes LOW, playback stops. Melodies are selected by input serial data on pins SIO and SC, as shown in table 2. The melody select command comprises a fixed code (1000) followed by 4 melody select data bits (B3 to B0). The 8 bits of data are retained even after playback. If serial data is input during playback, the data is ignored and playback continues.

Pin SC should be LOW when either a LOW-to-HIGH or HIGH-to-LOW transition occurs on pin ST.

Figure 5. Serial data input timing

| B 3 | B 2 | B1 | B0 | ST                | Melody     | B 3 | B 2 | B1 | B0 | ST                | Melody      |

|-----|-----|----|----|-------------------|------------|-----|-----|----|----|-------------------|-------------|

| L   | L   | L  | L  | $L \rightarrow H$ | 1st melody | Н   | L   | L  | L  | $L \rightarrow H$ | 9th melody  |

| L   | L   | L  | Н  | $L \rightarrow H$ | 2nd melody | Н   | L   | L  | Н  | $L \rightarrow H$ | 10th melody |

| L   | L   | Н  | L  | $L \rightarrow H$ | 3rd melody | Н   | L   | Н  | L  | $L \rightarrow H$ | 11th melody |

| L   | L   | Н  | Н  | $L \rightarrow H$ | 4th melody | Н   | L   | Н  | Н  | $L \rightarrow H$ | 12th melody |

| L   | Н   | L  | L  | $L \rightarrow H$ | 5th melody | Н   | Н   | L  | L  | $L \rightarrow H$ | 13th melody |

| L   | Н   | L  | Н  | $L \rightarrow H$ | 6th melody | Н   | Н   | L  | Н  | $L \rightarrow H$ | 14th melody |

| L   | н   | Н  | L  | $L \rightarrow H$ | 7th melody | Н   | Н   | Н  | L  | $L \rightarrow H$ | 15th melody |

| L   | Н   | Н  | Н  | $L \rightarrow H$ | 8th melody | Н   | Н   | Н  | Н  | $L \rightarrow H$ | SRAM melody |

Table 2. Serial data melody select

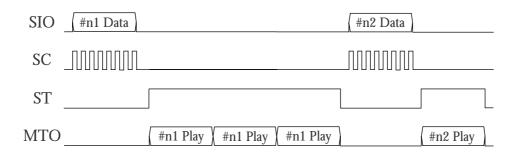

Melody plays repeatedly when ST is HIGH, and stops immediately when ST goes LOW.

Figure 6. Melody repetition timing

### **Playback timing diagrams**

#### **Playback start**

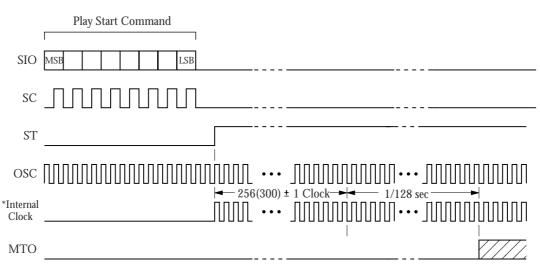

Playback starts after an interval t<sub>ST</sub> after ST goes HIGH.

When the reference clock frequency is 32.768 kHz,  $t_{ST} = (256 \pm 1 \text{ oscillator cycles}) + 1/128 \text{ seconds}$ . When the reference clock frequency is 38.4 kHz,  $t_{ST} = (300 \pm 1 \text{ oscillator cycles}) + 1/128 \text{ seconds}$ .

Figure 7. Playback start timing

#### **Playback stop**

Playback stops immediately when ST goes LOW. In external clock input versions, the IC internal clock also stops when ST goes LOW, regardless of whether or not there is a clock input signal on pin OSC. In built-in RC oscillator versions, the oscillator also stops when ST goes LOW.

Figure 8. Stop timing

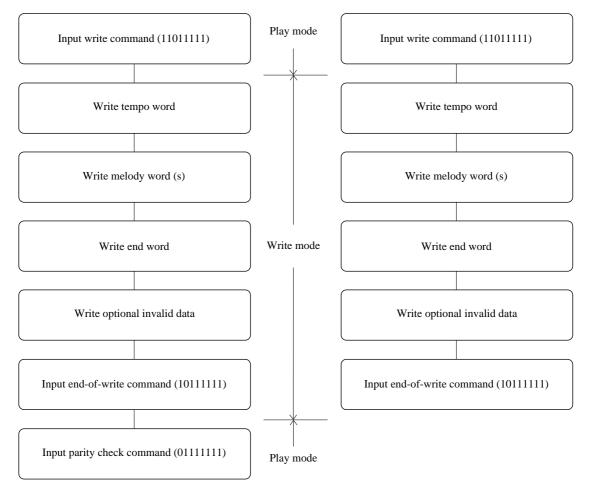

### Write Mode Control

#### Write sequence

The SM1126 Series devices can accept data words written to the built-in SRAM to play any melody. The SRAM write sequence is described below.

- 1. Write the SRAM write command (11011111) to invoke write mode.

- 2. Write the tempo word (parity check ON/OFF selectable).

- 3. Write all necessary melody data words (parity check ON/OFF selectable).

- 4. Write the melody end word (parity check ON/OFF selectable).

- 5. Optionally, write extra data words (these are ignored).

- 6. Write the end-of-write command (10111111) to return to play mode.

- 7. If parity check was ON, write the parity check command (01111111) to perform an error check.

The built-in SRAM can store 64 words, so all melody and end words must fit within this limit. Note that the tempo word is not stored in SRAM, but in a separate register. Playback of melodies stored in SRAM begins from the SRAM leading address and continues until the end word is detected, at which point playback continues again from the SRAM leading address. All data in SRAM after the end word is ignored.

Example 1. Parity check selected

Example 2. Parity check not selected

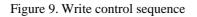

#### Write command

The SRAM write command (11011111), shown below, is used to invoke write mode.

Figure 10. Write command timing

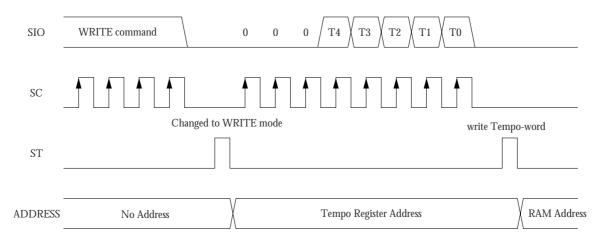

#### Tempo word

The tempo word controls the melody playback speed. The tempo word comprises a fixed code (000) followed by the tempo code (T4 to T0), as shown below. The tempo word is always the first word written after invoking write mode, and all subsequent words are melody data words.

Figure 11. Tempo word timing

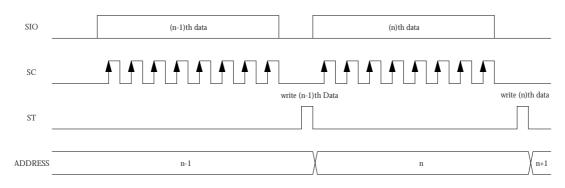

#### Melody words

Melody words contain all the information needed for playback of a single note, including the note duration and type (name or rest). Each melody word comprises a 3-bit length code (R2 to R0) followed by a 5-bit type code (S4 to S0).

Figure 12. Melody word timing

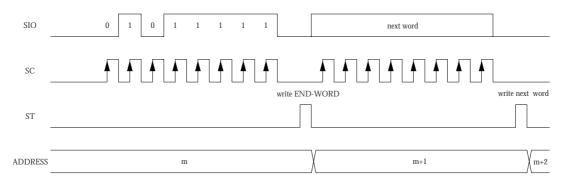

### End word

The end word (01011111) indicates the end of the melody. When the end word is detected during melody playback, operation returns to the SRAM leading address. All data in SRAM after the end word is ignored.

Figure 13. End word timing

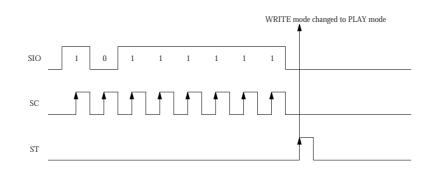

#### **End-of-write command**

The end-of-write command (10111111) is used to return to play mode from write mode. This command should be executed when power is first applied to set play mode.

Figure 14. End-of-write command timing

#### Parity check command

Data words (tempo word, melody words, end word) can have an optional parity bit added, forming 9-bit data words, for a parity check function. The parity check command is executed in play mode, immediately after the end-of-write command is executed.

The parity bit is added at the beginning of the data word. Note that the last 8 bits are always the valid data bits. The parity check function performs an odd parity check (an odd number of 1s within the 9-bit data). If the parity check command is not executed, play mode operation continues using the valid 8 bits of data in each data word.

The parity check sequence is described below.

- 1. The internal G flag (Good flag) is set to 1 when the write command is executed.

- 2. When writing data words, the G flag remains set to 1 for odd parity, but is set to 0 if even parity is detected.

- 3. The G flag remains set to 1 only if all data words have odd parity.

- 4. Write the end-of-write command to return to play mode.

- 5. Write the parity check command.

- 6. When ST is HIGH, the SIO pin functions as the G flag output.

- 7. When ST goes LOW, the G flag output is released.

Figure 15. Parity check timing

### **Command summary**

| Command              | MSB | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | LSB |

|----------------------|-----|-------|-------|-------|-------|-------|-------|-----|

| Melody start command | 1   | 0     | 0     | 0     | B3    | B2    | B1    | B0  |

| Write command        | 1   | 1     | 0     | 1     | 1     | 1     | 1     | 1   |

| Tempo word           | 0   | 0     | 0     | T4    | Т3    | T2    | T1    | TO  |

| Melody word          | R2  | R1    | R0    | S4    | S3    | S2    | S1    | S0  |

| End word             | 0   | 1     | 0     | 1     | 1     | 1     | 1     | 1   |

| End-of-write command | 1   | 0     | 1     | 1     | 1     | 1     | 1     | 1   |

| Parity check command | 0   | 1     | 1     | 1     | 1     | 1     | 1     | 1   |

### **Musical Specifications**

#### Maximum program steps

A maximum of 256 steps can be programmed into mask-programmable ROM, and a maximum of 64 steps (including one end word) can be stored in built-in SRAM. Each step represents either a note (sound pitch and length) a rest, or a tie.

### Note length (including rests)

Eight rhythm values for notes and rests can be programmed. Also, 2 or more notes can be musically tied.

Table 3. Rhythm values

| Typo |   | Code     |    |    |                  |    |     |               |  |  |  |

|------|---|----------|----|----|------------------|----|-----|---------------|--|--|--|

| Туре | 0 | 1        | 2  | 3  | 4                | 5  | 6   | 7             |  |  |  |

| Note | ٩ | <b>)</b> | Þ. |    | 3                | ۵. | 0   | <i>.</i>      |  |  |  |

| Rest | 7 | ۶        | 7. | ** | ( <sup>4</sup> ) | ۶. | -=- | _ <b>_</b> _` |  |  |  |

### Pitch and scale

SM1126 Series devices support 27 pitches from F4 to G6. The pitch varies with the clock frequency, as shown in the frequency listing in table 4. The reference clock selected at master-slice does not affect the pitch range.

Also, two pitches higher than G6 can be set as alarm pitches in mask ROM. Note that an alarm pitch option cannot be specified in SRAM.

The frequency error calculation for a given pitch is shown below.

Error calculation: (A4 pitch with 32.768 kHz clock)

$$1200 \times \log_2 \frac{\text{Output frequency}}{\text{Reference frequency}} = 1200 \times \frac{\log_{10} \frac{\text{Output frequency}}{\text{Reference frequency}}}{\log_{10} 2}$$

$$\approx 3986.3 \times \log_{10} \frac{\text{Output frequency}}{\text{Reference frequency}}$$

$$\approx 3986.3 \times \log_{10} \frac{439.839}{440.000}$$

≈ -0.63 cent

Table 4. Frequency range

|            | No  | ote co | de |     | System   | clock                  | 32                   | 2.768 kHz syste   | m                        | 38.4 kHz system      |                   |                          |

|------------|-----|--------|----|-----|----------|------------------------|----------------------|-------------------|--------------------------|----------------------|-------------------|--------------------------|

| <b>S</b> 4 | \$3 | S 2    | S1 | S 0 | Pitch    | Reference<br>frequency | Frequency<br>divider | Frequency<br>(Hz) | Relative<br>error (cent) | Frequency<br>divider | Frequency<br>(Hz) | Relative<br>error (cent) |

| 0          | 0   | 0      | 0  | 0   | Rest     | -                      | -                    | -                 | -                        | -                    | -                 | -                        |

| 0          | 0   | 0      | 0  | 1   | F4       | 349.228                | 188                  | 348.596           | -3.14                    | 220                  | 349.091           | -0.68                    |

| 0          | 0   | 0      | 1  | 0   | F#4      | 369.994                | 177                  | 370.260           | 1.24                     | 208                  | 369.231           | -3.58                    |

| 0          | 0   | 0      | 1  | 1   | G4       | 391.995                | 167                  | 392.431           | 1.92                     | 196                  | 391.837           | -0.70                    |

| 0          | 0   | 1      | 0  | 0   | G#4      | 415.305                | 158                  | 414.785           | -2.17                    | 185                  | 415.135           | -0.71                    |

| 0          | 0   | 1      | 0  | 1   | A4       | 440.000                | 149                  | 439.839           | -0.63                    | 175                  | 438.857           | -4.50                    |

| 0          | 0   | 1      | 1  | 0   | A#4      | 466.164                | 141                  | 464.794           | -5.09                    | 165                  | 465.455           | -2.64                    |

| 0          | 0   | 1      | 1  | 1   | B4       | 493.883                | 133                  | 492.752           | -3.97                    | 156                  | 492.308           | -5.53                    |

| 0          | 1   | 0      | 0  | 0   | C5       | 523.251                | 125                  | 524.288           | 3.43                     | 147                  | 522.449           | -2.66                    |

| 0          | 1   | 0      | 0  | 1   | C#5      | 554.365                | 118                  | 555.390           | 3.20                     | 139                  | 552.518           | -5.78                    |

| 0          | 1   | 0      | 1  | 0   | D5       | 587.330                | 112                  | 585.143           | -6.46                    | 131                  | 586.260           | -3.16                    |

| 0          | 1   | 0      | 1  | 1   | D#5      | 622.254                | 105                  | 624.152           | 5.27                     | 123                  | 624.390           | 5.93                     |

| 0          | 1   | 1      | 0  | 0   | E5       | 659.255                | 99                   | 661.980           | 7.14                     | 116                  | 662.069           | 7.37                     |

| 0          | 1   | 1      | 0  | 1   | F5       | 698.456                | 94                   | 697.191           | -3.14                    | 110                  | 698.182           | -0.68                    |

| 0          | 1   | 1      | 1  | 0   | F#5      | 739.989                | 89                   | 736.360           | -8.51                    | 104                  | 738.462           | -3.58                    |

| 0          | 1   | 1      | 1  | 1   | G5       | 783.991                | 84                   | 780.190           | -8.41                    | 98                   | 783.673           | -0.70                    |

| 1          | 0   | 0      | 0  | 0   | G#5      | 830.609                | 79                   | 829.570           | -2.17                    | 92                   | 834.783           | 8.68                     |

| 1          | 0   | 0      | 0  | 1   | A5       | 880.000                | 74                   | 885.622           | 11.02                    | 87                   | 882.759           | 5.42                     |

| 1          | 0   | 0      | 1  | 0   | A#5      | 932.328                | 70                   | 936.229           | 7.23                     | 82                   | 936.585           | 7.89                     |

| 1          | 0   | 0      | 1  | 1   | B5       | 987.767                | 66                   | 992.970           | 9.10                     | 78                   | 984.615           | -5.53                    |

| 1          | 0   | 1      | 0  | 0   | C6       | 1046.502               | 63                   | 1040.254          | -10.37                   | 73                   | 1052.055          | 9.16                     |

| 1          | 0   | 1      | 0  | 1   | C#6      | 1108.731               | 59                   | 1110.780          | 3.20                     | 69                   | 1113.043          | 6.72                     |

| 1          | 0   | 1      | 1  | 0   | D6       | 1174.659               | 56                   | 1170.286          | -6.46                    | 65                   | 1181.538          | 10.11                    |

| 1          | 0   | 1      | 1  | 1   | D#6      | 1244.508               | 53                   | 1236.528          | -11.14                   | 62                   | 1238.710          | -8.08                    |

| 1          | 1   | 0      | 0  | 0   | E6       | 1318.510               | 50                   | 1310.720          | -10.26                   | 58                   | 1324.138          | 7.37                     |

| 1          | 1   | 0      | 0  | 1   | F6       | 1396.913               | 47                   | 1394.383          | -3.14                    | 55                   | 1396.364          | -0.68                    |

| 1          | 1   | 0      | 1  | 0   | F#6      | 1479.978               | 44                   | 1489.455          | 11.05                    | 52                   | 1476.923          | -3.58                    |

| 1          | 1   | 0      | 1  | 1   | G6       | 1567.982               | 42                   | 1560.381          | -8.41                    | 49                   | 1567.347          | -0.70                    |

| 1          | 1   | 1      | 0  | 0   | AL1      | -                      | -                    | -                 | -                        | -                    | -                 | -                        |

| 1          | 1   | 1      | 0  | 1   | AL2      | -                      | -                    | -                 | -                        | -                    | -                 | -                        |

| 1          | 1   | 1      | 1  | 0   | Tie      | -                      | -                    | -                 | -                        | -                    | -                 | -                        |

| 1          | 1   | 1      | 1  | 1   | End word | -                      | -                    | -                 | -                        | -                    | -                 | -                        |

(Note) A4 is the following note.

Pitches AL1 and AL2 are optional alarm pitches which can take any value higher than G6, set in mask ROM. This option is not supported in SRAM.

#### Tempo

There are 29 tempos that can be selected for each melody. The tempo does not vary with the clock frequency.

Table 5. Tempo range

| Code | Frequency divider | Tempo       | <b>]</b> = |

|------|-------------------|-------------|------------|

| 03   | 4                 |             | 320.0      |

| 04   | 5                 | Prestissimo | 256.0      |

| 05   | 6                 |             | 213.3      |

| 06   | 7                 | Presto      | 182.9      |

| 07   | 8                 |             | 160.0      |

| 08   | 9                 | Allegro     | 142.2      |

| 09   | 10                |             | 128.0      |

| AO   | 11                | Moderato    | 116.4      |

| OB   | 12                |             | 106.7      |

| 0C   | 13                |             | 98.5       |

| 0D   | 14                | Andante     | 91.4       |

| 0E   | 15                | Anuante     | 85.3       |

| 0F   | 16                |             | 80.0       |

| 10   | 17                |             | 75.3       |

| 11   | 18                | Adagio      | 71.1       |

| 12   | 19                |             | 67.4       |

| 13   | 20                | Larghetto   | 64.0       |

| 14   | 21                | Laighello   | 61.0       |

| 15   | 22                |             | 58.2       |

| 16   | 23                |             | 55.7       |

| 17   | 24                |             | 53.3       |

| 18   | 25                |             | 51.2       |

| 19   | 26                | ]           | 49.2       |

| 1A   | 27                | Largo       | 47.4       |

| 1B   | 28                | ]           | 45.7       |

| 1C   | 29                |             | 44.1       |

| 1D   | 30                |             | 42.7       |

| 1E   | 31                |             | 41.3       |

| 1F   | 32                | 1           | 40.0       |

Quarter note () length = {1536 (32.768 kHz system) or 1800 (38.4 kHz system)} × tempo counter frequency divider  $\div$  clock frequency

(Ex. 1) Tempo code = 1F (divider = 32), clock frequency = 32.768 kHz (32.768 kHz system)  $1536 \times 32 \div 32768 = 1.5$  (seconds)

(Ex. 2) Tempo code = 18 (divider = 25), CLK frequency = 153.6 kHz (38.4 kHz system)  $1800 \times 25 \div 38400 = 1.17$  (seconds)

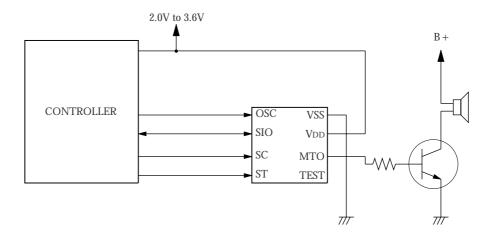

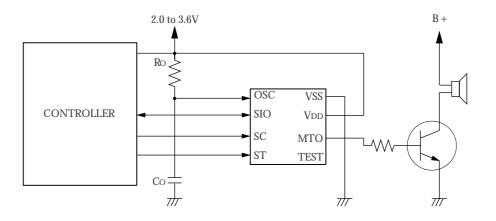

# **TYPICAL APPLICATION**

# **External Clock Input Versions**

## **Built-in RC Oscillator Versions**

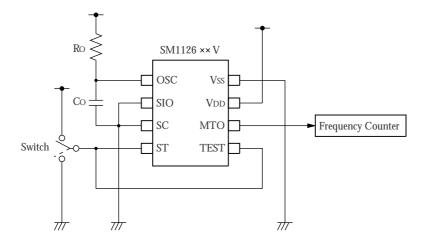

### **OSCILLATOR FREQUENCY MEASUREMENT**

The measurement circuit below shows a SM1126××V with built-in RC oscillator circuit and external RC oscillator components capacitor  $C_0$  and resistor  $R_0$ .

When ST is switched to  $V_{DD}$ , the oscillator starts and outputs a pulse on MTO with a frequency double that of the RC oscillator. The output pulse is counted using a frequency counter.

Note that the board mounting and wiring will marginally affect the output frequency, even for equivalent values for R<sub>0</sub> and C<sub>0</sub>.

NIPPON PRECISION CIRCUITS INC. reserves the right to make changes to the products described in this data sheet in order to improve the design or performance and to supply the best possible products. Nippon Precision Circuits Inc. assumes no responsibility for the use of any circuits shown in this data sheet, conveys no license under any patent or other rights, and makes no claim that the circuits are free from patent infringement. Applications for any devices shown in this data sheet are for illustration only and Nippon Precision Circuits Inc. makes no claim or warranty that such applications will be suitable for the use specified without further testing or modification. The products described in this data sheet are not intended to use for the apparatus which influence human lives due to the failure or malfunction of the products. Customers are requested to comply with applicable laws and regulations in effect now and hereinafter, including compliance with export controls on the distribution or dissemination of the products. Customers shall not export, directly or indirectly, any products without first obtaining required licenses and approvals from appropriate government agencies.

#### NIPPON PRECISION CIRCUITS INC.

4-3, Fukuzumi 2-chome Koto-ku, Tokyo 135-8430, Japan Telephone: 03-3642-6661 Facsimile: 03-3642-6698

NC9722BE 1998.12