# Simple Sequencers™ in 6-Lead SC70

# ADM1085/ADM1086/ADM1087/ADM1088

#### **FEATURES**

Provide programmable time delays between enable signals

Can be cascaded with power modules for multiple supply sequencing

Power supply monitoring from 0.6 V

**Output stages:**

High voltage (up to 22 V) open-drain output (ADM1085/ADM1087)

Push-pull output (ADM1086/ADM1088)

Capacitor-adjustable time delays

High voltage (up to 22 V) Enable and V<sub>IN</sub> inputs

Low power consumption (15 µA)

Specified over -40°C to +125°C temperature range

6-lead SC70 package

#### **APPLICATIONS**

Desktop/notebook computers, servers Low power portable equipment **Routers Base stations** Line cards **Graphics cards**

### **GENERAL DESCRIPTION**

The ADM1085/ADM1086/ADM1087/ADM1088 are simple sequencing circuits that provide a time delay between the enabling of voltage regulators and/or dc-dc converters at powerup in multiple supply systems. When the output voltage of the first power module reaches a preset threshold, a time delay is initiated before an enable signal allows subsequent regulators to power up. Any number of these devices can be cascaded with regulators to allow sequencing of multiple power supplies.

Threshold levels can be set with a pair of external resistors in a voltage divider configuration. By choosing appropriate resistor values, the threshold can be adjusted to monitor voltages as low as 0.6 V.

The ADM1086 and ADM1088 have push-pull output stages, with active-high (ENOUT) and active-low (ENOUT) logic outputs, respectively. The ADM1085 has an active-high (ENOUT) logic output; the ADM1087 has an active-low (ENOUT) output. Both the ADM1085 and ADM1087 have open-drain output stages that can be pulled up to voltage levels as high as 22 V through an external resistor. This level-shifting

### Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

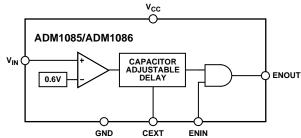

### **FUNCTIONAL BLOCK DIAGRAMS**

property ensures compatibility with enable input logic levels of different regulators and converters.

All four models have a dedicated enable input pin that allows the output signal to the regulator to be controlled externally. This is an active-high input (ENIN) for the ADM1085 and ADM1086, and an active-low input (ENIN) for the ADM1087 and ADM1088.

The simple sequencers are specified over the extended -40°C to +125°C temperature range. With low current consumption of 15 μA (typ) and 6-lead SC70 packaging, the parts are suitable for low-power portable applications.

Table 1. Selection Table

|          |              | Output Stage |            |

|----------|--------------|--------------|------------|

| Part No. | Enable Input | ENOUT        | ENOUT      |

| ADM1085  | ENIN         |              | Open-Drain |

| ADM1086  | ENIN         |              | Push-Pull  |

| ADM1087  | ENIN         | Open-Drain   |            |

| ADM1088  | ENIN         | Push-Pull    |            |

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 www.analog.com

Fax: 781.326.8703 © 2004 Analog Devices, Inc. All rights reserved.

# **TABLE OF CONTENTS**

| Specifications                               | Application Information 1        |

|----------------------------------------------|----------------------------------|

| Absolute Maximum Ratings 4                   | Sequencing Circuits              |

| ESD Caution                                  | Dual LOFO Sequencing             |

| Pin Configuration and Function Descriptions5 | Simultaneous Enabling            |

| Typical Performance Characteristics          | Power Good Signal Delays         |

| Circuit Information                          | Quad-Supply Power Good Indicator |

| Timing Characteristics and Truth Tables9     | Sequencing with FET Switches     |

| Capacitor-Adjustable Delay Circuit9          | Outline Dimensions               |

| Open-Drain and Push-Pull Outputs10           | Ordering Guide                   |

### **REVISION HISTORY**

7/04—Revision 0: Initial Version

# **SPECIFICATIONS**

$V_{\text{CC}}$  = full operating range,  $T_{\text{A}}$  =  $-40^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$  , unless otherwise noted.

Table 2.

| Parameter                                                          | Min                 | Тур   | Max                  | Unit   | Test Conditions/Comments                                                        |

|--------------------------------------------------------------------|---------------------|-------|----------------------|--------|---------------------------------------------------------------------------------|

| SUPPLY                                                             |                     |       |                      |        |                                                                                 |

| V <sub>CC</sub> Operating Voltage Range                            | 2.25                |       | 3.6                  | V      |                                                                                 |

| V <sub>IN</sub> Operating Voltage Range                            | 0                   |       | 22                   | V      |                                                                                 |

| Supply Current                                                     |                     | 10    | 15                   | μΑ     |                                                                                 |

| VIN Rising Threshold, VTH_RISING                                   | 0.56                | 0.6   | 0.64                 | V      | $V_{CC} = 3.3 \text{ V}$                                                        |

| V <sub>IN</sub> Falling Threshold, V <sub>TH_FALLING</sub>         | 0.545               | 0.585 | 0.625                | V      | $V_{CC} = 3.3 \text{ V}$                                                        |

| V <sub>IN</sub> Hysteresis                                         |                     | 15    |                      | mV     |                                                                                 |

| V <sub>IN</sub> to ENOUT/ENOUT Delay                               |                     |       |                      |        |                                                                                 |

| V <sub>IN</sub> Rising                                             |                     | 35    |                      | μs     | CEXT floating, C = 20 pF                                                        |

| -                                                                  |                     | 2     |                      | ms     | CEXT = 470 pF                                                                   |

| V <sub>IN</sub> Falling                                            |                     | 20    |                      | μs     | V <sub>IN</sub> = V <sub>TH_FALLING</sub> to (V <sub>TH_FALLING</sub> – 100 mV) |

| V <sub>IN</sub> Leakage Current                                    |                     | 170   |                      | μΑ     | V <sub>IN</sub> = 22 V                                                          |

| CEXT Charge Current                                                | 125                 | 250   | 375                  | nA     |                                                                                 |

| Threshold Temperature Coefficient                                  |                     | 30    |                      | ppm/°C |                                                                                 |

| ENIN/ENIN TO ENOUT/ENOUT Propagation                               |                     | 0.5   |                      | μs     | V <sub>IN</sub> > V <sub>TH_RISING</sub>                                        |

| Delay                                                              |                     |       |                      |        |                                                                                 |

| ENIN/ENIN Voltage Low                                              |                     |       | $0.3 \ V_{CC} - 0.2$ | V      |                                                                                 |

| ENIN/ENIN Voltage High                                             | $0.3  V_{CC} + 0.2$ |       |                      | V      |                                                                                 |

| ENIN/ENIN Leakage Current                                          |                     | 170   |                      | μΑ     | ENIN/ENIN = 22 V                                                                |

| ENOUT/ENOUT Voltage Low                                            |                     |       | 0.4                  | V      | V <sub>IN</sub> < V <sub>TH_FALLING</sub> (ENOUT),                              |

| J                                                                  |                     |       |                      |        | $V_{IN} > V_{TH\_RISING} (ENOUT),$                                              |

|                                                                    |                     |       |                      |        | I <sub>SINK</sub> = 1.2 mA                                                      |

| ENOUT/ENOUT Voltage High                                           | 0.8 V <sub>CC</sub> |       |                      | V      | $V_{IN} > V_{TH\_RISING}$ (ENOUT),                                              |

| (ADM1086/ADM1088)                                                  |                     |       |                      |        | V <sub>IN</sub> < V <sub>TH_FALLING</sub> (ENOUT),                              |

| <del></del>                                                        |                     |       |                      | 1.     | $I_{\text{SOURCE}} = 500  \mu\text{A}$                                          |

| ENOUT/ENOUT Open-Drain Output Leakage<br>Current (ADM1085/ADM1087) |                     |       | 0.4                  | μΑ     | ENOUT/ENOUT = 22 V                                                              |

## **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25$ °C, unless otherwise noted.

Table 3.

| Parameter                             | Rating          |

|---------------------------------------|-----------------|

| V <sub>CC</sub>                       | −0.3 V to +6 V  |

| V <sub>IN</sub>                       | −0.3 V to +25 V |

| CEXT                                  | −0.3 V to +6 V  |

| ENIN, ENIN                            | −0.3 V to +25 V |

| ENOUT, ENOUT (ADM1085, ADM1087)       | −0.3 V to +25 V |

| ENOUT, ENOUT (ADM1086, ADM1088)       | −0.3 V to +6 V  |

| Operating Temperature Range           | −40°C to +125°C |

| Storage Temperature Range             | −65°C to +150°C |

| $\theta_{JA}$ Thermal Impedance, SC70 | 146°C/W         |

| Lead Temperature                      |                 |

| Soldering (10 s)                      | 300°C           |

| Vapor Phase (60 s)                    | 215℃            |

| Infrared (15 s)                       | 220°C           |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although this product features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

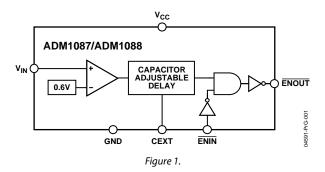

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 2. Pin Configuration

### **Table 4. Pin Function Descriptions**

| Pin No. | Mnemonic        | Description                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | ENIN, ENIN      | Enable Input. Controls the status of the enable output. Active high for ADM1085/ADM1086. Active low for ADM1087/ADM1088.                                                                                                                                                                                                                                                                                          |

| 2       | GND             | Ground.                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3       | V <sub>IN</sub> | Input for the Monitored Voltage Signal. Can be biased via a voltage divider resistor network to customize the effective input threshold. Can precisely monitor an analog power supply output signal and detect when it has powered up. The voltage applied at this pin is compared with a 0.6 V on-chip reference. With this reference, digital signals with various logic-level thresholds can also be detected. |

| 4       | ENOUT, ENOUT    | Enable Output. Asserted when the voltage at $V_{\text{IN}}$ is above $V_{\text{TH\_RISING}}$ and the time delay has elapsed, provided that the enable input is asserted. Active high for the ADM1085/ADM1086. Active low for the ADM1087/ADM1088.                                                                                                                                                                 |

| 5       | CEXT            | External Capacitor Pin. The capacitance on this pin determines the time delay on the enable output. The delay is seen only when the voltage at $V_{IN}$ rises past $V_{TH\_RISING}$ , and not when it falls below $V_{TH\_FALLING}$ .                                                                                                                                                                             |

| 6       | V <sub>CC</sub> | Power Supply.                                                                                                                                                                                                                                                                                                                                                                                                     |

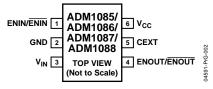

## TYPICAL PERFORMANCE CHARACTERISTICS

Figure 3.  $V_{IN}$  Threshold vs. Temperature

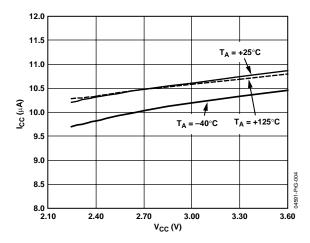

Figure 4. Supply Current vs. Supply Voltage

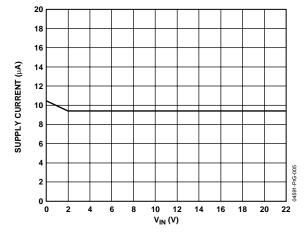

Figure 5. Supply Current vs. V<sub>IN</sub> Voltage

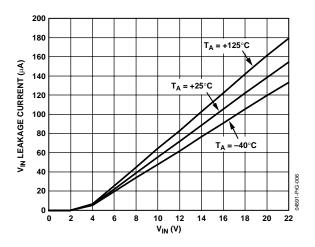

Figure 6. V<sub>IN</sub> Leakage Current vs. V<sub>IN</sub> Voltage

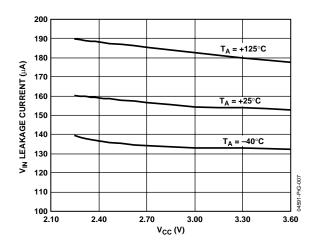

Figure 7. V<sub>IN</sub> Leakage Current vs. V<sub>CC</sub> Voltage

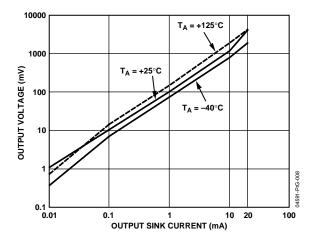

Figure 8. Output Voltage vs. Output Sink Current

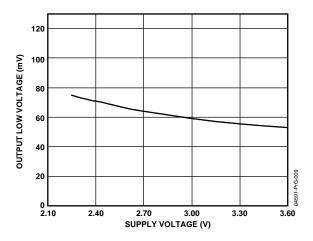

Figure 9. Output Low Voltage vs. Supply Voltage

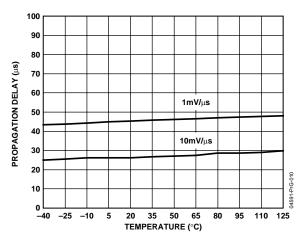

Figure 10. V<sub>CC</sub> Falling Propagation Delay vs. Temperature

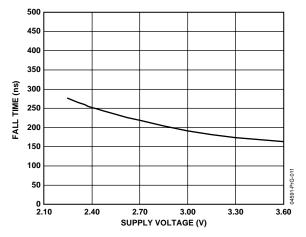

Figure 11. Output Fall Time vs. Supply Voltage

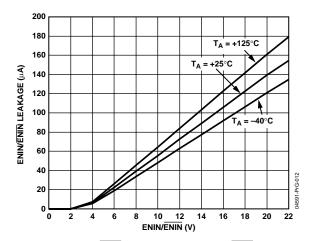

Figure 12. ENIN/ENIN Leakage Current vs. ENIN/ENIN Voltage

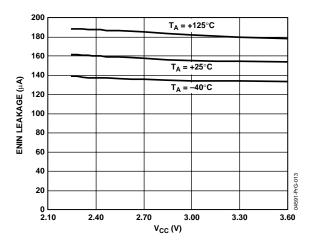

Figure 13. ENIN/ $\overline{ENIN}$  Leakage Current vs.  $V_{CC}$  Voltage

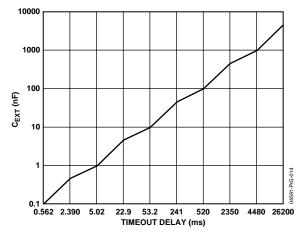

Figure 14. CEXT Capacitance vs. Timeout Delay

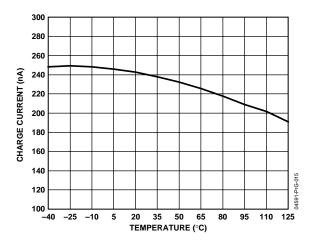

Figure 15. CEXT Charge Current vs. Temperature

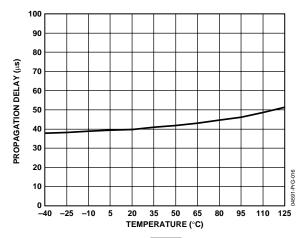

Figure 16. V<sub>IN</sub> to ENOUT/ENOUT Propagation Delay (CEXT Floating) vs. Temperature

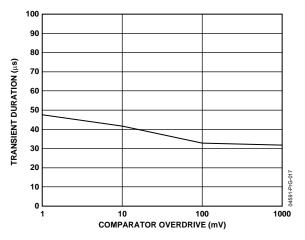

Figure 17. Maximum V<sub>IN</sub> Transient Duration vs. Comparator Overdrive

## CIRCUIT INFORMATION

### TIMING CHARACTERISTICS AND TRUTH TABLES

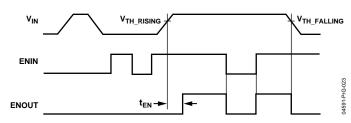

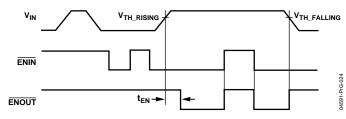

The enable outputs of the ADM1085/ADM1086/ADM1087/ ADM1088 are related to the  $V_{\rm IN}$  and enable inputs by a simple AND function. The enable output is asserted only if the enable input is asserted and the voltage at  $V_{\rm IN}$  is above  $V_{\rm TH\_RISING}$ , with the time delay elapsed. Table 5 and Table 6 show the enable output logic states for different  $V_{\rm IN}$ /enable input combinations when the capacitor delay has elapsed. The timing diagrams in Figure 18 and Figure 19 give a graphical representation of how the ADM1085/ADM1086/ADM1087/ADM1088 enable outputs respond to  $V_{\rm IN}$  and enable input signals.

Table 5. ADM1085/ADM1086 Truth Table

| V <sub>IN</sub>             | ENIN | ENOUT |

|-----------------------------|------|-------|

| <v<sub>TH_FALLING</v<sub>   | 0    | 0     |

| $<$ V <sub>TH_FALLING</sub> | 1    | 0     |

| $>V_{TH\_RISING}$           | 0    | 0     |

| $>V_{TH\_RISING}$           | 1    | 1     |

Table 6. ADM1087/ADM1088 Truth Table

| V <sub>IN</sub>           | ENIN | ENOUT |

|---------------------------|------|-------|

| <v<sub>TH_FALLING</v<sub> | 1    | 1     |

| <v<sub>TH_FALLING</v<sub> | 0    | 1     |

| >V <sub>TH_RISING</sub>   | 1    | 1     |

| >V <sub>TH_RISING</sub>   | 0    | 0     |

Figure 18. ADM1085/ADM1086 Timing Diagram

Figure 19. ADM1087/ADM1088 Timing Diagram

When  $V_{\rm IN}$  reaches the upper threshold voltage ( $V_{\rm TH\_RISING}$ ), an internal circuit generates a delay ( $t_{\rm EN}$ ) before the enable output is asserted. If  $V_{\rm IN}$  drops below the lower threshold voltage ( $V_{\rm TH\_FALLING}$ ), the enable output is deasserted immediately.

Similarly, if the enable input is disabled while  $V_{\rm IN}$  is above the threshold, the enable output deasserts immediately. <u>Unlike  $V_{\rm IN}$ , a low-to-high transition on ENIN (or high-to-low on ENIN)</u> does not yield a time delay on ENOUT (ENOUT).

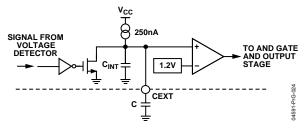

### CAPACITOR-ADJUSTABLE DELAY CIRCUIT

Figure 20 shows the internal circuitry used to generate the time delay on the enable output. A 250 nA current source charges a small internal parasitic capacitance,  $C_{\rm INT}$ . When the capacitor voltage reaches 1.2 V, the enable output is asserted. The time taken for the capacitor to reach 1.2 V, in addition to the propagation delay of the comparator, constitutes the enable timeout, which is typically 35  $\mu$ s.

To minimize the delay between  $V_{\rm IN}$  falling below  $V_{\rm TH\_FALLING}$  and the enable output de-asserting, an NMOS transistor is connected in parallel with  $C_{\rm INT}$ . The output of the voltage detector is connected to the gate of this transistor so that, when  $V_{\rm IN}$  falls below  $V_{\rm TH\_FALLING}$ , the transistor switches on and  $C_{\rm INT}$  discharges quickly.

Figure 20. Capacitor-Adjustable Delay Circuit

Connecting an external capacitor to the CEXT pin delays the rise time—and therefore the enable timeout—further. The relationship between the value of the external capacitor and the resulting timeout is characterized by the following equation:

$$t_{EN} = (C \times 4.8 \times 10^6) + 35 \,\mu s$$

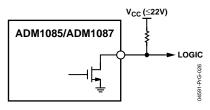

### **OPEN-DRAIN AND PUSH-PULL OUTPUTS**

The ADM1085 and ADM1087 have open-drain output stages that require an external pull-up resistor to provide a logic-high voltage level. The geometry of the NMOS transistor enables the output to be pulled up to voltage levels as high as 22 V.

Figure 21. Open-Drain Output Stage

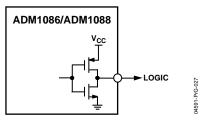

The ADM1086 and ADM1088 have push-pull (CMOS) output stages that require no external components to drive other logic circuits. An internal PMOS pull-up transistor provides the logic-high voltage level.

Figure 22. Push-Pull Output Stage

## APPLICATION INFORMATION

### **SEQUENCING CIRCUITS**

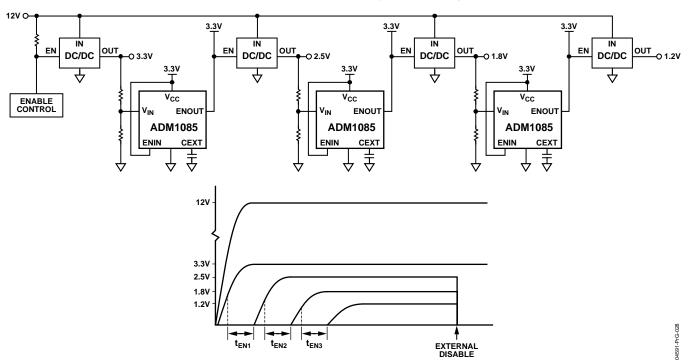

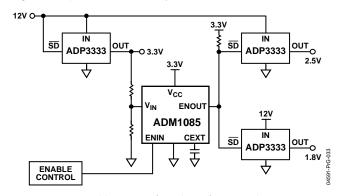

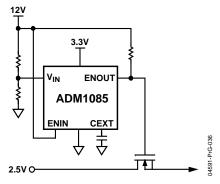

The ADM1085/ADM1086/ADM1087/ADM1088 are compatible with voltage regulators and dc-to-dc converters that have active-high or active-low enable or shutdown inputs, with a choice of open-drain or push-pull output stages. Figure 23 to Figure 25 illustrate how each of the ADM1085/ADM1086/ADM1087/ADM1088 simple sequencers can be used in multiple-supply systems, depending on which regulators are used and which output stage is preferred.

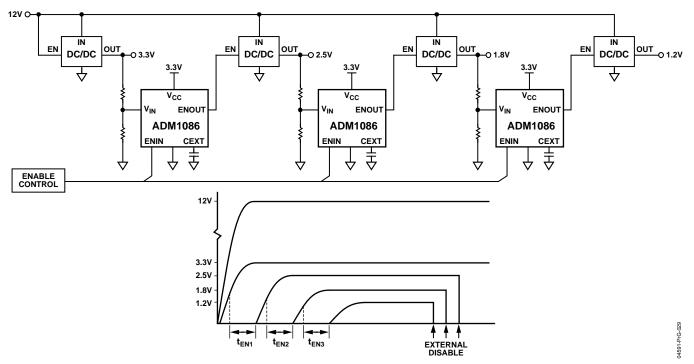

In Figure 23, three ADM1085s are used to sequence four supplies on power-up. Separate capacitors on the CEXT pins determine the time delays between enabling of the 3.3 V, 2.5 V, 1.8 V, and 1.2 V supplies. Because the dc/dc converters and ADM1085s are connected in cascade, and the output of any converter is dependent on that of the previous one, an external controller can disable all four supplies simultaneously by disabling the first dc/dc converter in the chain.

For power-down sequencing, an external controller dictates when the supplies are switched off by accessing the ENIN inputs individually.

Figure 23. Typical ADM1085 Application Circuit

Rev. 0 | Page 11 of 16

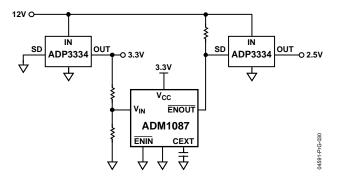

Figure 24. Typical ADM1086 Application Circuit

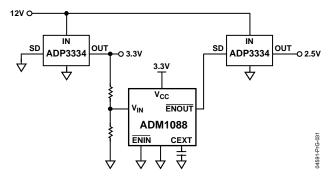

Figure 25. Typical ADM1087 Application Circuit Using ADP3334 Voltage Regulators

Figure 26. Typical ADM1088 Application Circuit Using ADP3334 Voltage Regulators

### **DUAL LOFO SEQUENCING**

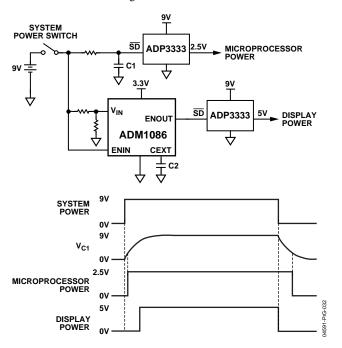

A power sequencing solution for a portable device, such as a PDA, is shown in Figure 27. This solution requires that the microprocessor's power supply turn on before the LCD display turns on, and that the LCD display power-down before the microprocessor powers down. In other words, the *last* power supply to turn *on* is the *first* one to turn *off* (LOFO).

An RC network connects the battery and the  $\overline{SD}$  input of the ADP3333 voltage regulator. This causes power-up and power-down transients to appear at the  $\overline{SD}$  input when the battery is connected and disconnected. The 3.3 V microprocessor supply turns on quickly on power-up and turns off slowly on power-down. This is due to two factors: Capacitor C1 charges up to 9 V on power-up and charges down from 9 V on power-down, and the  $\overline{SD}$  pin has logic-high and logic-low input levels of 2 V and 0.4 V.

For the display power sequencing, the ADM1085 is equipped with capacitor C2, which creates the delay between the microprocessor and display power turning on. When the system is powered down, the ADM1085 turns off the display power immediately, while the 3.3 V regulator waits for C1 to discharge to 0.4 V before switching off.

Figure 27. Dual LOFO Power-Supply Sequencing

#### SIMULTANEOUS ENABLING

The enable output can drive multiple enable or shutdown regulator inputs simultaneously.

Figure 28. Enabling a Pair of Regulators from a Single ADM1085

#### **POWER GOOD SIGNAL DELAYS**

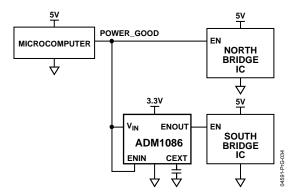

Sometimes sequencing is performed by asserting Power Good signals when the voltage regulators are already on, rather than sequencing the power supplies directly. In these scenarios, a simple sequencer IC can provide variable delays so that enabling separate circuit blocks can be staggered in time.

For example, in a notebook PC application, a dedicated microcomputer asserts a Power Good signal for North Bridge™ and South Bridge™ ICs. The ADM1086 delays the south bridge's signal, so that it is enabled after the north bridge.

Figure 29. Power Good Delay

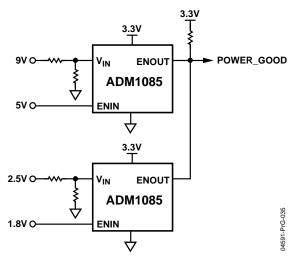

### **QUAD-SUPPLY POWER GOOD INDICATOR**

The enable output of the simple sequencers is equivalent to an AND function of  $V_{\rm IN}$  and ENIN. ENOUT is high only when the voltage at  $V_{\rm IN}$  is above the threshold and the enable input (ENIN) is high as well. Although ENIN is a digital input, it can tolerate voltages as high as 22 V and can detect if a supply is present. Therefore, a simple sequencer can monitor two supplies and assert what can be interpreted as a Power Good signal when both supplies are present. The outputs of two ADM1085s can be wire-ANDed together to make a quad-supply Power Good indicator.

Figure 30. Quad-Supply Power Good Indicator

### **SEQUENCING WITH FET SWITCHES**

The open-drain outputs of the ADM1085 and ADM1087 can drive external FET transistors, which can switch on power-supply rails. All that is needed is a pull-up resistor to a voltage source that is high enough to turn on the FET.

Figure 31. Sequencing with a FET Switch

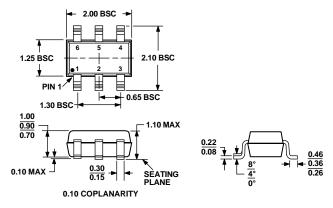

# **OUTLINE DIMENSIONS**

COMPLIANT TO JEDEC STANDARDS MO-203AB

Figure 32. 6-Lead Plastic Surface-Mount Package [SC70] (KS-6) Dimensions shown in millimeters

### **ORDERING GUIDE**

| Model            | Temperature Range | Quantity | Package Description                                           | Package Option | Branding |

|------------------|-------------------|----------|---------------------------------------------------------------|----------------|----------|

| ADM1085AKS-REEL7 | −40°C to +125°C   | 3k       | 6-Lead Thin Shrink Small Outline<br>Transistor Package (SC70) | KS-6           | MoV      |

| ADM1086AKS-REEL7 | −40°C to +125°C   | 3k       | 6-Lead Thin Shrink Small Outline<br>Transistor Package (SC70) | KS-6           | MoW      |

| ADM1087AKS-REEL7 | −40°C to +125°C   | 3k       | 6-Lead Thin Shrink Small Outline<br>Transistor Package (SC70) | KS-6           | MOX      |

| ADM1088AKS-REEL7 | −40°C to +125°C   | 3k       | 6-Lead Thin Shrink Small Outline<br>Transistor Package (SC70) | KS-6           | MOY      |

NOTES