# Increment/Decrement Dual Digital Potentiometer

AD5222

#### **FEATURES**

128-Position, 2-Channel Potentiometer Replacement 10 k $\Omega$ , 50 k $\Omega$ , 100 k $\Omega$ , 1 M $\Omega$  Very Low Power: 40  $\mu$ A Max  $\pm$ 2.7 V Dual Supply Operation or 2.7 V to 5.5 V Single Supply Operation Increment/Decrement Count Control

#### **APPLICATIONS**

Stereo Channel Audio Level Control

Mechanical Potentiometer Replacement

Remote Incremental Adjustment Applications

Instrumentation: Gain, Offset Adjustment

Programmable Voltage-to-Current Conversion

Line Impedance Matching

#### **GENERAL DESCRIPTION**

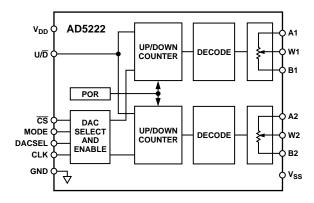

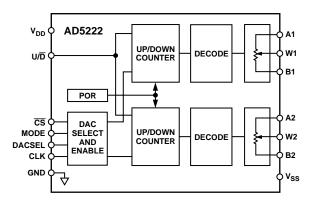

The AD5222 provides a dual channel, 128-position, digitally controlled variable-resistor (VR) device. This device performs the same electronic adjustment function as a potentiometer or variable resistor. These products were optimized for instrument and test equipment push-button applications. Choices between bandwidth or power dissipation are available as a result of the wide selection of end-to-end terminal resistance values.

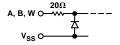

The AD5222 contains two fixed resistors with wiper contacts that tap the fixed resistor value at a point determined by a digitally controlled up/down counter. The resistance between the wiper and either end point of the fixed resistor provides a constant resistance step size that is equal to the end-to-end resistance divided by the number of positions (e.g.,  $R_{STEP} = 10 \text{ k}\Omega/128 = 78 \Omega$ ). The variable resistor offers a true adjustable value of resistance, between Terminal A and the wiper, or Terminal B and the wiper. The fixed A-to-B terminal resistance of  $10 \text{ k}\Omega$ ,  $50 \text{ k}\Omega$ ,  $100 \text{ k}\Omega$ , or  $1 \text{ M}\Omega$  has a nominal temperature coefficient of  $-35 \text{ ppm}/^{\circ}\text{C}$ .

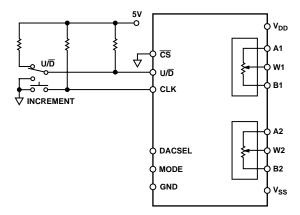

The chip select  $\overline{\text{CS}}$ , count CLK and U/ $\overline{\text{D}}$  direction control inputs set the variable resistor position. The MODE determines whether both VRs are incremented together or independently. With MODE at logic zero, both wipers are incremented UP or DOWN without changing the relative settings between the wipers. Also, the relative ratio between the wipers is preserved if either wiper reaches the end of the resistor array. In the independent MODE (Logic 1) only the VR determined by the DACSEL pin is changed. DACSEL (Logic 0) changes RDAC 1. These inputs, which control the internal up/down counter, can be easily generated with

#### FUNCTIONAL BLOCK DIAGRAM

mechanical or push-button switches (or other contact closure devices). This simple digital interface eliminates the need for microcontrollers in front panel interface designs.

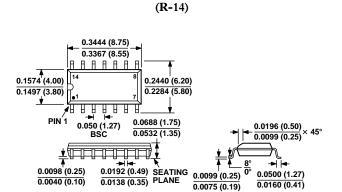

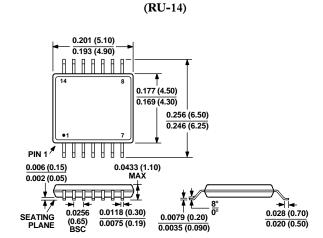

The AD5222 is available in the surface-mount (SO-14) package. For ultracompact solutions, selected models are available in the thin TSSOP-14 package. All parts are guaranteed to operate over the extended industrial temperature range of  $-40^{\circ}$ C to +85°C. For 3-wire, SPI-compatible interface applications, see the AD5203/AD5204/AD5206, AD7376, and AD8400/AD8402/AD8403 products.

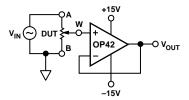

Figure 1. Typical Push-Button Control Application

#### REV.0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

## **AD5222—SPECIFICATIONS** $(V_{DD} = 3 \text{ V} \pm 10\% \text{ or 5 V} \pm 10\%, V_{SS} = 0 \text{ V}, V_A = +V_{DD}, V_B = 0 \text{ V}, -40^{\circ}\text{C} < T_A < +85^{\circ}\text{C}, unless otherwise noted.})$

| Parameter                                                                                                                                                                                                                                                                             | Symbol                                                                                                                                                                                       | Condition                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Min                                                | Typ <sup>1</sup>                            | Max                                    | Unit                                              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|---------------------------------------------|----------------------------------------|---------------------------------------------------|

| DC CHARACTERISTICS RHEOSTAT MODE (Specifications Apply to All VRs)                                                                                                                                                                                                                    |                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                    |                                             |                                        |                                                   |

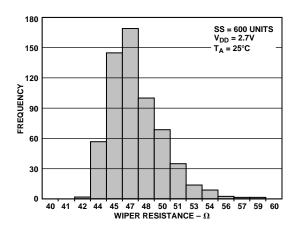

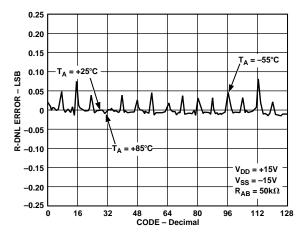

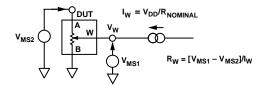

| Resistor Differential NL <sup>2</sup> Resistor Nonlinearity <sup>2</sup> Nominal Resistor Tolerance Resistance Temperature Coefficient Wiper Resistance <sup>3</sup> Nominal Resistance Match                                                                                         | $\begin{array}{c} \text{R-DNL} \\ \text{R-INL} \\ \Delta R \\ R_{AB}/\Delta T \\ R_{W} \\ \Delta R/R_{O} \end{array}$                                                                        | $\begin{array}{l} R_{WB}, V_A = NC \\ R_{WB}, V_A = NC \\ V_{AB} = V_{DD}, \text{Wiper} = \text{No Connect}, T_A = 25^{\circ}\text{C} \\ V_{AB} = V_{DD}, \text{Wiper} = \text{No Connect} \\ I_W = V_{DD}/R, V_{DD} = 3 \text{ V or 5 V} \\ \text{CH 1 to 2, } V_{AB} = V_{DD}, T_A = 25^{\circ}\text{C} \end{array}$                                                                                                                                         | -1<br>-1<br>-30                                    | ±1/4<br>±0.4<br>-35<br>45<br>0.2            |                                        | LSB<br>LSB<br>%<br>ppm/°C<br>Ω<br>%               |

| DC CHARACTERISTICS POTENTIOME Resolution Integral Nonlinearity <sup>4</sup> Differential Nonlinearity <sup>4</sup> Voltage Divider Temperature Coefficient Full-Scale Error Zero-Scale Error                                                                                          | TER DIVIDE N INL INL DNL $\Delta V_{w}/\Delta T$ $V_{wfse}$ $V_{wzse}$                                                                                                                       | R MODE (Specifications Apply to All VRs) $R_{AB} = 10 \text{ k}\Omega, 50 \text{ k}\Omega, \text{ or } 100 \text{ k}\Omega$ $R_{AB} = 1 \text{ M}\Omega$ $\text{Code} = 40_{\text{H}}$ $\text{Code} = 7F_{\text{H}}$ $\text{Code} = 00_{\text{H}}$                                                                                                                                                                                                             | 7<br>-1<br>-2<br>-1<br>-1<br>0                     | $\pm 1/4$ $\pm 1/2$ $\pm 1/4$ 20 $-0.5$ 0.5 | +2<br>+1                               | Bits<br>LSB<br>LSB<br>LSB<br>ppm/°C<br>LSB<br>LSB |

| RESISTOR TERMINALS Voltage Range <sup>5</sup> Capacitance <sup>6</sup> A, B Capacitance <sup>6</sup> W Common-Mode Leakage                                                                                                                                                            | $V_{A, B, W} \\ C_{A, B} \\ C_{W} \\ I_{CM}$                                                                                                                                                 | $f$ = 1 MHz, Measured to GND, Code = $40_H$<br>$f$ = 1 MHz, Measured to GND, Code = $40_H$<br>$V_A$ = $V_B$ = $V_W$                                                                                                                                                                                                                                                                                                                                            | V <sub>ss</sub>                                    | 45<br>60<br>1                               | $V_{\mathrm{DD}}$                      | V<br>pF<br>pF<br>nA                               |

| DIGITAL INPUTS AND OUTPUTS Input Logic High Input Logic Low Input Current Input Capacitance <sup>6</sup>                                                                                                                                                                              | $egin{array}{c} V_{IH} \ V_{IL} \ I_{IL} \ C_{IL} \end{array}$                                                                                                                               | $V_{\rm DD} = 5 \text{ V}/3 \text{ V}$<br>$V_{\rm DD} = 5 \text{ V}/3 \text{ V}$<br>$V_{\rm IN} = 0 \text{ V or } 5 \text{ V}$                                                                                                                                                                                                                                                                                                                                 | 2.4/2.1                                            | 5                                           | 0.8/0.6<br>±1                          | V<br>V<br>μΑ<br>pF                                |

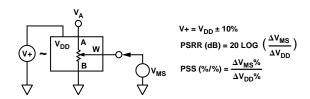

| POWER SUPPLIES Power Single-Supply Range Power Dual-Supply Range Positive Supply Current Negative Supply Current Power Dissipation <sup>7</sup> Power Supply Sensitivity                                                                                                              | $\begin{array}{c} V_{DD\;RANGE} \\ V_{DD/SS\;RANGE} \\ I_{DD} \\ I_{SS} \\ P_{DISS} \\ PSS \end{array}$                                                                                      | $\begin{split} V_{SS} &= 0 \text{ V} \\ V_{IH} &= 5 \text{ V or } V_{IL} = 0 \text{ V} \\ V_{SS} &= -2.5 \text{ V}, V_{DD} = +2.7 \text{ V} \\ V_{IH} &= 5 \text{ V or } V_{IL} = 0 \text{ V}, V_{DD} = 5 \text{ V} \end{split}$                                                                                                                                                                                                                               | 2.7<br>±2.3                                        | 15<br>15<br>150<br>0.002                    | 5.5<br>±2.7<br>40<br>40<br>400<br>0.05 | V<br>V<br>μΑ<br>μΑ<br>μW<br>%/%                   |

| DYNAMIC CHARACTERISTICS <sup>6, 8, 9</sup> Bandwidth –3 dB  Total Harmonic Distortion V <sub>W</sub> Settling Time Resistor Noise Voltage                                                                                                                                             | BW_10K<br>BW_50K<br>BW_100K<br>BW_1M<br>THD <sub>W</sub><br>t <sub>S</sub>                                                                                                                   | $\begin{split} R_{AB} &= 10 \text{ k}\Omega, \text{ Code} = 40_{H} \\ R_{AB} &= 50 \text{ k}\Omega, \text{ Code} = 40_{H} \\ R_{AB} &= 100 \text{ k}\Omega, \text{ Code} = 40_{H} \\ R_{AB} &= 500 \text{ k}\Omega, \text{ Code} = 40_{H} \\ V_{A} &= 1 \text{ V rms} + 2 \text{ V dc}, V_{B} = 2 \text{ V dc}, f = 1 \text{ kHz} \\ R_{AB} &= 10 \text{ k}\Omega, \pm 1 \text{ LSB Error Band} \\ R_{WB} &= 5 \text{ k}\Omega, f = 1 \text{ kHz} \end{split}$ |                                                    | 1000<br>180<br>78<br>7<br>0.005<br>2<br>14  |                                        | kHz<br>kHz<br>kHz<br>kHz<br>%<br>µs<br>nV√Hz      |

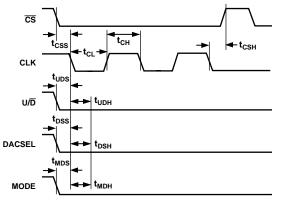

| INTERFACE TIMING CHARACTERIST Input Clock Pulsewidth CS to CLK Setup Time CS Rise to CLK Hold Time U/D to Clock Fall Setup Time U/D to Clock Fall Hold Time DACSEL to Clock Fall Setup Time DACSEL to Clock Fall Hold Time MODE to Clock Fall Setup Time MODE to Clock Fall Hold Time | tCS (Applies to t <sub>CH</sub> , t <sub>CL</sub> ) t <sub>CS</sub> s t <sub>CSH</sub> t <sub>UDS</sub> t <sub>UDH</sub> t <sub>DSS</sub> t <sub>DSH</sub> t <sub>MDS</sub> t <sub>MDH</sub> | o All Parts) <sup>6, 10</sup><br>Clock Level High or Low                                                                                                                                                                                                                                                                                                                                                                                                       | 30<br>20<br>20<br>10<br>30<br>20<br>30<br>20<br>40 |                                             |                                        | ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns            |

#### NOTES

$<sup>^{</sup>l}\text{Typicals}$  represent average readings at 25  $^{\circ}\text{C},\,V_{DD}$  = 5 V.

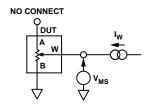

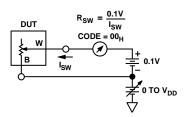

<sup>&</sup>lt;sup>2</sup>Resistor position nonlinearity error R-INL is the deviation from an ideal value measured between the maximum resistance and the minimum resistance wiper positions. R-DNL measures the relative step change from ideal between successive tap positions. Parts are guaranteed monotonic. See Figure 22 test circuit.

$<sup>^3\</sup>mbox{Wiper}$  resistance is not measured on the  $R_{AB}$  = 1  $M\Omega$  models.

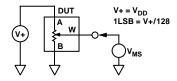

$<sup>^4</sup>$ INL and DNL are measured at  $V_W$  with the RDAC configured as a potentiometer divider similar to a voltage output D/A converter.  $V_A = V_{DD}$  and  $V_B = 0$  V. DNL specification limits of ±1 LSB maximum are guaranteed monotonic operating conditions. See Figure 21 test circuit.

<sup>&</sup>lt;sup>5</sup>Resistor Terminals A, B, W have no limitations on polarity with respect to each other.

<sup>&</sup>lt;sup>6</sup>Guaranteed by design and not subject to production test.

$<sup>^{7}</sup>P_{DISS}$  is calculated from ( $I_{DD} \times V_{DD}$ ). CMOS logic level inputs result in minimum power dissipation.  $^{8}Bandwidth$ , noise and settling time are dependent on the terminal resistance value chosen. The lowest R value results in the fastest settling time and highest bandwidth. The highest R value results in the minimum overall power consumption.

$<sup>^{9}</sup>$ All dynamic characteristics use  $V_{\rm DD}$  = 5 V.

The Grammer characteristics are measured values. All input control voltages are specified with  $t_R = t_F = 2.5$  ns (10% to 90% of +3 V) and timed from a voltage level of 1.5 V. Switching characteristics are measured using both  $V_{DD} = 5$  V or  $V_{DD} = 3$  V.

#### ABSOLUTE MAXIMUM RATINGS

| (1 <sub>A</sub> = 25°C, unless otherwise noted)             |

|-------------------------------------------------------------|

| V <sub>DD</sub> to GND0.3 V, +7 V                           |

| $V_{SS}$ to GND                                             |

| $V_{DD}$ to $V_{SS}$                                        |

| $V_A$ , $V_B$ , $V_W$ to GND 0 V, $V_{DD}$                  |

| $A_X - B_X$ , $A_X - W_X$ , $B_X - W_X$ $\pm 20 \text{ mA}$ |

| Digital Input Voltage to GND 0 V, V <sub>DD</sub> + 0.3 V   |

| Operating Temperature Range40°C to +85°C                    |

| Maximum Junction Temperature (T <sub>I</sub> max) 150°C     |

| Storage Temperature65°C to +150°C                           |

| Lead Temperature (Soldering, 10 sec) 300°C                  |

| Package Power Dissipation $(T_I max - T_A)/\theta_{IA}$     |

| Thermal Resistance $\theta_{JA}$ ,                          |

| SOIC (SO-14)                                                |

| T000D 14                                                    |

Figure 2. Detail Timing Diagram

#### Truth Table

| CS | CLK      | U/D | Operation                         |

|----|----------|-----|-----------------------------------|

| L  | 1        | Н   | Wiper Increment Toward Terminal A |

| L  | <b>↓</b> | L   | Wiper Decrement Toward Terminal B |

| Η  | X        | X   | Wiper Position Fixed              |

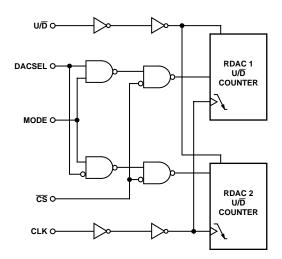

Common Mode (MODE = 0) moves both wipers together either UP or DOWN the resistor array without changing the relative distance between the wipers. Also, the distance between both wipers is preserved if either reaches the end of the array. Independent Mode (MODE = 1) allows user to control each RDAC individually: DACSEL = 0 sets RDAC1; DACSEL = 1: sets RDAC2.

#### **ORDERING GUIDE**

| Model        | Kilo<br>Ohms | Temperature | Package<br>Description | Package<br>Option |

|--------------|--------------|-------------|------------------------|-------------------|

| AD5222BR10   | 10           | -40°C/+85°C | SO-14                  | R-14              |

| AD5222BRU10  | 10           | -40°C/+85°C | TSSOP-14               | RU-14             |

| AD5222BR50   | 50           | -40°C/+85°C | SO-14                  | R-14              |

| AD5222BRU50  | 50           | -40°C/+85°C | TSSOP-14               | RU-14             |

| AD5222BR100  | 100          | -40°C/+85°C | SO-14                  | R-14              |

| AD5222BRU100 | 100          | -40°C/+85°C | TSSOP-14               | RU-14             |

| AD5222BR1M   | 1,000        | -40°C/+85°C | SO-14                  | R-14              |

| AD5222BRU1M  | 1,000        | -40°C/+85°C | TSSOP-14               | RU-14             |

The AD5222 die size is 56 mil  $\times$  60 mil, 3360 sq. mil; 1.4224 mm  $\times$  1.524 mm, 2.1677 sq. mm. Contains 1503 transistors. Patent Number 5495245 applies.

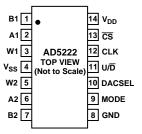

#### PIN FUNCTION DESCRIPTIONS

| Pin | Name              | Description                                                                                                                 |

|-----|-------------------|-----------------------------------------------------------------------------------------------------------------------------|

| 1   | B1                | B Terminal RDAC #1.                                                                                                         |

| 2   | A1                | A Terminal RDAC #1.                                                                                                         |

| 3   | W1                | Wiper RDAC #1, DACSEL = 0.                                                                                                  |

| 4   | $V_{SS}$          | Negative Power Supply. Specified for operation at both 0 V or $-2.7$ V (Sum of $ V_{DD}  +  V_{SS} $ < 5.5 V).              |

| 5   | W2                | Wiper RDAC #2, DACSEL = 1.                                                                                                  |

| 6   | A2                | A Terminal RDAC #2.                                                                                                         |

| 7   | B2                | B Terminal RDAC #2.                                                                                                         |

| 8   | GND               | Ground.                                                                                                                     |

| 9   | MODE              | Common MODE = 0, Independent MODE = 1.                                                                                      |

| 10  | DACSEL            | DAC Select determines which wiper is incremented in the Independent MODE = 1. DACSEL = 0 sets RDAC1, DACSEL = 1 sets RDAC2. |

| 11  | $U/\overline{D}$  | UP/DOWN Direction Control.                                                                                                  |

| 12  | CLK               | Serial Clock Input, Negative Edge Triggered.                                                                                |

| 13  | CS                | Chip Select Input, Active Low. When $\overline{CS}$ is high, the UP/DOWN counter is disabled.                               |

| 14  | $V_{\mathrm{DD}}$ | Positive Power Supply. Specified for operation at both +3 V or +5 V. (Sum of $ V_{DD} $ + $ V_{SS} $ < 5.5 V).              |

#### PIN CONFIGURATION

#### CAUTION\_

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD5222 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

REV. 0 \_3\_

## **AD5222—Typical Performance Characteristics**

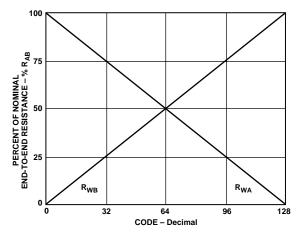

Figure 3. Wiper-To-End Terminal Resistance vs. Code

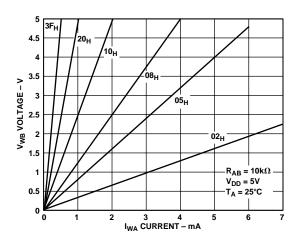

Figure 4. Resistance Linearity vs. Conduction Current

Figure 5. Wiper Contact Resistance

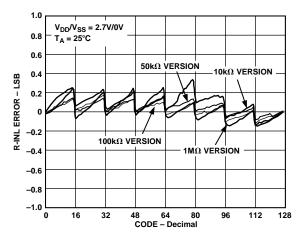

Figure 6. R-DNL Relative Resistance Step Position Change vs. Code

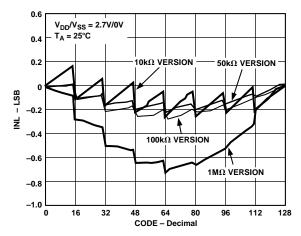

Figure 7. R-INL Resistance Nonlinearity Error vs. Code

Figure 8. Potentiometer Divider INL Error vs. Code

-4- REV. 0

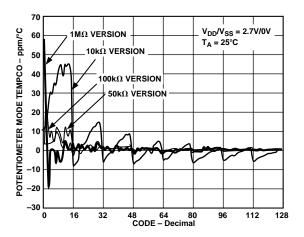

Figure 9.  $\Delta V_{WB}/\Delta T$  Potentiometer Mode Tempco

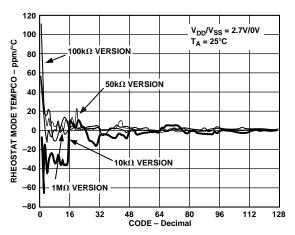

Figure 10.  $\Delta R_{WB}/\Delta T$  Rheostat Mode Tempco

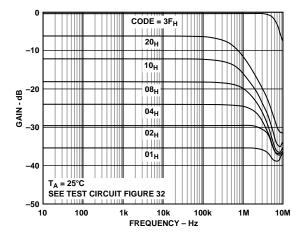

Figure 11. 10  $k\Omega$  Gain vs. Frequency vs. Code

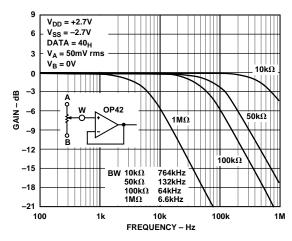

Figure 12. Gain vs. Frequency vs. R<sub>AB</sub>

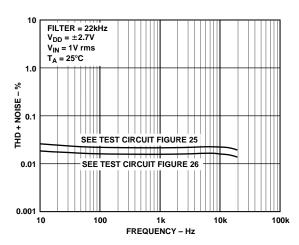

Figure 13. Total Harmonic Distortion Plus Noise vs. Frequency

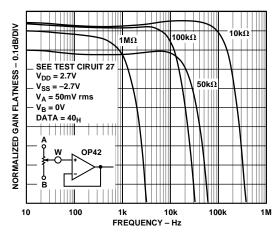

Figure 14. Normalized Gain Flatness vs. Frequency

REV. 0 \_5\_

### **AD5222**

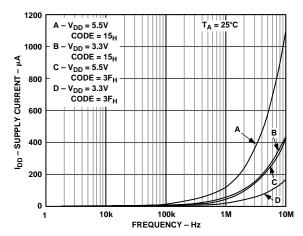

Figure 15. I<sub>DD</sub>, I<sub>SS</sub> Supply Current vs. Clock Frequency

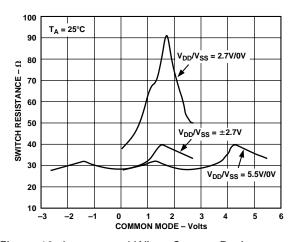

Figure 16. Incremental Wiper Contact Resistance vs.  $V_{\rm DD}/V_{\rm SS}$

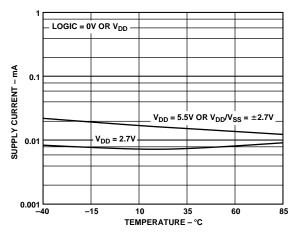

Figure 17. Supply Current vs. Temperature

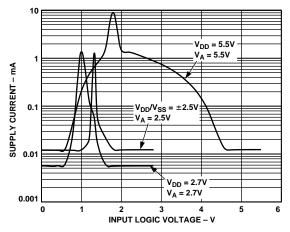

Figure 18. Supply Current vs. Input Logic Voltage

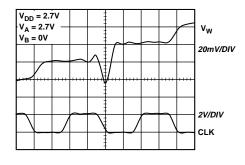

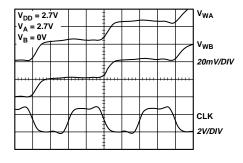

Figure 19. Midscale Transition  $3F_H$  to  $40_H$

Figure 20. Stereo Step Transition, Mode = 0

-6- REV. 0

## Parametric Test Circuits—AD5222

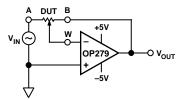

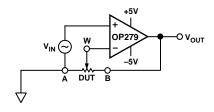

Figure 21. Potentiometer Divider Nonlinearity Error Test Circuit (INL, DNL)

Figure 22. Resistor Position Nonlinearity Error (Rheostat Operation; R-INL, R-DNL)

Figure 23. Wiper Resistance Test Circuit

Figure 24. Power Supply Sensitivity Test Circuit (PSS, PSRR)

Figure 25. Inverting Programmable Gain Test Circuit

Figure 26. Noninverting Programmable Gain Test Circuit

Figure 27. Gain vs. Frequency Test Circuit

Figure 28. Incremental ON Resistance Test Circuit

REV. 0 -7-

#### AD5222

#### **OPERATION**

The AD5222 provides a 128-position, digitally-controlled, variable resistor (VR) device. Changing the VR settings is accomplished by pulsing the CLK pin while  $\overline{CS}$  is active low. The  $U/\overline{D}$  (UP/DOWN) control input pin controls the direction of the increment. When the wiper hits the end of the resistor (Terminal A or B) additional CLK pulses no longer change the wiper setting. The wiper position is immediately decoded by the wiper decode logic changing the wiper resistance. Appropriate debounce circuitry is required when push-button switches are used to control the count sequence and direction of count. The exact timing requirements are shown in Figure 2. The AD5222 powers ON in a centered wiper position, exhibiting nearly equal resistances of  $R_{WA}$  and  $R_{WB}$ .

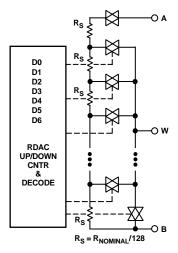

Figure 29. Block Diagram

#### DIGITAL INTERFACING OPERATION

The AD5222 contains a push-button controllable interface. The active inputs are clock (CLK),  $\overline{CS}$  and up/down (U/ $\overline{D}$ ). While the MODE, and DACSEL pins control common updates or individual updates. The negative-edge sensitive CLK input requires clean transitions to avoid clocking multiple pulses into the internal UP/DOWN counter register, Figure 30. Standard logic families work well. If mechanical switches are used for product evaluation a flip-flop or other suitable means should debounce them. When  $\overline{CS}$  is taken active low, the clock begins to increment or decrement the internal up/down counter, dependent upon the state of the  $U/\overline{D}$  control pin. The UP/DOWN counter value (D) starts at  $40_{\rm H}$  at system power ON. Each new CLK pulse will increment the value of the internal counter by 1 LSB until the full-scale value of 7F<sub>H</sub> is reached, as long as the  $U/\overline{D}$  pin is logic high. If the  $U/\overline{D}$  pin is taken to logic low, the counter will count down, stopping at code 00<sub>H</sub> (zero-scale). Additional clock pulses on the CLK pin are ignored when the wiper is at either the 00<sub>H</sub> position or the 7F<sub>H</sub> position. The detailed digital logic interface circuitry is shown in Figure 30.

Figure 30. Detailed Digital Logic Interface Circuit All digital inputs  $(\overline{CS}, U/\overline{D}, CLK, MODE, DACSEL)$  are protected with a series input resistor and parallel Zener ESD structure shown in Figure 31. All potentiometer terminal pins (A, B, W) are protected from ESD as shown in Figure 32.

Figure 31. Equivalent ESD Protection Digital Pins

Figure 32. Equivalent ESD Protection Analog Pins

Figure 33. AD5222 Equivalent RDAC Circuit

-8- REV. 0

**AD5222**

## PROGRAMMING THE VARIABLE RESISTOR Rheostat Operation

The nominal resistance of the RDAC between Terminals A and B are available with values of 10 k $\Omega$ , 50 k $\Omega$ , 100 k $\Omega$ , and 1 M $\Omega$ The final three characters of the part number determine the nominal resistance value, e.g.,  $10 \text{ k}\Omega = 10$ ;  $50 \text{ k}\Omega = 50$ ;  $100 \text{ k}\Omega$ = 100; 1 M $\Omega$  = 1M. The nominal resistance (R<sub>AB</sub>) of the VR has 128 contact points accessed by the wiper terminal, plus the B terminal contact. At power ON, the resistance from the wiper to either end Terminal A or B is approximately equal. Pulsing the CLK pin will increase the resistance from the wiper W to Terminal B by one unit of R<sub>S</sub> resistance, see Figure 33. The resistance R<sub>WB</sub> is determined by the number of pulses applied to the clock pin. Each segment of the internal resistor string has a nominal resistance value of  $R_S = R_{AB}/128$ , which becomes 78  $\Omega$ in the case of the  $10 \text{ k}\Omega$  AD5222BR10 product. Care should be taken to limit the current flow between W and B in the direct contact state ( $R_{WB}$  code = 0) to a maximum value of 20 mA to avoid degradation or possible destruction of the internal switch contact.

Like the mechanical potentiometer the RDAC replaces, it is totally symmetrical (see Figure 3). The resistance between the wiper W and Terminal A also produces a digitally controlled resistance  $R_{WA}$ . When these terminals are used the B-terminal should be tied to the wiper.

The typical part-to-part distribution of  $R_{BA}$  is process-lot-dependent having a  $\pm 30\%$  variation. The change in  $R_{BA}$  with temperature has a -35 ppm/°C temperature coefficient.

The  $R_{BA}$  temperature coefficient increases as the wiper is programmed near the B-terminal due to the larger percentage contribution of the wiper contact switch resistance, which has a 0.5%/°C temperature coefficient. Figures 9 and 10 show the effect of the wiper contact resistance as a function of code setting.

## PROGRAMMING THE POTENTIOMETER DIVIDER Voltage Output Operation

The digital potentiometer easily generates an output voltage proportional to the input voltage applied to a given terminal. For example connecting A-terminal to 5 V and B-terminal to ground produces an output voltage at the wiper which can be any value starting at zero volts up to 1 LSB less than 5 V. Each LSB of voltage is equal to the voltage applied across Terminals AB divided by the 128-position resolution of the potentiometer divider. The general equation defining the output voltage with respect to ground for any given input voltage applied to Terminals AB is:

$$V_W(D) = D/128 \times V_{AB} + V_B \tag{1}$$

D represents the current contents of the internal up/down counter.

Operation of the digital potentiometer in the divider mode results in more accurate operation over temperature. Here the output voltage is dependent on the ratio of the internal resistors not the absolute value, therefore, the drift improves to 20 ppm/°C.

REV. 0 \_9\_

#### **OUTLINE DIMENSIONS**

Dimensions shown in inches and (mm).

14-Lead Narrow Body SOIC

14-Lead TSSOP