# ANALOG DEVICES

# 2 Pair/1 Pair ETSI Compatible HDSL Analog Front End

# Preliminary Technical Data

# AD5011

#### FEATURES

Integrated front End for Single Pair or Two Pair HDSL Systems Meets ETSI Specifications

Supports 1168 kbps and 2.32 Mbps

Programmable Filtering Supports Adaptive HDSL

Transmit and Receive Signal Path Functions

- Receive Hybrid Amplifier, PGA, ADC and Adaptable Filter

- Transmit DAC, Adaptable Filter and Differential Outputs

Normal Loopback

Serial Interface to Digital Transceivers Single 3 V Power Supply

#### GENERAL DESCRIPTION

The AD5011 is an analog front end for two pair or single pair HDSL applications that use 1168 kbps or 2.32 Mbps data rates. The device integrates all the transmit and receive functional blocks. A standard serial interface is used to communicate with the DAC and ADC. The filters in both the transmit and receive paths are programmable which allows adaptive HDSL to be performed also. The part is available in a 48-pin LQFP package and is specified for a temperature range of -40 °C to +85 °C.

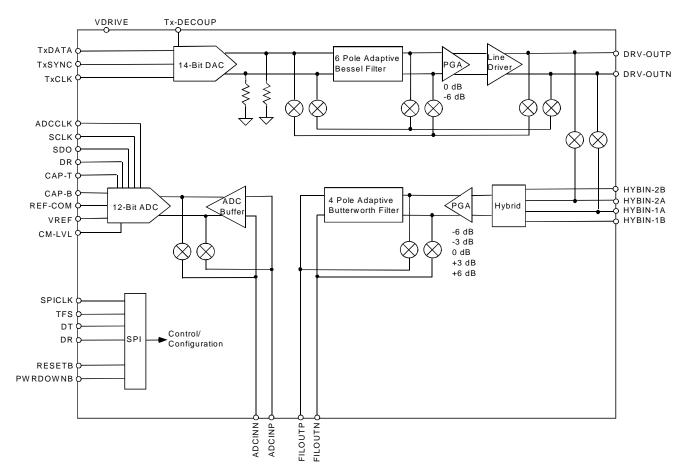

#### FUNCTIONAL BLOCK DIAGRAM

#### **REV** PrA

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel:

781/329-4700

Fax:

781/326-8703

World Wide Web Site: hppt://www.analog.com

| Parameter                                                                                                                                 | Min      | AD5011B<br>Typ Max                                                                                  | Units                                        | Test Conditions/Comments                                                             |

|-------------------------------------------------------------------------------------------------------------------------------------------|----------|-----------------------------------------------------------------------------------------------------|----------------------------------------------|--------------------------------------------------------------------------------------|

| TRANSMITCHANNEL<br>Signal to Noise <sup>2</sup><br>Total Harmonic Distortion <sup>2</sup>                                                 | 68<br>66 | 71<br>71                                                                                            | dB<br>dB                                     | F <sub>OUT</sub> = 73 kHz<br>F <sub>OUT</sub> = 73 kHz                               |

| TRANSMIT DAC<br>Resolution<br>Clock Frequency<br>Coding<br>Output Update Rate <sup>3</sup><br>Output Voltage                              |          | 14<br>18.688<br>2s Complement<br>1168<br>1                                                          | Bits<br>MHz<br>kHz<br>Vpp Diff               |                                                                                      |

| TRANSMIT FILTER<br>Cutoff Frequency <sup>4</sup><br>Corner Frequency Accuracy<br>Adjacent Corner Step                                     |          | $\begin{array}{c} 49 - 120.8 \\ 108 - 265 \\ 235 - 580 \\ \pm 5 \\ \pm 40 \end{array}$              | kHz<br>kHz<br>kHz<br>%<br>% nom              | Bottom Range (8 kHz steps)<br>Mid Range (18 kHz steps)<br>Top Range (40.5 kHz steps) |

| LINE DRIVER <sup>5</sup><br>VCM<br>Common Mode Voltage Error<br>Output Power<br>Output Voltage<br>Channel Gain Accuracy                   |          | $ \begin{array}{c} 1.5 \\ \pm 100 \\ 13.5 \\ 4 \\ 2 \\ \pm 1 \end{array} $                          | V<br>mV<br>dBm<br>Vpp Diff<br>Vpp Diff<br>dB | Tx-GAIN = 0<br>Tx-GAIN = 1                                                           |

| RECEIVE CHANNEL<br>Signal to (Noise + Distortion) <sup>6</sup><br>Fotal Harmonic Distortion                                               | 66<br>68 | 68<br>71                                                                                            | dB<br>dB                                     | $F_{IN} = 73 \text{ kHz}$<br>$F_{IN} = 73 \text{ kHz}$                               |

| HYBRID INTERFACE<br>Input Voltage Range<br>Common Mode Input Voltage<br>Input Impedance<br>Input Offset Voltage                           |          | 5<br>1.5<br>10<br>80                                                                                | Vpp Diff<br>V<br>k w<br>mV                   | PGA = 0 dB<br>PGA = 0 dB                                                             |

| PROGRAMMABLE GAIN AMPLIFIER <sup>7</sup><br>Overall Gain Accuracy<br>Gain Step<br>Gain Step Accuracy                                      |          | $^{\pm 1}_{3}_{\pm 0.25}$                                                                           | dB<br>dB<br>dB                               | For all Gain Settings from -6 dB to +9 dB                                            |

| RECEIVE FILTER<br>Cutoff Frequency <sup>4</sup><br>Accuracy<br>Adjacent Corner Step<br>Output Load Capacitance<br>Output Load Resistance  |          | $\begin{array}{c} 49 - 120.8 \\ 108 - 265 \\ 235 - 580 \\ \pm 5 \\ \pm 40 \\ 20 \\ TBD \end{array}$ | kHz<br>kHz<br>kHz<br>%<br>% nom<br>pF<br>W   | Bottom Range (8 kHz steps)<br>Mid Range (18 kHz steps)<br>Top Range (40.5 kHz steps) |

| RECEIVEADC<br>Resolution<br>Coding<br>Sample Rate                                                                                         |          | 12<br>2s Complement<br>2.32                                                                         | Bits<br>MHz                                  |                                                                                      |

| LOGIC INPUTS<br>Input Logic High, $V_{INH}^{8}$<br>Input Logic Low, $V_{INL}$<br>$I_{IN}$ , Input Current<br>$C_{IN}$ , Input Capacitance | 2        | $\begin{array}{ccc} 3 & & & \\ 0 & & 0.2 & \\ & \pm 10 & \\ & 10 & \end{array}$                     | V<br>V<br>mA<br>pF                           | $V_{IN} = 0 V$ to DVDD                                                               |

| Parameter                                       | AD734<br>Min | юВ<br>Тур | Max  | Units | Test Conditions/Comments   |

|-------------------------------------------------|--------------|-----------|------|-------|----------------------------|

|                                                 | 191111       | тур       | WIAX |       |                            |

| LOGICOUTPUTS                                    |              |           |      |       |                            |

| Output Logic High, V <sub>OH</sub> <sup>9</sup> | VDD -        | 0.3       |      | V     | $I_{OUT} = 200 \text{ mA}$ |

| Output Logic Low, V <sub>OL</sub>               |              |           | 0.3  | V     | $I_{OUT} = 200 \text{ mA}$ |

| POWERSUPPLIES                                   |              |           |      |       |                            |

| AVDD, DVDD                                      | 3.15         | 3.3       | 3.45 | V     |                            |

| IDD                                             | 0.10         | 0.0       | 0.10 | '     |                            |

| Normal Mode (excluding Driver)                  |              | 32        |      | mA    |                            |

| Line Driver                                     |              | 75        |      | mA    | 33w Differential Load      |

<sup>1</sup>Operating temperature range is as follows: B Version: -40°C to +85°C.

<sup>2</sup>The complete transmit path spectrum and pulse shape comply with ETSI requirements. SNR and THD are measured within a 547 kHz bandwidth. Noise and Spurious tones beyong 540 kHz are therefore excluded.

<sup>3</sup>The transmit DAC maximum update rate is half the maximum output data rate i.e. 1168 kHz. The maximum transmit clock is 16 x 1168 = 18.688 MHz.

<sup>4</sup>There are three ranges (bottom range, mid range, top range), each range being divided into eight steps. The transmit filter corner frequency can be set independently from the receive filter corner frequency. the filter tuning circuit requires a continuous 16.384 MHz clock applied to the Fclk pin.

<sup>5</sup>Transformer turns ratio = 1:2:3 at 50 kHz when loaded by ETSI (RTR/TM3036) HDSL test loops.

<sup>6</sup>With 547 kHz filter snd 0 dB PGA gain selected. <sup>7</sup>The PGA gain is set by setting the PGA-GC bits in the control register.

<sup>8</sup>The input switching threshold voltage is approximately 1.2 V to allow interfacing to 2.5 V and 3.3 V logic.

$^9 \mathrm{The}$  output level is determined by the voltage on the logic supply pin  $V_{\mathrm{DRIVE}}.$

Specifications subject to change without notice.

# AD5011

# TIMING CHARACTERISTICS ( $V_{DD} = +2.7 V$ to +5.5 V; AGND = DGND = 0 V, unless otherwise noted)

|                 | Limit at<br>T <sub>MIN</sub> to T <sub>MAX</sub> |        |                                                                 |

|-----------------|--------------------------------------------------|--------|-----------------------------------------------------------------|

| Parameter       | (B Version)                                      | Units  | Test Conditions/Comments                                        |

| ADCCLK          | <= 1160kHz                                       |        |                                                                 |

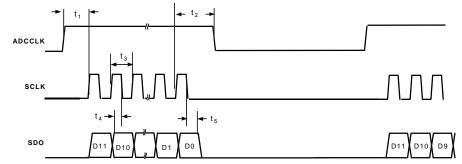

| t <sub>1</sub>  | $1.5*t_3$                                        | ns min | ADCCLK Rising Edge to SCLK Rising Edge Delay                    |

|                 | 2*t <sub>3</sub>                                 | ns typ |                                                                 |

| t <sub>2</sub>  | $2.5*t_3$                                        | ns min | SCLK Rising Edge to ADCCLK Falling Edge Delay                   |

|                 | 3*t <sub>3</sub>                                 | ns typ |                                                                 |

| t <sub>3</sub>  | 26.939                                           | ns min | SCLK Period (1/32*ADCCLK Period)                                |

| t <sub>4</sub>  | 5                                                | ns min | Data Setup Time Before SCLK Falling Edge                        |

| t <sub>5</sub>  | 10                                               | ns min | Data Hold Time After SCLK Falling Edge                          |

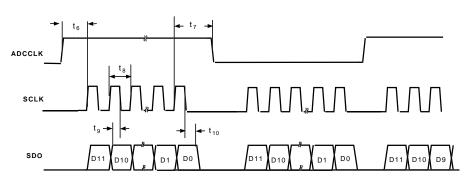

| 1160 kHz        | < ADCCLK <= 2320 kHz                             |        |                                                                 |

| t <sub>6</sub>  | 20                                               | ns min | ADCCLK Rising Edge to SCLK Rising Edge Delay                    |

|                 | 1*t <sub>8</sub>                                 | ns typ |                                                                 |

| t <sub>7</sub>  | 1.5*t8                                           | ns min | SCLK Rising Edge to ADCCLK Falling Edge Delay                   |

|                 | 2*t <sub>8</sub>                                 | ns typ |                                                                 |

| t <sub>8</sub>  | 26.939                                           | ns min | SCLK Period (1/16*ADCCLK Period)                                |

| t <sub>9</sub>  | 5                                                | ns min | Data Setup Time Before SCLK Falling Edge                        |

| t <sub>10</sub> | 10                                               | ns min | Data Hold Time After SCLK Falling Edge                          |

| TRANSMI         | T DAC                                            |        |                                                                 |

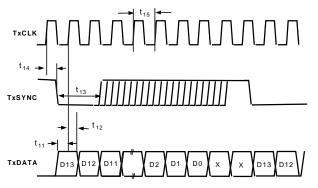

| t <sub>11</sub> | 53.5                                             | ns min | TxCLK Period (1/18.688 MHz)                                     |

| t <sub>12</sub> | 12                                               | ns min | Data Setup Time Before TxCLK Rising Edge                        |

| t <sub>13</sub> | 10                                               | ns min | Data Hold Time After TxCLK Rising Edge                          |

| t <sub>14</sub> | t <sub>11</sub>                                  | ns min | TxSYNC Low Time                                                 |

| t <sub>15</sub> | 3                                                | ns min | TxCLK Rising Edge to TxSYNC Falling Edge Delay                  |

|                 |                                                  | t11/2  | ns max                                                          |

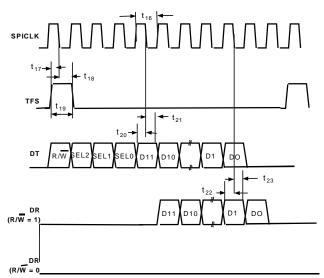

| CONTRO          | L REGISTER                                       |        |                                                                 |

| t <sub>16</sub> | 50                                               | ns min | SPICLK Period                                                   |

|                 | 76                                               | ns typ |                                                                 |

| t <sub>17</sub> | 15                                               | ns min | TFS Setup Time Before SPICLK Falling Edge                       |

|                 | t <sub>16</sub> - 15                             | ns max |                                                                 |

| t <sub>18</sub> | 15                                               | ns min | TFS Hold Time After SPICLK Falling Edge                         |

|                 | t <sub>16</sub> - 15                             | ns max |                                                                 |

| t <sub>19</sub> | t <sub>16</sub>                                  | ns typ | TFS High Time                                                   |

| t <sub>20</sub> | 7                                                | ns min | DT Setup Time Before SPICLK Falling Edge                        |

| t <sub>21</sub> | 10                                               | ns min | DT Hold Time After SPICLK Falling Edge                          |

| t <sub>22</sub> | 7                                                | ns min | DR Setup Time Before SPICLK Falling Edge $(R/\overline{W} = 1)$ |

| t <sub>23</sub> | 10                                               | ns min | DR Hold Time After SPICLK Falling Edge $(R/\overline{W} = 1)$   |

Guaranteed by design but not production tested.

SCLK activity and serial output data activity does not coincide with the sesitive ADCCLK clock edges

Figure 1. ADC Timing (ADCCLK <= 1160 kHz)

## AD5011

SCLK activity and serial output data activity does not coincide with the sesitive ADCCLK clock edges

Figure 2. ADC Timing (1160 kHz < ADCCLK <= 2320 kHz)

The rising edge of TxSYNC can occur anywhere as long at the TxSYNC low time exceeds one TxCLK period. The TxSYNC falling edge must occur after the TxCLK rising edge which captures the LSB of the previous word. This ensures correct loading into the DAC. The first 14 bits are loaded into the DAC, the 2 LSBs being don't cares.

Figure 3. DAC Timing

If  $R/\overline{W} = 1$ , the selected register's contents will be output on DR. If  $R/\overline{W} = 0$ , no data will be output on DR. The SEL bits identify which of the four register banks is being written to. The 12 LSBs contain the word. When the AD5011 is reset using RESETB, the registers are reset to zero.

Figure 4. Control Interface

# AD5011

## PINDESCRIPTION

| Mnemonic            | Function                                                                                                                                                                                                   |  |  |  |  |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| POWER SUPPLY        |                                                                                                                                                                                                            |  |  |  |  |

| VDRIVE              | Digital output drive level.                                                                                                                                                                                |  |  |  |  |

| AGND                | Analog power supply.                                                                                                                                                                                       |  |  |  |  |

| AGND                | Analog Ground.                                                                                                                                                                                             |  |  |  |  |

| DVDD                | Positive power supply for the digital section.                                                                                                                                                             |  |  |  |  |

| DGND                | Digital Ground.                                                                                                                                                                                            |  |  |  |  |

| TRANSMIT CHA        | NNEL                                                                                                                                                                                                       |  |  |  |  |

| TxDATA              | Transmit data input.                                                                                                                                                                                       |  |  |  |  |

| TxSYNC              | Transmit data frame synchronization, logic input.                                                                                                                                                          |  |  |  |  |

| TxCLK               | Transmit serial clock, logic input.                                                                                                                                                                        |  |  |  |  |

| TxDECOUP            | Transmit DAC reference decoupling pin. The reference which supplies the DAC needs some external decoupling.                                                                                                |  |  |  |  |

| DRV-OUTP            | Differential line driver positive output.                                                                                                                                                                  |  |  |  |  |

| DRV-OUTN            | Differential line driver negative output.                                                                                                                                                                  |  |  |  |  |

| EXTERNAL INTE       | ERFACE                                                                                                                                                                                                     |  |  |  |  |

| SPICLK              | Serial interface clock, logic input.                                                                                                                                                                       |  |  |  |  |

| TFS                 | Serial Interface frame synchronisation, logic input.                                                                                                                                                       |  |  |  |  |

| DT                  | Serial interface data input.                                                                                                                                                                               |  |  |  |  |

| DR                  | Serial interface data output.                                                                                                                                                                              |  |  |  |  |

| RESETB              | Master Reset. This is an active low logic input.                                                                                                                                                           |  |  |  |  |

| PWRDWNB             | Master powerdown. When PWRDWNB is taken low, the complete AD5011 device is placed in a sleep mode.                                                                                                         |  |  |  |  |

| FCLK                | Filter tuning clock. The clock for the filter tuning circuit in both the transmit and receive paths is supplied to FCLK. A 16.384 MHz should be connected to this pin to obtain the specified frequencies. |  |  |  |  |

| TEST                | Test Mode. When TEST is tied to DVDD, the AD5011 is placed in a test mode. For normal operation, this pin should be tied to DGND.                                                                          |  |  |  |  |

| <b>RECEIVE CHAN</b> | NEL                                                                                                                                                                                                        |  |  |  |  |

| HYBIN-2B            | Hybrid non-inverting input.                                                                                                                                                                                |  |  |  |  |

| HYBIN-2A            | Hybrid inverting input.                                                                                                                                                                                    |  |  |  |  |

| HYBIN-1B            | Hybrid inverting input.                                                                                                                                                                                    |  |  |  |  |

| HYBIN-1A            | Hybrid non-inverting input.                                                                                                                                                                                |  |  |  |  |

| FILTOUTP            | Positive differential output of the antialiasing filter.                                                                                                                                                   |  |  |  |  |

| FILTOUTN            | Negative differential output of the antialiasing filter.                                                                                                                                                   |  |  |  |  |

| ADCINP              | Positive differential input to the ADC.                                                                                                                                                                    |  |  |  |  |

| ADCINN              | Negative differential input to the ADC.                                                                                                                                                                    |  |  |  |  |

| CAP-T               | Receive ADC reference decoupling pin. The reference which supplies the ADC needs some external decoupling.                                                                                                 |  |  |  |  |

| CAP-B               | Receive ADC reference decoupling pin. The reference which supplies the ADC needs some external decoupling.                                                                                                 |  |  |  |  |

| VREF                | Voltage Reference. The external reference is applied to this pin.                                                                                                                                          |  |  |  |  |

| REF-COM             | Reference common.                                                                                                                                                                                          |  |  |  |  |

| COM-LVL             | Common mode level.                                                                                                                                                                                         |  |  |  |  |

| ADCCLK              | ADC Sample clock, logic input. This clock also operates as the frame synchronization.                                                                                                                      |  |  |  |  |

| SCLK                | ADC serial interface clock, logic input.                                                                                                                                                                   |  |  |  |  |

| SDO                 | ADC serial data out.                                                                                                                                                                                       |  |  |  |  |

# AD5011

| Serial Register                                                                                                                            | SEL[2:0]=000<br>Control Reg                                                                                                                                                                                                                 | SEL[2:0]=001<br>Tx Prog Filt Reg                                                                                                        | SEL[2:0]=010<br>Rx Prog Filt Reg                                                                                                                                                            | SEL[2:0]=011<br>Test Purposes Only                                                                                                                                                                                                                                                                                                                                                                    |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| D[15]<br>D[14]<br>D[13]<br>D[12]<br>D[11]<br>D[10]<br>D[9]<br>D[8]<br>D[7]<br>D[6]<br>D[7]<br>D[6]<br>D[5]<br>D[4]<br>D[3]<br>D[2]<br>D[1] | $R/\overline{W} = 0$<br>SEL[2] = 0<br>SEL[1] = 0<br>$\overline{PWDN} \cdot \overline{Tx}$<br>$\overline{PWDN} \cdot \overline{Rx}$<br>LOOPBACK<br>AA-BUF-BP<br>AA-FLTR-BP<br>Tx-GAIN-SEL<br>Tx-DACOUT<br>Tx-LPF-BP<br>Tx-DRVR-BP<br>PGA-GC2 | $R/\overline{W} = 0$ $SEL[2] = 0$ $SEL[0] = 1$ $WRBOTH$ $TPFD[0]$ $TFPD[8]$ $TFPD[7]$ $TFPD[6]$ $TFPD[5]$ $TFPD[4]$ $TFPD[2]$ $TFPD[1]$ | $RV FING FINE Reg$ $R\overline{W} = 0$ $SEL[2] = 0$ $SEL[1] = 1$ $SEL[0] = 0$ $WRBOTH$ $RPFD[10]$ $RPFD[9]$ $RFPD[7]$ $RFPD[6]$ $RFPD[6]$ $RFPD[5]$ $RFPD[4]$ $RFPD[3]$ $RFPD[2]$ $RFPD[1]$ | $R/\overline{W} = 0$ $SEL[2] = 0$ $SEL[1] = 1$ $SEL[0] = 1$ $Reserved$ |  |  |

| D[1]<br>D[0]                                                                                                                               | PGA-GC1<br>PGA-GC0                                                                                                                                                                                                                          | TFPD[0]                                                                                                                                 | RFPD[0]                                                                                                                                                                                     | Reserved<br>Reserved                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

### Table 1. Control Register

## **Control Register Functions**

| Mnemonic                        | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $R/\overline{W}$                | When $R/\overline{W}$ is high, the register bank addressed by SEL[2:0] is loaded into the output shift register.<br>Serial data will subsequently be output onto the DR pin. If $R/\overline{W}$ is low, the serial input data located at D[11:0] will be written into the register bank addressed by SEL[2:0].                                                                                                                                                    |

| $\overline{PWDN}$ -Tx           | When $\overline{PWDN}$ - $\overline{Tx}$ is low, the entire transmit channel is powered down. The line driver output is high impedance when the transmit channel is powered down.                                                                                                                                                                                                                                                                                  |

| $\overline{PWDN}-\overline{Rx}$ | When this bit is low, the entire receive channel is powered down.                                                                                                                                                                                                                                                                                                                                                                                                  |

| LOOPBACK                        | When this bit is high, analog loopback is selected.                                                                                                                                                                                                                                                                                                                                                                                                                |

| AA-BUF-BP                       | When this bit equals 1, the ADC buffer is bypassed.                                                                                                                                                                                                                                                                                                                                                                                                                |

| AA-FLTR-BP                      | When this bit equals 1, the receive filter is bypassed.                                                                                                                                                                                                                                                                                                                                                                                                            |

| Tx-GAIN-SEL                     | When Tx-GAIN-SEL equals 1, the output of the transmit filter is attenuated by 6 dB.                                                                                                                                                                                                                                                                                                                                                                                |

| WRBOTH                          | The transmit and receive programmable filter corner frequencies are addressed by the 11-bits words TPFD and RPFD respectively. TPFD data is loaded from the serial input register to the transmit filter register if $SEL[2:0] = 010$ . RPFD data is written to the receive filter register if $SEL[2:0] = 010$ . If WRBOTH equals 1 during either of the above conditions, the word in the serial input register is loaded into both the TFPD and RFPD registers. |

| Tx-DACOUT | Tx-FILT-BP | Tx-DRVR-BP | Configuration                                                                                                                      |

|-----------|------------|------------|------------------------------------------------------------------------------------------------------------------------------------|

| 0         | 0          | 0          | Default. All Components in the Tx channel are used.                                                                                |

| 1         | 0          | 0          | The DAC output is seen at the line driver output pins. The line driver                                                             |

| 0         |            | 0          | amplifier output is in a high impedance state.                                                                                     |

| 0         | 1          | 0          | The Tx filter is bypassed. The DACOUT is fed to the PGA. The                                                                       |

| 0         | 0          | 1          | filter amplifier output is in a high impedance state.<br>The filter output is seen at the line driver output pins. The line driver |

| 0         | 0          | 1          | amplifier output is in a high impedance state.                                                                                     |

Configuring the Transmit Channel

# AD5011

| GGA-GC2 | PGA-GC1 | PGA-GC0 | Gain (dB) |

|---------|---------|---------|-----------|

| 0       | 0       | 0       | -6        |

| 0       | 0       | 1       | -3        |

| 0       | 1       | 0       | 0         |

| 0       | 1       | 1       | 3         |

| 1       | 0       | 0       | 6         |

| 1       | 0       | 1       | 9         |

| 1       | 1       | 0       | 9         |

| 1       | 1       | 1       | 9         |

Programmable Gain Amplifier Gain Settings (Receive Signal)

Transmit and Receive Filter Corner Frequency (kHz)

|            |         | -       | 5        |

|------------|---------|---------|----------|

| TPFD [7:0] | TPFD[8] | TPFD[9] | TPFD[10] |

| RPFD[0:7]  | RPFD[8] | RPFD[9] | RPFD[10] |

| TBD        | 49      | 108     | 235      |

| TBD        | 52      | 114     | 250      |

| TBD        | 59.8    | 131     | 287      |

| TBD        | 67.5    | 148     | 324      |

| TBD        | 75.3    | 165     | 361      |

| TBD        | 83      | 182     | 399      |

| TBD        | 90.8    | 199     | 436      |

| TBD        | 98.5    | 216     | 473      |

| TBD        | 106.3   | 233     | 510      |

| TBD        | 114     | 250     | 547      |

| TBD        | 120.8   | 265     | 580      |