# **External Memory Interface Handbook Volume 2**

# **Section II. Board Planning**

101 Innovation Drive San Jose, CA 95134 www.altera.com

EMI\_PLAN\_BOARD-3.0

# **Contents**

| Chapter 1. DDR2 and DDR3 SDRAM Interface Termination and Layout Guidelines |     |

|----------------------------------------------------------------------------|-----|

| Leveling and Dynamic ODT                                                   | 1–2 |

| Read and Write Leveling                                                    |     |

| Calibrated Output Impedance and ODT                                        |     |

| Dynamic ODT                                                                |     |

| Dynamic OCT in Stratix III and Stratix IV Devices                          | 1–5 |

| Dynamic OCT in Stratix V Devices                                           |     |

| Board Termination for DDR2 SDRAM                                           |     |

| External Parallel Termination                                              |     |

| On-Chip Termination                                                        |     |

| Recommended Termination Schemes                                            |     |

| Dynamic On-Chip Termination                                                |     |

| FPGA Writing to Memory                                                     |     |

| FPGA Reading from Memory                                                   |     |

| On-Chip Termination (Non-Dynamic)                                          |     |

| Class II External Parallel Termination                                     |     |

| FPGA Writing to Memory                                                     |     |

| FPGA Reading from Memory                                                   |     |

| Class I External Parallel Termination                                      |     |

| FPGA Writing to Memory                                                     |     |

| FPGA Reading from Memory                                                   |     |

| Class I Termination Using ODT                                              |     |

| FPGA Writing to Memory                                                     |     |

| FPGA Reading from Memory                                                   |     |

| No-Parallel Termination                                                    |     |

| FPGA Writing to Memory                                                     |     |

| FPGA Reading from Memory                                                   |     |

| Board Termination for DDR3 SDRAM                                           |     |

| Single-Rank DDR3 SDRAM Unbuffered DIMM                                     |     |

| DQS, DQ, and DM for DDR3 SDRAM UDIMM                                       |     |

| Memory Clocks for DDR3 SDRAM UDIMM                                         |     |

| Commands and Addresses for DDR3 SDRAM UDIMM                                |     |

| Stratix III, Stratix IV, and Stratix V FPGAs                               |     |

| DQS, DQ, and DM for Stratix III, Stratix IV, and Stratix V FPGA            |     |

| Memory Clocks for Stratix III, Stratix IV, and Stratix V FPGA              |     |

| Commands and Addresses for Stratix III and Stratix IV FPGA                 |     |

| Multi-Rank DDR3 SDRAM Unbuffered DIMM                                      |     |

| DDR3 SDRAM Registered DIMM                                                 |     |

| DDR3 SDRAM Components With Leveling                                        |     |

| DDR3 SDRAM Components With or Without Leveling                             |     |

| Stratix III, Stratix IV, and Stratix V FPGAs                               |     |

| Drive Strength                                                             |     |

| How Strong is Strong Enough?                                               |     |

| System Loading                                                             |     |

| Component Versus DIMM                                                      |     |

| FPGA Writing to Memory                                                     |     |

| FPGA Reading from Memory                                                   |     |

| Single- Versus Dual-Rank DIMM                                              |     |

| Single DIMM Versus Multiple DIMMs                                          |     |

iv Contents

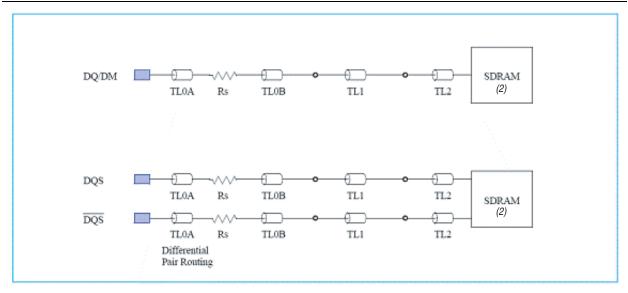

| Design Layout Guidelines                                                                              | . 1–58 |

|-------------------------------------------------------------------------------------------------------|--------|

| Layout Guidelines for DDR2 SDRAM Interface                                                            |        |

| Layout Guidelines for DDR3 SDRAM Interface                                                            |        |

| Layout Guidelines for DDR3 SDRAM Wide Interface (>72 bits)                                            |        |

| Fly-By Network Design for Clock, Command, and Address Signals                                         | . 1–66 |

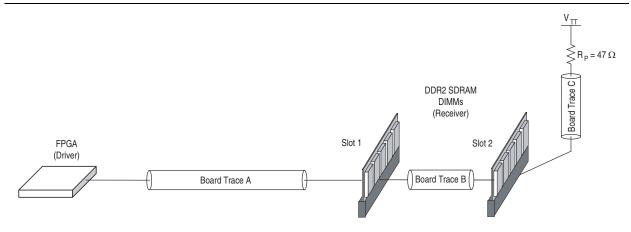

| Chapter 2. Dual-DIMM DDR2 and DDR3 SDRAM Interface Termination, Drive Strength, Loading, an           | d      |

| Board Layout Guidelines                                                                               | 2 1    |

| DDR2 SDRAM                                                                                            |        |

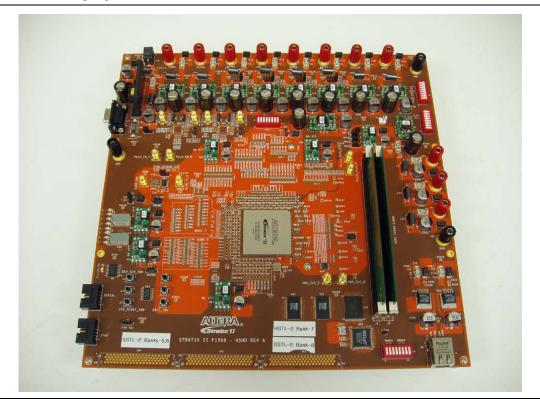

| Stratix II High Speed Board                                                                           |        |

| Overview of ODT Control                                                                               |        |

| DIMM Configuration                                                                                    |        |

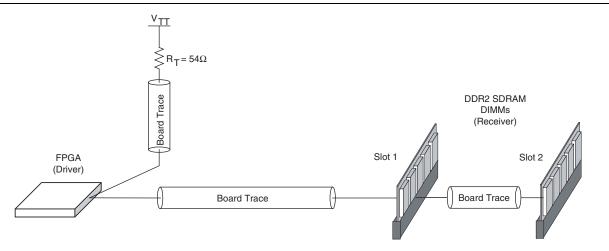

| Dual-DIMM Memory Interface with Slot 1 Populated                                                      |        |

| FPGA Writing to Memory                                                                                | 205    |

| Write to Memory Using an ODT Setting of 150Ω                                                          |        |

| Reading from Memory                                                                                   | ∠-/    |

| FPGA Writing to Memory                                                                                |        |

| Write to Memory Using an ODT Setting of $150\Omega$                                                   | ∠−c    |

| Reading from Memory                                                                                   |        |

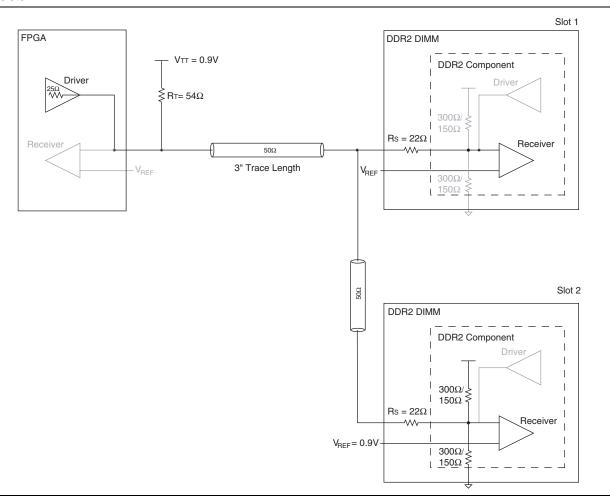

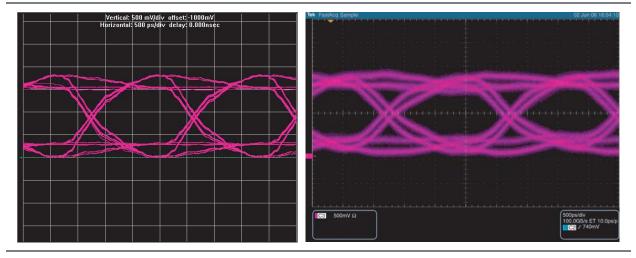

| Dual-DIMM Memory Interface with Both Slot 1 and Slot 2 Populated                                      |        |

| FPGA Writing to Memory                                                                                |        |

| Write to Memory in Slot 1 Using an ODT Setting of 75- $\Omega$                                        |        |

| Write to Memory in Slot 2 Using an ODT Setting of $75-\Omega$                                         |        |

| Reading From Memory                                                                                   |        |

| FPGA OCT Features                                                                                     |        |

| Stratix III and Stratix IV Devices                                                                    |        |

| Arria II GX Devices                                                                                   |        |

| Dual-DIMM DDR2 Clock, Address, and Command Termination and Topology                                   |        |

| Address and Command Signals                                                                           |        |

| Control Group Signals                                                                                 |        |

| Clock Group Signals                                                                                   |        |

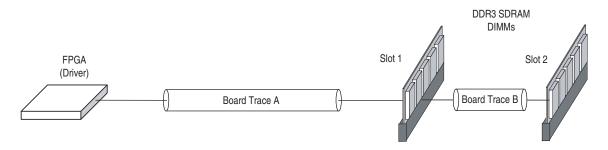

| DDR3 SDRAM                                                                                            |        |

| Comparison of DDR3 and DDR2 DQ and DQS ODT Features and Topology                                      |        |

| Dual-DIMM DDR3 Clock, Address, and Command Termination and Topology                                   |        |

| Address and Command Signals                                                                           |        |

| Control Group Signals                                                                                 |        |

| Clock Group Signals                                                                                   |        |

| Write to Memory in Slot 1 Using an ODT Setting of 75 $\Omega$ With One Slot Populated                 |        |

| Write to Memory in Slot 2 Using an ODT Setting of 75 $\Omega$ With One Slot Populated                 |        |

| Write to Memory in Slot 1 Using an ODT Setting of 150 $\Omega$ With Both Slots Populated              |        |

| Write to Memory in Slot 2 Using an ODT Setting of 150 $\Omega$ With Both Slots Populated              |        |

| Read from Memory in Slot 1 Using an ODT Setting of 150 $\Omega$ on Slot 2 with Both Slots Populated . |        |

| Read From Memory in Slot 2 Using an ODT Setting of 150 $\Omega$ on Slot 1 With Both Slots Populated   | . 2–30 |

| Conclusion                                                                                            | . 2–30 |

| References                                                                                            | . 2–31 |

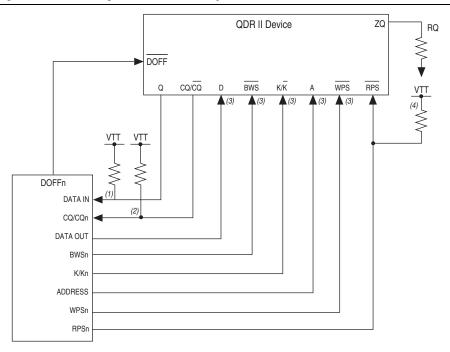

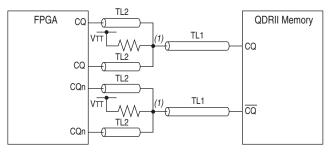

| Chapter 3. QDR II SRAM Interface Termination and Layout Guidelines                                    |        |

| I/O Standards                                                                                         | 3–1    |

| QDR II SRAM Configurations                                                                            |        |

| Signal Terminations                                                                                   |        |

| Output from the FPGA to the QDR II SRAM Component                                                     |        |

| Input to the FPGA from the QDR II SRAM Component                                                      |        |

Contents

| Termination Schemes                                                      | 2 15   |

|--------------------------------------------------------------------------|--------|

| PCB Layout Guidelines                                                    |        |

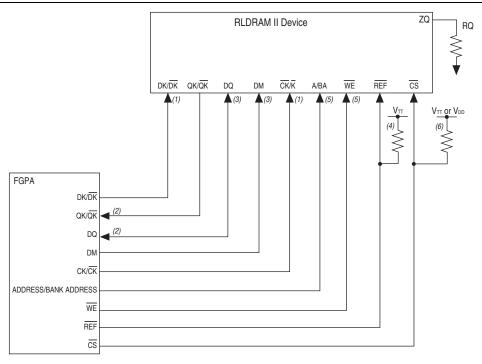

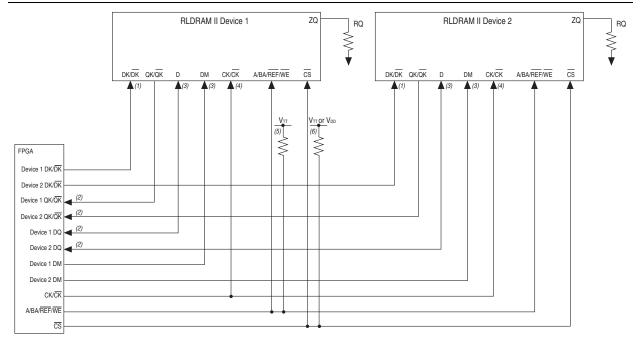

| Chapter 4. RLDRAM II Interface Termination and Layout Guidelines         |        |

| I/O Standards                                                            |        |

| RLDRAM II Configurations                                                 |        |

| Signal Terminations                                                      |        |

| Outputs from the FPGA to the RLDRAM II Component                         |        |

| Input to the FPGA from the RLDRAM II Component                           |        |

| Termination Schemes                                                      | 4–10   |

| PCB Layout Guidelines                                                    |        |

| Chapter 5. Power Estimation Methods for External Memory Interface Design | IS     |

| Additional Information                                                   |        |

| Document Revision History                                                | Info–1 |

| How to Contact Altera                                                    | Info–1 |

| Typographic Conventions                                                  | Info-2 |

vi Contents

# 1. DDR2 and DDR3 SDRAM Interface Termination and Layout Guidelines

This chapter provides guidelines on how to improve the signal integrity of your system and layout guidelines to help you successfully implement a DDR2 or DDR3 SDRAM interface on your system.

DDR3 SDRAM is the third generation of the DDR SDRAM family, and offers improved power, higher data bandwidth, and enhanced signal quality with multiple on-die termination (ODT) selection and output driver impedance control while maintaining partial backward compatibility with the existing DDR2 SDRAM standard.

This chapter focuses on the following key factors that affect signal quality at the receiver:

- Leveling and dynamic ODT

- Proper use of termination

- Output driver drive strength setting

- Loading at the receiver

- Layout guidelines

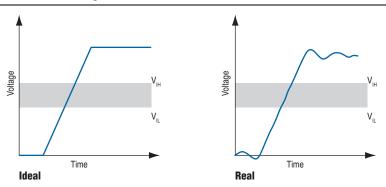

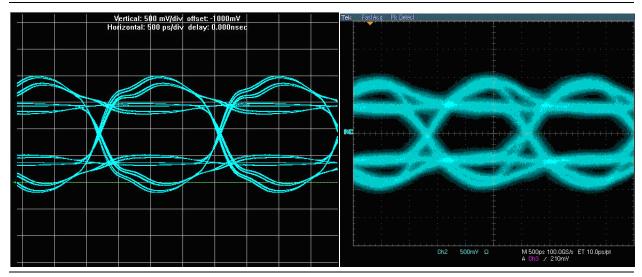

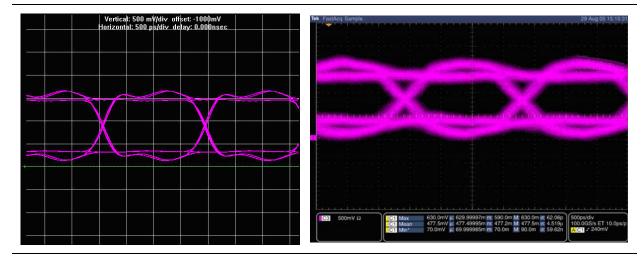

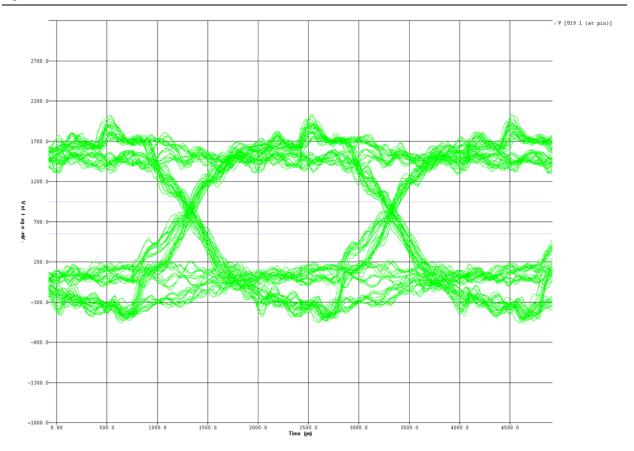

As memory interface performance increases, board designers must pay closer attention to the quality of the signal seen at the receiver because poorly transmitted signals can dramatically reduce the overall data-valid margin at the receiver. Figure 1–1 shows the differences between an ideal and real signal seen by the receiver.

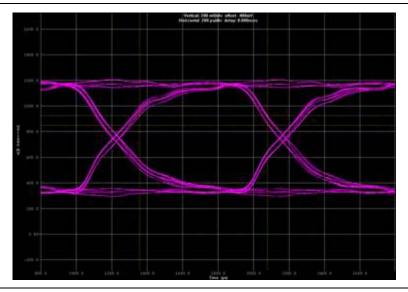

Figure 1–1. Ideal and Real Signal at the Receiver

In addition, this chapter compares various types of termination schemes, and their effects on the signal quality on the receiver. It also discusses the proper drive strength setting on the FPGA to optimize the signal integrity at the receiver, and the effects of different loading types, such as components versus DIMM configuration, on signal quality.

The objective of this chapter is to understand the trade-offs between different types of termination schemes, the effects of output drive strengths, and different loading types, so you can swiftly navigate through the multiple combinations and choose the best possible settings for your designs.

# **Leveling and Dynamic ODT**

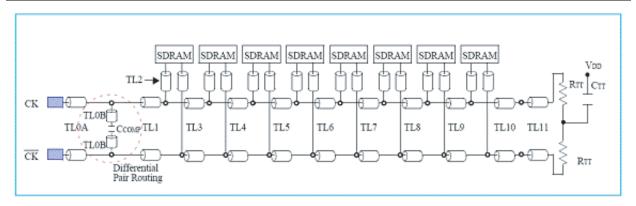

DDR3 SDRAM DIMMs, as specified by JEDEC, always use a fly-by topology for the address, command, and clock signals. This standard DDR3 SDRAM topology requires the use of Altera DDR3 SDRAM Controller with UniPHY or ALTMEMPHY with read and write leveling.

Altera recommends that for full DDR3 SDRAM compatibility when using discrete DDR3 SDRAM components, you should mimic the JEDEC DDR3 UDIMM fly-by topology on your custom printed circuit boards (PCB).

Arria II devices do not support DDR3 SDRAM with read or write leveling, so these devices do not support standard DDR3 SDRAM DIMMs or DDR3 SDRAM components using the standard DDR3 SDRAM fly-by address, command, and clock layout topology.

### **Read and Write Leveling**

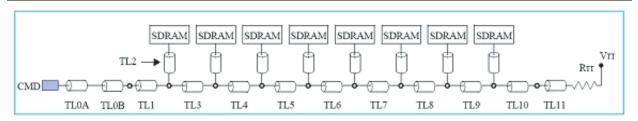

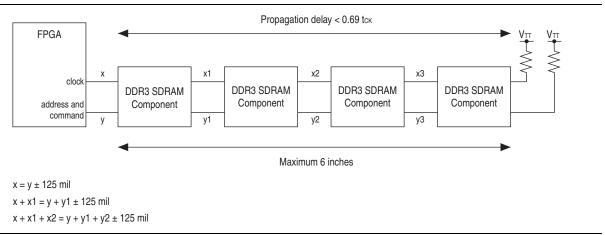

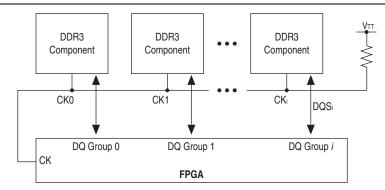

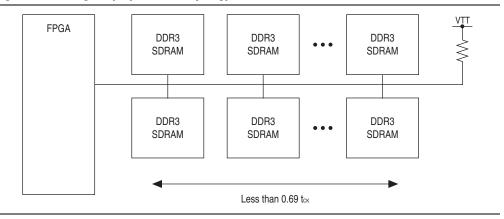

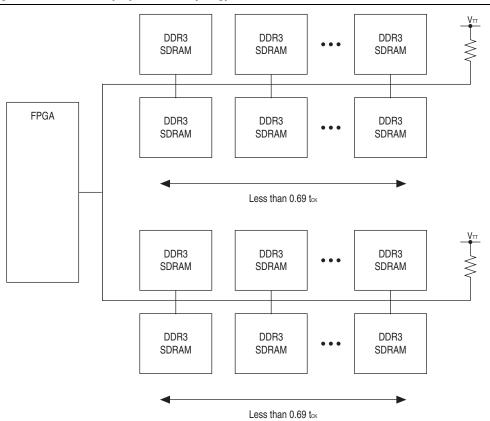

One major difference between DDR2 and DDR3 SDRAM is the use of leveling. To improve signal integrity and support higher frequency operations, the JEDEC committee defined a fly-by termination scheme used with clocks, and command and address bus signals. Fly-by topology reduces simultaneous switching noise (SSN) by deliberately causing flight-time skew between the data and strobes at every DRAM as the clock, address, and command signals traverse the DIMM (Figure 1–2).

Command, Address, Clock in fly-by topology in DDR3 DIMM

Data Skew Calibrated Out at Power Up with Write Leveling

Figure 1–2. DDR3 DIMM Fly-By Topology Requiring Write Leveling

The flight-time skew caused by the fly-by topology led the JEDEC committee to introduce the write leveling feature on the DDR3 SDRAMs; thus requiring controllers to compensate for this skew by adjusting the timing per byte lane.

During a write, DQS groups launch at separate times to coincide with a clock arriving at components on the DIMM, and must meet the timing parameter between the memory clock and DQS defined as  $t_{DOSS}$  of  $\pm$  0.25  $t_{CK}$ .

June 2011

Altera Corporation

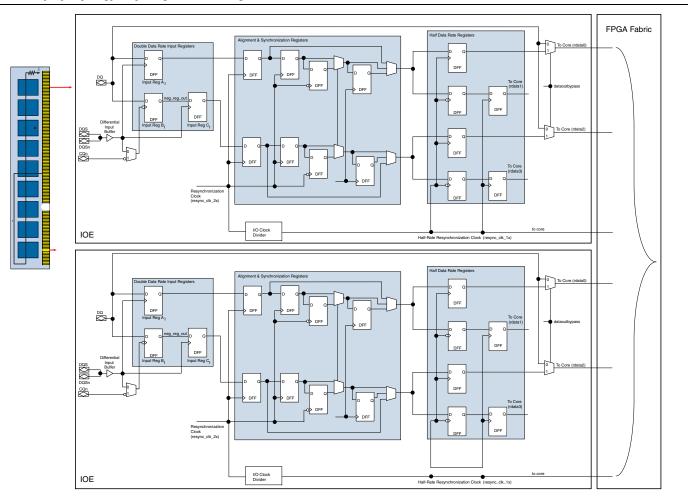

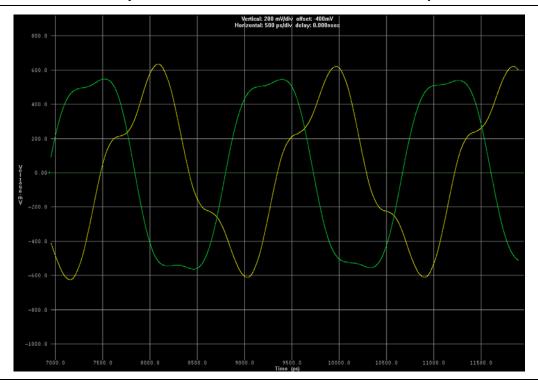

During the read operation, the memory controller must compensate for the delays introduced by the fly-by topology. The Stratix III, Stratix IV, and Stratix V FPGAs have alignment and synchronization registers built in the I/O element (IOE) to properly capture the data.

Figure 1–3 shows two DQS groups returning from the DIMM for the same read command.

Figure 1-3. DDR3 DIMM Fly-By Topology Requiring Read Leveling

## **Calibrated Output Impedance and ODT**

In DDR2 SDRAM, there are only two drive strength settings, full or reduced, which correspond to the output impedance of 18  $\Omega$  and 40  $\Omega$ , respectively. These output drive strength settings are static settings and are not calibrated; as a result, the output impedance varies as the voltage and temperature drifts.

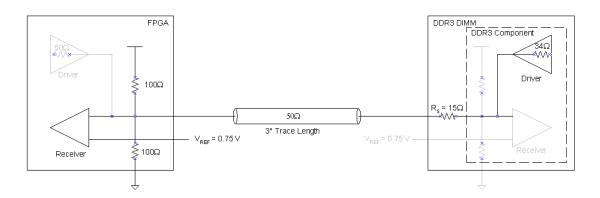

The DDR3 SDRAM uses a programmable impedance output buffer. Currently, there are two drive strength settings,  $34~\Omega$  and  $40~\Omega$ . The 40- $\Omega$  drive strength setting is currently a reserved specification defined by JEDEC, but available on the DDR3 SDRAM, as offered by some memory vendors. Refer to the datasheet of the respective memory vendors for more information about the output impedance setting. You select the drive strength settings by programming the memory mode register defined by mode register 1 (MR1). To calibrate output driver impedance, an external precision resistor, RZQ, connects the ZQ pin and VSSQ. The value of this resistor must be  $240~\Omega \pm 1\%$ .

If you are using a DDR3 SDRAM DIMM, RZQ is soldered on the DIMM so you do not need to layout your board to account for it. Output impedance is set during initialization. To calibrate output driver impedance after power-up, the DDR3 SDRAM needs a calibration command that is part of the initialization and reset procedure and is updated periodically when the controller issues a calibration command.

In addition to calibrated output impedance, the DDR3 SDRAM also supports calibrated parallel ODT through the same external precision resistor, RZQ, which is possible by using a merged output driver structure in the DDR3 SDRAM, which also helps to improve pin capacitance in the DQ and DQS pins. The ODT values supported in DDR3 SDRAM are 20  $\Omega$ , 30  $\Omega$ , 40  $\Omega$ , 60  $\Omega$ , and 120  $\Omega$ , assuming that RZQ is 240  $\Omega$ .

In DDR3 SDRAM, there are two commands related to the calibration of the output driver impedance and ODT. The controller often uses the first calibration command, ZQ CALIBRATION LONG (ZQCL), at initial power-up or when the DDR3 SDRAM is in a reset condition. This command calibrates the output driver impedance and ODT to the initial temperature and voltage condition, and compensates for any process variation due to manufacturing. If the controller issues the ZQCL command at initialization or reset, it takes 512 memory clock cycles to complete; otherwise, it requires 256 memory clock cycles to complete. The controller uses the second calibration command, ZQ CALIBRATION SHORT (ZQCS) during regular operation to track any variation in temperature or voltage. The ZQCS command takes 64 memory clock cycles to complete. Use the ZQCL command any time there is more impedance error than can be corrected with a ZQCS command.

For more information about using ZQ Calibration in DDR3 SDRAM, refer to the application note by Micron, *TN-41-02 DDR3 ZQ Calibration*.

# **Dynamic ODT**

Dynamic ODT is a new feature in DDR3 SDRAM, and not available in DDR2 SDRAM. Dynamic ODT can change the ODT setting without issuing a mode register set (MRS) command. When you enable dynamic ODT, and there is no write operation, the DDR3 SDRAM terminates to a termination setting of RTT\_NORM; when there is a write operation, the DDR3 SDRAM terminates to a setting of RTT\_WR. You can preset the values of RTT\_NORM and RTT\_WR by programming the mode registers, MR1 and MR2.

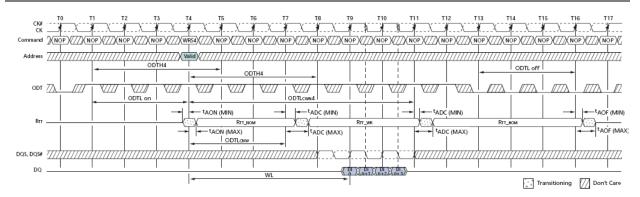

Figure 1–4 shows the behavior of ODT when you enable dynamic ODT.

### Note to Figure 1-4:

(1) Source: TN-41-04 DDR3 Dynamic On-Die Termination, Micron.

In the two-DIMM DDR3 SDRAM configuration, dynamic ODT helps reduce the jitter at the module being accessed, and minimizes reflections from any secondary modules.

For more information about using the dynamic ODT on DDR3 SDRAM, refer to the application note by Micron, *TN-41-04 DDR3 Dynamic On-Die Termination*.

### Dynamic OCT in Stratix III and Stratix IV Devices

Stratix III and Stratix IV devices support on-off dynamic series and parallel termination for a bi-directional I/O in all I/O banks. Dynamic OCT is a new feature in Stratix III and Stratix IV FPGA devices. You enable dynamic parallel termination only when the bidirectional I/O acts as a receiver and disable it when the bidirectional I/O acts as a driver. Similarly, you enable dynamic series termination only when the bidirectional I/O acts as a driver and is disable it when the bidirectional I/O acts as a receiver. The default setting for dynamic OCT is series termination, to save power when the interface is idle—no active reads or writes.

Additionally, the dynamic control operation of the OCT is separate to the output enable signal for the buffer. Hence, UniPHY IP can only enable parallel OCT during read cycles, saving power when the interface is idle.

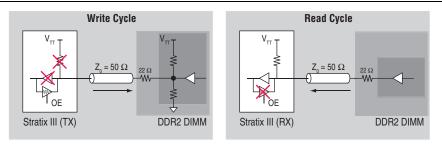

Figure 1–5. Dynamic OCT Between Stratix III and Stratix IV FPGA Devices

This feature is useful for terminating any high-performance bidirectional path because signal integrity is optimized depending on the direction of the data. In addition, dynamic OCT also eliminates the need for external termination resistors when used with memory devices that support ODT (such as DDR3 SDRAM), thus reducing cost and easing board layout.

However, dynamic OCT in Stratix III and Stratix IV FPGA devices is different from dynamic ODT in DDR3 SDRAM mentioned in previous sections and these features should not be assumed to be identical.

For detailed information about the dynamic OCT feature in the Stratix III FPGA, refer to the *Stratix III Device I/O Features* chapter in volume 1 of the *Stratix III Device Handbook*.

For detailed information about the dynamic OCT feature in the Stratix IV FPGA, refer to the *I/O Features in Stratix IV Devices* chapter in volume 1 of the *Stratix IV Device Handbook*.

### **Dynamic OCT in Stratix V Devices**

Stratix V devices also support dynamic OCT feature and provide more flexibility. Stratix V OCT calibration uses one RZQ pin that exists in every OCT block. You can use any one of the following as a reference resistor on the RZQ pin to implement different OCT values:

- **2**40-Ω reference resistor—to implement  $R_S$  OCT of 34 Ω, 40 Ω, 48 Ω, 60 Ω, and 80 Ω; and  $R_T$  OCT resistance of 20 Ω, 30 Ω, 40 Ω, and 120 Ω.

- 100  $\Omega$  reference resistor—to implement R<sub>S</sub> OCT of 25  $\Omega$  and 50  $\Omega$ ; and R<sub>T</sub> OCT resistance of 50  $\Omega$ .

For detailed information about the dynamic OCT feature in the Stratix V FPGA, refer to the *I/O Features in Stratix V Devices* chapter in volume 1 of the *Stratix V Device Handbook*.

# **Board Termination for DDR2 SDRAM**

DDR2 adheres to the JEDEC standard of governing Stub-Series Terminated Logic (SSTL), JESD8-15a, which includes four different termination schemes.

Two commonly used termination schemes of SSTL are:

- Single parallel terminated output load with or without series resistors (Class I, as stated in JESD8-15a)

- Double parallel terminated output load with or without series resistors (Class II, as stated in JESD8-15a)

Depending on the type of signals you choose, you can use either termination scheme. Also, depending on your design's FPGA and SDRAM memory devices, you may choose external or internal termination schemes.

With the ever-increasing requirements to reduce system cost and simplify printed circuit board (PCB) layout design, you may choose not to have any parallel termination on the transmission line, and use point-to-point connections between the memory interface and the memory. In this case, you may take advantage of internal termination schemes such as on-chip termination (OCT) on the FPGA side and on-die termination (ODT) on the SDRAM side when it is offered on your chosen device.

## **External Parallel Termination**

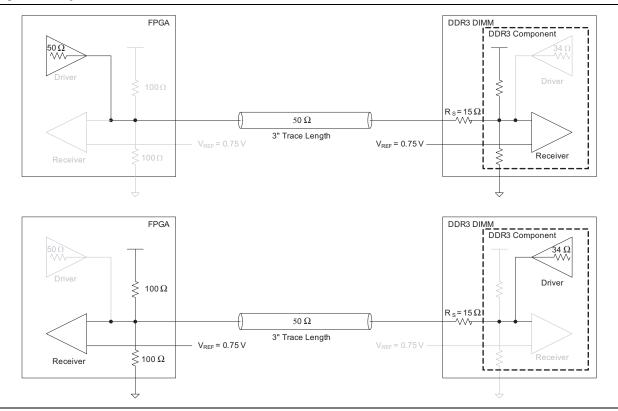

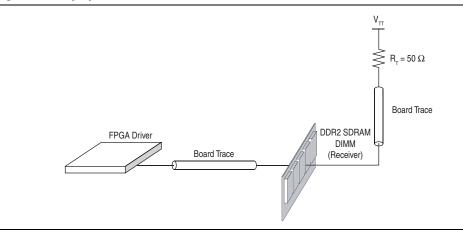

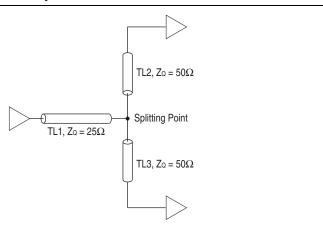

If you use external termination, you must study the locations of the termination resistors to determine which topology works best for your design. Figure 1–6 and Figure 1–7 illustrate the two most commonly used termination topologies: fly-by topology and non-fly-by topology, respectively.

Figure 1-6. Fly-By Placement of a Parallel Resistor

With fly-by topology (Figure 1–6), you place the parallel termination resistor after the receiver. This termination placement resolves the undesirable unterminated stub found in the non-fly-by topology. However, using this topology can be costly and complicate routing. The Stratix II Memory Board 2 uses the fly-by topology for the parallel terminating resistors placement. The Stratix II Memory Board 2 is a memory test board available only within Altera for the purpose of testing and validating Altera's memory interface.

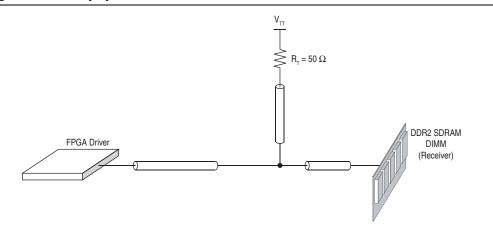

Figure 1-7. Non-Fly-By Placement of a Parallel Resistor

With non-fly-by topology (Figure 1–7), the parallel termination resistor is placed between the driver and receiver (closest to the receiver). This termination placement is easier for board layout, but results in a short stub, which causes an unterminated transmission line between the terminating resistor and the receiver. The unterminated transmission line results in ringing and reflection at the receiver.

If you do not use external termination, DDR2 offers ODT and Altera® FPGAs have varying levels of OCT support. You should explore using ODT and OCT to decrease the board power consumption and reduce the required board real estate.

# **On-Chip Termination**

OCT technology is offered on Arria II GX, Cyclone III, Stratix III, Stratix IV, and Stratix V devices. Table 1–1 summarizes the extent of OCT support for each device. This table provides information about SSTL-18 standards because SSTL-18 is the supported standard for DDR2 memory interface by Altera FPGAs.

On-chip series (R<sub>S</sub>) termination is supported only on output and bidirectional buffers. The value of R<sub>S</sub> with calibration is calibrated against a 25- $\Omega$  resistor for class II and 50- $\Omega$  resistor for class I connected to R<sub>UP</sub> and R<sub>DN</sub> pins and adjusted to  $\pm$  1% of 25  $\Omega$  or 50  $\Omega$ . On-chip parallel (R<sub>T</sub>) termination is supported only on inputs and bidirectional buffers. The value of R<sub>T</sub> is calibrated against 100  $\Omega$  connected to the R<sub>UP</sub> and R<sub>DN</sub> pins. Calibration occurs at the end of device configuration. Dynamic OCT is supported only on bidirectional I/O buffers.

Table 1-1. On-Chip Termination Schemes

|                                               |                            | FPGA Device   |         |                               |         |                               |         |               |         |

|-----------------------------------------------|----------------------------|---------------|---------|-------------------------------|---------|-------------------------------|---------|---------------|---------|

| Termination Scheme                            | SSTL-<br>18                | Arria II GX   |         | Cyclone III and<br>Cyclone IV |         | Stratix III and<br>Stratix IV |         | Stratix V     |         |

|                                               |                            | Column<br>I/O | Row I/O | Column<br>I/O                 | Row I/O | Column<br>I/O                 | Row I/O | Column<br>I/O | Row I/O |

| On-Chip Series Termination                    | Class I                    | 50            | 50      | 50                            | 50      | 50                            | 50      | 50            | _       |

| without Calibration                           | Class II                   | 25            | _       | 25                            | 25      | 25                            | 25      | 25            | _       |

| On-Chip Series Termination                    | Class I                    | 50            | _       | 50                            | 50      | 50                            | 50      | 50            | _       |

| with Calibration                              | Class II                   | _             | _       | 25                            | 25      | 25                            | 25      | 25            | _       |

| On-Chip Parallel Termination with Calibration | Class I<br>and<br>Class II | _             | _       | _                             | _       | 50                            | 50      | 50            | _       |

The dynamic OCT scheme is only available in Stratix III, Stratix IV, and Stratix V FPGAs. The dynamic OCT scheme enables series termination ( $R_S$ ) and parallel termination ( $R_T$ ) to be dynamically turned on and off during the data transfer.

The series and parallel terminations are turned on or off depending on the read and write cycle of the interface. During the write cycle, the  $R_S$  is turned on and the  $R_T$  is turned off to match the line impedance. During the read cycle, the  $R_S$  is turned off and the  $R_T$  is turned on as the Stratix III FPGA implements the far-end termination of the bus (Figure 1–8).

Figure 1-8. Dynamic OCT for Memory Interfaces

# **Recommended Termination Schemes**

Table 1–2 provides the recommended termination schemes for major DDR2 memory interface signals. Signals include data (DQ), data strobe (DQS/DQSn), data mask (DM), clocks (mem clk/mem clk n), and address and command signals.

When interfacing with multiple DDR2 SDRAM components where the address, command, and memory clock pins are connected to more than one load, follow these steps:

- 1. Simulate the system to get the new slew-rate for these signals.

- 2. Use the derated tIS and tIH specifications from the DDR2 SDRAM datasheet based on the simulation results.

- 3. If timing deration causes your interface to fail timing requirements, consider signal duplication of these signals to lower their loading, and hence improve timing.

- Altera uses Class I and Class II termination in this table to refer to drive strength, and not physical termination.

- You must simulate your design for your system to ensure correct functionality.

Table 1–2. Termination Recommendations (Part 1 of 2) (Note 1)

| Device Family       | Signal Type         | SSTL 18 IO Standard (2), (3), (4), (5), (6) | FPGA End<br>Discrete<br>Termination       | Memory End Termination<br>1 Rank/DIMM                                                  | Memory<br>I/O<br>Standard |

|---------------------|---------------------|---------------------------------------------|-------------------------------------------|----------------------------------------------------------------------------------------|---------------------------|

| Arria II GX         |                     |                                             |                                           |                                                                                        |                           |

|                     | DQ/DQS              | Class I 8 mA                                | $50 \Omega$ Parallel to $V_{TT}$ discrete | ODT75 (7)                                                                              | HALF (7)                  |

| DDR2 component      | DM                  | Class I 8 mA                                | N/A                                       | EC O parallal to V                                                                     | N/A                       |

|                     | Address and command | Class I MAX                                 | N/A                                       | - 56 Ω parallel to V <sub>TT</sub><br>discrete                                         | N/A                       |

|                     | Clock               | Class I 8 mA                                | N/A                                       | $\times 1 = 100 \Omega$ differential (10)<br>$\times 2 = 200 \Omega$ differential (11) | N/A                       |

|                     | DQ/DQS              | Class I 8 mA                                | $50 \Omega$ Parallel to $V_{TT}$ discrete | ODT75 (7)                                                                              | FULL (9)                  |

| DDR2 DIMM           | DM                  | Class I 8 mA                                | N/A                                       | 56 $\Omega$ parallel to $V_{TT}$                                                       | N/A                       |

| DDR2 DIIVIIVI       | Address and command | Class I MAX                                 | N/A                                       | discrete                                                                               | N/A                       |

|                     | Clock               | Class I 8 mA                                | N/A                                       | N/A = on DIMM                                                                          | N/A                       |

| Cyclone III and Cyc | clone IV            |                                             |                                           |                                                                                        |                           |

|                     | DQ/DQS              | Class I 12 mA                               | $50 \Omega$ Parallel to $V_{TT}$ discrete | ODT75 (7)                                                                              | HALF (8)                  |

|                     | DM                  | Class I 12 mA                               | N/A                                       | 56 $\Omega$ parallel to $V_{TT}$                                                       | N/A                       |

| DDR2 component      | Address and command | Class I MAX                                 | N/A                                       | discrete                                                                               | N/A                       |

|                     | Clock               | Class I 12 mA                               | N/A                                       | $\times 1 = 100 \Omega$ differential (10)<br>$\times 2 = 200 \Omega$ differential (11) | N/A                       |

|                     | DQ/DQS              | Class I 12 mA                               | $50 \Omega$ Parallel to $V_{TT}$ discrete | ODT75 (7)                                                                              | FULL (9)                  |

| DDR2 DIMM           | DM                  | Class I12 mA                                | N/A                                       | - 56 Ω parallel to $V_{TT}$                                                            | N/A                       |

| DOING DIIVIIVI      | Address and command | Class I MAX                                 | N/A                                       | discrete                                                                               | N/A                       |

|                     | Clock               | Class I 12 mA                               | N/A                                       | N/A = on DIMM                                                                          | N/A                       |

Table 1–2. Termination Recommendations (Part 2 of 2) (Note 1)

| Device Family          | Signal Type          | SSTL 18 IO Standard<br>(2), (3), (4), (5), (6) | FPGA End<br>Discrete<br>Termination | Memory End Termination<br>1 Rank/DIMM  | Memory<br>I/O<br>Standard |

|------------------------|----------------------|------------------------------------------------|-------------------------------------|----------------------------------------|---------------------------|

| Stratix III, Stratix I | V, and Stratix V     |                                                |                                     |                                        |                           |

|                        | DQ/DQS               | Class I R50/P50 DYN CAL                        | N/A                                 | ODT75 (7)                              | HALF (7)                  |

|                        | DM                   | Class I R50 CAL                                | N/A                                 | ODT75 (7)                              | N/A                       |

| Address and command    |                      | Class I R50 CAL                                | N/A                                 | 56 $\Omega$ Parallel to $V_T$ discrete | N/A                       |

| DDR2 component         | Clock                | DIFF Class I R50 NO CAL                        | N/A                                 | $x1 = 100 \Omega$ differential (10)    | N/A                       |

|                        | GIOCK                | DIFF Class I R50 NO CAL                        | N/A                                 | $X2 = 200 \Omega$ differential (11)    | N/A                       |

| DQS DIFF recommend     |                      | DIFF Class I R50/P50 DYN<br>CAL                | N/A                                 | ODT75 (7)                              | HALF (7)                  |

|                        | DQS SE (12)          | Class I R50/P50 DYN CAL                        | N/A                                 | ODT75 (7)                              | HALF (7)                  |

|                        | DQ/DQS               | Class I R50/P50 DYN CAL                        | N/A                                 | ODT75 (7)                              | FULL (9)                  |

|                        | DM                   | Class I R50 CAL                                | N/A                                 | ODT75 (7)                              | N/A                       |

| DDR2 DIMM              | Address and command  | Class I MAX                                    | N/A                                 | 56 $\Omega$ Parallel to $V_T$ discrete | N/A                       |

| DUNZ DIIVIIVI          | Clock                | DIFF Class I R50 NO CAL                        | N/A                                 | N/A = on DIMM                          | N/A                       |

|                        | DQS DIFF recommended | DIFF Class I R50/P50 DYN<br>CAL                | N/A                                 | ODT75 (7)                              | FULL (9)                  |

|                        | DQS SE (12)          | Class I R50/P50 DYN CAL                        | N/A                                 | ODT75 (7)                              | FULL (9)                  |

#### Notes to Table 1-2:

- (1) N/A is not available.

- (2) R is series resistor.

- (3) P is parallel resistor.

- (4) DYN is dynamic OCT.

- (5) NO CAL is OCT without calibration.

- (6) CAL is OCT with calibration.

- (7) ODT75 vs. ODT50 on the memory has the effect of opening the eye more, with a limited increase in overshoot/undershoot.

- (8) HALF is reduced drive strength.

- (9) FULL is full drive strength.

- (10) x1 is a single-device load.

- (11) x2 is two-device load.

- (12) DQS SE is single-ended DQS.

# **Dynamic On-Chip Termination**

The termination schemes are described in JEDEC standard JESD8-15a for SSTL 18 I/O. Dynamic OCT is available in Stratix III and Stratix IV. When the Stratix III FPGA (driver) is writing to the DDR2 SDRAM DIMM (receiver), series OCT is enabled dynamically to match the impedance of the transmission line. As a result, reflections are significantly reduced. Similarly, when the FPGA is reading from the DDR2 SDRAM DIMM, the parallel OCT is dynamically enabled.

For information about setting the proper value for termination resistors, refer to the *Stratix III Device I/O Features* chapter in the *Stratix III Device Handbook* and the *I/O Features in Stratix IV Devices* chapter in the *Stratix IV Device Handbook*..

### **FPGA Writing to Memory**

Figure 1–9 shows dynamic series OCT scheme when the FPGA is writing to the memory. The benefit of using dynamic series OCT is that when driver is driving the transmission line, it "sees" a matched transmission line with no external resistor termination.

Figure 1-9. Dynamic Series OCT Scheme with ODT on the Memory

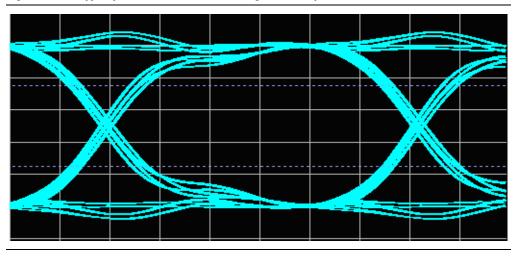

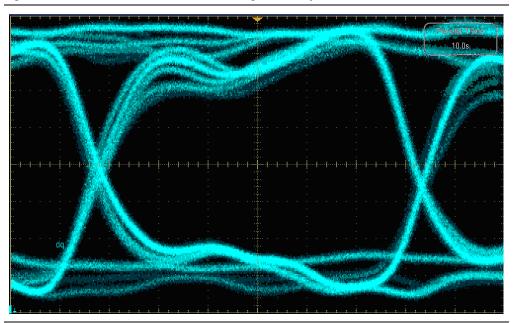

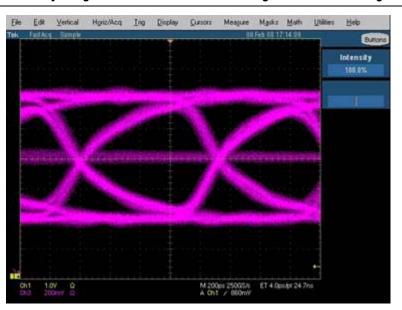

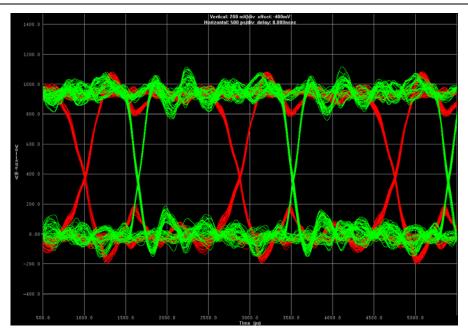

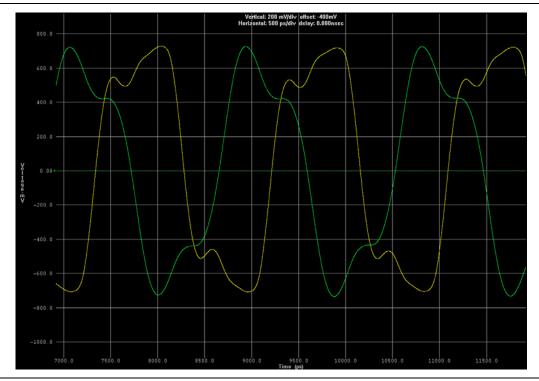

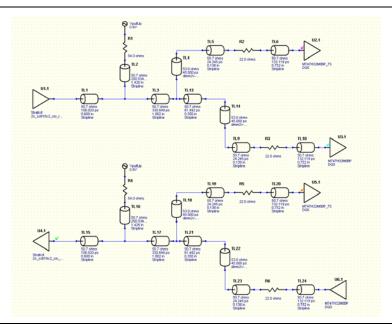

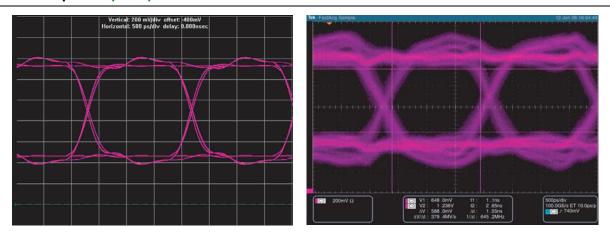

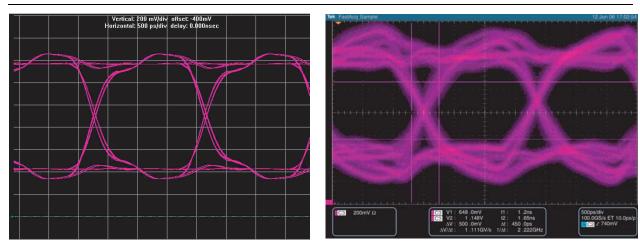

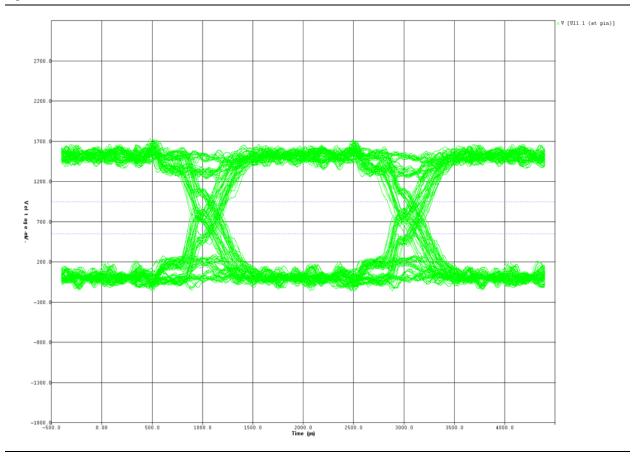

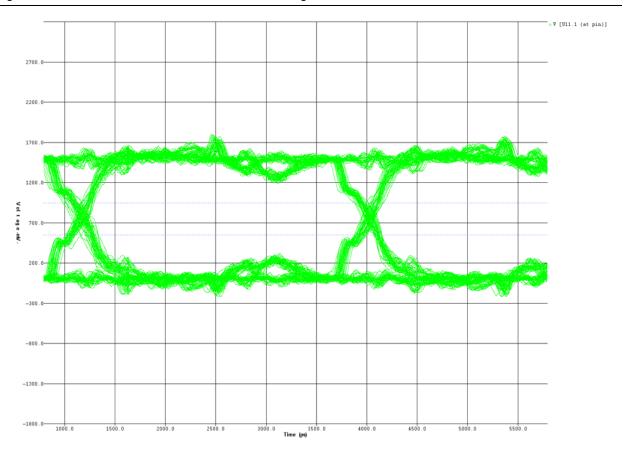

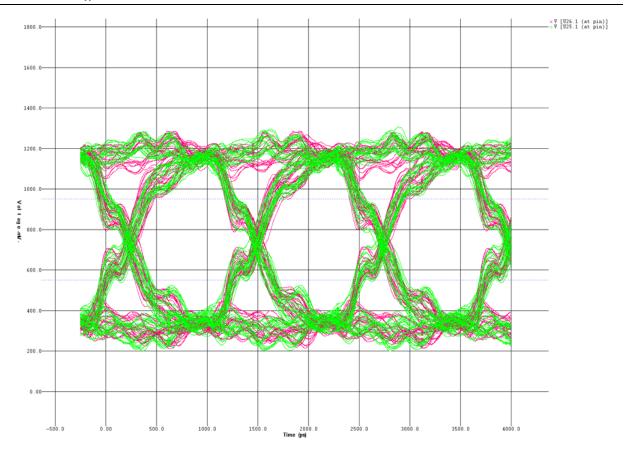

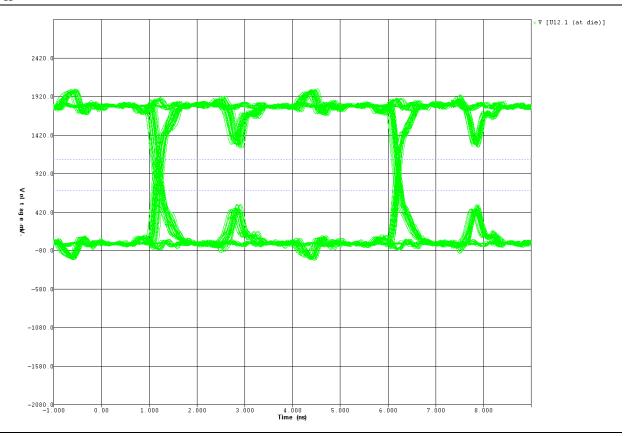

Figure 1–10 and Figure 1–11 show the simulation and measurement results of a write to the DDR2 SDRAM DIMM. The system uses Class I termination with a 50- $\Omega$  series OCT measured at the DIMM with a full drive strength and a 75  $\Omega$  ODT at the DIMM. Both simulation and bench measurements are in 200 pS/div and 200 mV/div.

Figure 1–10. HyperLynx Simulation FPGA Writing to Memory

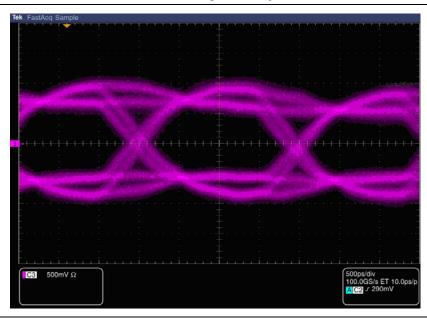

Figure 1-11. Board Measurement, FPGA Writing to Memory

Table 1–3 summarizes the comparison between the simulation and the board measurement of the signal seen at the DDR2 SDRAM DIMM.

Table 1–3. Signal Comparison When the FPGA is Writing to the Memory (Note 1)

|                   | Eye Width (ns)<br><i>(2)</i> | Eye Height (V) | Overshoot (V) | Undershoot (V) |

|-------------------|------------------------------|----------------|---------------|----------------|

| Simulation        | 1.194                        | 0.740          | N/A           | N/A            |

| Board Measurement | 1.08                         | 0.7            | N/A           | N/A            |

#### Notes to Table 1-3:

- (1) N/A is not applicable.

- (2) The eye width is measured from  $V_{IH}/V_{IL}(ac) = VREF \pm 250$  mV to  $V_{IH}/V_{IL}(dc) = VREF \pm 125$  mV, where  $V_{IH}$  and  $V_{IL}$  are determined per the JEDEC specification for SSTL-18.

The data in Table 1–3 and Figure 1–10 and Figure 1–11 suggest that when the FPGA is writing to the memory, the bench measurements are closely matched with simulation measurements. They indicate that using the series dynamic on-chip termination scheme for your bidirectional I/Os maintains the integrity of the signal, while it removes the need for external termination.

Depending on the I/O standard, you should consider the four parameters listed in Table 1–3 when designing a memory interface. Although the simulation and board measurement appear to be similar, there are some discrepancies when the key parameters are measured. Although simulation does not fully model the duty cycle distortion of the I/O, crosstalk, or board power plane degradation, it provides a good indication on the performance of the board.

For memory interfaces, the eye width is important when determining if there is a sufficient window to correctly capture the data. Regarding the eye height, even though most memory interfaces use voltage-referenced I/O standards (in this case, SSTL-18), as long as there is sufficient eye opening below and above VIL and VIH, there should be enough margin to correctly capture the data. However, because effects such as crosstalk are not taken into account, it is critical to design a system to achieve the optimum eye height, because it impacts the overall margin of a system with a memory interface.

Refer to the memory vendors when determining the over- and undershoot. They typically specify a maximum limit on the input voltage to prevent reliability issues.

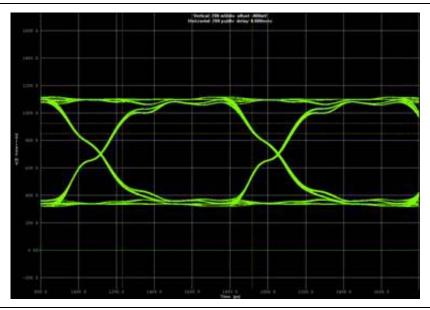

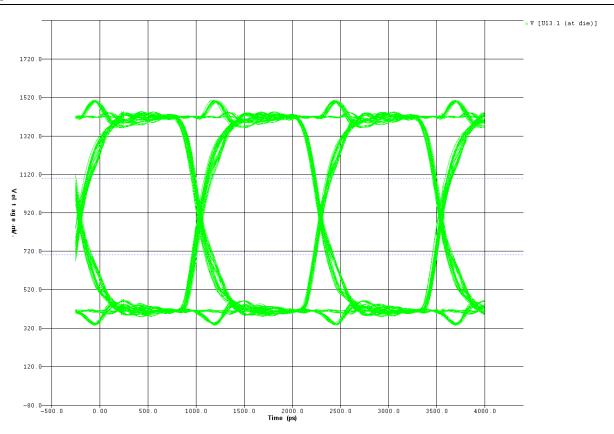

### **FPGA Reading from Memory**

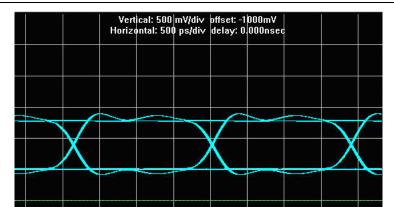

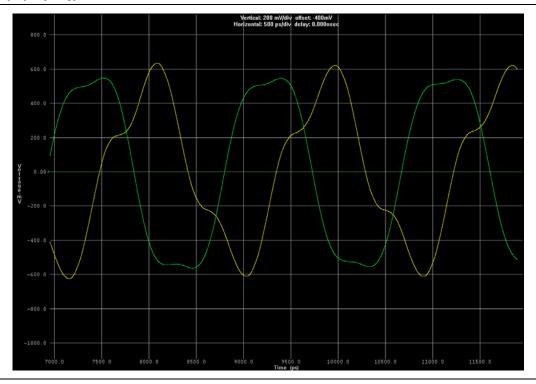

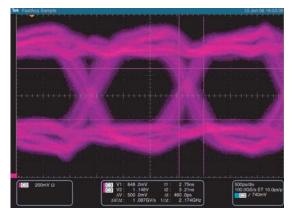

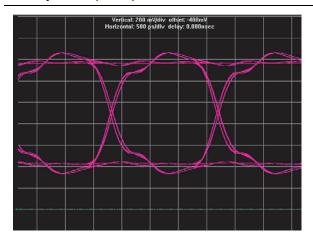

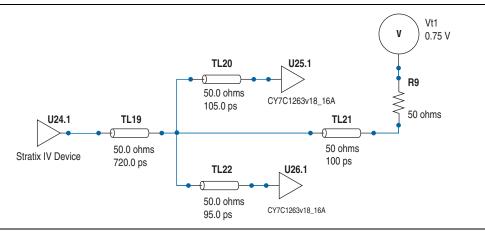

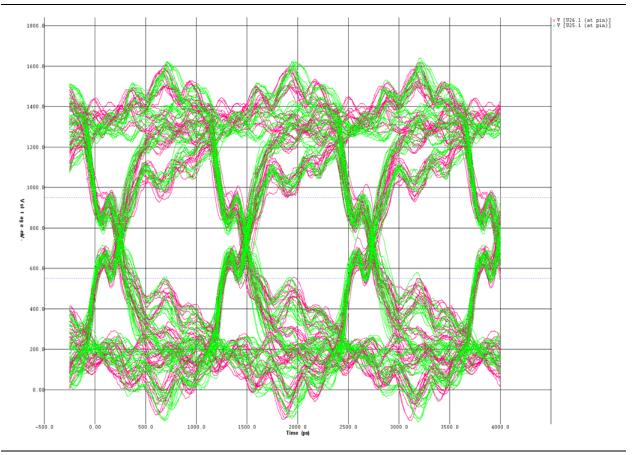

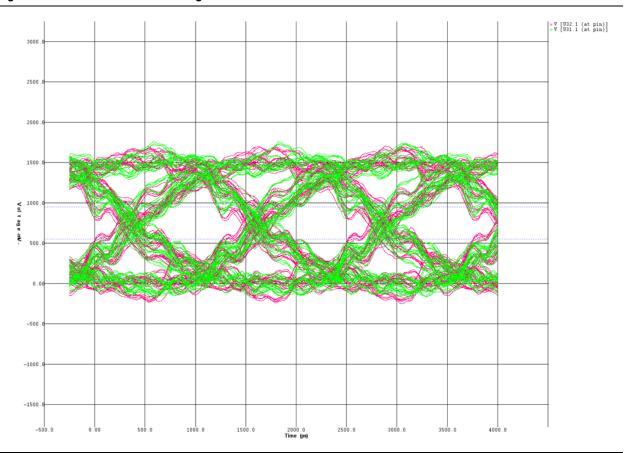

Figure 1–12 shows the dynamic parallel termination scheme when the FPGA is reading from memory. When the DDR2 SDRAM DIMM is driving the transmission line, the ringing and reflection is minimal because the FPGA-side termination 50- $\Omega$  pull-up resistor is matched with the transmission line. Figure 1–13 shows the simulation and measurement results of a read from DDR2 SDRAM DIMM. The system uses Class I termination with a 50- $\Omega$  calibrated parallel OCT measured at the FPGA end with a full drive strength and a 75- $\Omega$  ODT at the memory. Both simulation and bench measurements are in 200 pS/div and 200 mV/div.

Figure 1–12. Dynamic Parallel OCT Scheme with Memory-Side Series Resistor

Figure 1-13. Hyperlynx Simulation and Board Measurement, FPGA Reading from Memory

Table 1–4 summarizes the comparison between the simulation and the board measurement of the signal seen at the FPGA end.

Table 1-4. Signal Comparison When the FPGA is Reading from the Memory (Note 1), (2)

|                   | Eye Width (ns) | Eye Height (V) | Overshoot (V) | Undershoot (V) |

|-------------------|----------------|----------------|---------------|----------------|

| Simulation        | 1.206          | 0.740          | N/A           | N/A            |

| Board Measurement | 1.140          | 0.680          | N/A           | N/A            |

#### Notes to Table 1-4:

- (1) The drive strength on the memory DIMM is set to Full.

- (2) N/A is not applicable.

- (3) The eye width is measured from  $V_{IH}/V_{IL}(ac) = VREF \pm 250$  mV to  $V_{IH}/V_{IL}(dc) = VREF \pm 125$  mV, in which  $V_{IH}$  and  $V_{IL}$  are determined per the JEDEC specification for SSTL-18.

The data in Table 1–4 and Figure 1–13 suggest that bench measurements are closely matched with simulation measurements when the FPGA is reading from the memory. They indicate that using the parallel dynamic on-chip termination scheme in bidirectional I/Os maintains the integrity of the signal, while it removes the need for external termination.

## **On-Chip Termination (Non-Dynamic)**

When you use the 50- $\Omega$  OCT feature in a Class I termination scheme using ODT with a memory-side series resistor, the output driver is tuned to  $50~\Omega$ , which matches the characteristic impedance of the transmission line. Figure 1–14 shows the Class I termination scheme using ODT when the 50- $\Omega$  OCT on the FPGA is turned on.

Figure 1–14. Class I Termination Using ODT with 50- $\Omega$  OCT

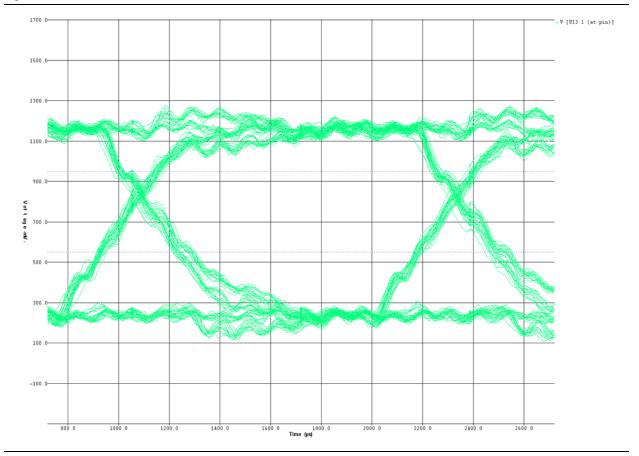

The resulting signal quality has a similar eye opening to the 8 mA drive strength setting (refer to "Drive Strength" on page 1–51) without any over- or undershoot. Figure 1–15 shows the simulation and measurement of the signal at the memory side (DDR2 SDRAM DIMM) with the drive strength setting of 50- $\Omega$  OCT in the FPGA.

Figure 1–15. HyperLynx Simulation and Measurement, FPGA Writing to Memory

Table 1–5 shows data for the signal at the DDR2 SDRAM DIMM of a Class I scheme termination using ODT with a memory-side series resistor. The FPGA is writing to the memory with 50- $\Omega$  OCT.

Table 1–5. Simulation and Board Measurement Results for 50- $\Omega$  OCT and 8-mA Drive Strength Settings (Note 1)

|                                         | Eye Width (ns) | Eye Height (V) | Overshoot (V) | Undershoot (V) |  |  |

|-----------------------------------------|----------------|----------------|---------------|----------------|--|--|

| 50- $\Omega$ OCT Drive Strength Setting |                |                |               |                |  |  |

| Simulation                              | 1.68           | 0.82           | N/A           | N/A            |  |  |

| Board Measurement                       | 1.30           | 0.70           | N/A           | N/A            |  |  |

### Note to Table 1-5:

(1) N/A is not applicable.

When you use the  $50-\Omega$  OCT setting on the FPGA, the signal quality for the Class I termination using ODT with a memory-side series resistor is further improved with lower over- and undershoot.

In addition to the 50- $\Omega$  OCT setting, Stratix II devices have a 25- $\Omega$  OCT setting that you can use to improve the signal quality in a Class II terminated transmission line. Figure 1–16 shows the Class II termination scheme using ODT when the 25- $\Omega$  OCT on the FPGA is turned on.

Figure 1–16. Class II Termination Using ODT with 25- $\Omega$  OCT

Figure 1–17 shows the simulation and measurement of the signal at the DDR2 SDRAM DIMM (receiver) with a drive strength setting of 25- $\Omega$  OCT in the FPGA.

Figure 1-17. HyperLynx Simulation and Measurement, FPGA Writing to Memory

Table 1–6 shows the data for the signal at the DDR2 SDRAM DIMM of a Class II termination with a memory-side series resistor. The FPGA is writing to the memory with 25- $\Omega$  OCT.

Table 1–6. Simulation and Board Measurement Results for 25- $\Omega$  OCT and 16-mA Drive Strength Settings (Part 1 of 2) (Note 1)

|                                 | Eye Width (ns) | Eye Height (V) | Overshoot (V) | Undershoot (V) |  |  |

|---------------------------------|----------------|----------------|---------------|----------------|--|--|

| 25-Ω OCT Drive Strength Setting |                |                |               |                |  |  |

| Simulation                      | 1.70           | 0.81           | N/A           | N/A            |  |  |

Table 1–6. Simulation and Board Measurement Results for 25- $\Omega$  OCT and 16-mA Drive Strength Settings (Part 2 of 2) (Note 1)

|                   | Eye Width (ns) | Eye Height (V) | Overshoot (V) | Undershoot (V) |

|-------------------|----------------|----------------|---------------|----------------|

| Board Measurement | 1.47           | 0.51           | N/A           | N/A            |

#### Note to Table 1-6:

(1) N/A is not applicable.

This type of termination scheme is only used for bidirectional signals, such as data (DQ), data strobe (DQS), data mask (DM), and memory clocks (CK) found in DRAMs.

### **Class II External Parallel Termination**

The double parallel (Class II) termination scheme is described in JEDEC standards JESD8-6 for HSTL I/O, JESD8-9b for SSTL-2 I/O, and JESD8-15a for SSTL-18 I/O. When the FPGA (driver) is writing to the DDR2 SDRAM DIMM (receiver), the transmission line is terminated at the DDR2 SDRAM DIMM. Similarly, when the FPGA is reading from the DDR2 SDRAM DIMM, the DDR2 SDRAM DIMM is now the driver and the transmission line is terminated at the FPGA (receiver). This type of termination scheme is typically used for bidirectional signals, such as data (DQ) and data strobe (DQS) signal found in DRAMs.

### **FPGA Writing to Memory**

Figure 1–18 shows the Class II termination scheme when the FPGA is writing to the memory. The benefit of using Class II termination is that when either driver is driving the transmission line, it sees a matched transmission line because of the termination resistor at the receiver-end, thereby reducing ringing and reflection.

Figure 1–18. Class-II Termination Scheme with Memory-Side Series Resistor

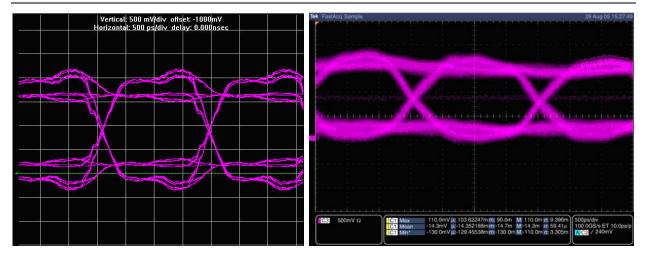

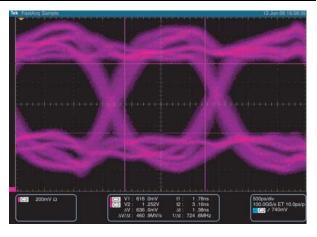

Figure 1–19 and Figure 1–20 show the simulation and measurement result of a write to the DDR2 SDRAM DIMM. The system uses Class II termination with a source-series resistor measured at the DIMM with a drive strength setting of 16 mA.

Figure 1–19. HyperLynx Simulation, FPGA Writing to Memory

The simulation shows a clean signal with a good eye opening, but there is slight overand undershoot of the 1.8-V signal specified by DDR2 SDRAM. The over- and undershoot can be attributed to either overdriving the transmission line using a higher than required drive strength setting on the driver or the over-termination on the receiver side by using an external resistor value that is higher than the characteristic impedance of the transmission line. As long as the over- and undershoot do not exceed the absolute maximum rating specification listed in the memory vendor's DDR2 SDRAM data sheet, it does not result in any reliability issues. The simulation results are then correlated with actual board level measurements. Figure 1–20 shows the measurement obtained from the Stratix II Memory Board 2. The FPGA is using a 16 mA drive strength to drive the DDR2 SDRAM DIMM on a Class II termination transmission line.

Figure 1-20. Board Measurement, FPGA Writing to Memory

Table 1–7 summarizes the comparison between the simulation and the board measurement of the signal seen at the DDR2 SDRAM DIMM.

|            | Eye Width (ns) | Eye Height (V) | Overshoot (V) | Undershoot (V) |

|------------|----------------|----------------|---------------|----------------|

| Simulation | 1.65           | 1.28           | 0.16          | 0.14           |

Table 1–7. Signal Comparison When the FPGA is Writing to the Memory (Note 1)

1.35

# Board Measurement Notes to Table 1–7:

- (1) The drive strength on the FPGA is set to 16 mA.

- (2) The eye width is measured from V<sub>REF</sub> ± 125 mV where V<sub>IH</sub> and V<sub>IL</sub> are determined per the JEDEC specification for SSTL-18.

0.83

0.16

A closer inspection of the simulation shows an ideal duty cycle of 50%–50%, while the board measurement shows that the duty cycle is non-ideal, around 53%–47%, resulting in the difference between the simulation and measured eye width. In addition, the board measurement is conducted on a 72-bit memory interface, but the simulation is performed on a single I/O.

0.18

### **FPGA Reading from Memory**

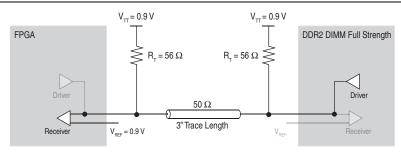

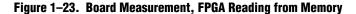

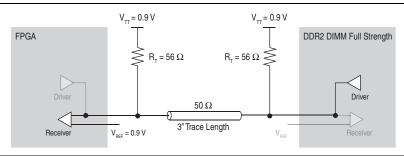

Figure 1–21 shows the Class II termination scheme when the FPGA is reading from memory. When the DDR2 SDRAM DIMM is driving the transmission line, the ringing and reflection is minimal because of the matched FPGA-side termination pull-up resistor with the transmission line.

Figure 1–21. Class II Termination Scheme with Memory-Side Series Resistor

Figure 1–22 and Figure 1–23 show the simulation and measurement, respectively, of the signal at the FPGA side with the full drive strength setting on the DDR2 SDRAM DIMM. The simulation uses a Class II termination scheme with a source-series resistor transmission line. The FPGA is reading from the memory with a full drive strength setting on the DIMM.

Figure 1-22. HyperLynx Simulation, FPGA Reading from Memory

Table 1–8 summarizes the comparison between the simulation and board measurements of the signal seen by the FPGA when the FPGA is reading from memory (driver).

Table 1–8. Signal Comparison, FPGA is Reading from Memory (Note 1), (2)

|                   | Eye Width (ns) | Eye Height (V) | Overshoot (V) | Undershoot (V) |

|-------------------|----------------|----------------|---------------|----------------|

| Simulation        | 1.73           | 0.76           | N/A           | N/A            |

| Board Measurement | 1.28           | 0.43           | N/A           | N/A            |

#### Note to Table 1-8:

- (1) The drive strength on the DDR2 SDRAM DIMM is set to full strength.

- (2) N/A is not applicable.

Both simulation and measurement show a clean signal and a good eye opening without any over- and undershoot. However, the eye height when the FPGA is reading from the memory is smaller compared to the eye height when the FPGA is writing to the memory. The reduction in eye height is attributed to the voltage drop on the series resistor present on the DIMM. With the drive strength setting on the memory already set to full, you cannot increase the memory drive strength to improve the eye height. One option is to remove the series resistor on the DIMM when the FPGA is reading from memory (refer to the section "Component Versus DIMM" on page 1–53). Another option is to remove the external parallel resistor near the memory so that the memory driver sees less loading. For a DIMM configuration, the latter option is a better choice because the series resistors are part of the DIMM and you can easily turn on the ODT feature to use as the termination resistor when the FPGA is writing to the memory and turn off when the FPGA is reading from memory.

The results for the Class II termination scheme demonstrate that the scheme is ideal for bidirectional signals such as data strobe and data for DDR2 SDRAM memory. Terminations at the receiver eliminate reflections back to the driver and suppress any ringing at the receiver.

### Class I External Parallel Termination

The single parallel (Class I) termination scheme refers to when the termination is located near the receiver side. Typically, this scheme is used for terminating unidirectional signals (such as clocks, address, and command signals) for DDR2 SDRAM.

However, because of board constraints, this form of termination scheme is sometimes used in bidirectional signals, such as data (DQ) and data strobe (DQS) signals. For bidirectional signals, you can place the termination on either the memory or the FPGA side. This section focuses only on the Class I termination scheme with memory-side termination. The memory-side termination ensures impedance matching when the signal reaches the receiver of the memory. However, when the FPGA is reading from the memory, there is no termination on the FPGA side, resulting in impedance mismatch. This section describes the signal quality of this termination scheme.

### **FPGA Writing to Memory**

When the FPGA is writing to the memory (Figure 1–24), the transmission line is parallel-terminated at the memory side, resulting in minimal reflection on the receiver side because of the matched impedance seen by the transmission line. The benefit of this termination scheme is that only one external resistor is required. Alternatively, you can implement this termination scheme using an ODT resistor instead of an external resistor.

Refer to the section "Class I Termination Using ODT" on page 1–29 for more information about how an ODT resistor compares to an external termination resistor.

Figure 1-24. Class I Termination Scheme with Memory-Side Series Resistor

Figure 1–25 shows the simulation and measurement of the signal at the memory (DDR2 SDRAM DIMM) of Class I termination with a memory-side resistor. The FPGA writes to the memory with a 16 mA drive strength setting.

Figure 1-25. HyperLynx Simulation and Board Measurement, FPGA Writing to Memory

Table 1–9 summarizes the comparison of the signal at the DDR2 SDRAM DIMM of a Class I and Class II termination scheme using external resistors with memory-side series resistors. The FPGA (driver) writes to the memory (receiver).

Table 1–9. Signal Comparison When the FPGA is Writing to Memory (Note 1)

|                                                             | Eye Width (ns) | Eye Height (V) | Overshoot (V) | Undershoot (V) |  |

|-------------------------------------------------------------|----------------|----------------|---------------|----------------|--|

| Class I Termination Scheme With External Parallel Resistor  |                |                |               |                |  |

| Simulation                                                  | 1.69           | 1.51           | 0.34          | 0.29           |  |

| Board Measurement                                           | 1.25           | 1.08           | 0.41          | 0.34           |  |

| Class II Termination Scheme With External Parallel Resistor |                |                |               |                |  |

| Simulation                                                  | 1.65           | 1.28           | 0.16          | 0.14           |  |

| Board Measurement                                           | 1.35           | 0.83           | 0.16          | 0.18           |  |

#### Note to Table 1-9:

Table 1–9 shows the overall signal quality of a Class I termination scheme is comparable to the signal quality of a Class II termination scheme, except that the eye height of the Class I termination scheme is approximately 30% larger. The increase in eye height is due to the reduced loading "seen" by the driver, because the Class I termination scheme does not have an FPGA-side parallel termination resistor. However, increased eye height comes with a price: a 50% increase in the over- and undershoot of the signal using Class I versus Class II termination scheme. You can decrease the FPGA drive strength to compensate for the decreased loading seen by the driver to decrease the over- and undershoot.

Refer to the section "Drive Strength" on page 1–51 for more information about how drive strength affects the signal quality.

### **FPGA Reading from Memory**

As described in the section "FPGA Writing to Memory" on page 1–26, in Class I termination, the termination is located near the receiver. However, if you use this termination scheme to terminate a bidirectional signal, the receiver can also be the driver. For example, in DDR2 SDRAM, the data signals are both receiver *and* driver.

Figure 1–26 shows a Class I termination scheme with a memory-side resistor. The FPGA reads from the memory.

Figure 1–26. Class I Termination Scheme with Memory-Side Series Resistor

<sup>(1)</sup> The drive strength on the FPGA is set to 16 mA.

When the FPGA reads from the memory (Figure 1–26), the transmission line is not terminated at the FPGA, resulting in an impedance mismatch, which then results in over- and undershoot. Figure 1–27 shows the simulation and measurement of the signal at the FPGA side (receiver) of a Class I termination. The FPGA reads from the memory with a full drive strength setting on the DDR2 SDRAM DIMM.

Figure 1–27. HyperLynx Simulation and Board Measurement, FPGA Reading from Memory

Table 1–10 summarizes the comparison of the signal "seen" at the FPGA of a Class I and Class II termination scheme using an external resistor with a memory-side series resistor. The FPGA (receiver) reads from the memory (driver).

|                                                             | Eye Width (ns) | Eye Height (V) | Overshoot (V) | Undershoot (V) |  |

|-------------------------------------------------------------|----------------|----------------|---------------|----------------|--|

| Class I Termination Scheme with External Parallel Resistor  |                |                |               |                |  |

| Simulation                                                  | 1.73           | 0.74           | 0.20          | 0.18           |  |

| Board Measurement                                           | 1.24           | 0.58           | 0.09          | 0.14           |  |

| Class II Termination Scheme with External Parallel Resistor |                |                |               |                |  |

| Simulation                                                  | 1.73           | 0.76           | N/A           | N/A            |  |

| Board Measurement                                           | 1.28           | 0.43           | N/A           | N/A            |  |

Table 1–10. Signal Comparison When the FPGA is Reading From Memory (Note 1), (2)

### Note to Table 1-10:

- (1) The drive strength on the DDR2 SDRAM DIMM is set to full strength.

- (2) N/A is not applicable.

When the FPGA reads from the memory using the Class I scheme, the signal quality is comparable to that of the Class II scheme, in terms of the eye height and width. Table 1–10 shows the lack of termination at the receiver (FPGA) results in impedance mismatch, causing reflection and ringing that is not visible in the Class II termination scheme. As such, Altera recommends using the Class I termination scheme for unidirectional signals (such as command and address signals), between the FPGA and the memory.

## **Class I Termination Using ODT**

Presently, ODT is becoming a common feature in memory, including SDRAMs, graphics DRAMs, and SRAMs. ODT helps reduce board termination cost and simplify board routing. This section describes the ODT feature of DDR2 SDRAM and the signal quality when the ODT feature is used.

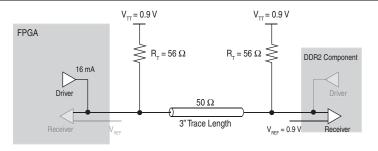

### **FPGA Writing to Memory**

DDR2 SDRAM has built-in ODT that eliminates the need for external termination resistors. To use the ODT feature of the memory, you must configure the memory to turn on the ODT feature during memory initialization. For DDR2 SDRAM, set the ODT feature by programming the extended mode register. In addition to programming the extended mode register during initialization of the DDR2 SDRAM, an ODT input pin on the DDR2 SDRAM must be driven high to activate the ODT.

Refer to the respective memory data sheet for additional information about setting the ODT feature and the timing requirements for driving the ODT pin in DDR2 SDRAM.

The ODT feature in DDR2 SDRAM is controlled dynamically—it is turned on while the FPGA is writing to the memory and turned off while the FPGA is reading from the memory. The ODT feature in DDR2 SDRAM has three settings:  $50\Omega$ ,  $75\Omega$ , and  $150\Omega$ . If there are no external parallel termination resistors and the ODT feature is turned on, the termination scheme resembles the Class I termination described in "Class I External Parallel Termination" on page 1–25.

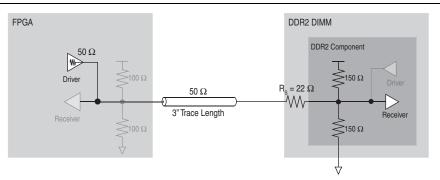

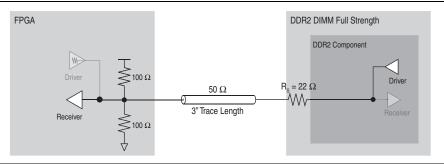

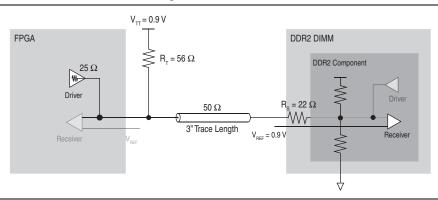

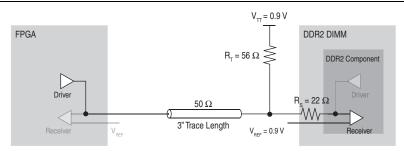

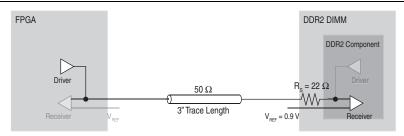

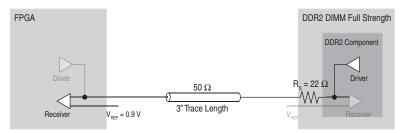

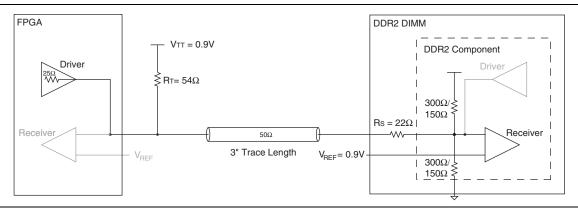

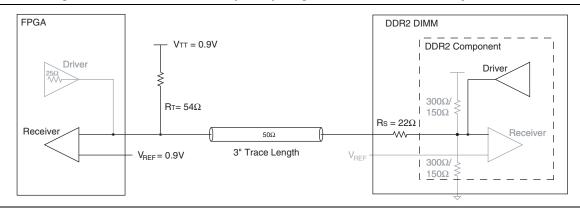

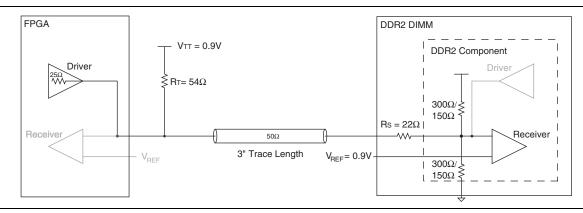

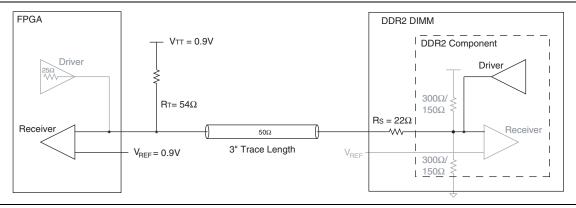

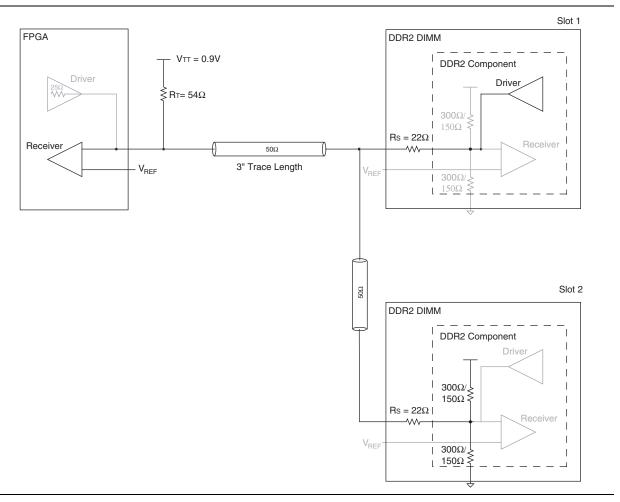

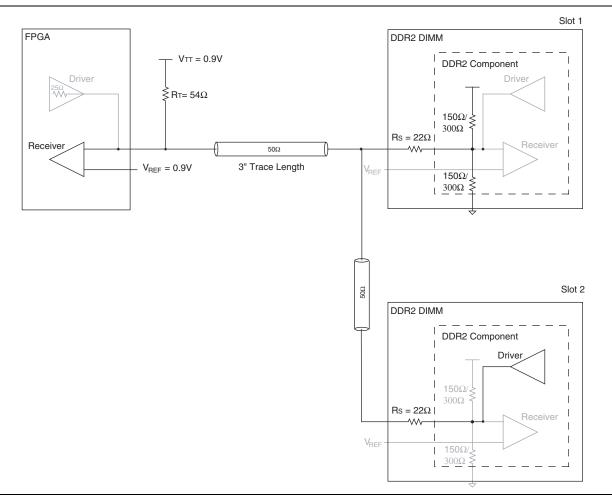

Figure 1–28 shows the termination scheme when the ODT on the DDR2 SDRAM is turned on.

FPGA

DDR2 DIMM

DDR2 Component

DDR2 Component

To Ω

R<sub>S</sub> = 22 Ω

Driver

V<sub>REF</sub> = 0.9 V

Receiver

Figure 1-28. Class I Termination Scheme Using ODT

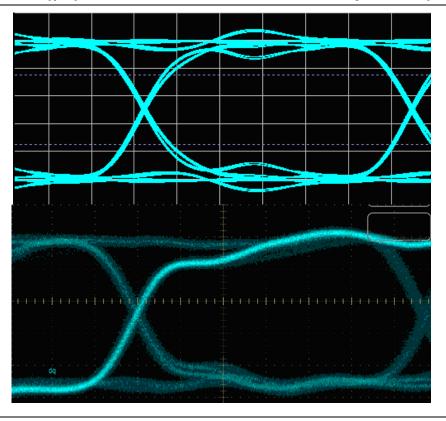

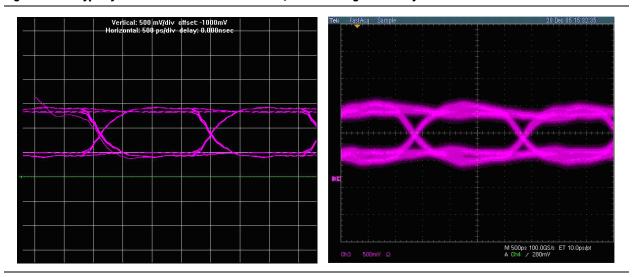

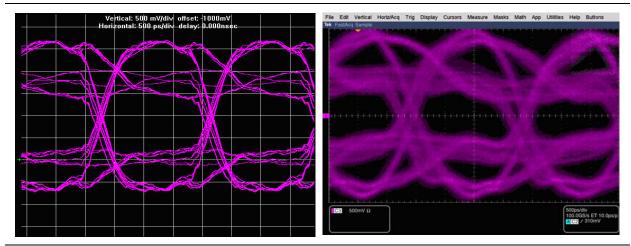

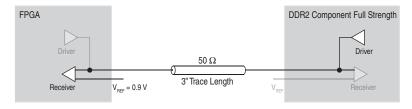

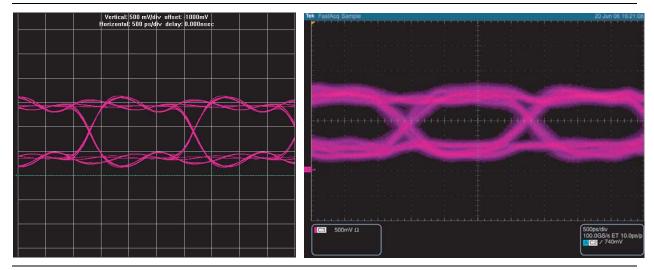

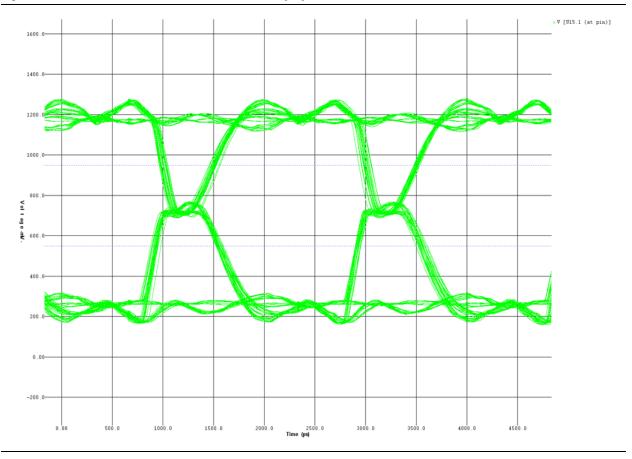

Figure 1–29 shows the simulation and measurement of the signal visible at the memory (receiver) using 50  $\Omega$  ODT with a memory-side series resistor transmission line. The FPGA writes to the memory with a 16 mA drive strength setting.

Figure 1–29. Simulation and Board Measurement, FPGA Writing to Memory

Table 1–11 summarizes the comparisons of the signal seen the DDR2 SDRAM DIMM of a Class I termination scheme using an external resistor and a Class I termination scheme using ODT with a memory-side series resistor. The FPGA (driver) writes to the memory (receiver).

Table 1–11. Signal Comparison When the FPGA is Writing to Memory (Note 1), (2)

|                                                            | Eye Width (ns) | Eye Height (V) | Overshoot (V) | Undershoot (V) |  |

|------------------------------------------------------------|----------------|----------------|---------------|----------------|--|

| Class I Termination Scheme with ODT                        |                |                |               |                |  |

| Simulation                                                 | 1.63           | 0.84           | N/A           | 0.12           |  |

| Board Measurement                                          | 1.51           | 0.76           | 0.05          | 0.15           |  |

| Class I Termination Scheme with External Parallel Resistor |                |                |               |                |  |

| Simulation                                                 | 1.69           | 1.51           | 0.34          | 0.29           |  |

| Board Measurement                                          | 1.25           | 1.08           | 0.41          | 0.34           |  |

#### Note to Table 1-11:

- (1) The drive strength on the FPGA is set to 16 mA.

- (2) N/A is not applicable.

When the ODT feature is enabled in the DDR2 SDRAM, the eye width is improved. There is some degradation to the eye height, but it is not significant. When ODT is enabled, the most significant improvement in signal quality is the reduction of the over- and undershoot, which helps mitigate any potential reliability issues on the memory devices.

Using memory ODT also eliminates the need for external resistors, which reduces board cost and simplifies board routing, allowing you to shrink your boards. Therefore, Altera recommends using the ODT feature on the DDR2 SDRAM memory.

### **FPGA Reading from Memory**

Altera's Arria GX, Arria II GX, Cyclone series, and Stratix II series of devices are not equipped with ODT. When the DDR2 SDRAM ODT feature is turned off when the FPGA is reading from the memory, the termination scheme resembles the no-parallel termination scheme illustrated by Figure 1–32 on page 1–33.

### **No-Parallel Termination**

The no-parallel termination scheme is described in the JEDEC standards JESD8-6 for HSTL I/O, JESD8-9b for SSTL-2 I/O, and JESD8-15a for SSTL-18 I/O. Designers who attempt series-only termination schemes such as this often do so to eliminate the need for a  $V_{\rm TT}$  power supply.

This is typically not recommended for any signals between an FPGA and DDR2 interface; however, information about this topic is included here as a reference point to clarify the challenges that may occur if you attempt to avoid parallel termination entirely.

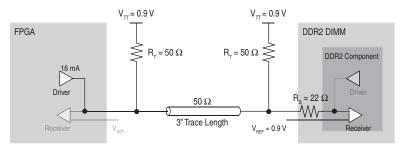

### **FPGA Writing to Memory**

Figure 1–30 shows a no-parallel termination transmission line of the FPGA driving the memory. When the FPGA is driving the transmission line, the signals at the memory-side (DDR2 SDRAM DIMM) may suffer from signal degradation (for example, degradation in rise and fall time). This is due to impedance mismatch, because there is no parallel termination at the memory-side. Also, because of factors such as trace length and drive strength, the degradation seen at the receiver-end might be sufficient to result in a system failure. To understand the effects of each termination scheme on a system, perform system-level simulations before and after the board is designed.

Figure 1-30. No-Parallel Termination Scheme

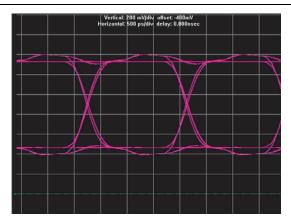

Figure 1–31 shows a HyperLynx simulation and measurement of the FPGA writing to the memory at 533 MHz with a no-parallel termination scheme using a 16 mA drive strength option. The measurement point is on the DDR2 SDRAM DIMM.

Figure 1–31. HyperLynx Simulation and Board Measurement, FPGA Writing to Memory

The simulated and measured signal shows that there is sufficient eye opening but also significant over- and undershoot of the 1.8-V signal specified by the DDR2 SDRAM. From the simulation and measurement, the overshoot is approximately 1 V higher than 1.8 V, and undershoot is approximately 0.8 V below ground. This over- and undershoot might result in a reliability issue, because it has exceeded the absolute maximum rating specification listed in the memory vendors' DDR2 SDRAM data sheet.

Table 1–12 summarizes the comparison of the signal visible at the DDR2 SDRAM DIMM of a no-parallel and a Class II termination scheme when the FPGA writes to the DDR2 SDRAM DIMM.

Table 1–12. Signal Comparison When the FPGA is Writing to Memory (Note 1)

|                                | Eye Width (ns)                                              | Eye Height (V) | Overshoot (V) | Undershoot (V) |  |  |  |  |

|--------------------------------|-------------------------------------------------------------|----------------|---------------|----------------|--|--|--|--|

| No-Parallel Termination Scheme |                                                             |                |               |                |  |  |  |  |

| Simulation                     | 1.66                                                        | 1.10           | 0.90          | 0.80           |  |  |  |  |

| Board Measurement              | 1.25                                                        | 0.60           | 1.10          | 1.08           |  |  |  |  |

| Class II Termination           | Class II Termination Scheme With External Parallel Resistor |                |               |                |  |  |  |  |

| Simulation                     | 1.65                                                        | 1.28           | 0.16          | 0.14           |  |  |  |  |

| Board Measurement              | 1.35                                                        | 0.83           | 0.16          | 0.18           |  |  |  |  |

Note to Table 1-12:

(1) The drive strength on the FPGA is set to Class II 16 mA.

Board Termination for DDR2 SDRAM

Although the appearance of the signal in a no-parallel termination scheme is not clean, when you take the key parameters into consideration, the eye width and height is comparable to that of a Class II termination scheme. The major disadvantage of using a no-parallel termination scheme is the over- and undershoot. There is no termination on the receiver, so there is an impedance mismatch when the signal arrives at the receiver, resulting in ringing and reflection. In addition, the 16-mA drive strength setting on the FPGA also results in overdriving the transmission line, causing the over- and undershoot. By reducing the drive strength setting, the over- and undershoot decreases and improves the signal quality "seen" by the receiver.

For more information about how drive strength affects the signal quality, refer to "Drive Strength" on page 1–51.

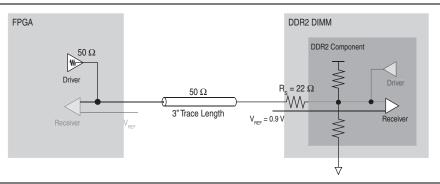

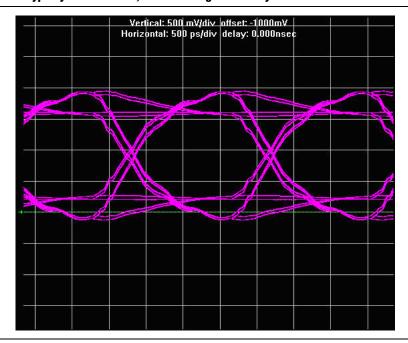

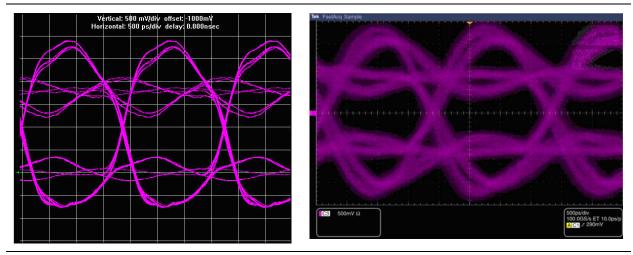

### **FPGA Reading from Memory**

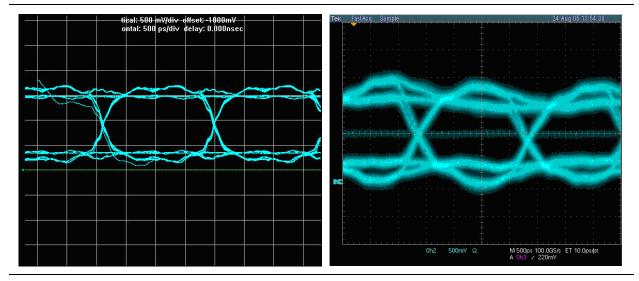

In a no-parallel termination scheme (Figure 1–32), when the memory is driving the transmission line, the resistor,  $R_S$  acts as a source termination resistor. The DDR2 SDRAM driver has two drive strength settings:

- Full strength, in which the output impedance is approximately  $18\Omega$

- **Reduced strength, in which the output impedance is approximately**  $40\Omega$

When the DDR2 SDRAM DIMM drives the transmission line, the combination of the  $22-\Omega$  source-series resistor and the driver impedance should match that of the characteristic impedance of the transmission line. As such, there is less over- and undershoot of the signal visible at the receiver (FPGA).

Figure 1–32. No-Parallel Termination Scheme, FPGA Reading from Memory

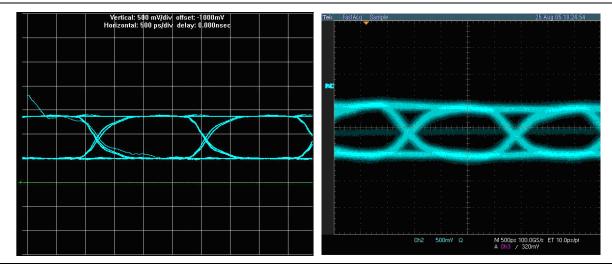

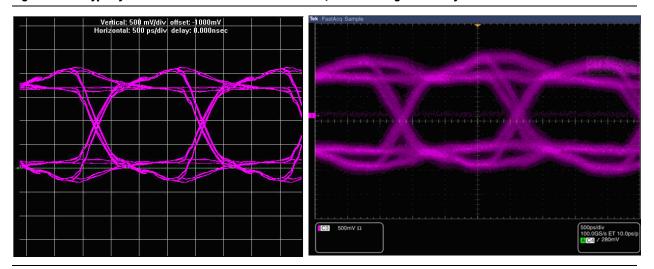

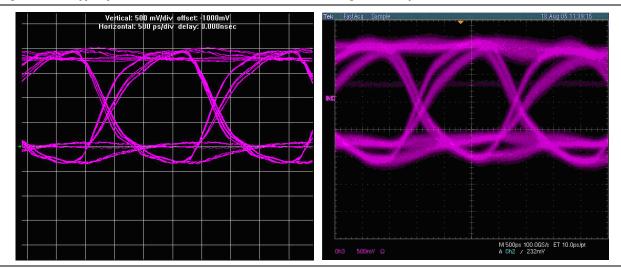

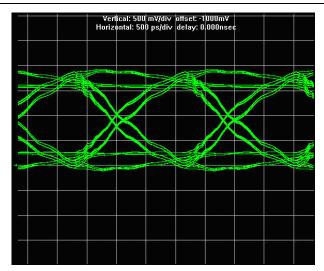

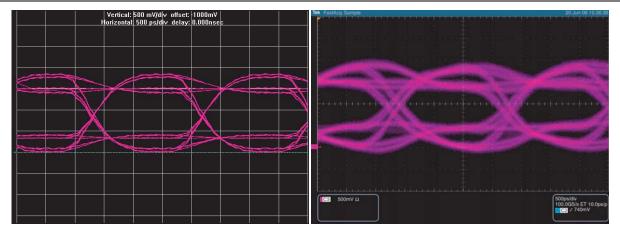

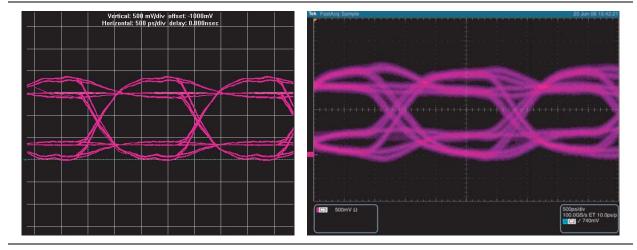

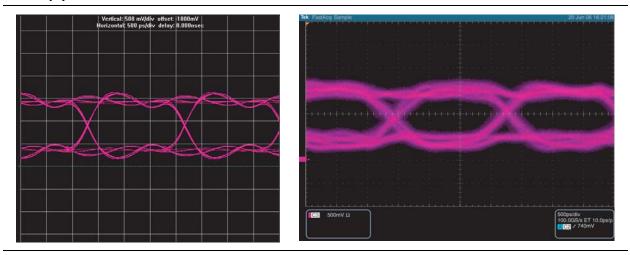

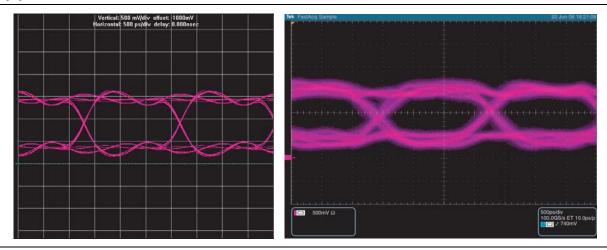

Figure 1–33 shows the simulation and measurement of the signal visible at the FPGA (receiver) when the memory is driving the no-parallel termination transmission line with a memory-side series resistor.

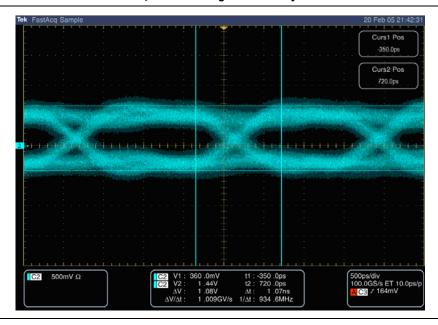

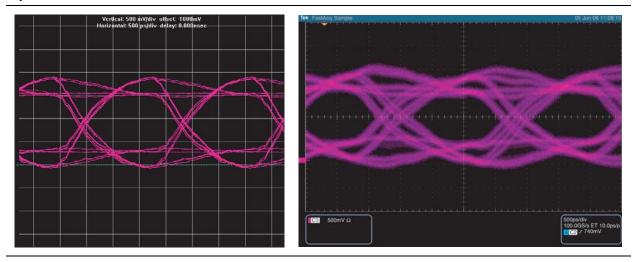

Vertical: \$00 mV/div offset: 1000mV

Horizontal: \$00 ps/div delay: 0.000n sec

Ch2 500mV Ω M50ge: 1000g8 £T 10 0gs/div A Ch1 / 224mV

Figure 1-33. HyperLynx Simulation and Board Measurement, FPGA Reading from Memory

Table 1–13 summarizes the comparison of the signal seen on the FPGA with a no-parallel and a Class II termination scheme when the FPGA is reading from memory.

|                                                             | Eye Width (ns) | Eye Height (V) | Overshoot (V) | Undershoot (V) |  |  |  |  |

|-------------------------------------------------------------|----------------|----------------|---------------|----------------|--|--|--|--|

| No-Parallel Termination Scheme                              |                |                |               |                |  |  |  |  |

| Simulation                                                  | 1.82           | 1.57           | 0.51          | 0.51           |  |  |  |  |

| Board Measurement                                           | 1.62           | 1.29           | 0.28          | 0.37           |  |  |  |  |

| Class II Termination Scheme with External Parallel Resistor |                |                |               |                |  |  |  |  |

| Simulation                                                  | 1.73           | 0.76           | N/A           | N/A            |  |  |  |  |

| Board Measurement                                           | 1.28           | 0.43           | N/A           | N/A            |  |  |  |  |

Table 1-13. Signal Comparison, FPGA Reading From Memory (Note 1), (2)

#### Note to Table 1-13:

- (1) The drive strength on the DDR2 SDRAM DIMM is set to full strength.

- (2) N/A is not applicable.

As in the section "FPGA Writing to Memory" on page 1–31, the eye width and height of the signal in a no-parallel termination scheme is comparable to a Class II termination scheme, but the disadvantage is the over- and undershoot. There is over- and undershoot because of the lack of termination on the transmission line, but the magnitude of the over- and undershoot is not as severe when compared to that described in "FPGA Writing to Memory" on page 1–31. This is attributed to the presence of the series resistor at the source (memory side), which dampens any reflection coming back to the driver and further reduces the effect of the reflection on the FPGA side.

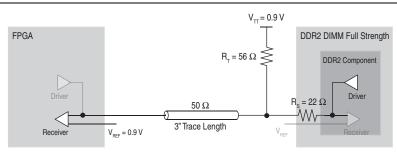

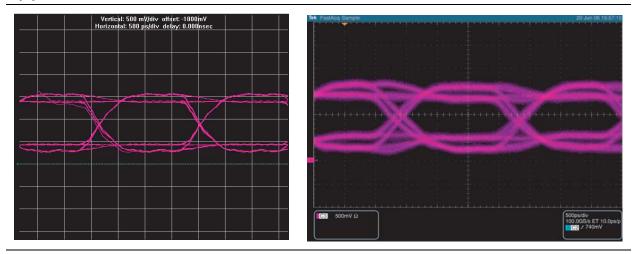

When the memory-side series resistor is removed (Figure 1–34), the memory driver impedance no longer matches the transmission line and there is no series resistor at the driver to dampen the reflection coming back from the unterminated FPGA side.

Figure 1-34. No-Parallel Termination Scheme, FPGA REading from Memory

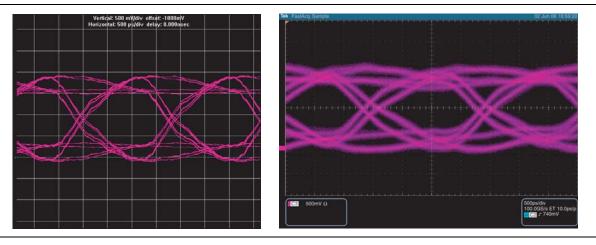

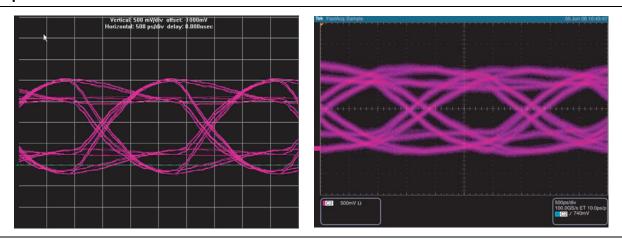

Figure 1–35 shows the simulation and measurement of the signal at the FPGA side in a no-parallel termination scheme with the full drive strength setting on the memory.

Figure 1-35. HyperLynx Simulation and Measurement, FPGA Reading from Memory

Table 1–14 summarizes the difference between no-parallel termination with and without memory-side series resistor when the memory (driver) writes to the FPGA (receiver).

Table 1–14. No-Parallel Termination with and without Memory-Side Series Resistor (Note 1)

|                         | Eye Width (ns) | Eye Height (V) | Overshoot (V) | Undershoot (V) |

|-------------------------|----------------|----------------|---------------|----------------|

| Without Series Resistor |                |                |               |                |

| Simulation              | 1.81           | 0.85           | 1.11          | 0.77           |

| Board Measurement       | 1.51           | 0.92           | 0.96          | 0.99           |

| With Series Resistor    |                |                |               |                |

| Simulation              | 1.82           | 1.57           | 0.51          | 0.51           |

| Board Measurement       | 1.62           | 1.29           | 0.28          | 0.37           |

Note to Table 1-14:

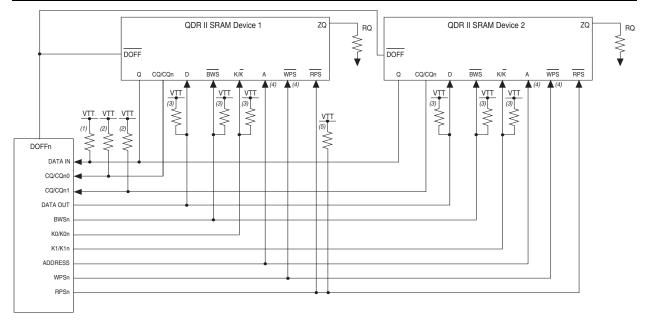

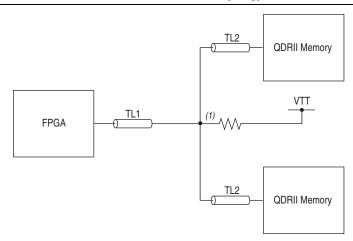

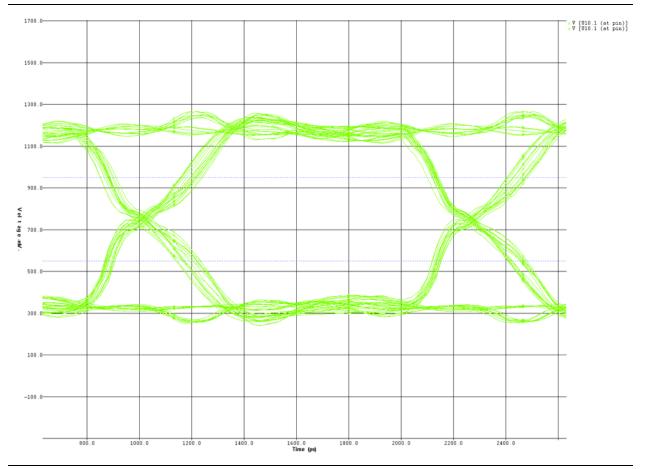

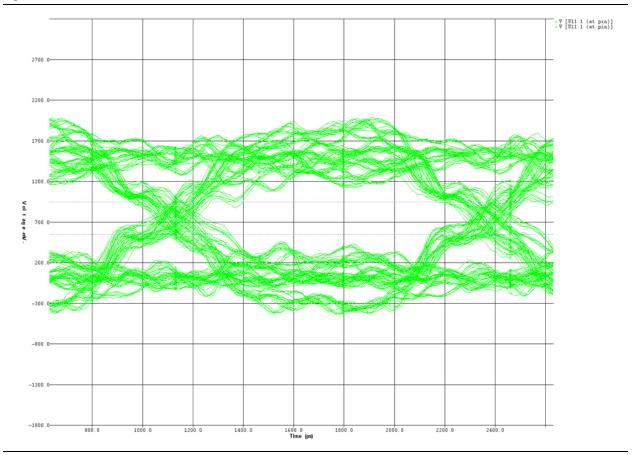

$<sup>(1) \</sup>quad \text{The drive strength on the memory is set to full drive strength}.$