16G044 16G044M

# Phase/Frequency Comparator 1 GHz Input Frequency

#### **FEATURES**

- Rising edge-triggered design

- Continuous duty cycle output response vs. input phase difference for  $\pi < \theta < \pi$

- Constant duty cycle output indicating direction of error for unequal frequency inputs

- · High reference frequency rejection

- Improved reference suppression compared with MC12040

- -122 dBc/Hz phase noise @ 1 KHz offset

- High speed, adjustable threshold comparator inputs for low level analog inputs

- AC coupled or ECL/10G PicoLogic™ input compatibility

- Available in C leaded or leadless chip carriers or in die form

- -55°C to +125°C operation (16G044M)

#### **APPLICATIONS**

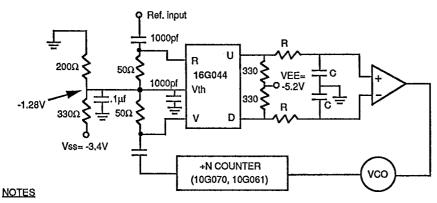

- Stable acquisition phase locked loops

- Frequency synthesizers (with 10G070 Variable Modulus Divider and 10G061 prog. counter)

- Frequency discriminators

- High speed PSK and FSK demodulators

- · High resolution time delay measurement

#### **FUNCTIONAL DESCRIPTION**

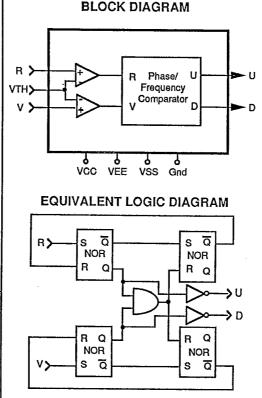

The 16G044/16G044M is a rising edge-triggered phase/frequency comparator with sensitive differential amplifier inputs capable of accepting input signals up to 1GHz in frequency. Functionally, it is similar in operation to the MC4044 or 11C44 although much faster and with much greater reference frequency rejection. When the R (Reference) and V (VCO) inputs are unequal in frequency and/or phase, the differential outputs U (Up) and D (Down) are pulse streams which when subtracted and integrated provide an error voltage for control of a VCO. This contrasts with an analog mixer or exclusive-OR based phase detector which does not produce explicit frequency error information. Use of the 16G044/16G044M in a PLL makes frequency acquisition more stable by comparison.

The 16G044/16G044M is fabricated using GigaBit's high volume, production proven GaAs MESFET process technology.

# 16G044/16G044M ORDERING INFORMATION

| Package                          |                        | G044<br>to 85°C)                    | 16G044M<br>(-55°C to +125°C) |                                        |  |  |

|----------------------------------|------------------------|-------------------------------------|------------------------------|----------------------------------------|--|--|

| Туре                             | 1GHz                   | 750 MHz                             | 1GHz                         | 750 MHz                                |  |  |

| 40-pin "C"<br>40-pin "L"<br>Dice | 16G044-2C<br>16G044-2L | 16G044-3C<br>16G044-3L<br>16G044-3X | 16G044M-2C<br>16G044M-2L     | 16G044M-3C<br>16G044M-3L<br>16G044M-3X |  |  |

T-45-17

# SigaBit Logic

# 16G044 16G044M

#### 16G044 Operation

Figure 1: 16G044 Operation

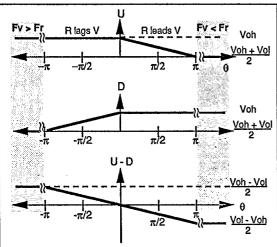

The operation of the 16G044 is best explained with reference to Figure 1 which plots the average value of U, D, and U - D versus the phase or frequency difference between the R and V inputs.

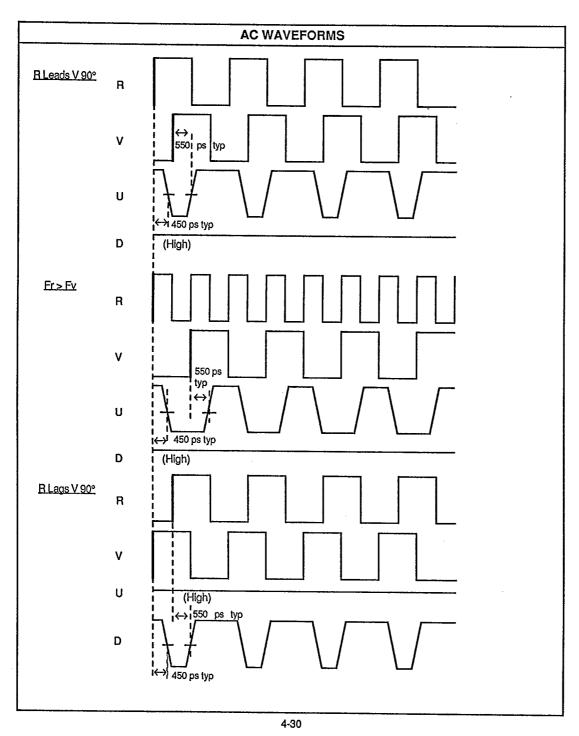

Four relationships between R and V are possible: R lags or leads V in phase and Fr is less than or greater than Fv.

#### 1. Rlags V in phase

When the R and V inputs are equal in frequency but R lags V in phase, the U output is pegged high (at VOH) and the D output pulses low with a duty cycle that is proportional to the phase difference between R and V, reaching a minimum of 50% for 180° phase difference. Therefore, the average value of D varies between VOH (0° phase difference) and (VOH + VOL)/2 (180° phase difference). The signal on D indicates that the VCO frequency should be decreased to bring the loop into lock.

#### 2. Fv > Fr

When the V input frequency exceeds that of the R input, the behavior of the 16G044 is the same as described in 1, above except that the D output duty cycle is constant at approximately 50%. The average value of D is constant at (VOH + VOL)/2 as shown in

Figure 1. As above, the signal on D indicates that the VCO frequency should be decreased to establish

#### 3. R Leads V in Phase

When the R and V inputs are equal in frequency but R leads V in phase, the D output is held high ( at VOH) and the U output pulses low with a duty cycle that is proportional to the phase angle between R and V, reaching a minimum of 50% for 180° phase difference. The average value of U varies between VOH (0° phase difference and (VOH + VOL)/2 (180° difference). The signal on U indicates that the VCO frequency should be increased to establish lock.

#### 4. <u>Fv < Fr</u>

When the V input frequency is less than the R input signal frequency, the 16G044 operates as described in 3, above except that the U output duty cycle does not vary, but is constant at approximately 50%. Therefore the average value of U is constant at (VOH + VOL)/2 as shown in Figure 1. Again, the signal on U provides information used to increase the VCO frequency to establish loop lock.

Note that when R and V are equal in frequency and phase, i.e. when the loop is locked, the average value of U - D is zero, meaning that the action of the 16G044 is to maintain the loop in lock status.

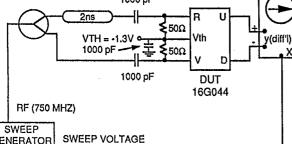

Figure 2: 16G044 Transfer Characteristic at 750 MHz (see Fig. 4) Avg (U - D) 0.6 slope = K 100 ps slope ≥ K/<sub>′</sub> typ.@ 750 MHz θ (rads)  $-\pi - 3\pi/4 - \pi/2$ π/2  $3\pi/4$ - 0.2 - 0.4 - 0.6 -0.8

T-45-17 16G044 16G044M

# 16G044 Operation (continued)

Figure 2 plots the transfer characteristic of the 16G044 with equal frequency R and V inputs at 750 MHz. The slope of the curve drawn as the solid straight line is the comparator gain constant, K, and is typically 600 mV/ $\pi$  radians or 0.19 V/rad. The reduction in K in the vicinity of zero phase difference is of particular interest to PLL system designers. The 16G044 is designed to minimize this decrease In gain to ≥ K/4 and to limit the range of flattening to less than 100ps or 27° (± 13.5°) of phase at 750

Figure 3 describes the logical I/O characteristics of the 16G044 which is useful for purposes of testing the device at low speed.

#### Figure 3: 16G044 State Table

|              | Inputs |     | Out         | puts        | Notes |  |

|--------------|--------|-----|-------------|-------------|-------|--|

|              | R      | ٧   | ٦           | D           | Moras |  |

| R leads V    | ×5°    | ٥٥١ | 1<br>0<br>1 | 1 1         | A     |  |

| <br>R lags V | ٥٥٥    | ۰۲× | 1 1         | 1<br>0<br>1 | A     |  |

Note A: This table assumes that the 0, 0 input state shown was preceded at some time with a falling edge (1->0) transition in both R and V.

#### **PIN DESCRIPTIONS**

|     |                                                                                               | ,   |                   |

|-----|-----------------------------------------------------------------------------------------------|-----|-------------------|

| R   | Reference signal input                                                                        | vcc | + 5.0V supply pin |

| V   | VCO signal input                                                                              | Gnd | Ground connection |

| υ   | The "Up" (R leads V) output                                                                   | vss | - 3.4V supply pin |

| D   | The "Down" (R lags V) output                                                                  | VEE | - 5.2V supply pin |

| VTH | Threshold voltage input for the input comparators. Must be in the range - 1.8V ≤ Vth ≤ - 0.8V |     |                   |

#### 16G044 Application in a Simple Phase Locked Loop

1. The transfer characteristic of the simple loop filter shown is 1/(1 + sT) where T = RC. Typically R should be chosen to be >1KΩ. The connections to the op-amp assume a negative VCO gain constant. These connections should be reversed if a VCO with a positive transfer characteristic is used.

T-45-17 16G044 16G044M

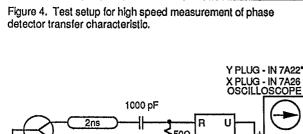

This test setup creates a delay line frequency discriminator which enables accurate linearity measurements of the phase detector. The resulting discriminator has zero output voltage at 500MHz and 1 GHz.

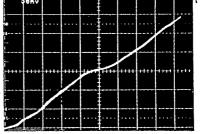

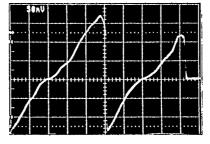

# Figure 4 Oscillographs (0 dBm Input)

(Y = 250 mV/div., X = 250 to 750 MHz)

(Y = 250 mV/div., X = 300 to 1300 MHz)

#### **ABSOLUTE MAXIMUM RATINGS**

contains built in low pass filter.

(Beyond which useful life may be impaired) (Notes 1, 4)

| SYMBOL | PARAMETER                                                                | ABSOLUTE MAXIMUM RATINGS | NOTES |

|--------|--------------------------------------------------------------------------|--------------------------|-------|

| TSTOR  | Storage Temperature                                                      | -65 °C to + 150 °C       |       |

| TJ     | Junction Temperature                                                     | - 55 °C to + 150 °C      |       |

| TÇ     | Case Temperature Under Bias                                              | - 55 °C to + 125 °C      | 2     |

| VCC    | Supply Voltage                                                           | · 0V to + 7.0V           |       |

| VSS    | Supply Voltage                                                           | - 4.0 V to + 0.5 V       |       |

| VEE    | Supply Voltage                                                           | - 6.0 V to VSS + 0.5 V   |       |

| VIN    | Voltage Applied to Any Input; Continuous<br>VSS = - 3.4 V, VEE = - 5.2 V | - 4.0 V to + 0.5 V       |       |

| IIN    | Current Into Any Input; Continuous                                       | - 0.5 mA to 1.0 mA       |       |

| VOUT   | Voltage Applied to Any Output                                            | -4.0V to +0.5 V          | 3     |

| IOUT   | Current From Any Output; Continuous                                      | -40 mA                   |       |

| PD     | Power Dissipation Per Output<br>POUT = (-VOUT) x IOUT                    | 50 mW                    |       |

GENERATOR HP 8350

- 1. All voltages specified relative to Gnd. Positive current is defined as current into the device.

- 2. TC is measured at case top.

- 3. Subject to IOUT and PD limitations.

- 4. Power supply sequencing is not necessary. However, sustained (>5 secs.) application of VSS in the absence of VEE could result in excessive power dissipation and damage to the device,

16G044 16G044M

| RECOMMENDED OPERATING CONDITIONS |                                                                                                       |                      |                                 |                        |                                                |       |  |

|----------------------------------|-------------------------------------------------------------------------------------------------------|----------------------|---------------------------------|------------------------|------------------------------------------------|-------|--|

| SYMBOL                           | PARAMETER                                                                                             | MIN                  | NOM                             | MAX                    | UNITS                                          | NOTES |  |

| TC<br>Gnd<br>VCC<br>VSS<br>VEE   | Case Operating Temperature<br>Ground connection<br>Supply Voltage<br>Supply Voltage<br>Supply Voltage | 4.75<br>-3.5<br>-5.5 | +25<br>0<br>5.0<br>-3.4<br>-5.2 | 5.25<br>- 3.3<br>- 5.1 | \<br>\<br>\<br>\<br>\<br>\<br>\<br>\<br>\<br>\ | 1     |  |

Notes:

1. TC measured at case top. User attention to device thermal management is recommended. See GigaBit Application Note 3 for a detailed treatment of thermal management considerations.

# DC CHARACTERISTICS (1,2)

VCC = 4.75V to 5.25V, VSS = - 3.3V to - 3.5V, VEE = - 5.1V to - 5.5V

|                                                                   |                                                                                                                                                                                                                  | (0                                         | 16G044<br>°C to 85°                             |                                 |                                               | 16G044M<br>(-55℃ to +125℃)                      |     |                                                |                  |

|-------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|-------------------------------------------------|---------------------------------|-----------------------------------------------|-------------------------------------------------|-----|------------------------------------------------|------------------|

| SYMBOL                                                            | PARAMETER                                                                                                                                                                                                        | MIN                                        | TYP                                             | MAX                             | MIN                                           | TYP                                             | MAX | UNITS                                          | NOTES            |

| CMR<br>VIH<br>VIL<br>IIN<br>VOH<br>VOL<br>ICC<br>ISS<br>IEE<br>PD | Input common mode range Input voltage high Input voltage low Input current Output voltage high Output voltage low Output high current VCC supply current VSS supply current VEE supply current Power dissipation | -1.8<br>-1.0<br>VTT<br>-300<br>-0.8<br>VSS | - 0.6<br>- 2.6<br>- 25<br>45<br>75<br>50<br>750 | - 1.8<br>-20<br>70<br>120<br>80 | - 1.8<br>- 0.8<br>VTT<br>-300<br>- 1.2<br>VSS | - 0.6<br>- 2.6<br>- 25<br>45<br>75<br>50<br>750 |     | V<br>V<br>V<br>µA<br>V<br>WA<br>MA<br>MA<br>MA | 3<br>4<br>4<br>5 |

Notes:

- 1. These characteristics are applicable from DC to  $\,\sim 500$  MHz.

- 2. VTH = 1.3V

- 3. Vin = -1.0V to -1.6V

- 4. Outputs terminated  $100\Omega$  to VTT = -2.0V.

- IOH is the available output current at VOH = 0.8V.

- 6. At nominal power supply voltages and 50% output duty cycle.

# **AC CHARACTERISTICS**

$VTH = -1.3V, \ \ VCC = 4.75V \ \ to \ 5.25V, \ \ VSS = -3.3V \ \ to \ -3.5V, \ \ VEE = -5.1V \ \ to \ -5.5V, \ \ outputs \ \ terminated \ in \ 100\Omega \ \ to \ \ VTT = -2.0V$

|        |                                          | (0    | 16G044<br>℃ to 85% | C)    | 16G044M<br>(-55°C to +125° |       |       |        |                    |

|--------|------------------------------------------|-------|--------------------|-------|----------------------------|-------|-------|--------|--------------------|

| SYMBOL | PARAMETER                                | MIN   | TYP                | MAX   | MIN                        | ТҮР   | MAX   | UNITS  | TEST<br>CONDITIONS |

| VIH    | Input voltage high                       | -1.0  |                    | -0.3  | -1.0                       |       | -0.3  | V      |                    |

| VIL    | Input voltage low                        | VTT   |                    | -1.7  | VTT                        |       | -1.7  | v      |                    |

| Kd2    | Large signal gain constant (-2 version)  | 500/π | 600/π              | 900/π | 500/π                      | 600/π | 900/π | mV/rad | <i>f</i> = 1GHz    |

| Kd3    | Large signal gain constant (-3 version)  | 500/π | 600/π              | 900/π | 500/π                      | 600/π | 900/π | mV/rađ | f = 750 MHz        |

| kd2    | Small signal gain constant (- 2 version) | 125/π | 300/π              | 450/π | 125/π                      | 300/π | 450/π | mV/rad | <b>f</b> = 1GHz    |

| kd3    | Small signal gain constant (- 3 version) | 125/π | 300/π              | 450/π | 125/π                      | 300/π | 450/π | mV/rad | <b>f</b> = 750 MHz |

6

T-45-17

16G044 16G044M

T-45-17

16G044 16G044M

T-90-20

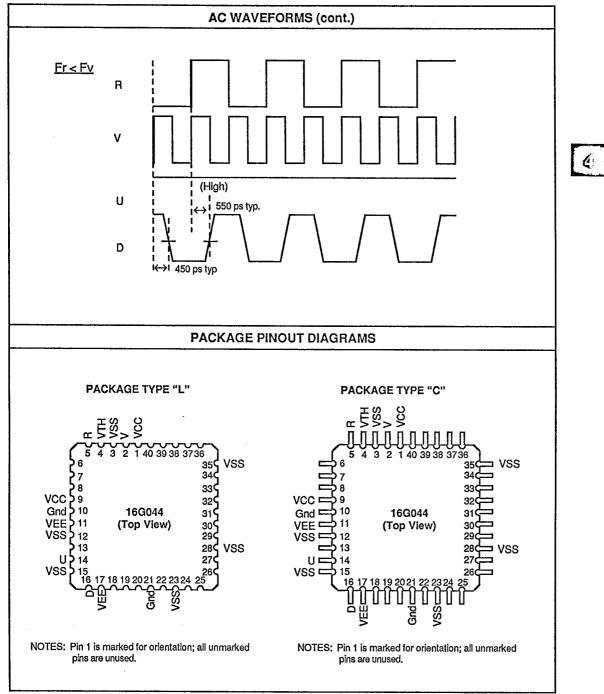

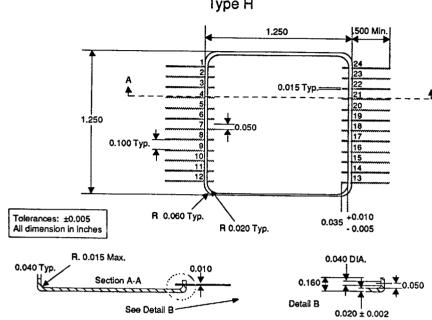

# 24 PIN METAL FLATPACK 18 PIN PACKAGE

# 24 PIN METAL FLATPACK Type H

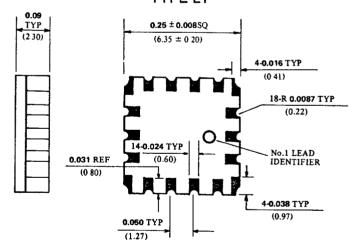

# 18 PIN LEADLESS CHIP CARRIER TYPE L1

All dimensions shown in inches and (millimeters)

T-90-20

# **36 PIN PACKAGES**

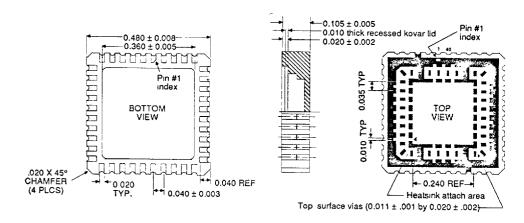

# 36 PIN LEADLESS CHIP CARRIER TYPE L36

#### NOTES:

- The package bottom thermal vias, top lid surface and 4 metallized corner castellations (when present) are all at Vss potential.

- 2) All dimensions in inches.

- 3) Plin #1 identifier may be an elongated pad or small, square gray marker.

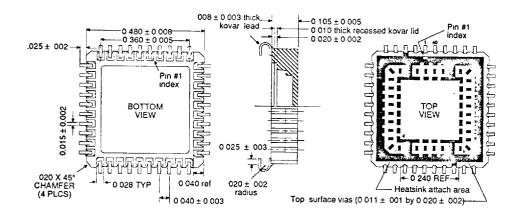

# 36 I/O LEAD FLATPACK TYPE F

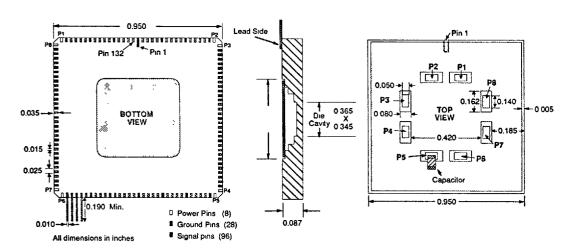

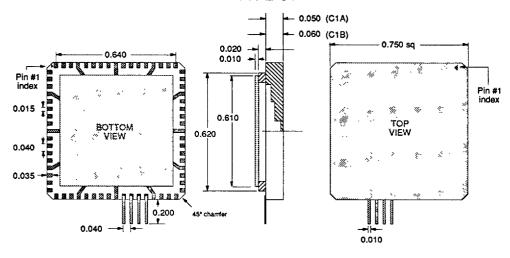

T-90-20 **40 PIN PACKAGES**

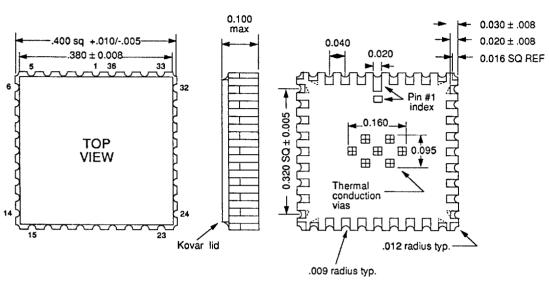

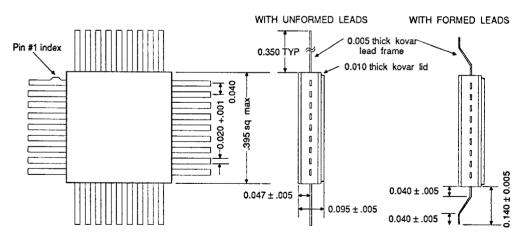

# **40 PIN LEADLESS CHIP CARRIER** TYPE L

#### **40 PIN LEADED CHIP CARRIER** TYPE C

#### NOTES

- (1) Footpint is JEDEC standard outline

(2) Top surface via 15 (for terminating resistors and decoupling capacitors) are not available on pins 3 4 17 18 22 24 37 and 38

(3) Top surface what from finding resistors and pins 3 and 23 are fixed at VTT potential (4) Recommended top surface thip resistors areo 0.60 long by 0.020 wide by 0.010 thick typ 100 mm km nominal power rating (MiniSystems MSR 21 or equivalent) (5) Recommended to surface this capacitors are 0.60 long by 0.030 wide by 0.020 thick typ 25V VDCW 1000 dt mm (Johanson RO9 case or equivalent) (6) Recommended heatsinks all GBL PINs 90GHS 40 A and 90GHS 40 B Thermally conductive, exertically non-ord-ductive apolys is secommended for heatsink attachment (Ablestick 789 4 or 561K, or Thermally Thermalbond\*\* or equivalent.)

- or equivalent.)

(8) L40 and C40 packages are dimensionally identical except for contact linger width

TOP SURFACE LEGEND Metalized Ceramic Screened Dielectric Bare Ceramic. . .. .

Top Surface Terminating/Decoupling Detail MAG REGNED DIELECTRIC TO ACT AS BOLDER DAM BAND PROVIDE BOUNT ON FROM BROWN PLANE CX ECTATA BRILLIC POCK GALAND AL

T-90-20 68 & 132 PIN **PACKAGES**

# 68 PIN LEADED CHIP CARRIER TYPE C1

- All dimensions in inches.

C1A PACKAGE: Package lid, top, and pins 4, 9, 14, 21, 26, 31, 38, 43, 48, 55, 60, 65 are at common potential (system ground).

C1B PACKAGE: Package lid and pins 4, 9, 14, 21, 26, 31, 38, 43, 48, 55, 60, 65 are at common potential (system ground).

Tolerance on all dimensions is ± 1 % but not larger than ± 0.005. Tolerance on 0.640 end pad to end pad dimension is ± 0.003.

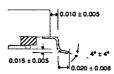

#### **GULLWING LEADS**

# 132 PIN LEADED CHIP CARRIER TYPE C3