# 3.3-V PHASE-LOCK LOOP CLOCK DRIVER

SCAS624A - APRIL 1999 REVISED MAY 1999

- Spread Spectrum Clock Compatible

- Operating Frequency 25 MHz to 140 MHz

- Static tPhase Error Distribution at 66MHz to 133 MHz is ±125 ps

- Jitter (cyc cyc) at 66 MHz to 133 MHz is |70| ps

- **Available in Plastic 24-Pin TSSOP**

- Phase-Lock Loop Clock Distribution for Synchronous DRAM Applications

- Distributes One Clock Input to One Bank of Five and One Bank of Four Outputs

- **Separate Output Enable for Each Output**

- External Feedback (FBIN) Terminal Is Used to Synchronize the Outputs to the Clock

- **On-Chip Series Damping Resistors**

- No External RC Network Required

- Operates at 3.3 V

#### **PW PACKAGE** (TOP VIEW) AGND 24 CLK 23 AV<sub>CC</sub> V<sub>CC</sub> 🛭 2 1Y0 **1**3 22 V<sub>CC</sub> 21 2Y0 1Y1 **∏**4 1Y2 15 20 **∏** 2Y1 GND 6 19 GND GND II 7 18 **∏** GND 17 1 2Y2 1Y3 🛮 8 1Y4 🛮 9 16 2Y3 V<sub>CC</sub> [] 10 15 V<sub>CC</sub> 14 🛮 2G 1G 🛮 11 FBOUT 12 13 FBIN

#### description

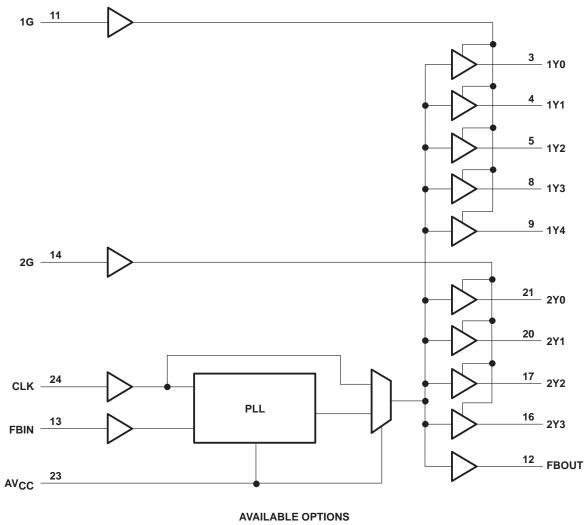

The CDCF2509 is a high-performance, low-skew, low-jitter, phase-lock loop (PLL) clock driver. It uses a PLL to precisely align, in both frequency and phase, the feedback (FBOUT) output to the clock (CLK) input signal. It is specifically designed for use with synchronous DRAMs. The CDCF2509 operates at 3.3 V V<sub>CC</sub>. It also provides integrated series-damping resistors that make it ideal for driving point-to-point loads.

One bank of five outputs and one bank of four outputs provide nine low-skew, low-jitter copies of CLK. Output signal duty cycles are adjusted to 50%, independent of the duty cycle at CLK. Each bank of outputs is enabled or disabled separately via the control (1G and 2G) inputs. When the G inputs are high, the outputs switch in phase and frequency with CLK; when the G inputs are low, the outputs are disabled to the logic-low state.

Unlike many products containing PLLs, the CDCF2509 does not require external RC networks. The loop filter for the PLL is included on-chip, minimizing component count, board space, and cost.

Because it is based on PLL circuitry, the CDCF2509 requires a stabilization time to achieve phase lock of the feedback signal to the reference signal. This stabilization time is required, following power up and application of a fixed-frequency, fixed-phase signal at CLK, and following any changes to the PLL reference or feedback signals. The PLL can be bypassed for test purposes by strapping AV<sub>CC</sub> to ground.

The CDCF2509 is characterized for operation from 0°C to 85°C.

For application information refer to application reports High Speed Distribution Design Techniques for CDC509/516/2509/2510/2516 (literature number SLMA003) and Using CDC2509A/2510A PLL with Spread Spectrum Clocking (SSC) (literature number SCAA039).

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

## **FUNCTION TABLE**

| INPUTS |    |     | OUTPUTS     |             |       |  |

|--------|----|-----|-------------|-------------|-------|--|

| 1G     | 2G | CLK | 1Y<br>(0:4) | 2Y<br>(0:3) | FBOUT |  |

| Х      | Х  | L   | L           | L           | L     |  |

| L      | L  | Н   | L           | L           | Н     |  |

| L      | Н  | Н   | L           | Н           | н     |  |

| н      | L  | Н   | Н           | L           | Н     |  |

| Н      | Н  | Н   | Н           | Н           | н     |  |

# functional block diagram

|             | PACKAGE               |  |  |

|-------------|-----------------------|--|--|

| TA          | SMALL OUTLINE<br>(PW) |  |  |

| 0°C to 85°C | CDCF2509PWR           |  |  |

SCAS624A - APRIL 1999 REVISED MAY 1999

# **Terminal Functions**

| TERMINAL |                | TYPE   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|----------|----------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| NAME     | NO.            | IYPE   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| CLK      | 24             | I      | Clock input. CLK provides the clock signal to be distributed by the CDCF2509 clock driver. CLK is used to provide the reference signal to the integrated PLL that generates the clock output signals. CLK must have a fixed frequency and fixed phase for the PLL to obtain phase lock. Once the circuit is powered up and a valid CLK signal is applied, a stabilization time is required for the PLL to phase lock the feedback signal to its reference signal. |  |  |  |  |

| FBIN     | 13             | I      | Feedback input. FBIN provides the feedback signal to the internal PLL. FBIN must be hard-wired to FBOUT to complete the PLL. The integrated PLL synchronizes CLK and FBIN so that there is nominally zero phase error between CLK and FBIN.                                                                                                                                                                                                                       |  |  |  |  |

| 1G       | 11             | I      | Output bank enable. 1G is the output enable for outputs 1Y(0:4). When 1G is low, outputs 1Y(0:4) are disabled to a logic-low state. When 1G is high, all outputs 1Y(0:4) are enabled and switch at the same frequency as CLK.                                                                                                                                                                                                                                     |  |  |  |  |

| 2G       | 14             | I      | Output bank enable. 2G is the output enable for outputs 2Y(0:3). When 2G is low, outputs 2Y(0:3) are disabled to a logic low state. When 2G is high, all outputs 2Y(0:3) are enabled and switch at the same frequency as CLK.                                                                                                                                                                                                                                     |  |  |  |  |

| FBOUT    | 12             | 0      | Feedback output. FBOUT is dedicated for external feedback. It switches at the same frequency as CLK. When externally wired to FBIN, FBOUT completes the feedback loop of the PLL. FBOUT has an integrated $25-\Omega$ series-damping resistor.                                                                                                                                                                                                                    |  |  |  |  |

| 1Y (0:4) | 3, 4, 5, 8, 9  | 0      | Clock outputs. These outputs provide low-skew copies of CLK. Output bank 1Y(0:4) is enabled via the 1G input. These outputs can be disabled to a logic-low state by deasserting the 1G control input. Each output has an integrated $25-\Omega$ series-damping resistor.                                                                                                                                                                                          |  |  |  |  |

| 2Y (0:3) | 21, 20, 17, 16 | 0      | Clock outputs. These outputs provide low-skew copies of CLK. Output bank 2Y(0:3) is enabled via the 2G input. These outputs can be disabled to a logic-low state by deasserting the 2G control input. Each output has an integrated 25- $\Omega$ series-damping resistor.                                                                                                                                                                                         |  |  |  |  |

| AVCC     | 23             | Power  | Analog power supply. AV <sub>CC</sub> provides the power reference for the analog circuitry. In addition, AV <sub>CC</sub> can be used to bypass the PLL for test purposes. When AV <sub>CC</sub> is strapped to ground, PLL is bypassed and CLK is buffered directly to the device outputs.                                                                                                                                                                      |  |  |  |  |

| AGND     | 1              | Ground | Analog ground. AGND provides the ground reference for the analog circuitry.                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| VCC      | 2, 10, 15, 22  | Power  | Power supply                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| GND      | 6, 7, 18, 19   | Ground | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

SCAS624A - APRIL 1999 REVISED MAY 1999

## absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage range, AV <sub>CC</sub> (see Note 1)                          | AV <sub>CC</sub> < V <sub>CC</sub> +0.7 V |

|------------------------------------------------------------------------------|-------------------------------------------|

| Supply voltage range, V <sub>CC</sub>                                        | –0.5 V to 4.6 V                           |

| Input voltage range, V <sub>I</sub> (see Note 2)                             |                                           |

| Voltage range applied to any output in the high or low state,                |                                           |

| V <sub>O</sub> (see Notes 2 and 3)                                           | 0.5 V to V <sub>CC</sub> + 0.5 V          |

| Input clamp current, I <sub>IK</sub> (V <sub>I</sub> < 0)                    | –50 mA                                    |

| Output clamp current, $I_{OK}$ ( $V_O < 0$ or $V_O > V_{CC}$ )               | ±50 mA                                    |

| Continuous output current, $I_O(V_O = 0 \text{ to } V_{CC})$                 | ±50 mA                                    |

| Continuous current through each V <sub>CC</sub> or GND                       | ±100 mA                                   |

| Maximum power dissipation at $T_A = 55^{\circ}C$ (in still air) (see Note 4) | 0.7 W                                     |

| Storage temperature range, T <sub>stq</sub>                                  | –65°C to 150°C                            |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- NOTES: 1. AVCC must not exceed VCC.

- 2. The input and output negative-voltage ratings may be exceeded if the input and output clamp-current ratings are observed.

- 3. This value is limited to 4.6 V maximum.

- 4. The maximum package power dissipation is calculated using a junction temperature of 150°C and a board trace length of 750 mils. For more information, refer to the Package Thermal Considerations application note in the ABT Advanced BiCMOS Technology Data Book, literature number SCBD002.

## recommended operating conditions (see Note 5)

|                                    |                                | MIN | MAX | UNIT |

|------------------------------------|--------------------------------|-----|-----|------|

| V <sub>CC</sub> , AV <sub>CC</sub> | Supply voltage                 | 3   | 3.6 | V    |

| VIH                                | High-level input voltage       | 2   |     | V    |

| V <sub>IL</sub>                    | Low-level input voltage        |     | 0.8 | V    |

| VI                                 | Input voltage                  | 0   | VCC | V    |

| IOH                                | High-level output current      |     | -12 | mA   |

| loL                                | Low-level output current       |     | 12  | mA   |

| T <sub>A</sub>                     | Operating free-air temperature | 0   | 85  | °C   |

NOTE 5: Unused inputs must be held high or low to prevent them from floating.

## timing requirements over recommended ranges of supply voltage and operating free-air temperature

|                  |                                 | MIN | MAX | UNIT |

|------------------|---------------------------------|-----|-----|------|

| f <sub>clk</sub> | Clock frequency                 | 25  | 140 | MHz  |

|                  | Input clock duty cycle          | 40% | 60% |      |

|                  | Stabilization time <sup>†</sup> |     | 1   | ms   |

<sup>†</sup> Time required for the integrated PLL circuit to obtain phase lock of its feedback signal to its reference signal. For phase lock to be obtained, a fixed-frequency, fixed-phase reference signal must be present at CLK. Until phase lock is obtained, the specifications for propagation delay, skew, and jitter parameters given in the switching characteristics table are not applicable. This parameter does not apply for input modulation under SSC application.

SCAS624A - APRIL 1999 REVISED MAY 1999

## electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

|                   | PARAMETER                 | TEST CONDITIONS                                                                 | V <sub>CC</sub> , AV <sub>CC</sub> | MIN                  | TYP‡                                           | MAX  | UNIT |

|-------------------|---------------------------|---------------------------------------------------------------------------------|------------------------------------|----------------------|------------------------------------------------|------|------|

| VIK               | Input clamp voltage       | I <sub>I</sub> = -18 mA                                                         | 3 V                                |                      |                                                | -1.2 | V    |

|                   |                           | I <sub>OH</sub> = -100 μA                                                       | MIN to MAX                         | V <sub>CC</sub> -0.2 |                                                |      |      |

| Vон               | High-level output voltage | I <sub>OH</sub> = -12 mA                                                        | 3 V                                | 2.1                  |                                                |      | V    |

|                   |                           | $I_{OH} = -6 \text{ mA}$                                                        | 3 V                                | 2.4                  |                                                |      |      |

|                   |                           | I <sub>OL</sub> = 100 μA                                                        | MIN to MAX                         |                      |                                                | 0.2  |      |

| VOL               | Low-level output voltage  | I <sub>OL</sub> = 12 mA                                                         | 3 V                                |                      |                                                | 0.8  | V    |

|                   |                           | I <sub>OL</sub> = 6 mA                                                          | 3 V                                |                      |                                                | 0.55 |      |

|                   |                           | V <sub>O</sub> = 1 V                                                            | 3.135 V                            | -32                  |                                                |      |      |

| loh               | High-level output current | V <sub>O</sub> = 1.65 V                                                         | 3.3 V                              |                      | -36                                            |      |      |

|                   |                           | V <sub>O</sub> = 3.135 V                                                        | 3.465 V                            |                      | -1.2  0.2  0.8  0.55  -36  -12  40  14  ±5  10 |      |      |

|                   |                           | V <sub>O</sub> = 1.95 V                                                         | 3.135 V                            | 34                   |                                                |      |      |

| lOL               | Low-level output current  | V <sub>O</sub> = 1.65 V                                                         | 3.3 V                              |                      | 40                                             |      |      |

|                   |                           | V <sub>O</sub> = 0.4 V                                                          | 3.465 V                            |                      |                                                | 14   |      |

| lį                | Input current             | V <sub>I</sub> = V <sub>CC</sub> or GND                                         | 3.6 V                              |                      |                                                | ±5   | μΑ   |

| I <sub>CC</sub> § | Supply current            | $V_I = V_{CC}$ or GND, $I_O = 0$ , Outputs: low or high                         | 3.6 V                              |                      |                                                | 10   | μΑ   |

| ΔlCC              | Change in supply current  | One input at V <sub>CC</sub> – 0.6 V,<br>Other inputs at V <sub>CC</sub> or GND | 3.3 V to 3.6 V                     |                      |                                                | 500  | μΑ   |

| Ci                | Input capacitance         | $V_I = V_{CC}$ or GND                                                           | 3.3 V                              |                      | 4                                              |      | pF   |

| Со                | Output capacitance        | V <sub>O</sub> = V <sub>CC</sub> or GND                                         | 3.3 V                              |                      | 6                                              |      | pF   |

<sup>‡</sup> For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions.

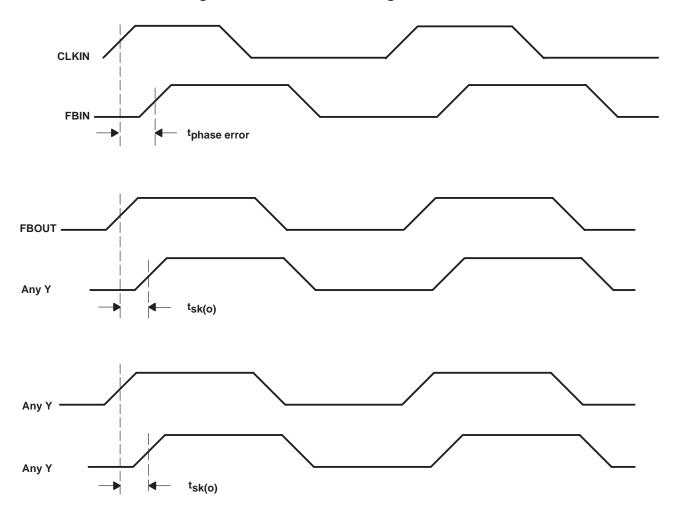

## switching characteristics over recommended ranges of supply voltage and operating free-air temperature, $C_1 = 25 \text{ pF}$ (see Note 6 and Figures 1 and 2)<sup>‡</sup>

| PARAMETER          |                                                            | FROM<br>(INPUT)/CONDITION                                | TO<br>(OUTPUT) | V <sub>CC</sub> , AV <sub>CC</sub> = 3.3 V<br>± 0.3 V |     |     | UNIT |

|--------------------|------------------------------------------------------------|----------------------------------------------------------|----------------|-------------------------------------------------------|-----|-----|------|

|                    |                                                            | (INTOT)/CONDITION                                        | (0011 01)      | MIN                                                   | TYP | MAX |      |

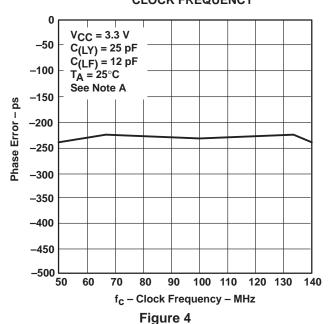

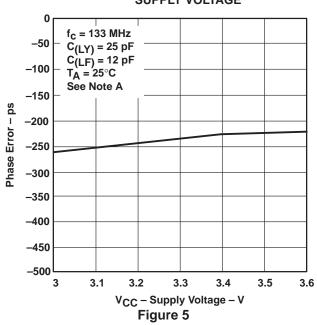

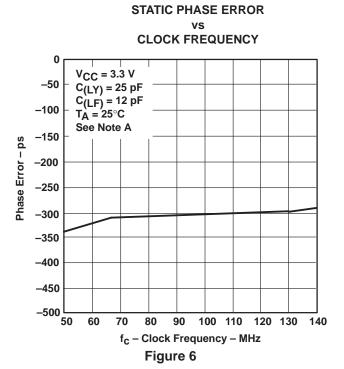

|                    | Phase error time – static (normalized) (See Figures 3 – 6) | CLKIN↑ = 66 MHz to133 MHz                                | FBIN↑          | -125                                                  |     | 125 | ps   |

| t <sub>sk(o)</sub> | Output skew time§                                          | Any Y or FBOUT                                           | Any Y or FBOUT |                                                       |     | 200 | ps   |

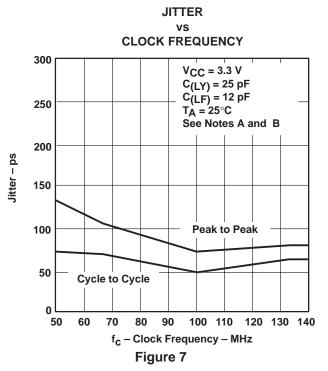

|                    | Phase error time – jitter (see Note 7)                     | Clkin = 66 MHz to 133 MHz                                | Any Y or FBOUT | -50                                                   |     | 50  |      |

|                    | Jitter(cycle-cycle)                                        | GIKIII = 00 IVII IZ 10 133 IVII IZ                       | Any Y or FBOUT |                                                       | 70  |     | ps   |

|                    | (See Figure 7)                                             | Clkin = 100 MHz to 133 MHz                               | Any Y or FBOUT |                                                       | 65  |     |      |

|                    | Duty cycle                                                 | F(clkin > 60 MHz)                                        | Any Y or FBOUT | 45%                                                   |     | 55% |      |

| t <sub>r</sub>     | Rise time (See Notes 8 and 9)                              | $V_O = 1.2 \text{ V to } 1.8 \text{ V,}$ IBIS simulation | Any Y or FBOUT | 2.5                                                   |     | 1   | V/ns |

| t <sub>f</sub>     | Fall time (See Notes 8 and 9)                              | V <sub>O</sub> = 1.2 V to 1.8 V,<br>IBIS simulation      | Any Y or FBOUT | 2.5                                                   |     | 1   | V/ns |

<sup>&</sup>lt;sup>‡</sup> These parameters are not production tested.

NOTES: 6. The specifications for parameters in this table are applicable only after any appropriate stabilization time has elapsed.

- Calculated per PC DRAM SPEC (t<sub>phase error</sub>, static jitter<sub>(cycle-to-cycle)</sub>).

This is equivalent to 0.8 ns/2.5 ns and 0.8 ns/2.7 ns into standard 500 Ω/ 30 pf load for output swing of 04. V to 2 V.

- 9. 64 MB DIMM configuration according to PC SDRAM Registered DIMM Design Support Document, Figure 20 and Table 13.

Intel is a trademark of Intel Corporation.

PC SDRAM Register DIMM Design Support Document is published by Intel Corporation.

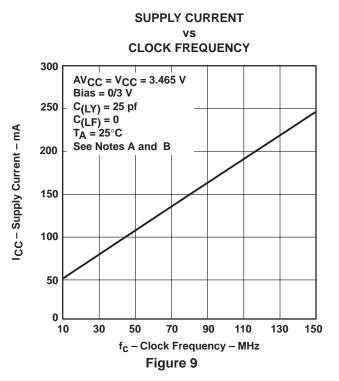

<sup>§</sup> For ICC of AVCC, and ICC vs Frequency (see Figures 8 and 9).

<sup>§</sup> The t<sub>sk(0)</sub> specification is only valid for equal loading of all outputs.

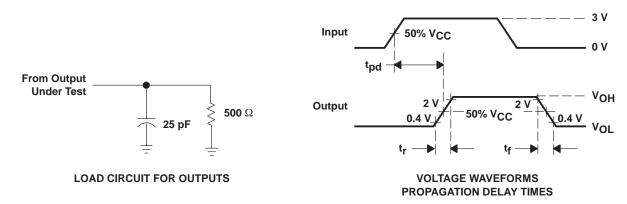

## PARAMETER MEASUREMENT INFORMATION

NOTES: A.  $C_L$  includes probe and jig capacitance.

- B. All input pulses are supplied by generators having the following characteristics: PRR  $\leq$  133 MHz, Z<sub>O</sub> = 50  $\Omega$ ,  $t_f \leq$  1.2 ns.  $t_f \leq$  1.2 ns.

- C. The outputs are measured one at a time with one transition per measurement.

Figure 1. Load Circuit and Voltage Waveforms

Figure 2. Phase Error and Skew Calculations

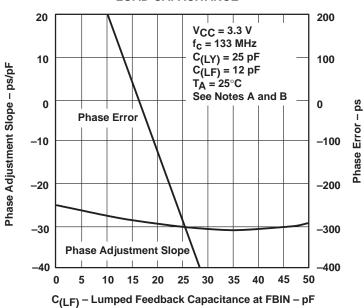

## TYPICAL CHARACTERISTICS

#### PHASE ADJUSTMENT SLOPE AND PHASE ERROR

#### vs LOAD CAPACITANCE

#### Figure 3

NOTES: A. Trace feedback length FBOUT to FBIN = 5 mm,  $Z_O = 50~\Omega$  Phase error measured from CLK to Y

B.  $C_{(LF)}$  = Lumped feedback capacitance at FBIN

## PHASE ERROR vs CLOCK FREQUENCY

NOTE A: Trace feedback length FBOUT to FBIN = 5 mm,  $Z_{\Omega}$  = 50  $\Omega$

## PHASE ERROR vs SUPPLY VOLTAGE

## TYPICAL CHARACTERISTICS

NOTES: A. Trace feedback length FBOUT to FBIN = 5 mm,  $Z_O$  = 50  $\Omega$

- B. Phase error measured from CLK to FBIN

- C. CLY = Lumped capacitive load at Y

- D. CLF = Lumped feedback capacitance at FBIN

#### TYPICAL CHARACTERISTICS

#### **ANALOG SUPPLY CURRENT CLOCK FREQUENCY** 16 AVCC = VCC = 3.465 V 14 Bias = 0/3 V AICC - Analog Supply Current - mA $C_{(LY)} = 25 pf$ $C_{(LF)} = 0$ $T_A = 25^{\circ}C$ 12 See Notes A and B 10 8 6 4 2 0 30 50 70 90 110 130 150 10 f<sub>C</sub> - Clock Frequency - MHz Figure 8

NOTES: A.  $C_{(LY)}$  = Lumped capacitive load at Y

B.  $C_{(LF)}^{(-1)}$  = Lumped feedback capacitance at FBIN

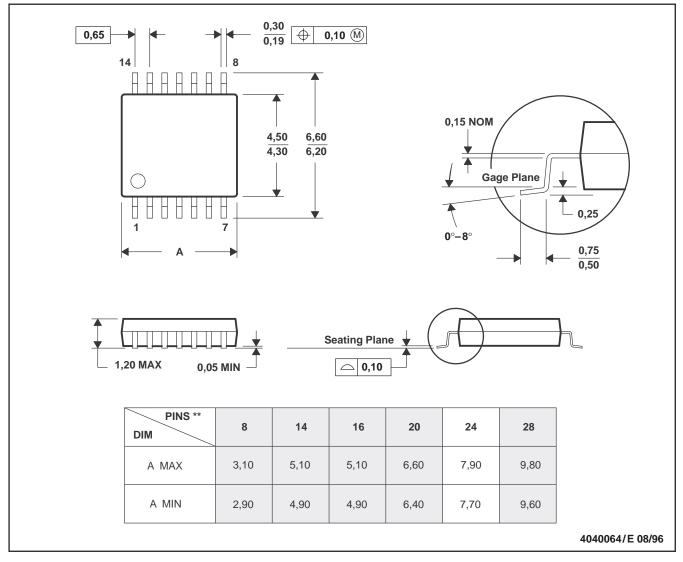

## **MECHANICAL INFORMATION**

## PW (R-PDSO-G\*\*)

## PLASTIC SMALL-OUTLINE PACKAGE

## 14 PIN SHOWN

NOTES: A. All linear dimensions are in millimeters.

B. This drawing is subject to change without notice.

C. Body dimensions do not include mold flash or protrusion not to exceed 0,15.

D. Falls within JEDEC MO-153

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1999, Texas Instruments Incorporated