## CDC930

# 133-MHz DIFFERENTIAL CLOCK SYNTHESIZER/DRIVER FOR PC MOTHERBOARDS WITH 3-STATE OUTPUTS

SCAS641 - JULY 2000

- Generates Clocks for Pentium®4 **Microprocessors**

- Uses a 14.318 MHz Crystal Input to **Generate Multiple Output Frequencies**

- Includes Spread Spectrum Clocking (SSC), 0.6% Downspread for Reduced EMI With Theoretical EMI Damping of 7 dB<sup>†</sup>

- **Power Management Control Terminals**

- Low Output Skew and Jitter for Clock Distribution

- **Operates From Single 3.3-V Supply**

- Consumes Less Than 30-mA Power-Down Current

- **Generates the Following Clocks:**

- 4 HCLK (Host) (Different Pairs-100/133 MHz)

- 1 3VMREF Pair (3.3 V, 180° Shifted 50/66 MHz)

- 10 PCI (3.3 V, 33.3 MHz)

- 2 REF (3.3 V, 14.318 MHz)

- 4 3V66 MHz (3.3 V, 66 MHz)

- 2 3V48 MHz (3.3 V, 48 MHz)

- Packaged in 56-Pin SSOP Package

#### description

The CDC930 is a differential clock synthesizer/ driver that generates HCLK/HCLK, 3VMREF/ 3VMREF, PCI, 3V66, 3V48, REF system clock signals to support a computer system with a Pentium®4 microprocessor and a Direct Rambus™ memory subsystem.

GND 56 V<sub>DD</sub>3.3V REF0/MultSel0 [ 55 ☐ 3VMREF 2 54 3VMREF REF1/MultSel1 V<sub>DD</sub>3.3V **[**] 4 53 GND XIN [ 52 SPREAD 5 XOUT [ 51 HCLK(1) GND [] 7 50 HCLK(1) PCI0 [ 49 V<sub>DD</sub>3.3V 8 PCI1 ¶ 9 48 HCLK(2) V<sub>DD</sub>3.3V **1** 10 47 HCLK(2) PCI2 [ 46 GND 11 PCI3 **∏** 12 45 | HCLK(3) GND **1** 13 44 HCLK(3) PCI4 [ 14 43 V<sub>DD</sub>3.3V PCI5 **1** 15 42 HCLK(4) V<sub>DD</sub>3.3V **1** 16 41 HCLK(4) PCI6 [ 17 40 GND 39 I\_REF PCI7 **1** 18 GND **1** 19 38 V<sub>DD</sub>3.3V PCI8 [ 20 37 | GND PCI9 **1** 21 36 V<sub>DD</sub>3.3V V<sub>DD</sub>3.3V **∏** 22 35 3V66(0) SEL100/133 [ 23 34 3V66(1) GND [ 33 **∏** GND 32 \ GND 3V48(0)/SeIA [ 25 26 31 **1** 3V66(2) 3V48(1)/SeIB [ 27 30 3V66(3) V<sub>DD</sub>3.3V [ 28 29 V<sub>DD</sub>3.3V PWRDWN [

DL PACKAGE (TOP VIEW)

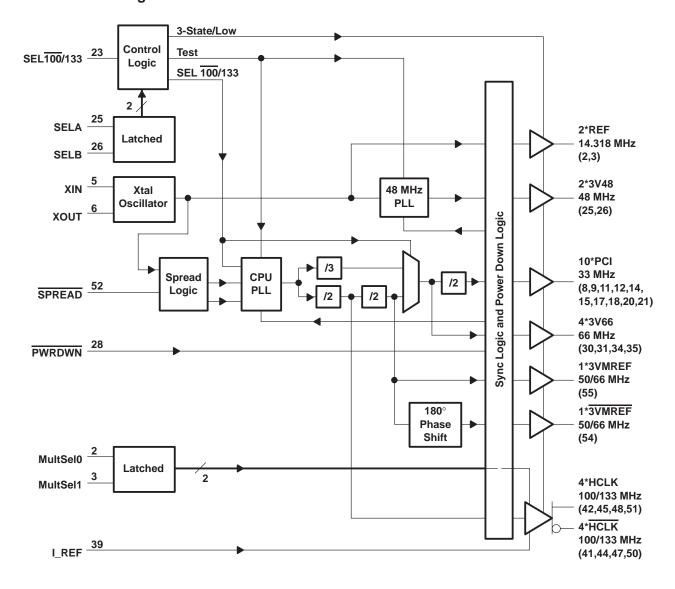

All output frequencies are generated from a 14.318-MHz crystal input. A reference clock input can be provided at the XIN input instead of a crystal. Two phase-locked loops (PLLs) are used to generate the host frequencies and the 48-MHz clock frequencies. On-chip loop filters and internal feedback eliminate the need for external components. The host, PCI clock and 48-MHz clock outputs provide low-skew/low-jitter clock signals for reliable clock operation. All outputs have 3-state capability, which can be selected using control inputs SEL133, SelA and SelB.

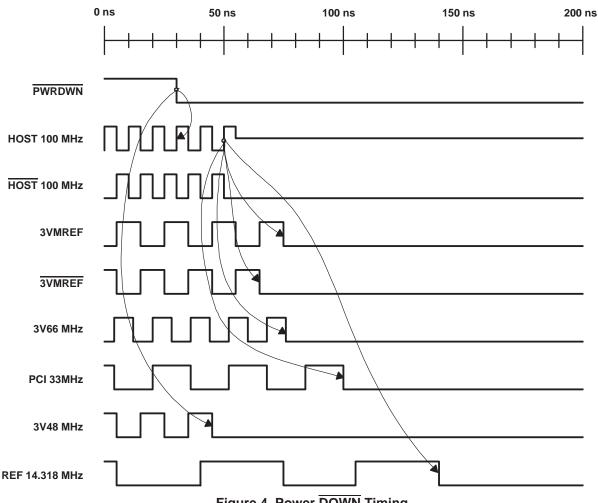

The outputs are either differential host clock or 3.3-V single-ended CMOS buffers. When PWRDWN is set to high, the device operates in normal mode. When PWRDWN is set low, the device transitions to a power-down mode in which HCLK is driven at 2×I<sub>RFF</sub>, HCLK is not driven, and all others are set low.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

†This is system design dependant. Intel and Pentium®4 are trademarks of Intel Corporation. Rambus is a trademark of Rambus Corporation.

SCAS641 - JULY 2000

## description (continued)

The HOST bus operates at 100 MHz or 133 MHz. The MREF bus operates at 50 MHz or 66 MHz. Output frequency selection is accomplished with corresponding setting for SEL100/133 control input. The PCI bus frequency is fixed to 33 MHz.

Since the CDC930 is based on PLL circuitry, it requires a stabilization time to achieve phase-lock of the PLL. This stabilization time is required following power up as well as changes to SEL inputs. With use of external reference clock, this signal must be fixed-frequency and fixed-phase prior stabilization time starts.

## functional block diagram

## **Terminal Functions**

| TERMINAL             |                                                 |         |                                                                                                                                                                                                                                |

|----------------------|-------------------------------------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                 | NO.                                             | 1/0     | DESCRIPTION                                                                                                                                                                                                                    |

| 3V48(0)/SeIA         | 25                                              | I/O     | Dual function 3.3 V, Type 3, 48-MHz clock output that latches the state of SelA during power up                                                                                                                                |

| 3V48(1)/SelB         | 26                                              | I/O     | Dual function 3.3 V, Type 3, 48-MHz clock output that latches the state of SelB during power up                                                                                                                                |

| 3V66[0-3]            | 30, 31, 34, 35                                  | 0       | 3.3 V, Type 5, 66-MHz clock outputs                                                                                                                                                                                            |

| 3VMREF               | 55                                              | 0       | 3.3 V, Type 5, 50/66-MHz memory clock output                                                                                                                                                                                   |

| 3VMREF               | 54                                              | 0       | 3.3 V, Type 5, 50/66-MHz memory clock output (180° out of phase with 3VMREF)                                                                                                                                                   |

| GND                  | 1, 7, 13, 19,<br>24, 32, 33, 37,<br>40, 46, 53  |         | Ground for core and HCLK/HCLK, 3VMREF/3VMREF, 3V48, 3V66 and PCI outputs                                                                                                                                                       |

| HCLK[1-4]            | 42, 45, 48, 51                                  | 0       | Type X1, host clock outputs                                                                                                                                                                                                    |

| HCLK[1-4]            | 41, 44, 47, 50                                  | 0       | Type X1, host complementary clock outputs                                                                                                                                                                                      |

| I_REF                | 39                                              | Special | Current reference pin for the host clock pairs. I_REF uses a fixed precision resistor tied to ground to establish the appropriate current.                                                                                     |

| PCI[0-9]             | 8, 9, 11, 12,<br>14, 15, 17, 18,<br>20, 21      | 0       | 3.3 V, Type 5, 33-MHz PCI clock outputs                                                                                                                                                                                        |

| PWRDWN               | 28                                              | I       | Power down for complete device with HOST at 2×I <sub>REF</sub> , HCLK not driven and all other outputs forced low.                                                                                                             |

| REF0/MultSel0        | 2                                               | I/O     | Dual function 3.3 V, Type 3, 14.318-MHz reference clock output. The state of MultSel0 is latched during power up. MultSel0 configures the $I_{OH}$ amplitude (and thus the $V_{OH}$ swing amplitude) of the HCLK pair outputs. |

| REF1/MultSel1        | 3                                               | I/O     | Dual function 3.3 V, Type 3, 14.318-MHz reference clock output. The state of MultSel1 is latched during power up. MultSel1 configures the $I_{OH}$ amplitude (and thus the $V_{OH}$ swing amplitude) of the HCLK pair outputs. |

| SEL100/133           | 23                                              | ı       | Active low LVTTL level logic select. SEL100/133 is used for enabling 100/133 MHz. Low=100 MHz, high=133 MHz                                                                                                                    |

| SPREAD               | 52                                              | I       | LVTTL level logic select. SPREAD pin enables/disables the spread spectrum for the HCLK/HCLK, 3VMREF/3VMREF, 3V66 and PCI outputs.                                                                                              |

| V <sub>DD</sub> 3.3V | 4, 10, 16, 22,<br>27, 29, 36, 38,<br>43, 49, 56 | I       | 3.3-V power for core and the HCLK/HCLK, 3VMREF/3VMREF, 3V48, 3V66, and PCI outputs.                                                                                                                                            |

| XIN                  | 5                                               | I       | Crystal input – 14.318 MHz                                                                                                                                                                                                     |

| XOUT                 | 6                                               | 0       | Crystal output – 14.318 MHz                                                                                                                                                                                                    |

SCAS641 - JULY 2000

#### **Function Tables**

#### **SELECT FUNCTIONS**

| INP        | PUTS |      |            | FUNCTION       |        |        |        |            |                      |

|------------|------|------|------------|----------------|--------|--------|--------|------------|----------------------|

| SEL100/133 | SelA | SelB | HOST, HCLK | 3VMREF, 3VMREF | PCI    | 3V66   | 3V48   | REF        | FUNCTION             |

| 0          | 0    | 0    | 100 MHz    | 50 MHz         | 33 MHz | 66 MHz | 48 MHz | 14.318 MHz | Active 100 MHz       |

| 0          | 1    | 1    | Hi-Z       | Hi-Z           | Hi-Z   | Hi-Z   | Hi-Z   | Hi-Z       | All outputs 3-stated |

| 1          | 0    | 0    | 133 MHz    | 66 MHz         | 33 MHz | 66 MHz | 48 MHz | 14.318 MHz | Active 133 MHz       |

| 1          | 1    | 1    | TCLK/2     | TCLK/4         | TCLK/8 | TCLK/4 | TCLK/2 | TCLK       | Test Mode            |

#### **ENABLE FUNCTION**

| INPUT      | OUTPUTS            |            |                |     |      |      |     |  |  |  |  |

|------------|--------------------|------------|----------------|-----|------|------|-----|--|--|--|--|

| SEL100/133 | HCLK               | HCLK       | 3VMREF, 3VMREF | PCI | 3V66 | 3V48 | REF |  |  |  |  |

| 0          | 2×I <sub>REF</sub> | Not driven | L              | L   | L    | L    | L   |  |  |  |  |

| 1          | On                 | On         | On             | On  | On   | On   | On  |  |  |  |  |

#### SPREAD SPECTRUM FUNCTION

| INPUT    |  | OUTPUTS                                                                       |

|----------|--|-------------------------------------------------------------------------------|

| 0        |  | Spread spectrum clocking active, -0.6% at HCLK/HCLK, 3VMREF/3VMREF, 3V66, PCI |

| SPREAD 1 |  | Spread spectrum clocking nonactive                                            |

#### **OUTPUT BUFFER SPECIFICATIONS**

| BUFFER NAME   | V <sub>DD</sub> RANGE<br>(V) | IMPEDANCE<br>(Ω) | BUFFER TYPE |

|---------------|------------------------------|------------------|-------------|

| 3V48, REF     | 3.135 – 3.465                | 20–60            | TYPE 3      |

| PCI, 3V66     | 3.135 – 3.465                | 12–65            | TYPE 5      |

| 3VMREF/3VMREF | 3.135 – 3.465                | 12–55            | TYPE 5      |

| HCLK/HCLK     |                              |                  | TYPE X1     |

#### **OUTPUT BUFFER SPECIFICATIONS**

| INPUTS   |          | BOARD TARGET | REFERENCE R,                                        | OUTPUT CURRENT                       | V <sub>OH</sub> AT Z  |

|----------|----------|--------------|-----------------------------------------------------|--------------------------------------|-----------------------|

| MultSel0 | MultSel1 | TRACE/TERM Z | $I_{REF} = VDD/3 \times R_r$ )                      | OUTFUT CORRENT                       | IREF = 2.32 mA        |

| 0        | 0        | <b>60</b> Ω  | R <sub>r</sub> = 475 1%, I <sub>REF</sub> = 2.32 mA | I <sub>OH</sub> = 5×I <sub>REF</sub> | 0.71 V at 60 $\Omega$ |

| 0        | 0        | 50 Ω         | $R_r = 475  1\%,  I_{REF} = 2.32  mA$               | I <sub>OH</sub> = 5×I <sub>REF</sub> | 0.59 V at 50 Ω        |

| 0        | 1        | 60 Ω         | $R_r = 475  1\%,  I_{REF} = 2.32  mA$               | I <sub>OH</sub> = 6×I <sub>REF</sub> | 0.85 V at 60 Ω        |

| 0        | 1        | <b>50</b> Ω  | R <sub>r</sub> = 475 1%, I <sub>REF</sub> = 2.32 mA | I <sub>OH</sub> = 6×I <sub>REF</sub> | 0.71 V at 50 $\Omega$ |

| 1        | 0        | 60 Ω         | $R_r = 475  1\%$ , $I_{REF} = 2.32  mA$             | IOH = 4×IREF                         | 0.56 V at 60 Ω        |

| 1        | 0        | 50 Ω         | $R_r = 475  1\%$ , $I_{REF} = 2.32  mA$             | IOH = 4×IREF                         | 0.47 V at 50 Ω        |

| 1        | 1        | 60 Ω         | $R_r = 475  1\%$ , $I_{REF} = 2.32  mA$             | I <sub>OH</sub> = 7×I <sub>REF</sub> | 0.99 V at 60 Ω        |

| 1        | 1        | 50 Ω         | $R_r = 475  1\%,  I_{REF} = 2.32  mA$               | I <sub>OH</sub> = 7×I <sub>REF</sub> | 0.82 V at 50 Ω        |

NOTE: The entries in **boldface** are the primary system configurations of interest. The outputs should be optimized for these configurations

SCAS641 - JULY 2000

## absolute maximum ratings over operating free-air temperature (unless otherwise noted)†

| Supply voltage range, V <sub>DD</sub>                                         |                                  |

|-------------------------------------------------------------------------------|----------------------------------|

| Input voltage range, V <sub>I</sub> (see Note 1)                              | 0.5 V to V <sub>DD</sub> + 0.5 V |

| Voltage range applied to any output in the high-impedance state               | or power-off state,              |

| V <sub>O</sub> (see Note 1)                                                   | 0.5 V to V <sub>DD</sub> + 0.5 V |

| Current into any output in the low state, IO                                  | 2 × rated I <sub>OL</sub>        |

| Input clamp current, I <sub>IK</sub> (V <sub>I</sub> < 0)                     |                                  |

| $(V_I < V_{DD})$                                                              | 18 mA                            |

| Output clamp current , I <sub>OK</sub> (V <sub>O</sub> < 0)                   |                                  |

| $(V_O < V_{DD})$                                                              | 50 mA                            |

| Package thermal impedance, θ <sub>JA</sub> (see Note 2)                       |                                  |

| Maximum power dissipation at $T_A = 55^{\circ}$ C (in still air) (see Note 3) | ) 1.3 W                          |

| Operating free-air temperature range, T <sub>A</sub>                          |                                  |

| Storage temperature range, T <sub>Stq</sub>                                   |                                  |

| Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds                  |                                  |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- NOTES: 1. The input and output negative-voltage ratings may be exceeded if the input and output clamp-current ratings are observed.

- 2. The package thermal impedance is calculated in accordance with EIA/JEDEC Std JESD51, except for the through-hole packages, which use a trace length of zero. The absolute maximum power dissipation allowed at T<sub>A</sub> = 55°C (in still air) is 1.3 W.

- 3. The maximum package power dissipation is calculated using a junction temperature of 1505C and a board trace length of 750 mils. For more information, refer to the *Package Thermal Considerations* application note in the *ABT Advanced BiCMOS Technology Data Book*, literature number SCBD002.

#### **DISSIPATION RATING TABLE**

| PACKAGE | $T_{\mbox{A}} \le 25^{\circ}\mbox{C}$ POWER RATING | DERATING FACTOR‡ ABOVE T <sub>A</sub> = 25°C | T <sub>A</sub> = 70°C<br>POWER RATING | T <sub>A</sub> = 85°C<br>POWER RATING |

|---------|----------------------------------------------------|----------------------------------------------|---------------------------------------|---------------------------------------|

| DL      | 1558.6 mW                                          | 12.468 mW/°C                                 | 997.5 mW                              | 810.52 mW                             |

<sup>‡</sup> This is the inverse of the traditional junction-to-case thermal resistance (R<sub>θ</sub>JA) and uses a board-mounted device at 74°C/W.

# **CDC930**

# 133-MHz DIFFERENTIAL CLOCK SYNTHESIZER/DRIVER FOR PC MOTHERBOARDS WITH 3-STATE OUTPUTS

SCAS641 - JULY 2000

## recommended operating conditions (see Note 2)

|                                                                                                                                                                                                                                                                                           |               | MIN            | иом†   | MAX                     | UNIT |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|----------------|--------|-------------------------|------|--|

| Supply voltage, V <sub>DD</sub>                                                                                                                                                                                                                                                           |               |                |        | 3.465                   | V    |  |

| High-level input voltage, V <sub>IH</sub>                                                                                                                                                                                                                                                 |               |                |        | V <sub>DD</sub> + 0.3 V | V    |  |

| Low-level input voltage, V <sub>IL</sub>                                                                                                                                                                                                                                                  |               | GND –<br>0.3 V |        | 0.8                     | V    |  |

| Input voltage, V <sub>I</sub>                                                                                                                                                                                                                                                             |               | 0              |        | $V_{DD}$                | V    |  |

| High-level input voltage, V <sub>IL</sub> Low-level input voltage, V <sub>IL</sub> Input voltage, V <sub>I</sub> High-level output current, I <sub>OH</sub> Low-level output current, I <sub>OL</sub> Reference frequency, f <sub>(XIN)</sub> ‡  Crystal frequency, f <sub>(XTAL)</sub> § | HCLK/HCLK     |                |        | -20                     |      |  |

|                                                                                                                                                                                                                                                                                           | 3VMREF/3VMREF |                |        | -15                     | mA   |  |

|                                                                                                                                                                                                                                                                                           | 48MHz, REFx   |                |        | -16                     | IIIA |  |

|                                                                                                                                                                                                                                                                                           | PCIx, 3V66x   |                |        | -15                     |      |  |

|                                                                                                                                                                                                                                                                                           | HCLK/HCLK     |                |        | 5                       | μА   |  |

| High-level input voltage, V <sub>IL</sub> Low-level input voltage, V <sub>IL</sub> Input voltage, V <sub>I</sub> High-level output current, I <sub>OH</sub> Low-level output current, I <sub>OL</sub> Reference frequency, f <sub>(XIN)</sub> ‡  Crystal frequency, f <sub>(XTAL)</sub> § | 3VMREF/3VMREF |                |        | 10                      |      |  |

| Low-level output current, IOL                                                                                                                                                                                                                                                             | 48MHz, REFx   |                |        | 10                      | mA   |  |

| igh-level input voltage, V <sub>IL</sub> pw-level input voltage, V <sub>IL</sub> put voltage, V <sub>I</sub> igh-level output current, I <sub>OH</sub> pw-level output current, I <sub>OL</sub> eference frequency, f <sub>(XIN)</sub> ‡  rystal frequency, f <sub>(XTAL)</sub> §         | PCIx, 3V66x   |                |        | 10                      |      |  |

| Reference frequency, f(XIN) <sup>‡</sup>                                                                                                                                                                                                                                                  | Test mode     |                | 14     |                         | MHz  |  |

| Crystal frequency, f(XTAL)§                                                                                                                                                                                                                                                               | Normal mode   | 13.8           | 14.318 | 14.8                    | MHz  |  |

| Operating free-air temperature, TA                                                                                                                                                                                                                                                        |               | 0              |        | 85                      | °C   |  |

<sup>&</sup>lt;sup>†</sup> All nominal values are measured at their respective nominal V<sub>DD</sub> values.

5.  $V_{IH}$ ,  $V_{IL}$ : All input levels referenced to  $V_{DD} = 3.30 \text{ V}$ .

<sup>‡</sup> Reference frequency is a test clock driven on the XIN input during the device test mode and normal mode. In test mode, XIN can be driven externally up to  $f_{(XIN)} = 16$  MHz. If XIN is driven externally, XOUT is floating. § This is a series fundamental crystal with  $f_O = 14.31818$  MHz. NOTES: 4. Unused inputs must be held high or low to prevent them from floating.

SCAS641 - JULY 2000

## electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

|                     | PARAMETER                   |                                    | TEST C                     | CONDITIONS                                                                                                                                                                                                                    | MIN TYPT | MAX  | UNIT |

|---------------------|-----------------------------|------------------------------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------|------|

| VIK                 | Input clamp voltage         |                                    | $V_{DD} = 3.135 V$ ,       | I <sub>I</sub> = -18 mA                                                                                                                                                                                                       |          | -1.2 | V    |

| R <sub>I</sub>      | Input resistance            | XIN-XOUT                           | $V_{DD} = 3.465 V,$        | $V_{I} = V_{DD} - 0.5 V$                                                                                                                                                                                                      | 100      |      | kΩ   |

|                     |                             | XOUT                               | $V_{DD} = 3.135 V,$        | $V_{I} = V_{DD} - 0.5 V$                                                                                                                                                                                                      |          | 50   | mA   |

| Iн                  | High-level input current    | MultSel0, MultSel1,<br>SelA, SelB  | V <sub>DD</sub> = 3.465 V, | $V_I = V_{DD}$                                                                                                                                                                                                                |          | 10   | μА   |

|                     |                             | SEL100/133<br>SPREAD, PWRDWN       | V <sub>DD</sub> = 3.465 V, | $V_I = V_{DD}$                                                                                                                                                                                                                |          | 5    | μΑ   |

|                     |                             | XOUT                               | $V_{DD} = 3.135 V$ ,       | VO = 0 V                                                                                                                                                                                                                      |          | -5   | mA   |

|                     | l and land in the arms of   | MultSel0, MultSel1,<br>SelA, SelB, | V <sub>DD</sub> = 3.465 V, | V <sub>I</sub> = GND                                                                                                                                                                                                          |          | -10  | μΑ   |

| ¹IL                 | Low-level input current     | SEL100/133<br>SPREAD, PWRDWN       | V <sub>DD</sub> = 3.465 V, | V <sub>I</sub> = GND                                                                                                                                                                                                          |          | -5   | μΑ   |

|                     |                             | I_REF                              | $V_{DD} = 3.465 V,$        | R <sub>r</sub> = 221                                                                                                                                                                                                          |          | -5.5 | mA   |

| loz                 | High-impedance-state outp   | out current                        | V <sub>DD</sub> = 3.465 V  | $\begin{array}{c} \text{SEL}\underline{A}, \text{SELB} = H,\\ \text{SEL}\overline{100}/133 \text{H} \rightarrow \text{L}\\ \underline{V_O} = V_{\mbox{\scriptsize DD}}  \text{or GND}\\ \mbox{PWRDWN} = \mbox{H} \end{array}$ |          | ±10  | μΑ   |

| I <sub>DD(Z)</sub>  | High-impedance-state sup    | ply current                        | V <sub>DD</sub> = 3.465 V  | $\begin{array}{c} \text{SELA, SELB = H,} \\ \text{SEL} \overline{100} / 133 \text{ H} \rightarrow \text{L} \\ \hline \text{PWRDWN = H} \end{array}$                                                                           |          | 40   | mA   |

| I <sub>DD(PD)</sub> | PWRDWN state supply cu      | rrent                              | $V_{DD} = 3.465 V,$        | PWRDWN = L                                                                                                                                                                                                                    |          | 30   | mA   |

| I <sub>DD</sub>     | Dynamic supply current      |                                    | V <sub>DD</sub> = 3.465 V  |                                                                                                                                                                                                                               |          | 250  | mA   |

| Cl                  | Input capacitance‡          |                                    | $V_{DD} = 3.3 \text{ V},$  | $V_I = V_{DD}$ or GND                                                                                                                                                                                                         | 2        | 5    | pF   |

| C <sub>(XTAL)</sub> | Crystal terminal capacitane | ce                                 | V <sub>DD</sub> = 3.3 V,   | V <sub>I</sub> = 0.3 V                                                                                                                                                                                                        | 18       |      | pF   |

<sup>†</sup> All typical values are measured at their respective nominal V<sub>DD</sub> values.

<sup>&</sup>lt;sup>‡</sup> These parameters are ensured by design and lab characterization, not 100% production tested.

$<sup>{\</sup>sf Control\ SELx,\ \overline{PWRDWN},\ \overline{SPREAD}\ threshold\ levels\ d\underline{uring}\ FUNC\ w/c\ level\ tests.}$

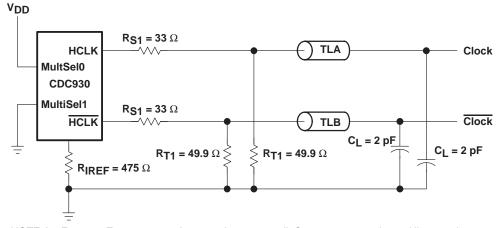

C<sub>L</sub> = MAX = 5 pF, R<sub>S</sub> = 33.2  $\Omega$ , R<sub>p</sub> = 49.9  $\Omega$  at HCLK/HCLK (Type X1) C<sub>L</sub> = MAX = 20 pF, R<sub>L</sub> = 500  $\Omega$  at 48 MHz, REF (Type 3) C<sub>L</sub> = MAX = 30 pF, R<sub>L</sub> = 500  $\Omega$  at PCIx, 3V66, 3VMREF, 3VMREF (Type 5)

SCAS641 - JULY 2000

## electrical characteristics over recommended operating free-air temperature range (unless otherwise noted) (continued)

## HCLK/HCLK (Type X1)

|    | PARAMETER                 |                                      | TEST CONDITIONS           |                             | MIN   | TYP† | MAX   | UNIT |

|----|---------------------------|--------------------------------------|---------------------------|-----------------------------|-------|------|-------|------|

|    |                           | $I_{ref} = 2.32 \text{ mA} \times 4$ | V <sub>DD</sub> = 3.135 V |                             | -8.1  |      |       | mA   |

|    |                           | ref = 2.32 mA × 4                    | V <sub>DD</sub> = 3.465 V | _                           |       |      | -10.5 | IIIA |

|    |                           | I <sub>ref</sub> = 2.32 mA × 5       | V <sub>DD</sub> = 3.135 V |                             | -10.1 |      |       | mA   |

|    |                           | ref = 2.32 mA × 3                    | V <sub>DD</sub> = 3.465 V | $V_{OH}$ at $Z = 50 \Omega$ |       |      | -13.1 | ША   |

| ЮН | High-level output current | 1 t = 2.22 mA v 6                    | V <sub>DD</sub> = 3.135 V | VOH at 2 = 30 32            | -12.1 |      |       | mA   |

|    |                           | $I_{ref} = 2.32 \text{ mA} \times 6$ | V <sub>DD</sub> = 3.465 V |                             |       |      | -15.7 | IIIA |

|    |                           | I <sub>ref</sub> = 2.32 mA × 7       | V <sub>DD</sub> = 3.135 V |                             | -14.1 |      |       | mA   |

|    |                           | ref = 2.32 mA × 7                    | V <sub>DD</sub> = 3.465 V |                             |       |      | -18.4 | IIIA |

| СО | Output capacitance‡       | $V_O = V_{DD}$ or GND                |                           |                             |       | 3.5  |       | pF   |

<sup>&</sup>lt;sup>†</sup> All typical values are measured at their respective nominal V<sub>DD</sub> values.

## 48MHz, REFx (Type 3), $C_L = 20$ pF, $R_L = 500 \Omega$

|      | PARAMETER                       | TEST CO                       | NDITIONS                 | MIN            | TYP† | MAX | UNIT |

|------|---------------------------------|-------------------------------|--------------------------|----------------|------|-----|------|

| Vон  | High-level output voltage       | V <sub>DD</sub> = min to max, | I <sub>OH</sub> = -1 mA  | VDD –<br>0.1 V |      |     | V    |

| 0    |                                 | V <sub>DD</sub> = 3.135 V,    | I <sub>OH</sub> = -14 mA | 2.4            |      |     |      |

| V/01 | Low-level output voltage        | V <sub>DD</sub> = min to max, | I <sub>OL</sub> = 1 mA   |                |      | 0.1 | V    |

| VOL  | Low-level output voltage        | $V_{DD} = 3.135 \text{ V},$   | $I_{OL} = 9 \text{ mA}$  |                |      | 0.4 | V    |

|      |                                 | $V_{DD} = 3.135 \text{ V},$   | V <sub>O</sub> = 1 V     | -29            |      |     |      |

| loh  | High-level output current       | $V_{DD} = 3.3 \text{ V},$     | V <sub>O</sub> = 1.65 V  |                | -41  |     | mA   |

|      |                                 | $V_{DD} = 3.465 \text{ V},$   | V <sub>O</sub> = 3.135 V |                |      | -23 |      |

|      |                                 | $V_{DD} = 3.135 \text{ V},$   | V <sub>O</sub> = 1.95 V  | 29             |      |     |      |

| IOL  | Low-level output current        | $V_{DD} = 3.3 \text{ V},$     | V <sub>O</sub> = 1.65 V  |                | 53   |     | mA   |

|      |                                 | V <sub>DD</sub> = 3.465 V,    | V <sub>O</sub> = 0.4 V   |                |      | 27  |      |

| СО   | Output capacitance <sup>‡</sup> | V <sub>DD</sub> = 3.3 V,      | $V_O = V_{DD}$ or GND    | 2              |      | 5   | pF   |

<sup>†</sup> All typical values are measured at their respective nominal VDD values.

#### PCIx, 3V66x, MREF/MREF (Type 5), $C_1 = 20$ pF, $R_1 = 500 \Omega$

| PARAMETER |                                 | TEST CO                       | TEST CONDITIONS          |                | TYP <sup>†</sup> | MAX | UNIT |

|-----------|---------------------------------|-------------------------------|--------------------------|----------------|------------------|-----|------|

| Vон       | High-level output voltage       | V <sub>DD</sub> = min to max, | I <sub>OH</sub> = -1 mA  | VDD –<br>0.1 V |                  |     | V    |

| 011       |                                 | $V_{DD} = 3.135 V,$           | I <sub>OH</sub> = -18 mA | 2.4            |                  |     |      |

| V/01      | Low lovel output voltage        | V <sub>DD</sub> = min to max, | I <sub>OL</sub> = 1 mA   |                |                  | 0.1 | V    |

| VOL       | Low-level output voltage        | $V_{DD} = 3.135 V,$           | $I_{OL} = 12 \text{ mA}$ |                |                  | 0.4 | V    |

|           |                                 | $V_{DD} = 3.135 V,$           | V <sub>O</sub> = 1 V     | -33            |                  |     |      |

| loh       | High-level output current       | $V_{DD} = 3.3 V,$             | V <sub>O</sub> = 1.65 V  |                | -53              |     | mA   |

|           |                                 | $V_{DD} = 3.465 V,$           | V <sub>O</sub> = 3.135 V |                |                  | -33 |      |

|           |                                 | $V_{DD} = 3.135 V,$           | V <sub>O</sub> = 1.95 V  | 30             |                  |     |      |

| $I_{OL}$  | Low-level output current        | $V_{DD} = 3.3 V,$             | V <sub>O</sub> = 1.65 V  |                | 70               |     | mA   |

|           |                                 | $V_{DD} = 3.465 V,$           | $V_0 = 0.4 \text{ V}$    |                |                  | 38  |      |

| СО        | Output capacitance <sup>‡</sup> | $V_{DD} = 3.3 V,$             | $V_O = V_{DD}$ or GND    | 2              |                  | 5   | pF   |

<sup>&</sup>lt;sup>†</sup> All typical values are measured at their respective nominal V<sub>DD</sub> values.

<sup>&</sup>lt;sup>‡</sup>These parameters are ensured by design and lab characterization, not 100% production tested.

<sup>&</sup>lt;sup>‡</sup> These parameters are ensured by design and lab characterization, not 100% production tested.

<sup>&</sup>lt;sup>‡</sup> These parameters are ensured by design and lab characterization, not 100% production tested.

SCAS641 - JULY 2000

## switching characteristics, V<sub>DD</sub> = MIN to MAX, T<sub>A</sub> = 0°C to 85°C

|                   | PARAMETER                           | FROM<br>(INPUT) | TO<br>(OUTPUT)       | TEST CONDITIONS                                                                          | MIN                                         | TYP                                         | MAX                  | UNIT |                                       |                                                                              |  |  |    |    |

|-------------------|-------------------------------------|-----------------|----------------------|------------------------------------------------------------------------------------------|---------------------------------------------|---------------------------------------------|----------------------|------|---------------------------------------|------------------------------------------------------------------------------|--|--|----|----|

| vover             | Overshoot <sup>‡</sup>              |                 |                      | HCLK/HCLK 0.7 V ampli-                                                                   |                                             |                                             | V <sub>OH</sub> +200 | mV   |                                       |                                                                              |  |  |    |    |

| Vunder            | Undershoot <sup>‡</sup>             |                 |                      | tude                                                                                     |                                             |                                             | V <sub>OL</sub> -200 | mv   |                                       |                                                                              |  |  |    |    |

| vover             | Overshoot <sup>‡</sup>              |                 |                      | Other clocks, C <sub>L</sub> = Worst                                                     | GND-0.7                                     |                                             |                      | V    |                                       |                                                                              |  |  |    |    |

| Vunder            | Undershoot <sup>‡</sup>             |                 | case                 |                                                                                          |                                             |                                             | V <sub>DD</sub> +0.7 | v    |                                       |                                                                              |  |  |    |    |

| t <sub>PZL</sub>  | Output enable time to low level     |                 |                      | f(HCL) = 100 or 133 MHz,<br>SELA, SELB = H,                                              |                                             |                                             | 100                  | ns   |                                       |                                                                              |  |  |    |    |

| <sup>t</sup> PZH  | Output enable time to high level    | SEL100/133      | HCLK/                | SEL $\overline{100}/133 L \rightarrow H$ , R <sub>ref</sub> = 475 $\Omega$               |                                             |                                             | 100                  | ns   |                                       |                                                                              |  |  |    |    |

| <sup>t</sup> PHZ  | Output disable time from high level | SEL100/133      | HCLK                 | HCLK                                                                                     | f(HCL) = 100 or 133 MHz,<br>SELA, SELB = H, |                                             |                      | 10   | ns                                    |                                                                              |  |  |    |    |

| <sup>t</sup> PLZ  | Output disable time from low level  |                 |                      | SEL $\overline{100}/133 \text{ H} \rightarrow \text{L},$ R <sub>ref</sub> = 475 $\Omega$ |                                             |                                             | 10                   | ns   |                                       |                                                                              |  |  |    |    |

| <sup>t</sup> PZL  | Output enable time to low level     |                 |                      | f(HCL) = 100 or 133 MHz,<br>SELA, SELB = H,                                              |                                             |                                             | 10                   | ns   |                                       |                                                                              |  |  |    |    |

| <sup>t</sup> PZH  | Output enable time to high level    | SEL100/133      | REF, 3V48<br>3VMREF, | ,                                                                                        | ,                                           | REF, 3V48<br>3VMREF,                        | ,                    | · '  | · · · · · · · · · · · · · · · · · · · | SEL $\overline{100}$ /133 L $\rightarrow$ H, R <sub>ref</sub> = 475 $\Omega$ |  |  | 10 | ns |

| <sup>t</sup> PHZ  | Output disable time from high level | SEL 100/133     | 3VMREF,<br>3V66, PCI | OVANDEE.                                                                                 | OVANDEE                                     | f(HCL) = 100 or 133 MHz,<br>SELA, SELB = H, | 10                   | ns   |                                       |                                                                              |  |  |    |    |

| tPLZ              | Output disable time from low level  |                 |                      | SEL $\overline{100}/133 \text{ H} \rightarrow \text{L},$ R <sub>ref</sub> = 475 $\Omega$ | → L,                                        |                                             | 10                   | ns   |                                       |                                                                              |  |  |    |    |

| t <sub>stab</sub> | Stabilization time†                 |                 |                      | After power up                                                                           |                                             |                                             | 3                    | ms   |                                       |                                                                              |  |  |    |    |

<sup>†</sup> Stabilization time is the time required for the integrated PLL circuit to obtain phase lock of its feedback signal to its reference signal. In order for phase lock to be obtained, a fixed-frequency, fixed-phase reference signal must be present a XIN. Until phase lock is obtained, the specifications for propagation delay and skew parameters given in the switching characteristics tables are not applicable. Stabilization time is defined as the time from when V<sub>DD</sub> achieves its nominal operating level until the output frequency is stable and operating within specification.

## HCLK/ $\overline{\text{HCLK}}$ (Type X1) C<sub>L</sub> = 2 pF, R<sub>L</sub> > 500 k $\Omega$

|                                 | PARAMETER                                | FROM<br>(INPUT)    | TO<br>(OUTPUT) | TEST CONDITIONS                                      | MIN        | TYP M | λX       | UNIT |

|---------------------------------|------------------------------------------|--------------------|----------------|------------------------------------------------------|------------|-------|----------|------|

|                                 | LICLIC algorithms with 4th               |                    |                | f(HCLK) = 100 MHz                                    | 10         | 10    | ).2      | no   |

| t <sub>C</sub>                  | HCLK clock period <sup>†</sup>           |                    |                | f(HCLK) = 133 MHz                                    | 7.5        | 7.    | 65       | ns   |

| <sup>t</sup> jit(cc)            | Cycle to cycle jitter                    |                    |                | f(HCLK = 100 or 133 MHz                              |            | 2     | 00       | ps   |

| t <sub>dc</sub>                 | Duty cycle                               |                    |                | f(HCLK) = 100 or 133 MHz crossing point              | 45%        | 55    | 5%       |      |

| t <sub>sk(o)</sub>              | HCLK bus skew                            | HCLKx              | HCLKx          | f(HCLK) = 100 or 133 MHz crossing point              |            | 1     | 50       | ps   |

|                                 | Pulse duration width                     |                    |                | f(HCLK = 100 MHz                                     | 4.41       |       |          | no   |

| t <sub>W</sub>                  | Pulse duration width                     |                    |                | f(HCLK = 133 MHz                                     | 3.29       |       |          | ns   |

| t <sub>r</sub>                  | Rise time‡                               |                    |                | V <sub>O</sub> = 0.14 V to 0.56 V                    | 175        | 7     | 00       | ps   |

| t <sub>f</sub>                  | Fall time‡                               | 0.7 V<br>amplitude |                | V <sub>O</sub> = 0.14 V to 0.56 V                    | 175        | 7     | 00       | ps   |

| t <sub>r</sub> , t <sub>f</sub> | Rise and fall time matching <sup>‡</sup> | ampillade          |                | $2 \times (t_{\Gamma} - t_{f})/(t_{\Gamma} + t_{f})$ |            | 20    | %        |      |

| v <sub>cross</sub>              | Cross point voltages‡                    | 0.7 V<br>amplitude |                | f(HCLK) = 100 or 133 MHz<br>HCLK and HCLK            | 40%<br>VOH |       | 5%<br>DH | V    |

<sup>†</sup> The average over any 1-μs period of time is greater than the minimum specified period.

<sup>&</sup>lt;sup>‡</sup> These parameters are ensured by design and lab characterization, not 100% production tested.

<sup>&</sup>lt;sup>‡</sup> These parameters are ensured by design and lab characterization, not 100% production tested.

SCAS641 - JULY 2000

## switching characteristics, $V_{DD} = 3.135 \text{ V}$ to 3.465 V, $T_A = 0^{\circ}\text{C}$ to 85°C (continued)

# 3VMREF/3VMREF (Type 5) C<sub>L</sub> = 30 pF, R<sub>L</sub> = 500 $\Omega$

|                      | PARAMETER                            | FROM<br>(INPUT)   | TO<br>(OUTPUT)    | TEST CONDITIONS                                                                           | MIN | TYP | MAX  | UNIT |

|----------------------|--------------------------------------|-------------------|-------------------|-------------------------------------------------------------------------------------------|-----|-----|------|------|

|                      | 3VMREF/3VMREF clock                  |                   |                   | f(3VMREF/3VMREF) = 50 MHz                                                                 | 20  |     | 20.4 | ns   |

| t <sub>C</sub>       | period†                              |                   |                   | f(3VMREF/3VMREF) = 66 MHz                                                                 | 15  |     | 15.3 | ns   |

| <sup>t</sup> jit(cc) | Cycle to cycle jitter                |                   |                   | f(3VMREF/3VMREF) = 66 MHz,<br>f(HCLK) = 100 or 133 MHz,<br>VDD = 3.3 V, Measured at 1.5 V |     |     | 250  | ps   |

| t <sub>dc</sub>      | Duty cycle                           |                   |                   | f(3VMREF/3VMREF) = 66 MHz                                                                 | 45% |     | 55%  |      |

| t <sub>sk(o)</sub>   | 3VMREF/3VMREF output skew            | 3VMREF/<br>3VMREF | 3VMREF/<br>3VMREF | f(3VMREF/3VMREF) = 66 MHz,<br>f(HCLK) = 100 or 133 MHz,<br>VDD = 3.3 V, Measured at 1.5 V |     |     | 250  | ps   |

| t(off)               | 3VMREF/3VMREF clock<br>to PCI offset | 3VMREF/<br>3VMREF | PCIx              | f(3VMREF/3VMREF) = 66 MHz,<br>Measured points at 1.5 V,<br>Measured at rising edges       |     |     | 3    | ns   |

| t <sub>r</sub>       | Rise time                            |                   |                   | V <sub>O</sub> = 0.4 V to 2.4 V                                                           | 0.5 |     | 2    | ns   |

| tf                   | Fall time                            |                   |                   | V <sub>O</sub> = 0.4 V to 2.4 V                                                           | 0.5 |     | 2    | ns   |

<sup>†</sup> The average over any 1-µs period of time is greater than the minimum specified period.

## 3V66 (Type 5, No SSC), $C_L$ = 30 pF, $R_L$ = 500 $\Omega$

|                      | PARAMETER                      | FROM<br>(INPUT) | TO<br>(OUTPUT) | TEST CONDITIONS                                                                  | MIN | TYP   | MAX | UNIT |

|----------------------|--------------------------------|-----------------|----------------|----------------------------------------------------------------------------------|-----|-------|-----|------|

| t <sub>C</sub>       | 3V66 clock period <sup>†</sup> |                 |                | f(3V66)= 66 MHz                                                                  |     | 15.03 |     | ns   |

| <sup>t</sup> jit(cc) | Cycle to cycle jitter          |                 |                | f(3V66) = 66 MHz,<br>f(HCLK) = 100 or 133 MHz,<br>VDD = 3.3 V, Measured at 1.5 V |     |       | 300 | ps   |

| t <sub>dc</sub>      | Duty cycle                     |                 |                | f(3V66) = 66 MHz                                                                 | 45% |       | 55% |      |

| <sup>t</sup> sk(o)   | 3V66 output skew               | 3V66x           | 3V66x          | f(3V66) = 66 MHz,<br>f(HCLK) = 100 or 133 MHz,<br>VDD = 3.3 V, Measured at 1.5 V |     |       | 250 | ps   |

| <sup>t</sup> (off)   | 3V66 clock to PCI              | 3V66x           | PCIx           | f(3V66) = 66 MHz,<br>Measured points at 1.5 V,<br>Measured at rising edges       | 1.5 |       | 3.5 | ns   |

| t <sub>r</sub>       | Rise time                      |                 |                | V <sub>O</sub> = 0.4 V to 2.4 V                                                  | 0.5 |       | 2   | ns   |

| t <sub>f</sub>       | Fall time                      |                 |                | V <sub>O</sub> = 0.4 V to 2.4 V                                                  | 0.5 |       | 2   | ns   |

<sup>†</sup> The average over any 1-µs period of time is greater than the minimum specified period.

# PCI (Type 5), C<sub>L</sub> = 30 pF, R<sub>L</sub> = 500 $\Omega$

|                    | PARAMETER                     | FROM<br>(INPUT) | TO<br>(OUTPUT) | TEST CONDITIONS                 | MIN | TYP   | MAX | UNIT |

|--------------------|-------------------------------|-----------------|----------------|---------------------------------|-----|-------|-----|------|

| t <sub>C</sub>     | PCI clock period <sup>†</sup> |                 |                | f <sub>(PCI)</sub> = 33.3 MHz   |     | 30.06 |     | ns   |

| tjit(cc)           | Cycle to cycle jitter         |                 |                | f(HCLK) = 100 or 133 MHz        |     |       | 500 | ps   |

| t <sub>dc</sub>    | Duty cycle                    |                 |                | f <sub>(PCI)</sub> = 33.3 MHz   | 45% |       | 55% |      |

| t <sub>sk(o)</sub> | PCI output skew               | PCIx            | PCIx           | f(PCI) = 33.3 MHz               |     |       | 500 | ps   |

| t <sub>r</sub>     | Rise time                     |                 |                | V <sub>O</sub> = 0.4 V to 2.4 V | 0.5 |       | 2   | ns   |

| tf                 | Fall time                     |                 |                | V <sub>O</sub> = 0.4 V to 2.4 V | 0.5 |       | 2   | ns   |

<sup>†</sup> The average over any  $1-\mu s$  period of time is greater than the minimum specified period.

SCAS641 - JULY 2000

# switching characteristics, $V_{DD}$ = 3.135 V to 3.465 V, $T_A$ = 0°C to 85°C (continued)

# 3V48 (Type 3), C<sub>L</sub> = 20 pF, R<sub>L</sub> = 500 $\Omega$

|                      | PARAMETER             | FROM<br>(INPUT) | TO<br>(OUTPUT) | TEST CONDITIONS                                                                                                                                   | MIN | TYP   | MAX | UNIT |

|----------------------|-----------------------|-----------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|-----|------|

| t <sub>C</sub>       | 3V48 clock period†    |                 |                | f(3V48)= 48 MHz                                                                                                                                   |     | 15.03 |     | ns   |

| <sup>t</sup> jit(cc) | Cycle to cycle jitter |                 |                | f <sub>(3V48)</sub> = 48 MHz,<br>f <sub>(HCLK)</sub> = 100 or 133 MHz,<br>V <sub>DD</sub> = 3.3 V, Measured at 1.5 V                              |     |       | 350 | ps   |

| t <sub>dc</sub>      | Duty cycle            |                 |                | f(3V48) = 48 MHz                                                                                                                                  | 45% |       | 55% |      |

| tsk(o)               | 3V48 output skew      | 3V48x           | 3V48x          | $f_{(3V48)} = 48 \text{ MHz},$<br>$f_{(HCLK)} = 100 \text{ or } 133 \text{ MHz},$<br>$V_{DD} = 3.3 \text{ V}, \text{ Measured at } 1.5 \text{ V}$ |     |       | 250 | ps   |

| t(off)               | 3V48 clock to PCI     | 3V48x           | PCIx           | f(3V48) = 48 MHz,<br>Measured points at 1.5 V,<br>Measured at rising edges                                                                        | 1.5 |       | 3.5 | ns   |

| t <sub>r</sub>       | Rise time             |                 |                | V <sub>O</sub> = 0.4 V to 2.4 V                                                                                                                   | 1   |       | 4   | ns   |

| t <sub>f</sub>       | Fall time             |                 |                | V <sub>O</sub> = 0.4 V to 2.4 V                                                                                                                   | 1   |       | 4   | ns   |

<sup>†</sup> The average over any 1–µs period of time is greater than the minimum specified period.

# REF (Type 3), C<sub>L</sub> = 20 pF, R<sub>L</sub> = 500 $\Omega$

|                 | PARAMETER             | TEST CONDITIONS                         | MIN | TYP   | MAX | UNIT |

|-----------------|-----------------------|-----------------------------------------|-----|-------|-----|------|

| t <sub>C</sub>  | REF clock period†     | f(REF)= 14.318 MHz                      |     | 69.84 |     | ns   |

| tjit(cc)        | Cycle to cycle jitter | f(HCLK) = 100 or 133 MHz                |     |       | 1   | ps   |

| t <sub>dc</sub> | Duty cycle            | f(REF) = 14.318  MHz                    | 52% |       | 62% |      |

| t <sub>r</sub>  | Rise time             | $V_0 = 0.4 \text{ V to } 2.4 \text{ V}$ | 1   |       | 4   | ns   |

| tf              | Fall time             | V <sub>O</sub> = 0.4 V to 2.4 V         | 1   |       | 4   | ns   |

<sup>†</sup> The average over any 1-μs period of time is greater than the minimum specified period.

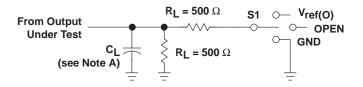

| TEST      | S1                     |

|-----------|------------------------|

| tPLH/tPHL | Open                   |

| tPLZ/tPZL | V <sub>ref</sub> (OFF) |

| tPHZ/tPZH | GND                    |

LOAD CIRCUIT of single-ended outputs for tpd and tsk

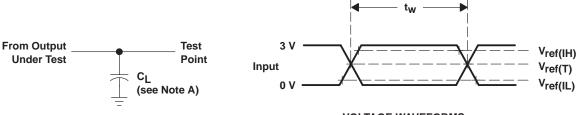

LOAD CIRCUIT of single-ended outputs for tr and tf

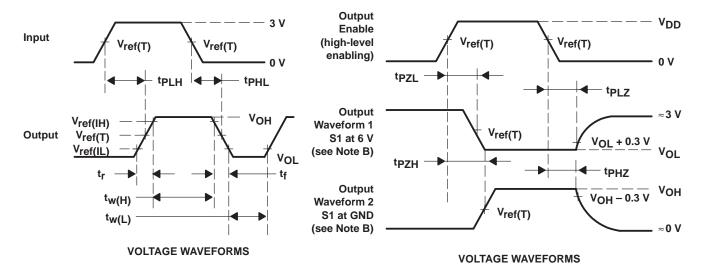

NOTES: A. CL includes probe and jig capacitance. CL = 2 pF (HCLK, HCLK), CL = 20 pF (48MHZ, REF), CL = 30 pF (PCIx, 3VMREF, 3V66).

- B. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control. Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

- C. All input pulses are supplied by generators having the following characteristics: PRR  $\leq$  14.318 MHz,  $Z_O = 50 \Omega$ ,  $t_r \leq 2.5 \text{ ns}$ ,  $t_f \le 2.5 \text{ ns.}$

- D. The outputs are measured one at a time with one transition per measurement.

|                        | PARAMETER                         | 3.3-V INTERFACE | 2.5-V INTERFACE | UNIT |

|------------------------|-----------------------------------|-----------------|-----------------|------|

| V <sub>ref(IH)</sub>   | High-level reference voltage      | 2.4             | 2               | V    |

| V <sub>ref(IL)</sub>   | Low-level reference voltage       | 0.4             | 0.4             | V    |

| V <sub>ref(T)</sub>    | Input threshold reference voltage | 1.5             | 1.25            | V    |

| V <sub>ref</sub> (OFF) | Off-state reference voltage       | 6               | 4.6             | V    |

Figure 1. Load Circuit and Voltage Waveforms

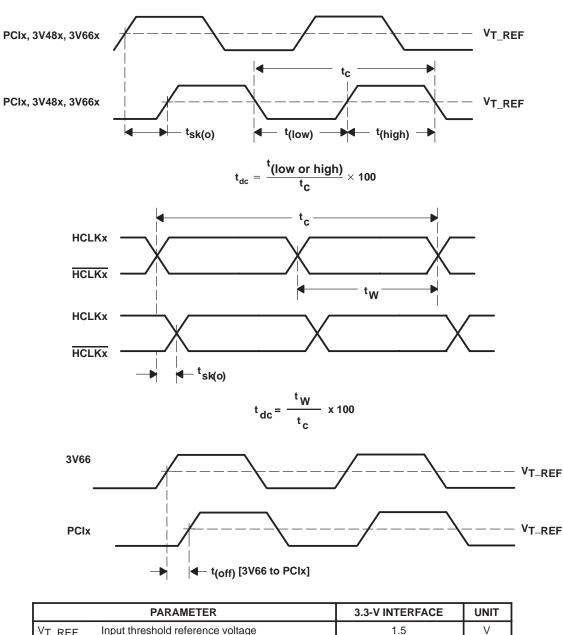

|        | PARAMETER                         | 3.3-V INTERFACE | UNIT |

|--------|-----------------------------------|-----------------|------|

| VT_REF | Input threshold reference voltage | 1.5             | V    |

Figure 2. Waveforms for Calculation of Output Skew, Duty Cycle, and Offset

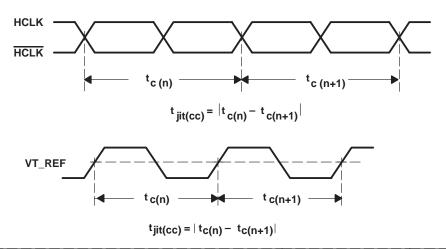

|        | PARAMETER                         | 3.3-V INTERFACE | UNIT |

|--------|-----------------------------------|-----------------|------|

| VT_REF | Input threshold reference voltage | 1.5             | V    |

Figure 3. Waveforms for Calculation of Cycle-Cycle Jitter

Figure 4. Power DOWN Timing

NOTE A:  $Z_{(TLA)} = Z_{(TLB)} = 50 \Omega$ ,  $L_{(TLA)} = L_{(TLB)} = 3.5$ ",  $C_L$  represents probe and jig capacitance.

Figure 5. Load Circuit for 0.7 V Amplitude HCLK/HCLK Bus

SCAS641 - JULY 2000

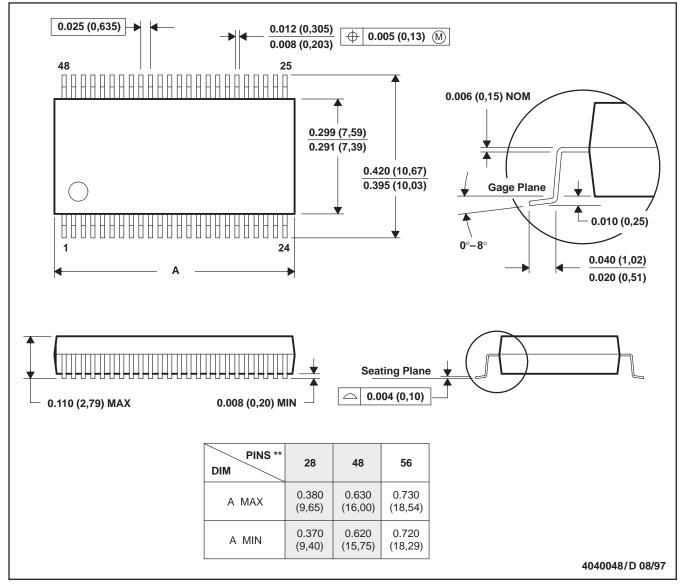

#### **MECHANICAL DATA**

## DL (R-PDSO-G\*\*)

#### **48-PIN SHOWN**

### PLASTIC SMALL-OUTLINE PACKAGE

NOTES: A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion not to exceed 0.006 (0,15).

- D. Falls within JEDEC MO-118

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Customers are responsible for their applications using TI components.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 2000, Texas Instruments Incorporated