# M28C64 64 Kbit (8K x 8) Parallel EEPROM With Software Data Protection

- Fast Access Time:

- 90 ns at V<sub>CC</sub>=5 V for M28C64 and M28C64-A

- 120 ns at V<sub>CC</sub>=3 V for M28C64-xxW

- Single Supply Voltage:

- 4.5 V to 5.5 V for M28C64 and M28C64-A

- 2.7 V to 3.6 V for M28C64-xxW

- Low Power Consumption

- Fast BYTE and PAGE WRITE (up to 64 Bytes)

- 1 ms at V<sub>CC</sub>=4.5 V for M28C64-A

- 3 ms at V\_CC=4.5 V for M28C64

- 5 ms at V\_CC=2.7 V for M28C64-xxW

- Enhanced Write Detection and Monitoring:

- Ready/Busy Open Drain Output

- Data Polling

- Toggle Bit

- Page Load Timer Status

- JEDEC Approved Bytewide Pin-Out

- Software Data Protection

- 100000 Erase/Write Cycles (minimum)

- Data Retention (minimum):

- 40 Years for M28C64 and M28C64-xxW

- 10 Years for M28C64-A

### Table 1. Signal Names

| A0-A12          | Address Input       |

|-----------------|---------------------|

| DQ0-DQ7         | Data Input / Output |

| W               | Write Enable        |

| Ē               | Chip Enable         |

| G               | Output Enable       |

| RB              | Ready / Busy        |

| Vcc             | Supply Voltage      |

| V <sub>SS</sub> | Ground              |

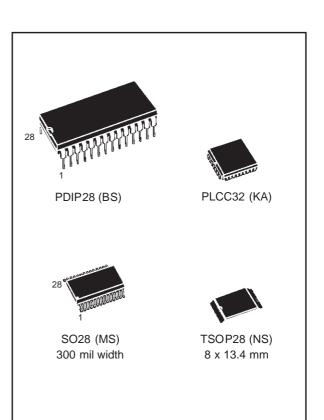

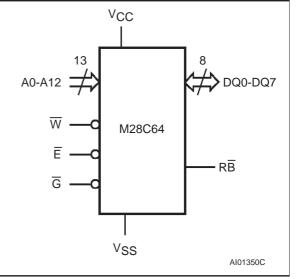

# Figure 1. Logic Diagram

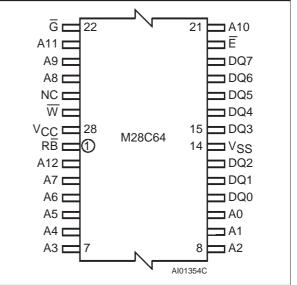

Figure 2A. DIP Connections

| RB <b>[</b> 1   | $\cup$   | 28 <b>]</b> ∨_CC |

|-----------------|----------|------------------|

| A12 🛾 2         |          | 27 🛛 🕅           |

| A7 🕻 3          |          | 26 🛛 NC          |

| A6 🕻 4          |          | 25 🛛 A8          |

| A5 🚺 5          |          | 24 🛿 A9          |

| A4 🕻 6          |          | 23 🛛 A11         |

| A3 🛽 7          | M28C64   | 22 🛛 🖸           |

| A2 🕻 8          | 10120004 | 21 🛛 A10         |

| A1 🕻 9          |          | 20 🛛 Ē           |

| A0 🚺 10         |          | 19 🛛 DQ7         |

| DQ0 🕻 11        |          | 18 🛛 DQ6         |

| DQ1 🚺 12        |          | 17 🛛 DQ5         |

| DQ2 🚺 13        |          | 16 🛛 DQ4         |

| Vss <b>[</b> 14 |          | 15 🛛 DQ3         |

|                 | AIO      | 1351C            |

|                 |          |                  |

Note: 1. NC = Not Connected

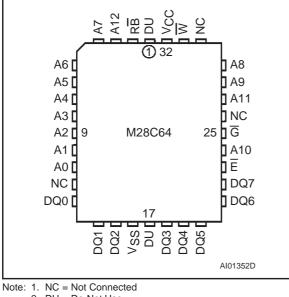

#### Figure 2B. PLLC Connections

#### 2. DU = Do Not Use

#### DESCRIPTION

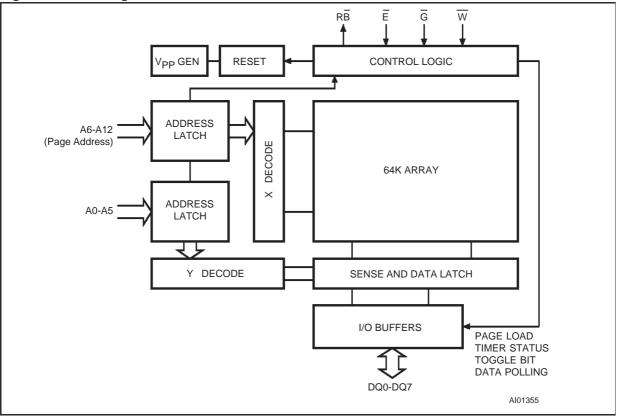

The M28C64 devices consist of 8192x8 bits of low power, parallel EEPROM, fabricated with STMicroelectronics' proprietary single polysilicon CMOS technology. The devices offer fast access time, with low power dissipation, and require a single voltage supply (5V or 3V, depending on the option chosen).

The device has been designed to offer a flexible microcontroller interface, featuring both hardware

#### Figure 2C. SO Connections

Note: 1. NC = Not Connected

#### Figure 2D. TSOP Connections

Note: 1. NC = Not Connected

and software handshaking, with Ready/Busy, Data Polling and Toggle Bit. The device supports a 64 byte Page Write operation. Software Data Protection (SDP) is also supported, using the standard JEDEC algorithm.

| Symbol           | Parameter                                                       | Value                        | Unit |

|------------------|-----------------------------------------------------------------|------------------------------|------|

| T <sub>A</sub>   | Ambient Operating Temperature                                   | -40 to 125                   | °C   |

| T <sub>STG</sub> | Storage Temperature                                             | -65 to 150                   | °C   |

| V <sub>CC</sub>  | Supply Voltage                                                  | -0.3 to V <sub>CC</sub> +1   | V    |

| V <sub>IO</sub>  | Input or Output Voltage                                         | -0.6 to V <sub>CC</sub> +0.6 | V    |

| VI               | Input Voltage                                                   | -0.3 to 6.5                  | V    |

| V <sub>ESD</sub> | Electrostatic Discharge Voltage (Human Body model) <sup>2</sup> | 4000                         | V    |

Table 2. Absolute Maximum Ratings <sup>1</sup>

Note: 1. Except for the rating "Operating Temperature Range", stresses above those listed in the Table "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and operation of the device at these or any other conditions above those indicated in the Operating sections of this specification is not implied. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability. Refer also to the ST SURE Program and other relevant quality documents.

2. MIL-STD-883C, 3015.7 (100 pF, 1500 Ω)

#### Figure 3. Block Diagram

#### Table 3. Operating Modes <sup>1</sup>

| Mode           | Ē | G | W | DQ0-DQ7  |

|----------------|---|---|---|----------|

| Stand-by       | 1 | Х | Х | Hi-Z     |

| Output Disable | Х | 1 | Х | Hi-Z     |

| Write Disable  | Х | Х | 1 | Hi-Z     |

| Read           | 0 | 0 | 1 | Data Out |

| Write          | 0 | 1 | 0 | Data In  |

| Chip Erase     | 0 | V | 0 | Hi-Z     |

Note: 1.  $0=V_{IL}$ ;  $1=V_{IH}$ ;  $X = V_{IH}$  or  $V_{IL}$ ;  $V=12V \pm 5\%$ .

#### SIGNAL DESCRIPTION

The external connections to the device are summarized in Table 1, and their use in Table 3.

Addresses (A0-A12). The address inputs are used to select one byte from the memory array during a read or write operation.

**Data In/Out (DQ0-DQ7).** The contents of the data byte are written to, or read from, the memory array through the Data I/O pins.

**Chip Enable**  $(\overline{E})$ . The chip enable input must be held low to enable read and write operations. When Chip Enable is high, power consumption is reduced.

**Output Enable** ( $\overline{\mathbf{G}}$ ). The Output Enable input controls the data output buffers, and is used to initiate read operations.

Write Enable ( $\overline{W}$ ). The Write Enable input controls whether the addressed location is to be read, from or written to.

**Ready/Busy** (**RB**). Ready/Busy is an open drain output that can be used to detect the end of the internal write cycle.

#### **DEVICE OPERATION**

In order to prevent data corruption and inadvertent write operations, an internal V<sub>CC</sub> comparator inhibits the Write operations if the V<sub>CC</sub> voltage is lower than V<sub>WI</sub> (see Table 4A and Table 4B). Once the voltage applied on the V<sub>CC</sub> pin goes over the V<sub>WI</sub> threshold (V<sub>CC</sub>>V<sub>WI</sub>), write access to the memory is allowed after a time-out t<sub>PUW</sub>, as specified in Table 4A and Table 4B.

Further protection against data corruption is offered by the  $\overline{E}$  and  $\overline{W}$  low pass filters: any glitch, on the  $\overline{E}$  and  $\overline{W}$  inputs, with a pulse width less than 10 ns (typical) is internally filtered out to prevent inadvertent write operations to the memory.

| Symbol           | Parameter                                                 | Min. | Max. | Unit |

|------------------|-----------------------------------------------------------|------|------|------|

| t <sub>PUR</sub> | Time Delay to Read Operation                              |      | 1    | μs   |

| t <sub>PUW</sub> | Time Delay to Write Operation (once $V_{CC} \ge V_{WI}$ ) |      | 10   | ms   |

| V <sub>WI</sub>  | Write Inhibit Threshold                                   | 3.0  | 4.2  | V    |

Table 4A. Power-Up Timing<sup>1</sup> for M28C64 (5V range) ( $T_A = 0$  to 70 °C or -40 to 85 °C or -40 to 125 °C;  $V_{CC} = 4.5$  to 5.5 V)

Note: 1. Sampled only, not 100% tested.

# Table 4B. Power-Up Timing<sup>1</sup> for M28C64-xxW (3V range)

$(T_A = 0 \text{ to } 70 \text{ °C or } -40 \text{ to } 85 \text{ °C}; V_{CC} = 2.7 \text{ to } 3.6 \text{ V})$

| Symbol                                  | Parameter                                                           | Min. | Max. | Unit |

|-----------------------------------------|---------------------------------------------------------------------|------|------|------|

| t <sub>PUR</sub>                        | Time Delay to Read Operation                                        |      | 1    | μs   |

| t <sub>PUW</sub>                        | $t_{PUW}$ Time Delay to Write Operation (once $V_{CC} \ge V_{WI}$ ) |      | 15   | ms   |

| V <sub>WI</sub> Write Inhibit Threshold |                                                                     | 1.5  | 2.5  | V    |

Note: 1. Sampled only, not 100% tested.

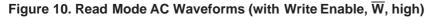

#### Read

The device is accessed like a static RAM. When  $\overline{E}$  and  $\overline{G}$  are low, and  $\overline{W}$  is high, the contents of the addressed location are presented on the I/O pins. Otherwise, when either  $\overline{G}$  or  $\overline{E}$  is high, the I/O pins revert to their high impedance state.

#### Write

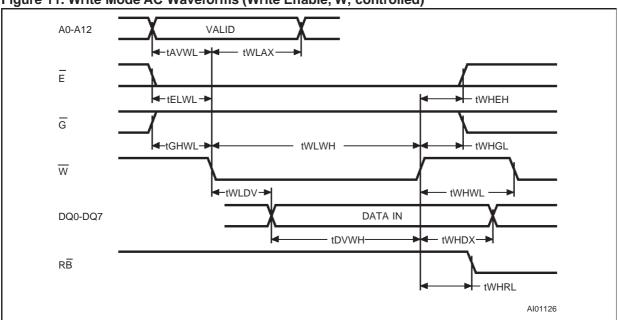

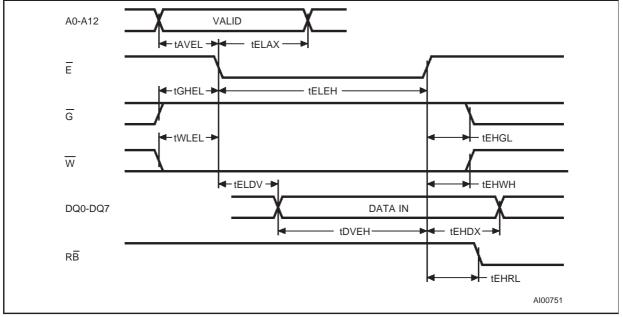

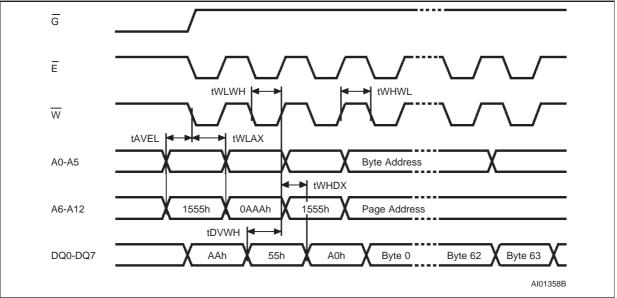

Write operations are initiated when both  $\overline{W}$  and  $\overline{E}$ are low and  $\overline{G}$  is high. The device supports both  $\overline{W}$ -controlled and  $\overline{E}$ -controlled write cycles (as shown in Figure 11 and Figure 12). The address is latched during the falling edge of  $\overline{W}$  or  $\overline{E}$  (which ever occurs later) and the data is latched on the rising edge of  $\overline{W}$  or  $\overline{E}$  (which ever occurs first). After a delay, t<sub>WLQ5H</sub>, that cannot be shorter than the value specified in Table 10A to Table 10C, the internal write cycle starts. It continues, under internal timing control, until the write operation is complete. The commencement of this period can be detected by reading the Page Load Timer Status on DQ5. The end of the cycle can be detected by reading the status of the Data Polling and the Toggle Bit functions on DQ7 and DQ6.

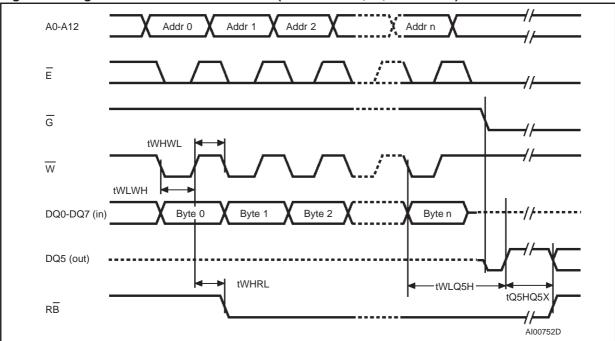

#### Page Write

<u>ک</u>

The Page Write mode allows up to 64 bytes to be written on a single page in a single go. This is achieved through a series of successive Write operations, no two of which are separated by more than the  $t_{WLQ5H}$  value (as specified in Table 10A to Table 10C).

All bytes must be located on the same page address (A12-A6 must be the same for all bytes).

The internal write cycle can start at any instant after  $t_{WLQ5H}$ . Once initiated, the write operation is internally timed, and continues, uninterrupted, until completion.

As with the single byte Write operation, described above, the DQ5, DQ6 and DQ7 lines can be used to detect the beginning and end of the internally controlled phase of the Page Write cycle.

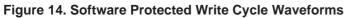

#### Software Data Protection (SDP)

The device offers a software-controlled writeprotection mechanism that allows the user to inhibit all write operations to the device. This can be useful for protecting the memory from inadvertent write cycles that may occur during periods of instability (uncontrolled bus conditions when excessive noise is detected, or when power supply levels are outside their specified values).

By default, the device is shipped in the "unprotected" state: the memory contents can be freely changed by the user. Once the Software Data Protection Mode is enabled, all write commands are ignored, and have no effect on the memory contents.

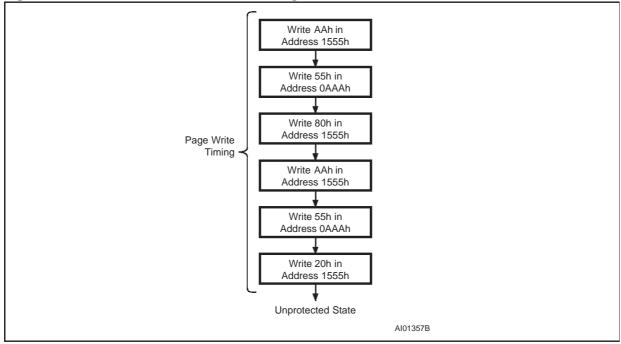

The device remains in this mode until a valid Software Data Protection disable sequence is received. The device reverts to its "unprotected" state.

The status of the Software Data Protection (enabled or disabled) is represented by a non-

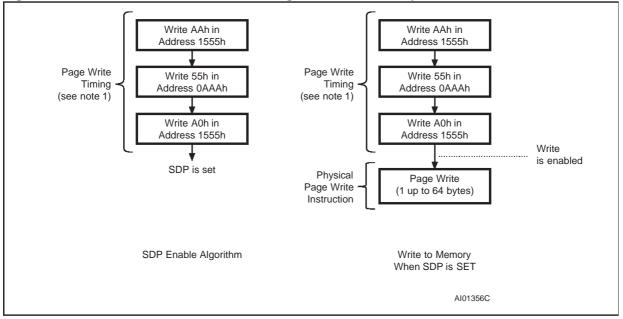

#### Figure 4. Software Data Protection Enable Algorithm and Memory Write

Note: 1. The most significant address bits (A12 to A6) differ during these specific Page Write operations.

volatile latch, and is remembered across periods of the power being off.

The Software Data Protection Enable command consists of the writing of three specific data bytes to three specific memory locations (each location being on a different page), as shown in Figure 4.

Similarly to disable the Software Data Protection, the user has to write specific data bytes into six different locations, as shown in Figure 5. This complex series of operations protects against the chance of inadvertent enabling or disabling of the Software Data Protection mechanism.

When SDP is enabled, the memory array can still have data written to it, but the sequence is more complex (and hence better protected from inadvertent use). The sequence is as shown in Figure 4. This consists of an unlock key, to enable the write action, at the end of which the SDP continues to be enabled. This allows the SDP to be enabled, and data to be written, within a single Write cycle ( $t_{WC}$ ).

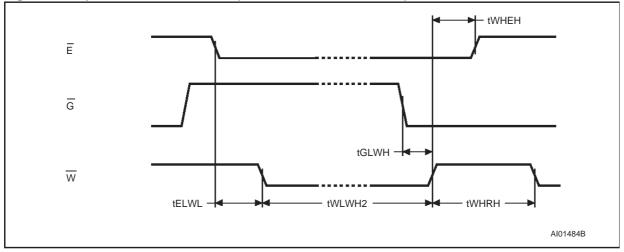

#### Software Chip Erase

Using this function, available on the M28C64 but not on the M28C64-A or M28C64-xxW, the contents of the entire memory are erased (set to FFh) by holding Chip Enable ( $\overline{E}$ ) low, and holding Output Enable ( $\overline{G}$ ) at V<sub>CC</sub>+7.0V. The chip is cleared when <u>a</u> 10 ms low pulse is applied to the Write Enable ( $\overline{W}$ ) signal (see Figure 7 and Table 5 for details).

#### **Status Bits**

The devices provide three status bits (DQ7, DQ6 and DQ5), and one output pin (RB), for use during write operations. These allow the application to use the write time latency of the device for getting on with other work. These signals are available on the I/O port bits DQ7, DQ6 and DQ5 (but only during programming cycle, once a byte or more has been latched into the memory) or continuously on the RB output pin.

**Data Polling bit (DQ7).** The internally timed write cycle starts after  $t_{WLQ5H}$  (defined in Table 10A to Table 10C) has elapsed since the previous byte was latched in to the memory. The value of the DQ7 bit of this last byte, is used as a signal

Figure 6. Status Bit Assignment

| DQ7                                                                                                       | DQ6 | DQ5  | DQ4  | DQ3  | DQ2  | DQ1  | DQ0  |  |

|-----------------------------------------------------------------------------------------------------------|-----|------|------|------|------|------|------|--|

| DP                                                                                                        | ΤB  | PLTS | Hi-Z | Hi-Z | Hi-Z | Hi-Z | Hi-Z |  |

| DP = Data Polling<br>TB = Toggle Bit<br>PLTS = Page Load Timer Status<br>Hi-Z = High impedance<br>Al02815 |     |      |      |      |      |      |      |  |

<u>//ک</u>

throughout this write operation: it is inverted while the internal write operation is underway, and is inverted back to its original value once the operation is complete.

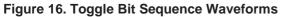

**Toggle bit (DQ6).** The device offers another way for determining when the internal write cycle is completed. During the internal Erase/Write cycle, DQ6 toggles from '0' to '1' and '1' to '0' (the first read value being '0') on subsequent attempts to read any byte of the memory. When the internal write cycle is complete, the toggling is stopped, and the values read on DQ7-DQ0 are those of the addressed memory byte. This indicates that the device is again available for new Read and Write operations.

**Page Load Timer Status bit (DQ5).** An internal timer is used to measure the period between successive Write operations, up to  $t_{WLQ5H}$  (defined in Table 10A to Table 10C). The DQ5 line is held low to show when this timer is running (hence showing that the device has received one write operation, and is waiting for the next). The DQ5 line is held high when the counter has

overflowed (hence showing that the device is now starting the internal write to the memory array).

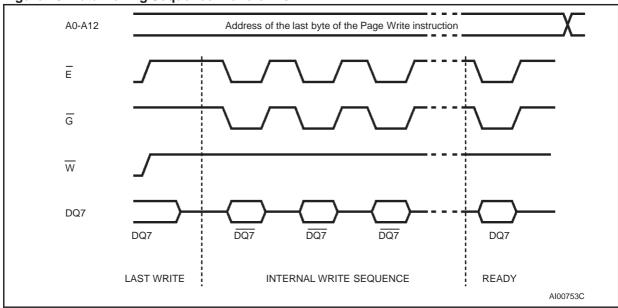

**Ready/Busy pin.** The  $R\overline{B}$  pin is an open drain output that is held low during the erase/write cycle, and that is released (allowed to float) at the completion of the programming cycle.

| Table 5. Chip Erase AC Characteristics <sup>1</sup> for M28C64 and M28C64-xxW                                                                                                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $(T_A = 0 \text{ to } 70 \degree \text{C} \text{ or } -40 \text{ to } 85 \degree \text{C} \text{ or } -40 \text{ to } 125 \degree \text{C}; V_{CC} = 4.5 \text{ to } 5.5 \text{ V})$ |

| $(T_{A} = 0 \text{ to } 70 ^{\circ}\text{C} \text{ or } -40 \text{ to } 85 ^{\circ}\text{C}: V_{CC} = 2.7 \text{ to } 3.6 \text{ V})$                                                |

| Symbol            | Parameter                              | Test Condition               | Min. | Max. | Unit |  |

|-------------------|----------------------------------------|------------------------------|------|------|------|--|

| t <sub>ELWL</sub> | Chip Enable Low to Write Enable Low    | $\overline{G} = V_{CC} + 7V$ | 1    |      | μs   |  |

| twhen             | Write Enable High to Chip Enable High  | $\overline{G} = V_{CC} + 7V$ | 0    |      | ns   |  |

| twLwH2            | Write Enable Low to Write Enable High  | $\overline{G} = V_{CC} + 7V$ | 10   |      | ms   |  |

| tglwh             | Output Enable Low to Write Enable High | $\overline{G} = V_{CC} + 7V$ | 1    |      | μs   |  |

| twhrh             | Write Enable High to Write Enable Low  | $\overline{G} = V_{CC} + 7V$ |      | 3    | ms   |  |

Note: 1. Sampled only, not 100% tested.

# Table 6A. Read Mode DC Characteristics for M28C64 and M28C64-A (5V range) (T<sub>A</sub> = 0 to 70 °C or -40 to 85 °C or -40 to 125 °C; V<sub>CC</sub> = 4.5 to 5.5 V)

| Symbol                        | Parameter                      | Test Condition                                                    | Min. | Max.                  | Unit |

|-------------------------------|--------------------------------|-------------------------------------------------------------------|------|-----------------------|------|

| ILI                           | Input Leakage Current          | $0 \ V \leq V_{IN} \leq V_{CC}$                                   |      | 10                    | μΑ   |

| I <sub>LO</sub>               | Output Leakage Current         | $0 V \le V_{OUT} \le V_{CC}$                                      |      | 10                    | μΑ   |

| I <sub>CC</sub> <sup>1</sup>  | Supply Current (TTL inputs)    | $\overline{E}$ = V_{IL}, $\overline{G}$ = V_{IL} , f = 5 MHz      |      | 30                    | mA   |

| ICC                           | Supply Current (CMOS inputs)   | $\overline{E} = V_{IL}, \overline{G} = V_{IL}, f = 5 \text{ MHz}$ |      | 25                    | mA   |

| I <sub>CC1</sub> <sup>1</sup> | Supply Current (Stand-by) TTL  | Ē = V <sub>IH</sub>                                               |      | 1                     | mA   |

| I <sub>CC2</sub> <sup>1</sup> | Supply Current (Stand-by) CMOS | $\overline{E}$ > V <sub>CC</sub> - 0.3V                           |      | 100                   | μΑ   |

| VIL                           | Input Low Voltage              |                                                                   | -0.3 | 0.8                   | V    |

| V <sub>IH</sub>               | Input High Voltage             |                                                                   | 2    | V <sub>CC</sub> + 0.5 | V    |

| V <sub>OL</sub>               | Output Low Voltage             | I <sub>OL</sub> = 2.1 mA                                          |      | 0.4                   | V    |

| V <sub>OH</sub>               | Output High Voltage            | I <sub>OH</sub> = -400 μA                                         | 2.4  |                       | V    |

Note: 1. All inputs and outputs open circuit.

# Table 6B. Read Mode DC Characteristics for M28C64-xxW (3V range) (T\_A = 0 to 70 $^\circ$ C or –40 to 85 $^\circ$ C; V\_{CC} = 2.7 to 3.6 V)

| Symbol                        | Parameter                      | Test Condition                                                                    | Min.                | Max.                  | Unit |

|-------------------------------|--------------------------------|-----------------------------------------------------------------------------------|---------------------|-----------------------|------|

| I <sub>LI</sub>               | Input Leakage Current          | $0 \text{ V} \leq \text{V}_{\text{IN}} \leq \text{V}_{\text{CC}}$                 |                     | 10                    | μΑ   |

| I <sub>LO</sub>               | Output Leakage Current         | $0 \ V \leq V_{OUT} \leq V_{CC}$                                                  |                     | 10                    | μA   |

| ı 1                           | Supply Current (CMOS inputs)   | $\overline{E}$ = V_{IL}, $\overline{G}$ = V_{IL} , f = 5 MHz, V_{CC} = 3.3V       |                     | 8                     | mA   |

| lcc <sup>1</sup>              |                                | $\overline{E} = V_{IL}, \ \overline{G} = V_{IL}, \ f = 5 \ MHz, \ V_{CC} = 3.6 V$ |                     | 10                    | mA   |

| I <sub>CC2</sub> <sup>1</sup> | Supply Current (Stand-by) CMOS | $\overline{E}$ > V <sub>CC</sub> - 0.3V                                           |                     | 20                    | μA   |

| VIL                           | Input Low Voltage              |                                                                                   | -0.3                | 0.6                   | V    |

| V <sub>IH</sub>               | Input High Voltage             |                                                                                   | 2                   | V <sub>CC</sub> + 0.5 | V    |

| V <sub>OL</sub>               | Output Low Voltage             | I <sub>OL</sub> = 1.6 mA                                                          |                     | 0.2 V <sub>CC</sub>   | V    |

| Vон                           | Output High Voltage            | I <sub>OH</sub> = -400 μA                                                         | 0.8 V <sub>CC</sub> |                       | V    |

Note: 1. All inputs and outputs open circuit.

| Symbol           | Parameter          | Test Condition  | Min. | Max. | Unit |

|------------------|--------------------|-----------------|------|------|------|

| C <sub>IN</sub>  | Input Capacitance  | $V_{IN} = 0 V$  |      | 6    | pF   |

| C <sub>OUT</sub> | Output Capacitance | $V_{OUT} = 0 V$ |      | 12   | pF   |

Table 7. Input and Output Parameters<sup>1</sup> ( $T_A = 25 \text{ °C}, f = 1 \text{ MHz}$ )

Note: 1. Sampled only, not 100% tested.

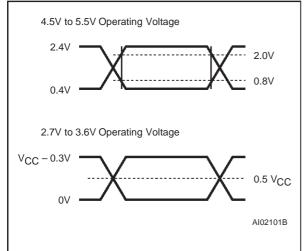

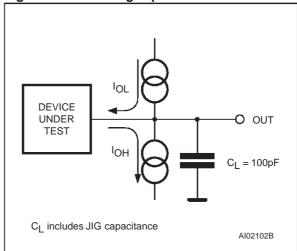

#### **Table 8. AC Measurement Conditions**

| Input Rise and Fall Times                                     | ≤ 20 ns                      |

|---------------------------------------------------------------|------------------------------|

| Input Pulse Voltages (M28C64, M28C64-A)                       | 0.4 V to 2.4 V               |

| Input Pulse Voltages (M28C64-xxW)                             | 0 V to V <sub>CC</sub> -0.3V |

| Input and Output Timing Reference Voltages (M28C64, M28C64-A) | 0.8 V to 2.0 V               |

| Input and Output Timing Reference Voltages (M28C64-xxW)       | 0.5 V <sub>CC</sub>          |

#### Figure 8. AC Testing Input Output Waveforms

Figure 9. AC Testing Equivalent Load Circuit

# Table 9A. Read Mode AC Characteristics for M28C64 and M28C64-A (5V range) (T\_A = 0 to 70 $^\circ C$ or –40 to 85 $^\circ C;$ V\_CC = 4.5 to 5.5 V)

|                     |                 |                                            | Test                                                         |     |     | M28 | C64 |     |     |      |

|---------------------|-----------------|--------------------------------------------|--------------------------------------------------------------|-----|-----|-----|-----|-----|-----|------|

| Symbol              | Alt.            | Parameter                                  | Condit                                                       | -90 |     | -12 |     | -15 |     | Unit |

|                     |                 |                                            | ion                                                          | Min | Max | Min | Max | Min | Max | 1    |

| tavqv               | tACC            | Address Valid to Output Valid              | $\overline{\overline{E}} = V_{IL}, \\ \overline{G} = V_{IL}$ |     | 90  |     | 120 |     | 150 | ns   |

| t <sub>ELQV</sub>   | t <sub>CE</sub> | Chip Enable Low to Output Valid            | $\overline{G} = V_{IL}$                                      |     | 90  |     | 120 |     | 150 | ns   |

| tGLQV               | toe             | Output Enable Low to Output Valid          | $\overline{E} = V_{IL}$                                      |     | 40  |     | 45  |     | 50  | ns   |

| tehqz <sup>1</sup>  | t <sub>DF</sub> | Chip Enable High to Output Hi-Z            | $\overline{G} = V_{IL}$                                      | 0   | 40  | 0   | 45  | 0   | 50  | ns   |

| t <sub>GHQZ</sub> 1 | t <sub>DF</sub> | Output Enable High to Output Hi-Z          | $\overline{E} = V_{IL}$                                      | 0   | 40  | 0   | 45  | 0   | 50  | ns   |

| t <sub>AXQX</sub>   | tон             | Address Transition to Output<br>Transition | $\overline{E} = V_{IL}, \\ \overline{G} = V_{IL}$            | 0   |     | 0   |     | 0   |     | ns   |

Note: 1. Output Hi-Z is defined as the point at which data is no longer driven.

# Table 9B. Read Mode AC Characteristics for M28C64 (5V range) (T<sub>A</sub> = -40 to 125 °C; $V_{CC}$ = 4.5 to 5.5 V)

|                     |                 |                                         | Test                                                         | M28 | C64 |      |

|---------------------|-----------------|-----------------------------------------|--------------------------------------------------------------|-----|-----|------|

| Symbol              | Alt.            | Parameter                               | Condit                                                       | -1  | 2   | Unit |

|                     |                 |                                         | ion                                                          | Min | Max | 1    |

| tAVQV               | tACC            | Address Valid to Output Valid           | $\overline{E} = V_{IL},$<br>$\overline{G} = V_{IL}$          |     | 120 | ns   |

| t <sub>ELQV</sub>   | t <sub>CE</sub> | Chip Enable Low to Output Valid         | $\overline{G} = V_{IL}$                                      |     | 120 | ns   |

| t <sub>GLQV</sub>   | t <sub>OE</sub> | Output Enable Low to Output Valid       | $\overline{E} = V_{IL}$                                      |     | 45  | ns   |

| tehqz <sup>1</sup>  | t <sub>DF</sub> | Chip Enable High to Output Hi-Z         | $\overline{G} = V_{IL}$                                      | 0   | 65  | ns   |

| t <sub>GHQZ</sub> 1 | t <sub>DF</sub> | Output Enable High to Output Hi-Z       | $\overline{E} = V_{IL}$                                      | 0   | 65  | ns   |

| t <sub>AXQX</sub>   | tон             | Address Transition to Output Transition | $\overline{\overline{E}} = V_{IL}, \\ \overline{G} = V_{IL}$ | 0   |     | ns   |

57

Note: 1. Output Hi-Z is defined as the point at which data is no longer driven.

|                     |                  |                                         | Test                                                          |     |     |     | ľ   | M28C6 | 64-xxW | 1   |     |     |     |      |

|---------------------|------------------|-----------------------------------------|---------------------------------------------------------------|-----|-----|-----|-----|-------|--------|-----|-----|-----|-----|------|

| Symbol              | Alt.             | Parameter                               | Condit                                                        | -1  | 2   | -1  | 5   | -2    | 20     | -2  | 25  | -3  | 0   | Unit |

|                     |                  |                                         | ion                                                           | Min | Max | Min | Мах | Min   | Max    | Min | Мах | Min | Max |      |

| tavqv               | t <sub>ACC</sub> | Address Valid to<br>Output Valid        | $\overline{\frac{E}{G}} = V_{IL},$<br>$\overline{G} = V_{IL}$ |     | 120 |     | 150 |       | 200    |     | 250 |     | 300 | ns   |

| <b>t</b> ELQV       | tCE              | Chip Enable Low to<br>Output Valid      | $\overline{G} = V_{IL}$                                       |     | 120 |     | 150 |       | 200    |     | 250 |     | 300 | ns   |

| t <sub>GLQV</sub>   | t <sub>OE</sub>  | Output Enable Low<br>to Output Valid    | $\overline{E} = V_{IL}$                                       |     | 80  |     | 80  |       | 100    |     | 150 |     | 150 | ns   |

| t <sub>EHQZ</sub> 1 | t <sub>DF</sub>  | Chip Enable High to<br>Output Hi-Z      | $\overline{G} = V_{IL}$                                       | 0   | 45  | 0   | 50  | 0     | 55     | 0   | 60  | 0   | 60  | ns   |

| t <sub>GHQZ</sub> 1 | t <sub>DF</sub>  | Output Enable High<br>to Output Hi-Z    | $\overline{E} = V_{IL}$                                       | 0   | 45  | 0   | 50  | 0     | 55     | 0   | 60  | 0   | 60  | ns   |

| t <sub>AXQX</sub>   | t <sub>OH</sub>  | Address Transition to Output Transition | $\overline{E} = V_{IL},$<br>$\overline{G} = V_{IL}$           | 0   |     | 0   |     | 0     |        | 0   |     | 0   |     | ns   |

Table 9C. Read Mode AC Characteristics for M28C64-xxW (3V range) (T<sub>A</sub> = 0 to 70 °C or -40 to 85 °C;  $V_{CC}$  = 2.7 to 3.6 V)

Note: 1. Output Hi-Z is defined as the point at which data is no longer driven.

Note: 1. Write Enable  $(\overline{W}) = V_{IH}$

57

| Symbol              | Alt.             | Parameter                                 | Test Condition                                   | M28 | 8C64 | Unit |

|---------------------|------------------|-------------------------------------------|--------------------------------------------------|-----|------|------|

| Symbol              |                  | Farameter                                 | Test Condition                                   | Min | Max  |      |

| tavwl               | t <sub>AS</sub>  | Address Valid to Write Enable Low         | $\overline{E} = V_{IL}, \overline{G} = V_{IH}$   | 0   |      | ns   |

| t <sub>AVEL</sub>   | t <sub>AS</sub>  | Address Valid to Chip Enable Low          | $\overline{G} = V_{IH}, \ \overline{W} = V_{IL}$ | 0   |      | ns   |

| tELWL               | tCES             | Chip Enable Low to Write Enable Low       | G = V <sub>IH</sub>                              | 0   |      | ns   |

| tGHWL               | tOES             | Output Enable High to Write Enable Low    | Ē = VIL                                          | 0   |      | ns   |

| t <sub>GHEL</sub>   | tOES             | Output Enable High to Chip Enable Low     | $\overline{W} = V_{IL}$                          | 0   |      | ns   |

| twlel               | twes             | Write Enable Low to Chip Enable Low       | $\overline{G} = V_{IH}$                          | 0   |      | ns   |

| t <sub>WLAX</sub>   | t <sub>AH</sub>  | Write Enable Low to Address Transition    |                                                  | 50  |      | ns   |

| t <sub>ELAX</sub>   | t <sub>AH</sub>  | Chip Enable Low to Address Transition     |                                                  | 50  |      | ns   |

| t <sub>WLDV</sub>   | t <sub>DV</sub>  | Write Enable Low to Input Valid           | $\overline{E} = V_{IL}, \overline{G} = V_{IH}$   |     | 1    | μs   |

| t <sub>ELDV</sub>   | t <sub>DV</sub>  | Chip Enable Low to Input Valid            | $\overline{G} = V_{IH}, \ \overline{W} = V_{IL}$ |     | 1    | μs   |

| t <sub>ELEH</sub>   | t <sub>WP</sub>  | Chip Enable Low to Chip Enable High       |                                                  | 50  |      | ns   |

| t <sub>WHEH</sub>   | tCEH             | Write Enable High to Chip Enable High     |                                                  | 0   |      | ns   |

| t <sub>WHGL</sub>   | t <sub>OEH</sub> | Write Enable High to Output Enable Low    |                                                  | 0   |      | ns   |

| t <sub>EHGL</sub>   | t <sub>OEH</sub> | Chip Enable High to Output Enable Low     |                                                  | 0   |      | ns   |

| tehwh               | twen             | Chip Enable High to Write Enable High     |                                                  | 0   |      | ns   |

| t <sub>WHDX</sub>   | t <sub>DH</sub>  | Write Enable High to Input Transition     |                                                  | 0   |      | ns   |

| <b>t</b> EHDX       | tDH              | Chip Enable High to Input Transition      |                                                  | 0   |      | ns   |

| t <sub>WHWL</sub>   | t <sub>WPH</sub> | Write Enable High to Write Enable Low     |                                                  | 50  | 1000 | ns   |

| t <sub>WLWH</sub>   | t <sub>WP</sub>  | Write Enable Low to Write Enable High     |                                                  | 50  |      | ns   |

| t                   | t                | Time-out after last byte write (M28C64)   |                                                  | 100 |      | μs   |

| twlq5h              | <sup>t</sup> BLC | Time-out after last byte write (M28C64-A) |                                                  | 20  |      | μs   |

| t <sub>Q5HQ5X</sub> | twc              | Write Cycle Time (M28C64)                 |                                                  |     | 3    | ms   |

| vQDHQDX             |                  | Write Cycle Time (M28C64-A)               |                                                  |     | 1    | ms   |

| twhrl               | t <sub>DB</sub>  | Write Enable High to Ready/Busy Low       | Note 1                                           |     | 150  | ns   |

| t <sub>EHRL</sub>   | t <sub>DB</sub>  | Chip Enable High to Ready/Busy Low        | Note 1                                           |     | 150  | ns   |

| tDVWH               | t <sub>DS</sub>  | Data Valid before Write Enable High       |                                                  | 50  |      | ns   |

| t <sub>DVEH</sub>   | t <sub>DS</sub>  | Data Valid before Chip Enable High        |                                                  | 50  |      | ns   |

# Table 10A. Write Mode AC Characteristics for M28C64 and M28C64-A (5V range) (T<sub>A</sub> = 0 to 70 °C or –40 to 85 °C; V<sub>CC</sub> = 4.5 to 5.5 V)

Note: 1. With a 3.3 k $\Omega$  pull-up resistor.

# Table 10B. Write Mode AC Characteristics for M28C64 (5V range) $(T_A$ = -40 to 125 $^\circ\text{C};$ V\_{CC} = 4.5 to 5.5 V)

| Symbol              | Alt.             | Perometer                                 | Test Condition                                   | M28 | 3C64 | Unit |

|---------------------|------------------|-------------------------------------------|--------------------------------------------------|-----|------|------|

| Symbol              | AIL.             | Parameter                                 | Test Condition                                   | Min | Max  |      |

| t <sub>AVWL</sub>   | t <sub>AS</sub>  | Address Valid to Write Enable Low         | $\overline{E} = V_{IL}, \overline{G} = V_{IH}$   | 0   |      | ns   |

| tAVEL               | t <sub>AS</sub>  | Address Valid to Chip Enable Low          | $\overline{G} = V_{IH}, \ \overline{W} = V_{IL}$ | 0   |      | ns   |

| telwl               | tCES             | Chip Enable Low to Write Enable Low       | $\overline{G} = V_{IH}$                          | 0   |      | ns   |

| t <sub>GHWL</sub>   | tOES             | Output Enable High to Write Enable Low    | $\overline{E} = V_{IL}$                          | 0   |      | ns   |

| <b>t</b> GHEL       | tOES             | Output Enable High to Chip Enable Low     | $\overline{W} = V_{IL}$                          | 0   |      | ns   |

| twlel               | twes             | Write Enable Low to Chip Enable Low       | $\overline{G} = V_{IH}$                          | 0   |      | ns   |

| t <sub>WLAX</sub>   | t <sub>AH</sub>  | Write Enable Low to Address Transition    |                                                  | 75  |      | ns   |

| tELAX               | t <sub>AH</sub>  | Chip Enable Low to Address Transition     |                                                  | 75  |      | ns   |

| t <sub>WLDV</sub>   | t <sub>DV</sub>  | Write Enable Low to Input Valid           | $\overline{E} = V_{IL}, \overline{G} = V_{IH}$   |     | 1    | μs   |

| t <sub>ELDV</sub>   | t <sub>DV</sub>  | Chip Enable Low to Input Valid            | $\overline{G} = V_{IH}, \ \overline{W} = V_{IL}$ |     | 1    | μs   |

| t <sub>ELEH</sub>   | t <sub>WP</sub>  | Chip Enable Low to Chip Enable High       |                                                  | 50  |      | ns   |

| twhen               | t <sub>CEH</sub> | Write Enable High to Chip Enable High     |                                                  | 0   |      | ns   |

| twhgl               | t <sub>OEH</sub> | Write Enable High to Output Enable Low    |                                                  | 0   |      | ns   |

| t <sub>EHGL</sub>   | toeh             | Chip Enable High to Output Enable Low     |                                                  | 0   |      | ns   |

| t <sub>EHWH</sub>   | t <sub>WEH</sub> | Chip Enable High to Write Enable High     |                                                  | 0   |      | ns   |

| twhdx               | t <sub>DH</sub>  | Write Enable High to Input Transition     |                                                  | 0   |      | ns   |

| <b>t</b> EHDX       | tDН              | Chip Enable High to Input Transition      |                                                  | 0   |      | ns   |

| t <sub>WHWL</sub>   | t <sub>WPH</sub> | Write Enable High to Write Enable Low     |                                                  | 50  | 1000 | ns   |

| t <sub>WLWH</sub>   | t <sub>WP</sub>  | Write Enable Low to Write Enable High     |                                                  | 50  |      | ns   |

| tur oru             | toulo            | Time-out after last byte write (M28C64)   |                                                  | 100 |      | μs   |

| twlq5h              | t <sub>BLC</sub> | Time-out after last byte write (M28C64-A) |                                                  | 20  |      | μs   |

| t <sub>Q5HQ5X</sub> | twc              | Write Cycle Time (M28C64)                 |                                                  |     | 3    | ms   |

| *QOHQOA             |                  | Write Cycle Time (M28C64-A)               |                                                  |     | 1    | ms   |

| twhrl               | t <sub>DB</sub>  | Write Enable High to Ready/Busy Low       | Note 1                                           |     | 150  | ns   |

| t <sub>EHRL</sub>   | t <sub>DB</sub>  | Chip Enable High to Ready/Busy Low        | Note 1                                           |     | 150  | ns   |

| t <sub>DVWH</sub>   | t <sub>DS</sub>  | Data Valid before Write Enable High       |                                                  | 50  |      | ns   |

| t <sub>DVEH</sub>   | t <sub>DS</sub>  | Data Valid before Chip Enable High        |                                                  | 50  |      | ns   |

57

| Sumbal              | A 14             | Beremeter                              | Test Condition                                   | M28C | 64-xxW | Unit |

|---------------------|------------------|----------------------------------------|--------------------------------------------------|------|--------|------|

| Symbol              | Alt.             | Parameter                              | Test Condition                                   | Min  | Max    |      |

| tavwl               | t <sub>AS</sub>  | Address Valid to Write Enable Low      | $\overline{E} = V_{IL}, \overline{G} = V_{IH}$   | 0    |        | ns   |

| tAVEL               | t <sub>AS</sub>  | Address Valid to Chip Enable Low       | $\overline{G} = V_{IH}, \ \overline{W} = V_{IL}$ | 0    |        | ns   |

| tELWL               | tCES             | Chip Enable Low to Write Enable Low    | $\overline{G} = V_{IH}$                          | 0    |        | ns   |

| tGHWL               | tOES             | Output Enable High to Write Enable Low | $\overline{E} = V_{IL}$                          | 0    |        | ns   |

| tGHEL               | tOES             | Output Enable High to Chip Enable Low  | $\overline{W} = V_{IL}$                          | 0    |        | ns   |

| twlel               | twes             | Write Enable Low to Chip Enable Low    | $\overline{G} = V_{IH}$                          | 0    |        | ns   |

| t <sub>WLAX</sub>   | t <sub>AH</sub>  | Write Enable Low to Address Transition |                                                  | 100  |        | ns   |

| t <sub>ELAX</sub>   | t <sub>AH</sub>  | Chip Enable Low to Address Transition  |                                                  | 100  |        | ns   |

| t <sub>WLDV</sub>   | t <sub>DV</sub>  | Write Enable Low to Input Valid        | $\overline{E} = V_{IL}, \overline{G} = V_{IH}$   |      | 1      | μs   |

| t <sub>ELDV</sub>   | t <sub>DV</sub>  | Chip Enable Low to Input Valid         | $\overline{G} = V_{IH}, \ \overline{W} = V_{IL}$ |      | 1      | μs   |

| t <sub>ELEH</sub>   | t <sub>WP</sub>  | Chip Enable Low to Chip Enable High    |                                                  | 100  | 1000   | ns   |

| twhen               | t <sub>CEH</sub> | Write Enable High to Chip Enable High  |                                                  | 0    |        | ns   |

| twhgl               | t <sub>OEH</sub> | Write Enable High to Output Enable Low |                                                  | 0    |        | ns   |

| t <sub>EHGL</sub>   | t <sub>OEH</sub> | Chip Enable High to Output Enable Low  |                                                  | 0    |        | ns   |

| tehwh               | twen             | Chip Enable High to Write Enable High  |                                                  | 0    |        | ns   |

| twhdx               | t <sub>DH</sub>  | Write Enable High to Input Transition  |                                                  | 0    |        | ns   |

| <b>t</b> EHDX       | tDН              | Chip Enable High to Input Transition   |                                                  | 0    |        | ns   |

| t <sub>WHWL</sub>   | t <sub>WPH</sub> | Write Enable High to Write Enable Low  |                                                  | 50   | 1000   | ns   |

| t <sub>WLWH</sub>   | t <sub>WP</sub>  | Write Enable Low to Write Enable High  |                                                  | 100  |        | ns   |

| t <sub>WLQ5H</sub>  | t <sub>BLC</sub> | Time-out after the last byte write     |                                                  | 100  |        | μs   |

| t <sub>Q5HQ5X</sub> | twc              | Write Cycle Time                       |                                                  |      | 5      | ms   |

| t <sub>WHRL</sub>   | t <sub>DB</sub>  | Write Enable High to Ready/Busy Low    | Note 1                                           |      | 150    | ns   |

| tehrl               | t <sub>DB</sub>  | Chip Enable High to Ready/Busy Low     | Note 1                                           |      | 150    | ns   |

| t <sub>DVWH</sub>   | t <sub>DS</sub>  | Data Valid before Write Enable High    |                                                  | 50   |        | ns   |

| t <sub>DVEH</sub>   | t <sub>DS</sub>  | Data Valid before Chip Enable High     |                                                  | 50   |        | ns   |

|                     |                  |                                        |                                                  |      |        |      |

57

# Table 10C. Write Mode AC Characteristics for M28C64-xxW (3V range) (T<sub>A</sub> = 0 to 70 °C or -40 to 85 °C; V<sub>CC</sub> = 2.7 to 3.6 V)

Note: 1. With a 3.3 k $\Omega$  pull-up resistor.

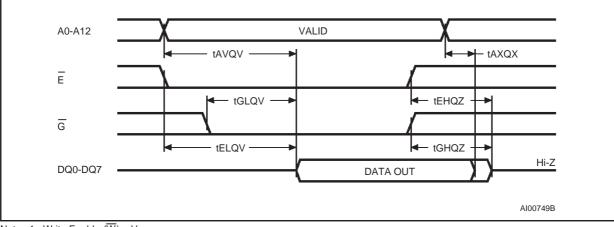

Figure 11. Write Mode AC Waveforms (Write Enable, W, controlled)

Figure 13. Page Write Mode AC Waveforms (Write Enable, W, controlled)

Note: 1. A12 to A6 must specify the same page address during each high-to-low transition of W (or E). G must be high only when W and E are both low.

57

Figure 15. Data Polling Sequence Waveforms

Note: 1. The Toggle Bit is first set to '0'.

57

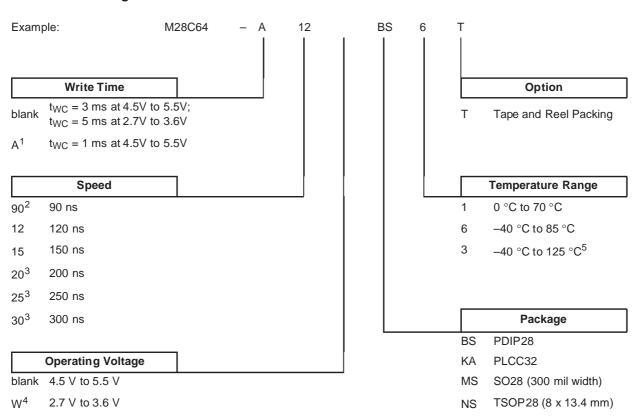

#### Table 11. Ordering Information Scheme

Note: 1. Available only with 120 ns speed (-12), 5V operating range (-blank), and -40 to 85 °C temperature range (-6).

2. Available for the M28C64 only.

3. Available for the 3V range (-xxW) only.

4. Not available for the 1 ms write time option (-A).

5. Available only for the "M28C64 - 12 MS 3" (5V range, SO28 package)

#### **ORDERING INFORMATION**

Devices are shipped from the factory with the memory content set at all '1's (FFh).

The notation used for the device number is as shown in Table 11. For a list of available options (speed, package, etc.) or for further information on any aspect of this device, please contact your nearest ST Sales Office.

| Cumh  |      | mm    |       |       | inches |       |  |  |

|-------|------|-------|-------|-------|--------|-------|--|--|

| Symb. | Тур. | Min.  | Max.  | Тур.  | Min.   | Max.  |  |  |

| A     |      | 3.94  | 5.08  |       | 0.155  | 0.200 |  |  |

| A1    |      | 0.38  | 1.78  |       | 0.015  | 0.070 |  |  |

| A2    |      | 3.56  | 4.06  |       | 0.140  | 0.160 |  |  |

| В     |      | 0.38  | 0.56  |       | 0.015  | 0.021 |  |  |

| B1    |      | 1.14  | 1.78  |       | 0.045  | 0.070 |  |  |

| С     |      | 0.20  | 0.30  |       | 0.008  | 0.012 |  |  |

| D     |      | 34.70 | 37.34 |       | 1.366  | 1.470 |  |  |

| E     |      | 14.80 | 16.26 |       | 0.583  | 0.640 |  |  |

| E1    |      | 12.50 | 13.97 |       | 0.492  | 0.550 |  |  |

| e1    | 2.54 | -     | -     | 0.100 | -      | -     |  |  |

| eA    |      | 15.20 | 17.78 |       | 0.598  | 0.700 |  |  |

| L     |      | 3.05  | 3.82  |       | 0.120  | 0.150 |  |  |

| S     |      | 1.02  | 2.29  |       | 0.040  | 0.090 |  |  |

| α     |      | 0°    | 15°   |       | 0°     | 15°   |  |  |

| N     |      | 28    |       |       | 28     |       |  |  |

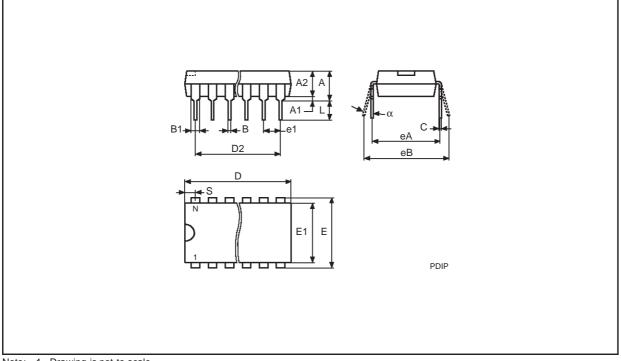

Table 12. PDIP28 - 28 pin Plastic DIP, 600 mils width

## Figure 17. PDIP28 (BS)

Note: 1. Drawing is not to scale.

| Symbol |      | mm    |       |       | inches |       |

|--------|------|-------|-------|-------|--------|-------|

| Symbol | Тур. | Min.  | Max.  | Тур.  | Min.   | Max.  |

| A      |      | 2.54  | 3.56  |       | 0.100  | 0.140 |

| A1     |      | 1.52  | 2.41  |       | 0.060  | 0.095 |

| A2     |      | -     | 0.38  |       | _      | 0.015 |

| В      |      | 0.33  | 0.53  |       | 0.013  | 0.021 |

| B1     |      | 0.66  | 0.81  |       | 0.026  | 0.032 |

| D      |      | 12.32 | 12.57 |       | 0.485  | 0.495 |

| D1     |      | 11.35 | 11.56 |       | 0.447  | 0.455 |

| D2     |      | 9.91  | 10.92 |       | 0.390  | 0.430 |

| E      |      | 14.86 | 15.11 |       | 0.585  | 0.595 |

| E1     |      | 13.89 | 14.10 |       | 0.547  | 0.555 |

| E2     |      | 12.45 | 13.46 |       | 0.490  | 0.530 |

| е      | 1.27 | -     | -     | 0.050 | -      | -     |

| F      |      | 0.00  | 0.25  |       | 0.000  | 0.010 |

| R      | 0.89 | -     | -     | 0.035 | -      | -     |

| N      |      | 32    | •     |       | 32     | •     |

| Nd     |      | 7     |       |       | 7      |       |

| Ne     |      | 9     |       |       | 9      |       |

| СР     |      |       | 0.10  |       |        | 0.004 |

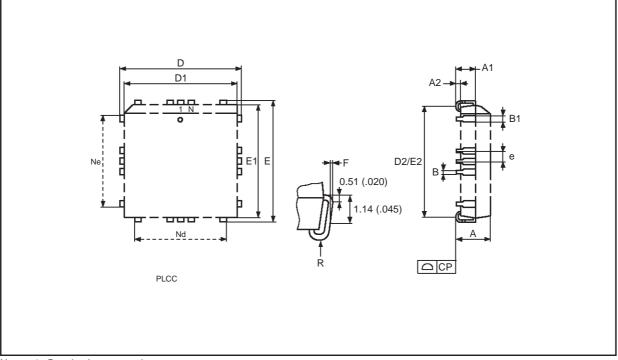

Table 13. PLCC32 - 32 lead Plastic Leaded Chip Carrier, rectangular

# Figure 18. PLCC (KA)

57

Note: 1. Drawing is not to scale.

| Symb. |      | mm    |       |       | inches |       |

|-------|------|-------|-------|-------|--------|-------|

| Symb. | Тур. | Min.  | Max.  | Тур.  | Min.   | Max.  |

| A     |      | 2.46  | 2.64  |       | 0.097  | 0.104 |

| A1    |      | 0.13  | 0.29  |       | 0.005  | 0.011 |

| A2    |      | 2.29  | 2.39  |       | 0.090  | 0.094 |

| В     |      | 0.35  | 0.48  |       | 0.014  | 0.019 |

| С     |      | 0.23  | 0.32  |       | 0.009  | 0.013 |

| D     |      | 17.81 | 18.06 |       | 0.701  | 0.711 |

| E     |      | 7.42  | 7.59  |       | 0.292  | 0.299 |

| e     | 1.27 | -     | -     | 0.050 | -      | -     |

| Н     |      | 10.16 | 10.41 |       | 0.400  | 0.410 |

| L     |      | 0.61  | 1.02  |       | 0.024  | 0.040 |

| α     |      | 0°    | 8°    |       | 0°     | 8°    |

| N     |      | 28    |       |       | 28     |       |

| CP    |      |       | 0.10  |       |        | 0.004 |

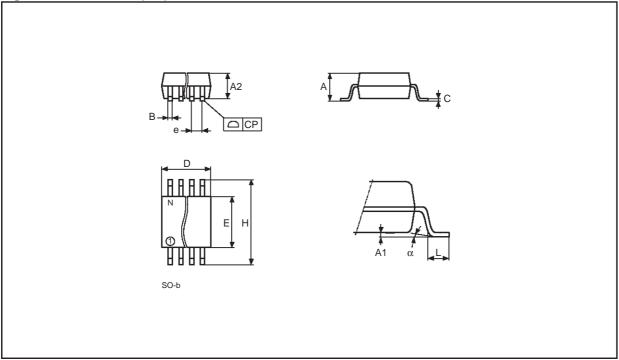

Table 14. SO28 - 28 lead Plastic Small Outline, 300 mils body width

#### Figure 19. SO28 wide (MS)

Note: 1. Drawing is not to scale.

57

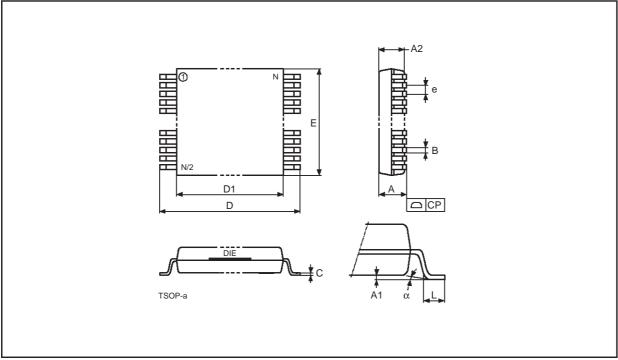

| Curren |      | mm    |       |       | inches |       |

|--------|------|-------|-------|-------|--------|-------|

| Symb.  | Тур. | Min.  | Max.  | Тур.  | Min.   | Max.  |

| А      |      |       | 1.25  |       |        | 0.049 |

| A1     |      |       | 0.20  |       |        | 0.008 |

| A2     |      | 0.95  | 1.15  |       | 0.037  | 0.045 |

| В      |      | 0.17  | 0.27  |       | 0.007  | 0.011 |

| С      |      | 0.10  | 0.21  |       | 0.004  | 0.008 |

| D      |      | 13.20 | 13.60 |       | 0.520  | 0.535 |

| D1     |      | 11.70 | 11.90 |       | 0.461  | 0.469 |

| E      |      | 7.90  | 8.10  |       | 0.311  | 0.319 |

| е      | 0.55 | -     | _     | 0.022 | _      | -     |

| L      |      | 0.50  | 0.70  |       | 0.020  | 0.028 |

| α      |      | 0°    | 5°    |       | 0°     | 5°    |

| Ν      |      | 28    |       |       | 28     |       |

| CP     | 1    |       | 0.10  | ĺ     |        | 0.004 |

Table 15. TSOP28 - 28 lead Plastic Thin Small Outline, 8 x 13.4 mm

#### Figure 20. TSOP28 (NS)

57

Note: 1. Drawing is not to scale.

| Description of Revision                                                                   |

|-------------------------------------------------------------------------------------------|

| -40 to 125°C temperature range added to timing and characteristics tables, and order info |

| Paragraph on behaviour, following an out-of-bounds page write operation, corrected        |

|                                                                                           |

|                                                                                           |

|                                                                                           |

|                                                                                           |

|                                                                                           |

|                                                                                           |

|                                                                                           |

|                                                                                           |

|                                                                                           |

|                                                                                           |

|                                                                                           |

|                                                                                           |

|                                                                                           |

|                                                                                           |

|                                                                                           |

|                                                                                           |

|                                                                                           |

\_\_\_\_

# Table 16. Revision History

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

© 2000 STMicroelectronics - All Rights Reserved

The ST logo is a registered trademark of STMicroelectronics.

All other names are the property of their respective owners.

STMicroelectronics GROUP OF COMPANIES

Australia - Brazil - China - Finland - France - Germany - Hong Kong - India - Italy - Japan - Malaysia - Malta - Morocco - Singapore - Spain -Sweden - Switzerland - United Kingdom - U.S.A.

http://www.st.com

24/24

Copyright © Each Manufacturing Company.

All Datasheets cannot be modified without permission.

This datasheet has been download from :

www.AllDataSheet.com

100% Free DataSheet Search Site.

Free Download.

No Register.

Fast Search System.

www.AllDataSheet.com