# TS68HC901

# HCMOS MULTI-FUNCTION PERIPHERAL

The TS68HC901 CMFP (CMOS Multi-Function Peripheral) is a combination of many of the necessary peripheral functions in a microprocessor system.

#### Included are:

- 8 INPUT/OUTPUT PINS

- Individually programmable direction

- Individual interrupt source capability

- Programmable edge selection

- 16 SOURCE INTERRUPT CONTROLLER

- 8 Internal sources

- 8 External sources

- Individual source enable

- · Individual source masking

- Programmable interrupt service modes

- Polling

- Vector generation

- Optional In-service status

- Daisy chaining capability

- FOUR TIMERS WITH INDIVIDUALLY PROGRAMMABLE PRESCALING

- Two multimode timers

- Delay mode

- Pulse width measurement mode

- Event counter mode

- Two delay mode timers

- Independent clock input

- Time out output option

- SINGLE CHANNEL USART

- Full Duplex

- Asynchronous to 65 kbps

- Byte synchronous to 1 Mbps

- Internal/External baud rate generation

- DMA handshake signals

- Modem control

- Loop back mode

- 68000 BUS COMPATIBLE

#### **DESCRIPTION**

The use of the CMFP in a system can significantly reduce chip count, thereby reducing system cost. The CMFP is completely 68000 bus compatible, and 24 directly addressable internal registers provide the necessary control and status interface to the programmer.

The CMFP is a derivative of the MK3801 STI, a Z80 family peripheral.

#### INTRODUCTION

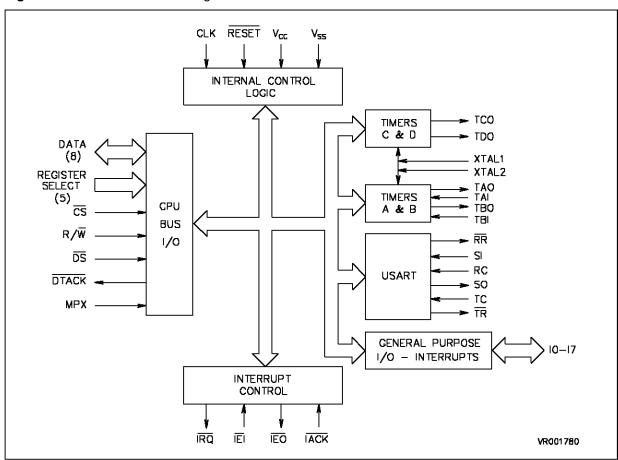

The TS68HC901 multi-function peripheral (CMFP) is a member of the 68000 peripherals. The CMFP directly interfaces to the 68000 processor via an asynchronous bus structure. Both vectored and polled interrupt schemes are supported, with the CMFP providing unique vector number generation for each of its 16 interrupt sources. Additionally, handshake lines are provided to facilitate DMAC interfacing. Refer to block diagram of the TS68HC901.

The TS68HC901 performs many of the functions common to most microprocessor-based systems.

The resources available to the user include:

- Eight Individually Programmable I/O Pins with Interrupt Capability

- 16-Source Interrupt Controller with Individual Source Enabling and Masking

- Four Timers, Two of which are Multi-Mode Timers

- Timers may be used as Baud Rate Generators for the Serial Channel

- Single-Channel Full-Duplex Universal Synchronous / Asynchronous Receiver-Transmitter (U-SART) that Supports Asynchronous and with the Addition of a Polynomial Generator Checker Supports Byte Synchronous Formats

By incorporating multiple functions within the CMFP, the system designer retains flexibility while minimizing device count.

From a programmer's point of view, the versatility of the CMFP may be attributed to its register set. The registers are well organized and allow the CMFP to be easily tailored to a variety of applications. All of the 24 registers are also directly addressable which simplifies programming. The register map is shown in Figure 2.

Figure 1: TS68HC901 Block Diagram

Figure 2 : CMFP Register Map.

|                                              |                                 | Add                                  | ress                                 |                                           |                                      |                                                                    | rigule 2 . GWIFF Register Map.                                                                                                                                                                                                                        |

|----------------------------------------------|---------------------------------|--------------------------------------|--------------------------------------|-------------------------------------------|--------------------------------------|--------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Hex                                          |                                 |                                      | Binary                               |                                           |                                      | Abbreviation                                                       | Register Name                                                                                                                                                                                                                                         |

| пех                                          | RS5                             | RS4                                  | RS3                                  | RS2                                       | RS1                                  |                                                                    |                                                                                                                                                                                                                                                       |

| 01<br>03<br>05                               | 0<br>0<br>0                     | 0<br>0<br>0                          | 0<br>0<br>0                          | 0<br>0<br>1                               | 0<br>1<br>0                          | GPIP<br>AER<br>DDR                                                 | General Purpose I/O Register<br>Active Edge Register<br>Data Direction Register                                                                                                                                                                       |

| 07<br>09<br>0B<br>0D<br>0F<br>11<br>13<br>15 | 0<br>0<br>0<br>0<br>0<br>0<br>0 | 0<br>0<br>0<br>0<br>0<br>1<br>1<br>1 | 0<br>1<br>1<br>1<br>1<br>0<br>0<br>0 | 1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1 | 1<br>0<br>1<br>0<br>1<br>0<br>1<br>0 | IERA<br>IERB<br>IPRA<br>IPRB<br>ISRA<br>ISRB<br>IMRA<br>IMRB<br>VR | Interrupt Enable Register A Interrupt Enable Register B Interrupt Pending Register A Interrupt Pending Register B Interrupt In-service Register A Interrupt In-service Register B Interrupt Mask Register A Interrupt Mask Register B Vector Register |

| 19<br>1B<br>1D<br>1F<br>21<br>23<br>25       | 0<br>0<br>0<br>0<br>1<br>1      | 1<br>1<br>1<br>1<br>0<br>0           | 1<br>1<br>1<br>1<br>0<br>0           | 0<br>0<br>1<br>1<br>0<br>0                | 0<br>1<br>0<br>1<br>0<br>1           | TACR TBCR TCDCR TADR TBDR TCDR TDDR                                | Timer A Control Register Timer B Control Register Timers C and D Control Register Timer A Data Register Timer B Data Register Timer C Data Register Timer D Data Register                                                                             |

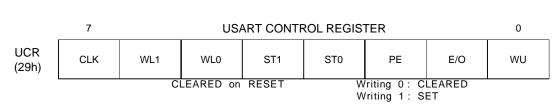

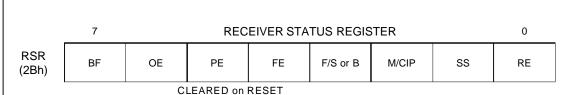

| 27<br>29<br>2B<br>2D<br>2F                   | 1<br>1<br>1<br>1                | 0<br>0<br>0<br>0                     | 0<br>1<br>1<br>1<br>1                | 1<br>0<br>0<br>1<br>1                     | 1<br>0<br>1<br>0                     | SCR<br>UCR<br>RSR<br>TSR<br>UDR                                    | Synchronous Character Register USART Control Register Receiver Status Register Transmitter Status Register USART Data Register                                                                                                                        |

Note: Hex addresses assume that RS1 connects with A1, RS2connects with A2, etc... and that DS is connected to LDS on the 68000 or DS is connect to DS on the 68008.

| Pin | MOTOROLA<br>6800 Type | MOTOROLA<br>Multiplexed | INTEL |

|-----|-----------------------|-------------------------|-------|

| 48  | CS                    | CS                      | CS    |

| 47  | E                     | DS                      | RD    |

| 1   | R/W                   | R/W                     | WR    |

| 35  | Vss                   | AS                      | ALE   |

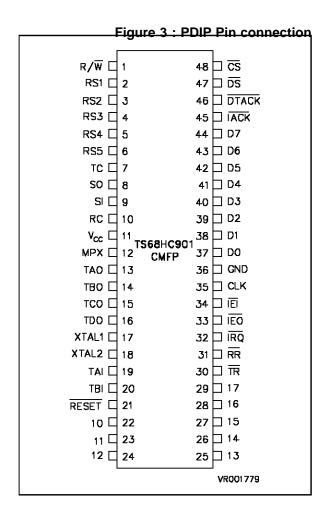

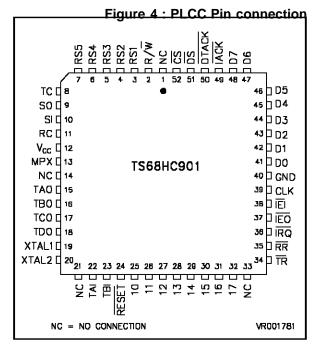

#### PIN DESCRIPTION

GND: Ground

Vcc: +5 volts (± 5%)

$R/\overline{W}$ : Read/Write (input). This input defines a

data transfert as a Read (High) or Write (Low) cycle. This signal is used as WR

with an Intel processor type.

DTACK: This output signals the completion of the operation phase of a bus cycle to the processor. If the bus cycle is a processor read, the CMFP asserts DTACK to indicate that the information on the Data bus is valid. If the bus cycle is a processor to the CMFP, DTACK acknowledges the acceptance of the data by the CMFP. DTACK will be asserted only by an CMFP that has CS or IAK (and IEI) asserted. This signal is not used with a 6800 processor type.

$\overline{\mathrm{CS}}$  : Chip Select (input, active low). CS is used to select the TS68HC901 CMFP for accesses to the internal registers. CS and IACK must not be asserted at the same time.

DS: Data Stobe (input, active low). This Input is part of the internal chip select and interrupt acknowledge functions.

> The CMFP must be located on the lower portion of the 16-bit data-bus so that the vector number passed to the processor during an interrupt acknowledge cycle will be located in the low byte of the data word. As a result, DS must be connected to the processor's lower data strobe if vectored interrupt are to be used. Note that this forces all registers to be located at odd addresses and latches data on the rising edge for writes. This signal is used as RD with an Intel processor type.

RS1-RS5: Register Address Bus (inputs). The ad-(A1-A5) dress bus is used to address one of the internal registers during a read or write cycle.

D0-D7: Data Bus (bi-directional, tri-stateable). This bus is used to receive data from or transmit data to the MFP's internal registers during a processor read or write cvcle. During an interrupt acknowledge cycle, the data bus is used to pass a vector number to the processor. Since the MFP is an 8-bit peripheral, the MFP could be located on either the upper or lower portion of the 16-bit data bus (even or odd address). However, during an interrupt acknowledge cycle, the vector number passed to the processor must be located in the low byte of the data word. As a result, D0-D7 of the MFP must be connected to the low eight bits of the processor data bus, placing MFP registers at odd addresses if vectored interrupt are to be used.

CLK: The clock input is a single-phase TTL compatible signal used for internal timing. This input should not be gated off at any time and must conform to minimum and maximum pulse width times. The clock is not necessarily the system clock in frequency nor phase. When the bus is multiplexed (MPX=1), an address strobe signal is connected to this pin. In the non multiplexed mode (MPX=0), this input is connected to the system clock when used with a 68000 processor type or to Vss (0Vpc) when used with a 6800 processor type.

RESET: Device reset. (input, active low). Reset disables the USART receiver and transmitter, stops all timers and forces the timer outputs low, disables all interrupt channels and clears any pending interrupts. The General Purpose Interrupt/I/O lines will be placed in the tri-state input mode. All internal registers (except the timer, USART data registers, and transmit status register) will be cleared.

MPX: This input selects the data bus mode:

MPX = 0 : non multiplexed mode

MPX = 1 : multiplexed mode. The register select lines RS1-RS5 and the data bus D0-D7 are multiplexed. An address strobe must be connected to the CLK pin.

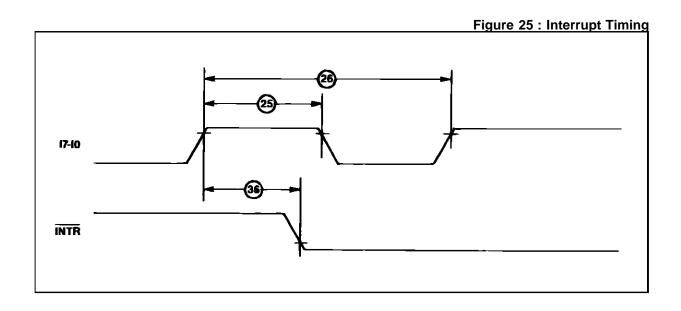

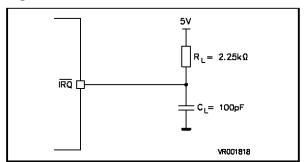

Interrupt Request (output, active low, open drain). This output signals the processor that an interrupt is pending from the CMFP. These are 16 interrupt channels that can generate an interrupt request. Clearing the interrupt pending registers (IPRA and IPRB) or clearing the interrupt mask registers (IMRA and IMRB) will cause IRQ to be negated. IRQ will also be negated as the result of an interrupt acknowledge cycle, unless additional interrupts are pending in the CMFP. Refer to paragraph INTER-RUPTS for further information.

ĪRQ :

IACK: Interrupt Acknowledge (input, active low). IACK is used to signal the TS68HC901 that the CPU is acknowledging an interrupt. CS and IACk must not be asserted at the same time.

IEI: Interrupt Enable In (input, active low). IEI is used to signal the TS68HC901 that no higher priority device is requesting interrupt service.

IEO: Interrupt Enable Out (output, active low).

IEO is used to signal lower priority peripherals that neither the TS68HC901 nor another higher priority peripheral is requesting interrupt service.

IO-I7: General Purpose Interrupt I/O lines. These lines may be used as interrupt inputs and/or I/O lines. When used as interrupt inputs, their active edge is programmable. A data direction register is used to define which lines are to be Hi-Z inputs and which lines are to be push-pull TTL compatible outputs.

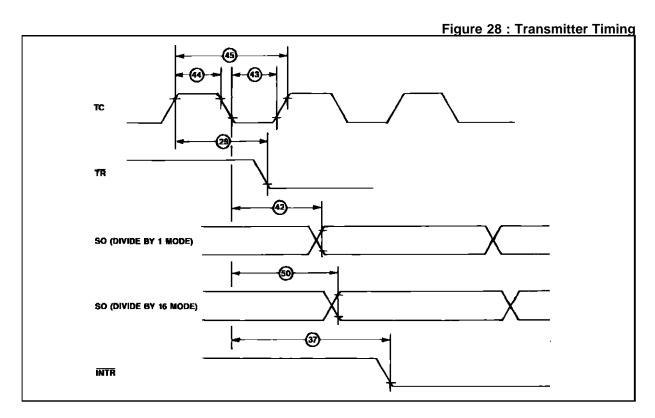

SO: Serial Output. This is the output of the U-SART transmitter.

SI: Serial Input. This is the input to the U-SART receiver.

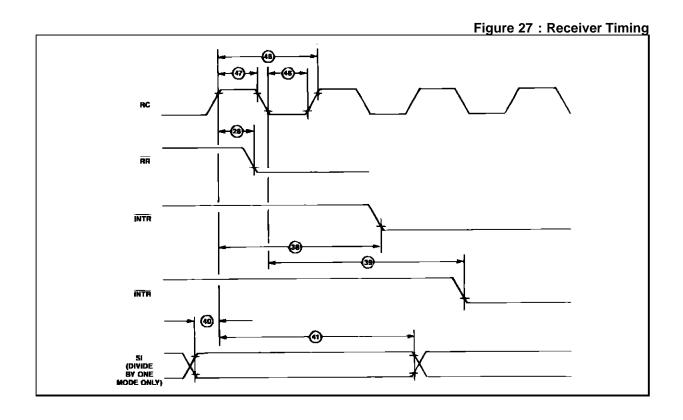

RC: Receiver Clock. This input controls the serial bit rate of the USART receiver.

TC: Transmitter Clock. This input controls the serial bit rate of the USART transmitter.

RR: Receiver Ready. (output, active low)

DMA output for receiver, which reflects

the status of Buffer Full in port number

15.

TR: Transmitter Ready. (output, active low)

DMA output for transmitter, which reflects the status of Buffer Empty in port

number 16.

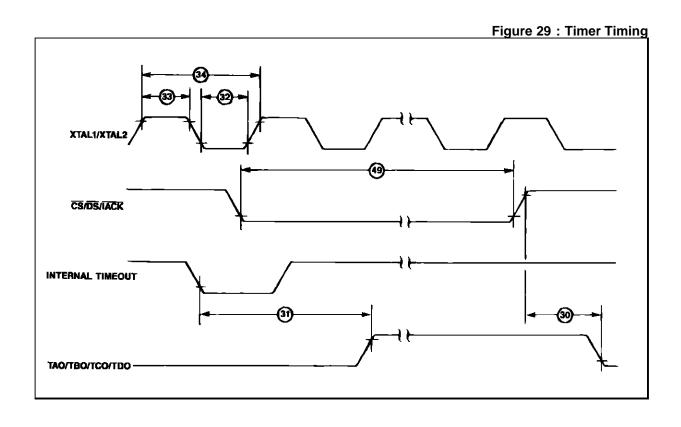

TAO,TBO,Timer Outputs. Each of the four timers TCO,TDO:has an output which can produce a square wave. The output will change states each timer cycle; thus one full period of the timer out signal is equal to two timer cycles. TAO or TBO can be reset (logic "O") by a write to TACR, or TBCR respectively.

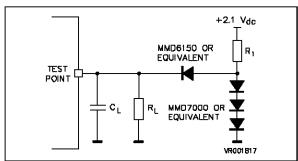

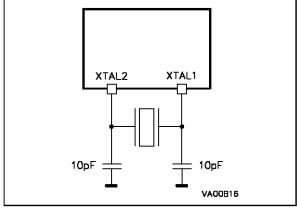

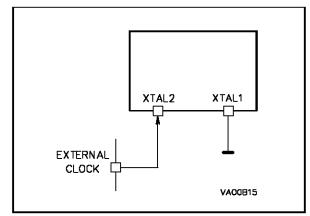

XTAL1, Timer Clock inputs. A crystal can be Connected between XTAL1 and XTAL2, or XTAL1 can be driven with a TTL level clock. When driving XTAL1 with a TTL level clock, XTAL2 must be allowed to float. When using a crystal, external capacitors are required. See figure 35. All chip accesses are independent of the timer clock.

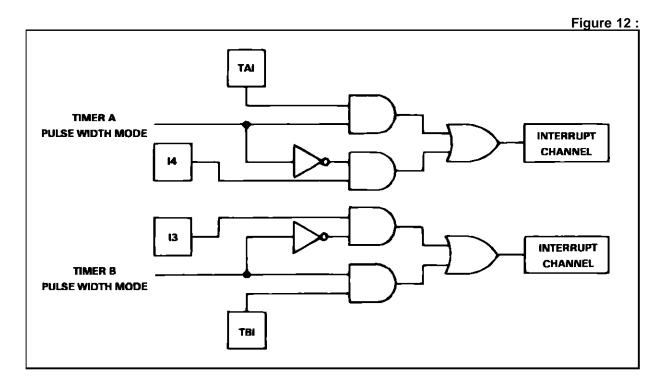

TAI,TBI: Timer A, B inputs. These inputs are control signals for timers A and B in the pulse width measurement mode and event count mode. These signals generate interrupts at the same priority level as the general purpose I/O interrupt lines I4 and I3, respectively. I4 and I3 do not have interrupt capability when the timers are operated in the pulse width measurement mode or the event count mode - under these conditions I4 and I3 may only be used for I/O. Refer to paragraph TIMERS for further information.

#### SIGNAL SUMMARY.

| Signal Name                           | Mnemonic           | I/O    | Active                |

|---------------------------------------|--------------------|--------|-----------------------|

| Power Input                           | Vcc                | Input  | High                  |

| Ground                                | GND                | Input  | Low                   |

| Clock                                 | CLK                | Input  | N/A                   |

| Chip Select                           | <u>cs</u>          | Input  | Low                   |

| Data Strobe                           | <del>DS</del>      | Input  | Low                   |

| Read/Write                            | R∕W                | Input  | Read-High / Write-Low |

| Data tranfer Acknowledge              | DTACK              | Output | Low                   |

| Register Select Bus                   | RS1-RS5            | Input  | N/A                   |

| Data Bus                              | D0-D7              | I/O    | N/A                   |

| Reset                                 | RESET              | Input  | Low                   |

| Interrupt Request                     | ĪRQ                | Output | Low                   |

| Interrupt Acknowledge                 | ĪACK               | Input  | Low                   |

| Interrupt Enable In                   | ĪĒĪ                | Input  | Low                   |

| Interrupt Enable Out                  | ĪĒŌ                | Output | Low                   |

| General Purpose I/O - Interrupt Lines | 10-17              | I/O    | N/A                   |

| Timer Clock                           | XTAL1, XTAL2       | Input  | High                  |

| Timer Inputs                          | TAI, TBI           | Input  | N/A                   |

| Timer Outputs                         | TAO, TBO, TCO, TDO | Output | N/A                   |

| Serial Input                          | SI                 | Input  | N/A                   |

| Serial Output                         | SO                 | Output | N/A                   |

| Receiver Clock                        | RC                 | Input  | N/A                   |

| Transmitter Clock                     | TC                 | Input  | N/A                   |

| Receiver Ready                        | RR                 | Output | Low                   |

| Transmitter Ready                     | TR                 | Output | Low                   |

| MPX                                   | MPX                | Input  | N/A                   |

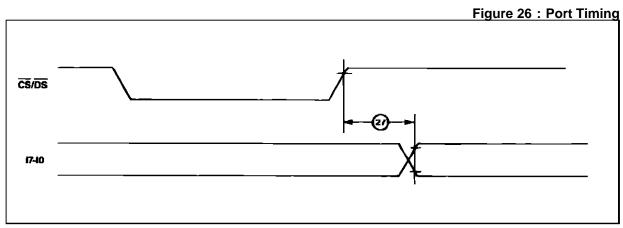

#### **BUS OPERATION**

The following paragraphs explain the control signals and bus operation during data transfer operations and reset.

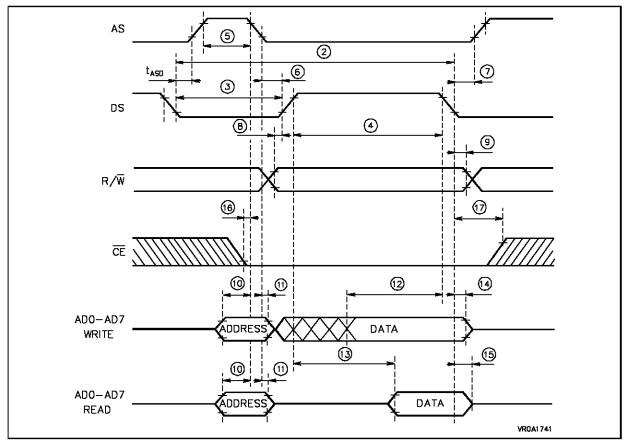

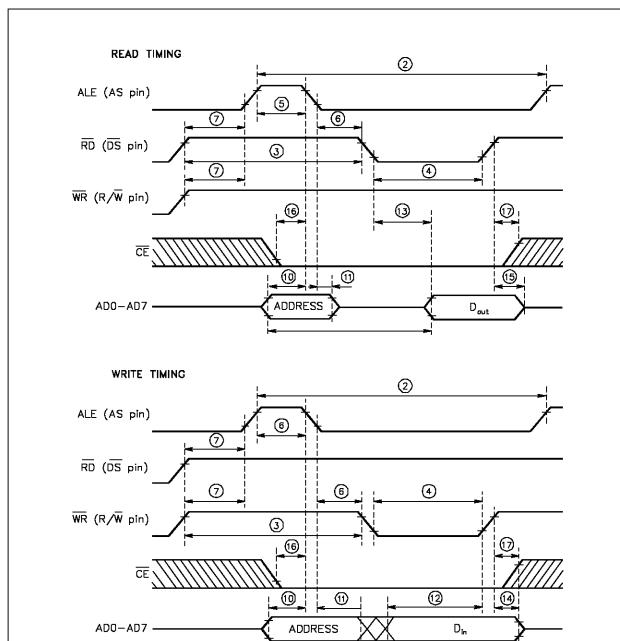

## DATA TRANSFER OPERATIONS.

Transfer of data between devices involves the following pins: Register Select Bus - RS5 through RS1 Data Bus - D0 through D7 Control Signals The address and data buses are separate parallel buses used to transfer data using an asynchronous bus structure. In all cycles, the bus master assumes responsibility for deskewing all signals it issues at both the start and end of a cycle. Additionally, the bus master is responsible for deskewing the acknowledge and data signals from the peripheral devices.

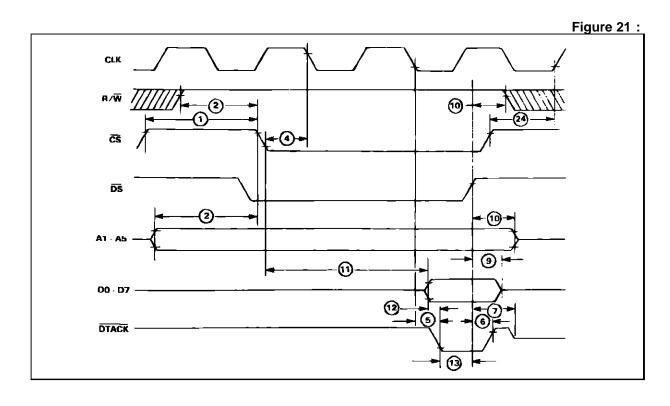

Read Cycle. To read a CMFP register,  $\overline{CS}$  and  $\overline{DS}$  must be asserted, and R/W must be high. The CMFP will place the content of the register which is selected by the register select bus (RS1 through RS5) on the data bus (D1 through D7) and then assert  $\overline{DTACK}$ . The register addresses are shown on Figure 2. After the processor has latched the data, DS is negated. The negation of either  $\overline{CS}$  or  $\overline{DS}$  will terminate the read operation. The CMFP will drive  $\overline{DTACK}$  High and place it in the high-impedance state. The timing for a read cycle is shown in figure 21.

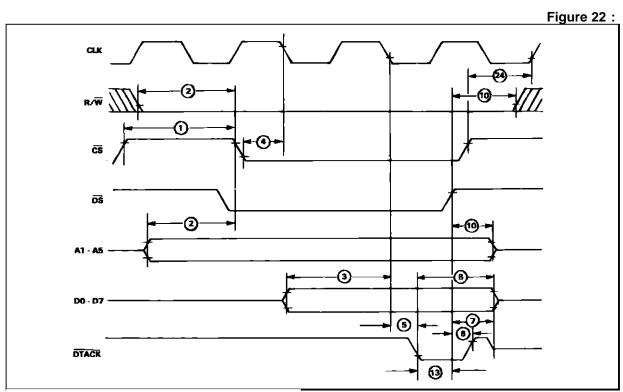

Write Cycle. To write a register  $\overline{\text{CS}}$  and  $\overline{\text{DS}}$  must be asserted, and R/W must be low. The CMFP will decode the address bus to determine which register is selected. Then the register will be loaded with the contents of the data bus and  $\overline{\text{DTACK}}$  will be asserted. When the processor recognizes  $\overline{\text{DTACK}}$ ,  $\overline{\text{DS}}$  will be negated. The write cycle is terminated when either  $\overline{\text{CS}}$  or  $\overline{\text{DS}}$  is negated. The CMFP will drive  $\overline{\text{DTACK}}$  high and place it in the high-impedance state. The timing for a write cycle is shown in figure 22.

#### INTERRUPT ACKNOWLEDGE OPERATION.

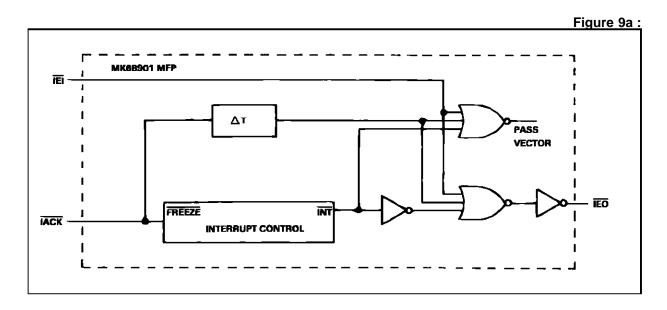

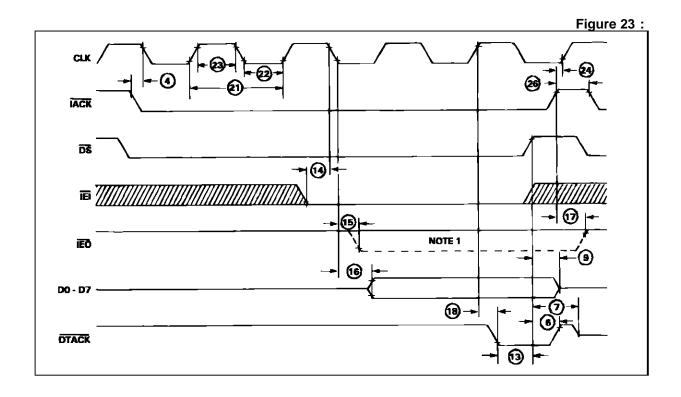

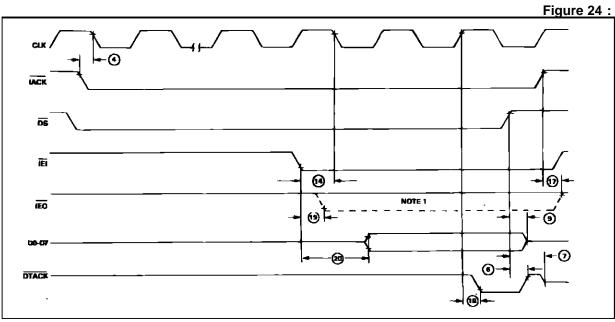

The CMFP has 16 interrupt sources, eight internal and eight external. When an interrupt request is pending, the CMFP will assert IRQ. In a vectored interrupt scheme, the processor will acknowledge the interrupt request by performing an interrupt acknowledge cycle. IACK and DS will be asserted. The CMFP responds to the IACK signal by placing a vector number on the lower eight bits of the data bus. This vector number corresponds to the IRQ handler for the particular interrupt requesting service. The format of this vector number is given in figure 6.

When the CMFP asserts DTACK to indicate that valid data is on the bus, the processor will latch the data and terminate the bus cycle by negating DS. When either DS or IACK are negated, the CMFP will terminate the interrupt acknowledge operation by driving DTACK high and placing it in the high-impedance state. Also, the data bus will be placed in the high-impedance state. IRQ will be negated as a result of the IACK cycle unless additional interrupts are pending.

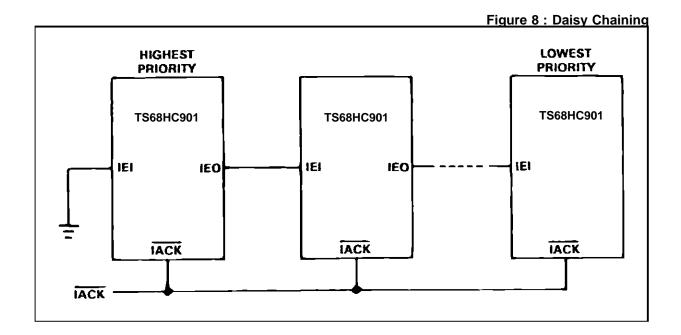

The CMFP can be part of a daisy-chain interrupt structure which allows multiple CMFPs to be placed at the same interrupt level by sharing a common IACK signal. A daisy-chain priority scheme is implemented with IEI and IEO signals. IEI indicates that no higher priority device is requesting interrupt service. IEO signals lower priority devices that neither this device nor any higher priority devices is requesting service. To daisy-chain CMFPs, the highest priority CMFP has its IEI tied low and successive CMFPs have their IEI connected to the next higher priority device's IEO. Note that when the daisy-chain

interrupt structure is not implemented, the  $\overline{\text{IEI}}$  of all CMFPs must be tied low.

When the processor initiates an interrupt acknowledge cycle by driving IACK and DS, the CMFP whose IEI is low may respond with a vector number if interrupt is pending. If this device does not have a pending interrupt, IEO is asserted which allows the next lower priority device to respond to the interrupt acknowledge. When an CMFP propagates IEO, it will not drive the data bus nor DTACK during the interrupt acknowledge cycle. The timing for an IACK cycle is shown in figure 23 and 24.

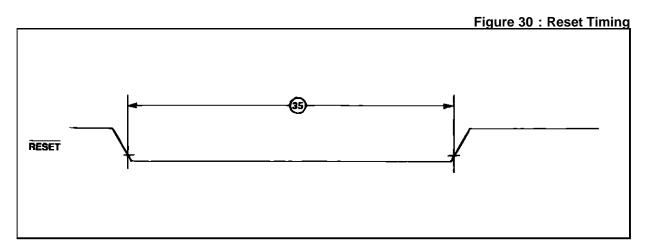

#### **RESET OPERATION**

The reset operation will initialize the CMFP to a known state. The reset operation requires that the RESET input be asserted for a minimum of two microseconds. During a device reset condition, all internal CMFP registers are cleared except for the timer data registers (TADR, TBDR, TCDR and TDDR), the USART data register (UDR), the transmitter status register (TSR) and the interrupt vector register. All timers are stopped and the USART receiver and transmitter are disabled. The interrupt channels are also disabled and any pending inter-

rupts are cleared. In addition, the general purpose interrupt I/O lines are placed in the high-impedance input mode and the timer outputs are driven low. External CMFP signals are negated. The interrupt vector register is initialized to a 0Fh.

#### NON MULTIPLEXED MODE

In this mode, the MPX input must be set to zero, and the TS68HC901 can be used with a 68000 processor type or a 6800 processor type. Refer to figure 21 to 24 for the electrical characteristics.

With a 6800 processor type the DS pin is connected to the E signal of the processor, the DTACK signal is not used and the CLK must be zeroed.

#### MULTIPLEXED MODE

The CMFP can be used either on a MOTOROLA or INTEL bus type. In this case the MPX pin is connected to Vcc. The table page 4 gives the signification of the different signals used. A dummy access to the TS68HC901 has to be done before any valid access in order to set up the internal logic of sampling.

#### INTERRUPT STRUCTURE

In a 68000 system, the CMFP will be assigned to one of the seven possible interrupt levels. All interrupt service requests from the CMFP's 16 interrupt channels will be presented at this level. Although, as an interrupt controller, the CMFP will internally prioritize its 16 interrupt sources. Additional interrupt sources may be placed at the same interrupt level by daisy-chaining multiple CMFPs. The CMFPs will be prioritized by their position in the chain.

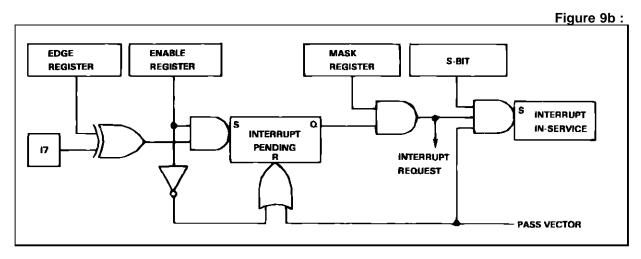

#### INTERRUPT PROCESSING

Each CMFP provides individual interrupt capability for its various functions. When an interrupt is received on one of the external interrupt channels or from one of the eight internal sources, the CMFP will request interrupt service. The 16 interrupt channels are assigned a fixed priority so that multiple pending interrupts are serviced according to their relative importance. Since the CMFP can internally generate 16 vector numbers, the unique vector number which corresponds to the highest priority channel that as a pending interrupt is presented to the processor during an interrupt acknowledge cycle. This unique vector number allows the processor to immediately

begin execution of the interrupt handler for the interrupt source, decreasing interrupt latency time.

#### INTERRUPT CHANNEL PRIORITIZATION

The 16 interrupt channels are prioritized as shown in figure 5. General purpose interrupt 7 (I7) is the highest priority interrupt channel and I0 is the lowest priority channel. Pending interrupts are presented to the CPU in order of priority unless they have been masked off. By selectively masking interrupts, the channel are in effect re-prioritized.

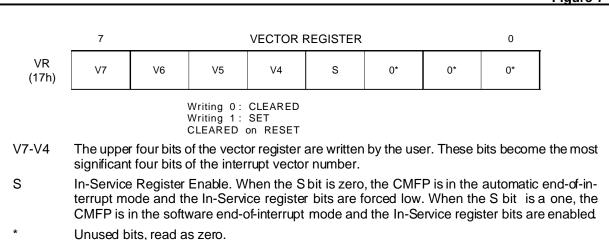

#### INTERRUPT VECTOR NUMBER FORMAT

During an interrupt acknowledge cycle, a unique 8-bit vector number is presented to the system which corresponds to the specific interrupt source which is requesting service. The format of the vector is shown in figure 6. The most significant four bits of the interrupt vector number are user programmable. These bits are set by writing the upper four bits of the vector register which is shown in figure 7. The low order bits are generated internally by the TS68HC901. Note that the binary channel number shown in figure 5 corresponds to the low order bits of the vector number associated with each channel.

Figure 9: Interrupt Channel Prioritization

Figure 5: Interrupt Channel Prioritization

| Priority | Channel | Description                     |  |

|----------|---------|---------------------------------|--|

| HIGHEST  | 1111    | General Purpose Interrupt 7(I7) |  |

|          | 1110    | General Purpose Interrupt 6(I6) |  |

|          | 1101    | Timer A                         |  |

|          | 1100    | Receive Buffer Full             |  |

|          | 1011    | Receive Error                   |  |

|          | 1010    | Transmit Buffer Empty           |  |

|          | 1001    | Transmit Error                  |  |

|          | 1000    | Timer B                         |  |

|          | 0111    | General Purpose Interrupt 5(I5) |  |

|          | 0110    | General Purpose Interrupt 4(I4) |  |

|          | 0101    | Timer C                         |  |

|          | 0100    | Timer D                         |  |

|          | 0011    | General Purpose Interrupt 3(I3) |  |

|          | 0010    | General Purpose Interrupt 2(I2) |  |

|          | 0001    | General Purpose Interrupt 1(I1) |  |

| LOWEST   | 0000    | General Purpose Interrupt 0(I0) |  |

V7-V4

Figure 6:

| V7       | V6         | V5          | V4         | IV3      | IV2      | IV1 | IV0 |

|----------|------------|-------------|------------|----------|----------|-----|-----|

| The four | most signi | ficant bits | are copied | from the | reaister |     |     |

IV3-IV0 These bits are supplied by the CMFP. They are the binary channel number of the highest priority channel that is requesting interrupt service.

Figure 7:

#### DAISY-CHAINING CMFPs

As an interrupt controller, the TS68HC901 CMFP will support eight external interrupt sources in addition to its eight internal interrupt sources. When a system requires more than eight external interrupt sources to be placed at the same interrupt level, sources may be added to the prioritized structure by daisy-chaining CMFPs. Interrupt sources are prioritized internally within each CMFP and the CMFPs are prioritized by their position in the chain. Unique vector numbers are provided for each interrupt sources.

The IEI and IEO signals implement the daisy-chained interrupt structure. The IEI of the highest priority CMFP is tied low and the IEO output of this device is tied to the next highest priority CMFP's IEI. The

IEI and IEO signals are daisy-chained in this manner for all CMFPs in the chain, with the lowest priority CMFP's IEO left unconnected. A diagram of an interrupt daisy-chain is shown in figure 8.

Daisy-chaining requires that all parts in the chain have a common IACK. When the common IACK is asserted during an interrupt acknowledge cycle, all parts will prioritize interrupts in parallel. When the IEI signal to a CMFP is asserted, the part may respond to the IACK cycle if it requires interrupt service. Otherwise, the part will assert IEO to the next lower priority device. Thus, priority is passed down the chain via IEI and IEO until a part which has appending interrupt is reached. The part with the pending interrupt passes a vector number to the processor and does not propagate IEO.

#### INTERRUPT CONTROL REGISTERS

CMPF interrupt processing is managed by the interrupt enable registers A and B, interrupt pending registers A and B, and interrupt mask registers A and B. These registers allow the programmer to enable or disable individual interrupt channels, mask individual interrupt channels, and access pending interrupt status information. In-service registers A and B allow interrupts to be nested as described hereafter. The interrupt control registers are shown in figure 10.

#### INTERRUPT ENABLE REGISTERS

The interrupt channels are individually enabled or disabled by writing a one or zero, respectively, to the appropriate bit of interrupt enable register A (IERA) or interrupt enable register B (IERB). The processor may read these registers at any time.

When a channel is enabled, interrupts received on the channel will be recognized by the CMFP and IRQ will be asserted to the processor, indicating that interrupt service is required. On the other hand, a disabled channel is completely inactive; interrupts received on the channel are ignored by the CMFP.

Writing a zero to a bit of interrupt enable register A or B will cause the corresponding bit of interrupt pending register A or B to be cleared. This will terminate all interrupt service requests for the channel and also negate IRQ, unless interrupts are pending from other sources. Disabling a channel, however, does not affect the corresponding bit in interrupt in-service registers A or B. So, if the CMFP is in the software end-of-interrupt mode and an interrupt is in service when a channel will remain set until cleared by software.

#### INTERRUPT PENDING REGISTERS

When an interrupt is received on an enabled channel, the corresponding interrupt pending bit is set in interrupt pending register A or B (IPRA or IPRB). In a vectored interrupt scheme, this bit will be cleared when the processor acknowledges the interrupting channel and the CMFP responds with a vector number. In a polled interrupt system, the interrupt pending registers must be read to determine the interrupting channel and then the interrupting pending bit is cleared by the interrupt handling routine without performing an interrupt acknowledge sequence.

A single bit of the interrupt pending registers is cleared in software by writing ones to all bit positions except the bit to be cleared. Note that writing ones to IPRA and IPRB has no effect on the contents of the register. A single bit of the interrupt pending registers is also cleared when the corresponding channel is disabled by writing a zero to the appropriate bit of IERA or IERB.

#### INTERRUPT MASK REGISTERS

Interrupts are masked for a channel by clearing the appropriate bit in interrupt mask register A or B (IMRA or IMRB). Even though an enabled channel is masked, the channel will recognize subsequent interrupts and set its interrupt pending bit. However, the channel is prevented from requesting interrupt service (IRQ to the processor) as long as the mask bit for that channel is cleared.

If a channel is requesting interrupt service at the time that its corresponding bit in IMRA or IMRB is cleared, the request will cease and IRQ will be negated, unless another channel is requesting interrupt service. Later, when the mask bit is set, any pending interrupt on the channel will be processed according to the channel's assigned priority. IMRA and IMRB may be read at any time.

Figure 10:

| 7                                          |                                         | INT                                                                                | ERRUPT EN                                                                                                                                                                                                               | IABLE REG                                                                                                                                                                                                                                                                                                                                                      | SISTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                               | 0       |  |  |

|--------------------------------------------|-----------------------------------------|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|---------|--|--|

| GPIP7                                      | GPIP6                                   | TIMER A                                                                            | RCV<br>Buffer full                                                                                                                                                                                                      | RCV<br>Error                                                                                                                                                                                                                                                                                                                                                   | XMIT<br>Buffer Empty                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | XMIT<br>Error                                                                                 | TIMER B |  |  |

| GPIP5                                      | GPIP4                                   | TIMER C                                                                            | TIMER D                                                                                                                                                                                                                 | GPIP3                                                                                                                                                                                                                                                                                                                                                          | GPIP2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | GPIP1                                                                                         | GPIP0   |  |  |

| 7                                          |                                         | INTE                                                                               | RRUPT PEI                                                                                                                                                                                                               | NDING REG                                                                                                                                                                                                                                                                                                                                                      | GISTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                               | 0       |  |  |

| GPIP7                                      | GPIP6                                   | TIMER A                                                                            | RCV<br>Buffer full                                                                                                                                                                                                      | RCV<br>Error                                                                                                                                                                                                                                                                                                                                                   | XMIT<br>Buffer Empty                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | XMIT<br>Error                                                                                 | TIMER B |  |  |

|                                            |                                         |                                                                                    |                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                               |         |  |  |

| GPIP5                                      | GPIP4                                   | TIMER C                                                                            | TIMER D                                                                                                                                                                                                                 | GPIP3                                                                                                                                                                                                                                                                                                                                                          | GPIP2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | GPIP1                                                                                         | GPIP0   |  |  |

| Writing 0 : CLEAR<br>Writing 1 : UNCHANGED |                                         |                                                                                    |                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                               |         |  |  |

| 7                                          |                                         | INTER                                                                              | RRUPT IN-S                                                                                                                                                                                                              | ERVICE RE                                                                                                                                                                                                                                                                                                                                                      | EGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                               | 0       |  |  |

| GPIP7                                      | GPIP6                                   | TIMER A                                                                            | RCV<br>Buffer full                                                                                                                                                                                                      | RCV<br>Error                                                                                                                                                                                                                                                                                                                                                   | XMIT<br>Buffer Empty                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | XMIT<br>Error                                                                                 | TIMER B |  |  |

|                                            |                                         |                                                                                    |                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                               |         |  |  |

| GPIP5                                      | GPIP4                                   | TIMER C                                                                            | TIMER D                                                                                                                                                                                                                 | GPIP3                                                                                                                                                                                                                                                                                                                                                          | GPIP2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | GPIP1                                                                                         | GPIP0   |  |  |

|                                            |                                         |                                                                                    |                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                               |         |  |  |

| 7                                          |                                         | IN                                                                                 | TERRUPT M                                                                                                                                                                                                               | IASK REGI                                                                                                                                                                                                                                                                                                                                                      | STERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                               | 0       |  |  |

| GPIP7                                      | GPIP6                                   | TIMER A                                                                            | RCV<br>Buffer full                                                                                                                                                                                                      | RCV<br>Error                                                                                                                                                                                                                                                                                                                                                   | XMIT<br>Buffer Empty                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | XMIT<br>Error                                                                                 | TIMER B |  |  |

|                                            |                                         |                                                                                    |                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                               |         |  |  |

| GPIP5                                      | GPIP4                                   | TIMER C                                                                            | TIMER D                                                                                                                                                                                                                 | GPIP3                                                                                                                                                                                                                                                                                                                                                          | GPIP2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | GPIP1                                                                                         | GPIP0   |  |  |

|                                            |                                         |                                                                                    |                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                               | •       |  |  |

|                                            | GPIP5  7  GPIP5  7  GPIP7  GPIP7  GPIP7 | GPIP5 GPIP4  7 GPIP7 GPIP6  GPIP5 GPIP4  7 GPIP7 GPIP6  GPIP5 GPIP4  7 GPIP7 GPIP6 | GPIP5 GPIP4 TIMER C  7 INTE GPIP7 GPIP6 TIMER A  GPIP5 GPIP4 TIMER C  Writing 0 : CL Writing 1 : UN  7 INTER GPIP7 GPIP6 TIMER A  GPIP5 GPIP4 TIMER C  7 INTER GPIP7 GPIP6 TIMER A  GPIP7 GPIP6 TIMER C  Writing 0 : MA | GPIP7 GPIP6 TIMER A Buffer full  TIMER C TIMER D  TIMER A RCV Buffer full  GPIP7 GPIP6 TIMER A RCV Buffer full  GPIP5 GPIP4 TIMER C TIMER D  Writing 0 : CLEAR Writing 1 : UNCHANGED  TIMER A RCV Buffer full  GPIP7 GPIP6 TIMER A RCV Buffer full  GPIP5 GPIP4 TIMER C TIMER D  TIMER A RCV Buffer full  GPIP5 GPIP4 TIMER C TIMER D  TIMER A RCV Buffer full | GPIP7 GPIP6 TIMER A Buffer full Error  GPIP5 GPIP4 TIMER C TIMER D GPIP3  7 INTERRUPT PENDING REG GPIP7 GPIP6 TIMER A RCV Buffer full Error  GPIP5 GPIP4 TIMER C TIMER D GPIP3  Writing 0 : CLEAR Writing 1 : UNCHANGED  7 INTERRUPT IN-SERVICE REG GPIP7 GPIP6 TIMER A RCV Buffer full Error  GPIP5 GPIP4 TIMER C TIMER D GPIP3  7 INTERRUPT MASK REGI GPIP7 GPIP6 TIMER A RCV Buffer full Error  GPIP7 GPIP6 TIMER A RCV Buffer full Error  GPIP7 GPIP6 TIMER A RCV Buffer full Error  GPIP7 GPIP6 TIMER A RCV Buffer full Error | GPIP7 GPIP6 TIMER A Buffer full Error Buffer Empty    GPIP5 GPIP4 TIMER C TIMER D GPIP3 GPIP2 | GPIP5   |  |  |

#### **NESTING CMFP INTERRUPTS**

In a 68000 vectored interrupt system, the CMFP is assigned to one of seven possible interrupt levels. When an interrupt is received from the CMFP, an interrupt acknowledge for that level is initiated. Once an interrupt is recognized at a particular level, interrupts at that same level or below are masked by 68000. As long as the processor's interrupt mask is unchanged, the 68000 interrupt structure will prohibit the nesting of interrupts at the same interrupt level. However, additional interrupt requests from the CMFP can be recognized before a previous channel's interrupt service routine is completed by lowering the processor's interrupt mask to the next lower interrupt level within the interrupt handler.

When nesting CMFP interrupts, it may be desirable to permit interrupts on any CMFP channel, regardless of its priority, to preempt or delay interrupt processing of an earlier channel's interrupt service request. Or, it may be desirable to only allow subsequent higher priority channel interrupt requests to supersede previously recognized lower priority interrupt requests. The CMFP interrupt structure provides this flexibility by offering two end-of-interrupt options for vectored interrupt schemes. Note that the end-of-interrupt modes are not active in a polled interrupt scheme.

## SELECTING THE END-OF-INTERRUPT MODE

In a vectored interrupt scheme, the CMFP may be programmed to operate in either the automatic end-of-interrupt mode or the software end-of-interrupt mode. The mode is selected by writing the S bit of the vector register (see figure 7). When the S bit is programmed to a one, the CMFP is placed in the software end-of-interrupt mode and when the S bit is a zero, all channels operate in the automatic end-of-interrupt mode.

#### AUTOMATIC END-OF-INTERRUPT

When an interrupt vector number is passed to the processor during an interrupt acknowledge cycle, the corresponding channel's interrupt pending bit is cleared. In the automatic end-of-interrupt mode, no further history of the interrupt remains in the CMFP. The in-service bits of the interrupt in-service registers (ISRA and ISRB) are forced low. Subsequent interrupts which are received on any CMFP channel will generate an interrupt request to the processor, even if the current interrupt's service routine has not been completed.

#### SOFTWARE END-OF-INTERRUPT

In the software end-of-interrupt mode, the channel's associated interrupt pending bit is cleared and in addition, the channel's in-service bit of in-service register A or B is set when its vector number is passed to the processor during an IACK cycle. A higher priority channel may subsequently request interrupt service and be acknowledged, but as long as the channel's in-service bit is set, no lower priority channel may request interrupt service nor pass its vector during an interrupt acknowledge sequence.

While only higher priority channels may request interrupt service, any channel can receive an interrupt and set its interrupt pending bit. Even the channel whose in-service bit is set can receive a second interrupt. However, no interrupt service request is made until its in-service bit is cleared.

The in-service bit for a particular channel can be cleared by writing a zero to its corresponding bit in ISRA or ISRB and ones to all other bit positions. Since bits in the in-service registers can only be cleared in software and not set, writing ones to the register does not alter their contents. ISRA and ISRB may be read at any time.

# GENERAL PURPOSE INPUT/OUTPUT INTERRUPT PORT

The general purpose interrupt input/output (I/O) port (GPIP) provides eight I/O lines (I0 through I7) that may be operated as either inputs or outputs under software control. In addition, these lines may optionally generate an interrupt on either a positive transition or negative transition of the input signal. The flexibility of the GPIP allows it to be configured as an 8-Bit I/O port or for bit I/O. Since interrupts are enabled on a bit-by-bit basis, a subset of the GPIP could be programmed as handshake lines or the port could be connected to as many as eight external interrupt sources, which would be prioritized by the CMFP interrupt controller for interrupt service.

#### 6800 INTERRUPT CONTROLLER

The CMFP interrupt controller is particularly useful in a system which has many 6800-type devices. Tvpically, in a vectored 68000 system, 6800-type peripherals use the autovector which corresponds to their assigned interrupt level since they do not provide a vector number in response to an AC cycle. The autovector interrupt handler must then poll all 6800-type devices at that interrupt level to determine which device is requesting service. However, by tying the IRQ output from a 6800-type device to the general purpose I/O interrupt port (GPIP) of a CMFP, a unique vector number will be provided to the processor during an interrupt acknowledge cycle. This interrupt structure will significantly reduce interrupt latency for 6800-type devices and other peripheral devices which do not support vector-by-device.

#### **GPIP CONTROL REGISTERS**

The GPIP is programmed via three control registers shown in figure 11. These registers control the data direction provide user access to the port, and specify the active edge for each bit of the GPIP which will produce an interrupt. These registers are described in detail in the following paragraphs.

#### **GPIP DATA REGISTER**

The general purpose I/O data register is used to input or output data to the port. When data is written to the GPIP data register, those pins which are defined as inputs will remain in the high-impedance state. Pins which are defined as outputs will assume the state (high or low) of their corresponding bit in the data register. When the GPIP is read, data will be passed directly from the bits of the data register for pins which are defined as outputs. Data from pins defined as inputs will come from the input buffers.

#### **ACTIVE EDGE REGISTER**

The active edge register (AER) allows each of the GPIP lines to produce an interrupt on either a one-to-zero or a zero-to-one transition. Writing a zero the appropriate edge bit of the active edge register causes the associated input to generate an interrupt on the one-to-zero transition. Writing a one to the edge bit will produce an interrupt on the zero-to-one transition of the corresponding GPIP line.

Figure 11: 7 ACTIVE EDGE REGISTER 0 **AER** 1 = RISING GPIP7 GPIP6 GPIP5 GPIP4 GPIP3 GPIP2 GPIP1 GPIP0 2 = FALLING (03h)DATA DIRECTION REGISTER DDR 1 = OUTPUT GPIP7 GPIP6 GPIP5 GPIP4 GPIP3 GPIP2 GPIP1 GPIP0 (05h) 2 = INPUT GENERAL PURPOSE I/O DATA REGISTER **GPIP** GPIP7 GPIP6 GPIP5 GPIP4 GPIP3 GPIP2 GPIP1 GPIP0 (01h)

#### Note

The transition detector is an exclusive-OR gate whose inputs are the edge bit and the input buffer. As a result, writing the EAR may cause an interrupt-producing transition, depending upon the state of the input. So, the AER should be configured before enabling interrupts via the interrupt enable registers (IERA and IERB). Also, changing the edge bit while interrupts are enabled may cause an interrupt on the corresponding channel.

#### DATA DIRECTION REGISTER

The data direction register (DDR) allows the programmer to define I0 through I7 as inputs or outputs by writing the corresponding bit. When a bit of the data direction register is written as a zero, the corresponding interrupt I/O pin will be a high-impedance input. Writing a one to any bit of the data direction register will cause the corresponding pin to be configured as a push-pull output.

#### **TIMERS**

The CMFP contains four 8-bit timers which provide many functions typically required in microprocessor systems. The timers can supply the baud rate clocks for the on-chip serial I/O channel, generate periodic interrupts, measure elapsed time, and count signal transitions. In addition, two timers have waveform generation capability.

All timers are prescaler/counter timers with a common independent clock input (XTAL1 or XTAL2) and are not required to be operated from the system clock. Each timer's output signal toggles when the timer's main counter times out. Additionally, timers A and B have auxiliary control signals which are used in two of the operation modes. An interrupt channel is assigned to each timer and when the auxiliary control signals are used, a separate interrupt channel will respond to transitions on these inputs.

#### **OPERATION MODES**

Timers A and B are full function timers which, in addition to the delay mode, operate in the pulse width measurement mode and the event count mode. Timers C and D are delay timers only. A brief discussion of each of the timer modes follows.

#### **DELAY MODE OPERATION**

All timers may operate in the delay mode. In this mode, the prescaler is always active. The prescaler specifies the number of timer clock cycles which must elapse before a count pulse is applied to the main counter. A count pulse causes the main counter to decrement by one. When the timer has decremented down to 01 (hexadecimal), the next count pulse will cause the main counter to be reloaded from the timer data register and a time out pulse will

be produced. This time out pulse is coupled to the timer's interrupt channel and, if the channel is enabled, an interrupt will occur. The time out pulse also causes the timer output pin to toggle. The output will remain in this new state until the next time out pulse occurs.

For example, if delay mode with a divide-by-10 prescaler is selected and the timer data register is loaded with 100 (decimal), the main counter will decrement once every 10 timer clock cycles. After 1,000 timer clocks, a time out pulse will be produced. This time out pulse will generate an interrupt if the channel is enabled (IERA, IERB) and in addition, the timer's output line will toggle. The output line will complete one full period every 2,000 cycles of the timer clock.

If the prescaler value is changed while the timer is enabled, the first time out pulse will occur at an indeterminate time no less than one nor more than 200 timer clock cycles. Subsequent time out pulses will then occur at the correct interval.

If the main counter is loaded with 01 (hexadecimal), a time out pulse will occur every time the prescaler presents a count pulse to the main counter. If the main counter is loaded with 00, a time out pulse will occur every 256 count pulses.

#### PULSE WIDTH MEASUREMENT OPERATION

Besides the delay mode, timers A and B may be programmed to operate in the pulse width measurement mode. In this mode an auxiliary control input is required; timers A and B auxiliary input lines are TAI and TBI. Also, in the pulse width measurement mode, interrupt channels normally associated with I4 and I3 will respond to transitions on TAI and TBI, respectively. General purpose lines I3 and I4 may still be used for I/O. A conceptual circuit of the timers

in the pulse width measurement mode is shown in Figure 12.

The pulse width measurement mode functions similarly to the delay mode, with the auxiliary control signal acting as an enable to the timer. When the control signal is active, the prescaler and main counter are allowed to operate. When the control signal is negated, the timer is stopped. So, the width of the active pulse on TAI or TBI is measured by the number of timer counts which occur while the timer is allowed to operate.

The active state of the auxiliary input line is defined by the associated interrupt channel's edge bit in the active edge register (AER). GPIP4 of the AER is the edge bit associated with TAI and GPIP3 is associated with TBI. When the edge bit is a one, the auxiliary input will be active high, enabling the timer while the input signal is at a high level. If the edge bit is low, the auxiliary input will be active low and the timer will operate while the input signal is at a low level.

The state of the active edge bit also specifies whether a zero-to-one transition or a one-to-zero transition of the auxiliary input pin will produce an interrupt when the interrupt channel is enabled. In normal operation, programming the active edge bit to a one will produce an interrupt on the zero-to-one transition of the associated input signal. Alternately, pro-

gramming the edge bit to a zero will produce an interrupt on the one-to-zero transition of the input signal. However, in the pulse width measurement mode, the interrupt generated by a transition on TAI or TBI will occur on the opposite transition as that normally defined by the edge bit.

For example, in the pulse width measurement mode, if the edge bit is a one, the timer will be allowed torun while the auxiliary input TAI is high. When TAI transitions from high to low, the timer will stop and, if the interrupt channel is enabled, an interrupt will occur. By having the interrupt occur on the one-to-zero transition instead of the zero-to-one transition, the processor will be interrupted when the pulse being measured has terminated and the width of the pulse is available from the timer. Therefore, the timers act like a divide-by-prescaler that can be programmed by the timer data register and the timer's A and B control register.

After reading the contents of the timer, the main counter must be reinitialized by writing to the timer data register to allow consecutive pulses to be measured. If the timer is written after the auxiliary input signal is active, the timer will count from the previous contents of the timer data register until it counts through 01 (hexadecimal). At the time, the main counter is loaded with the value from the timer data register, a time out pulse is generated which will tog-

gle the timer output, and an interrupt may be optionally generated on the timer interrupt channel.

Note that the pulse width measured will include counts from before the main counter was reloaded. If the timer data register is written while the pulse is transitioning to the active state, an indeterminate value may be written into the main counter.

Once the timer is reprogrammed for another mode, interrupts will again occur as normally defined by the edge bit. Note that an interrupt may be generated as the result of placing the timer into the pulse width measurement mode or by reprogramming the timer for another mode. Also, an interrupt may be generated by changing the state of the edge bit while in the pulse width measurement mode.

#### **EVENT COUNT MODE OPERATION**

In addition to the delay mode and the pulse width measurement mode, timers A and B may be programmed to operate in the event count mode. Like the pulse width measurement mode, the event count mode also requires an auxiliary input signal, TAI or TBI, and the interrupt channels normally associated with I4 and I3 will respond to transitions on TAI and TBI respectively. General purpose lines I3 and I4 only function as I/O ports.

In the event count mode the prescaler is disabled, allowing each active transition on TAI and TBI to produce a count pulse. The count pulse causes the main counter to decrement by one. When the timer counts through 01 (hexadecimal), a time out pulse is generated which will cause the output signal to toggle and may optionally produce an interrupt via the associated timer interrupt channel. The timer's main counter is also reloaded from the timer data register. To count transitions reliably, the input signal may only transition once every four timer clock periods. For this reason, the input signal must have a maximum frequency equal to one-fourth that of the timer clock.

The active edge of the auxiliary input signal is defined by the associated interrupt channel's edge bit. GPIP4 of the AER specifies the active edge for TAI and GPIP3 defines the active edge for TBI. When the edge bit is programmed to a one, a count pulse will be generated on the zero-to-one transition of the auxiliary input signal. When the edge bit is programmed to a zero, a count pulse will be generated on

the one-to-zero transition. Also, note that changing the state of the edge bit while the timer is in the event count mode may produce a count pulse.

Besides generating a count pulse, the active transition of the auxiliary input signal will also produce an interrupt on the I3 or I4 interrupt channel, if the interrupt channel is enabled. Typically, in the event count mode, these channels are not enabled since the timer is automatically counting transitions on the input signal. If the interrupt channel is enabled, the number of transitions could be counted in the interrupt routine without requiring the use of the timer.

#### TIMER REGISTERS

The four timers are programmed via three control registers and four timer data registers. Control registers TACR and TBCR and timer data registers TADR and TBDR (refer to figure 5.1) are associated with timers A and B respectively. Timers C and D are controlled by the control register TCDCR and the data registers TCDR and TDDR (refer to Figure 13).

#### TIMER DATA REGISTERS

Each timer's main counter is an 8-bit binary down counter. The value of the main counter may be read at any time by reading the timer's data register. The information read is the value of the counter which was captured on the last low-to-high transition of the DS pin.

The main counter is initialized by writing to the timer's data register. If the timer is stopped, data is loaded simultaneously into both the timer data register and the main counter. If the timer data register is written while the timer is enabled, the value is not loaded into the timer until the timer counts through 01 (hexadecimal). Writing the timer data register while the timer is counting through 01 (hexadecimal) will cause an indeterminate value to be loaded into the timer's main counter. The four data registers are shown in Figure 13.

#### TIMER CONTROL REGISTERS

Bits in the timer control registers select the operation mode, select the prescaler value, and disable the timers. Timer control registers TACR and TBCR also have bits which allow the programmer to reset out-

Figure 13:

|               |    |    |                  |            |           |                              |              | ŀ  | -igure 13 : |

|---------------|----|----|------------------|------------|-----------|------------------------------|--------------|----|-------------|

|               |    |    |                  |            |           |                              |              |    |             |

|               | 7  |    | (a)              | TIMER A DA | ATA REGIS | TER                          |              | 0  |             |

| TADR<br>(1Fh) | D7 | D6 | D5               | D4         | D3        | D2                           | D1           | D0 |             |

|               |    |    | (b) -            | TIMER B DA | ATA REGIS | TER                          |              |    |             |