PRELIMINARY - January 6, 1999

TEL:805-498-2111 FAX:805-498-3804 WEB:http://www.semtech.com

# DESCRIPTION

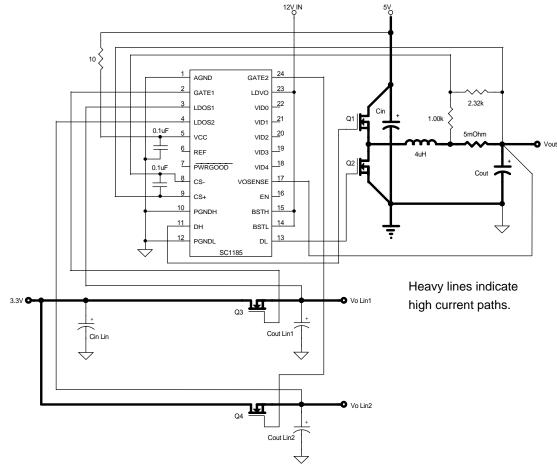

The SC1185 combines a synchronous voltage mode controller with two low-dropout linear regulators providing most of the circuitry necessary to implement three DC/DC converters for powering advanced microprocessors such as Pentium<sup>®</sup> II.

The SC1185 switching section features an integrated 5 bit D/A converter, pulse by pulse current limiting, integrated power good signaling, and logic compatible shutdown. The SC1185 switching section operates at a fixed frequency of 140kHz, providing an optimum compromise between size, efficiency and cost in the intended application areas. The integrated D/A converter provides programmability of output voltage from 2.0V to 3.5V in 100mV increments and 1.30V to 2.05V in 50mV increments with no external components.

The SC1185 linear sections are low dropout regulators supplying 1.5V for GTL bus and 2.5V for non-GTL I/O. The Reference voltage is made available for external linear regulators.

# **FEATURES**

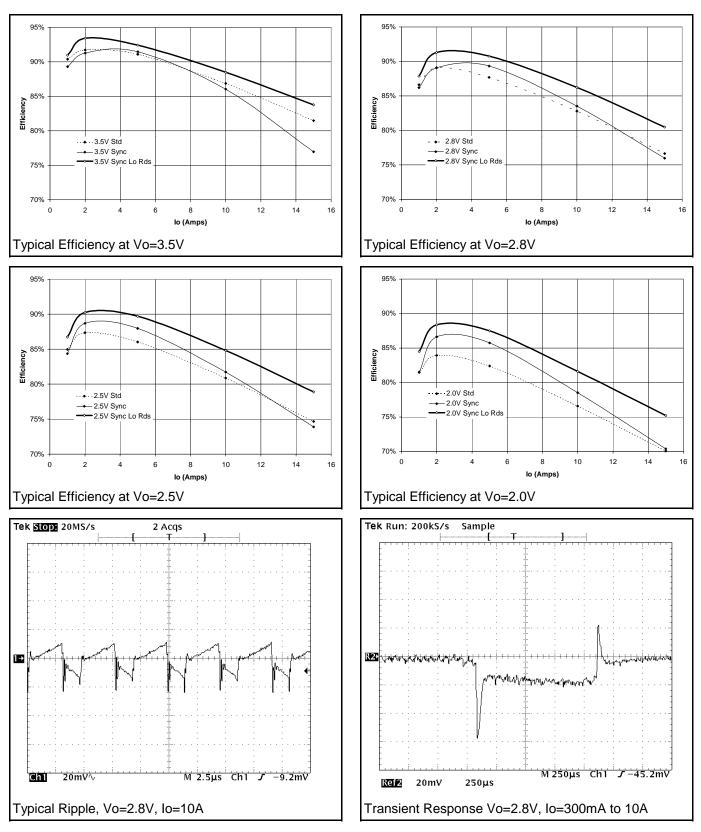

- Synchronous design, enables no heatsink solution

- 95% efficiency (switching section)

- 5 bit DAC for output programmability

- On chip power good function

- Designed for Intel Pentium<sup>®</sup> II requirements

- 1.5V, 2.5V @ 1% for linear section

- 1.265V ± 1.5% Reference available

## APPLICATIONS

- Pentium<sup>®</sup> II microprocessor supplies

- Flexible motherboards

- 1.3V to 3.5V microprocessor supplies

- Programmable triple power supplies

## **ORDERING INFORMATION**

| Part Number <sup>(1)</sup> | Package | Linear<br>Voltage | Temp.<br>Range (T <sub>J</sub> ) |

|----------------------------|---------|-------------------|----------------------------------|

| SC1185CSW                  | SO-24   | 1.5V/2.5V         | 0° to 125°C                      |

| SC1185ACSW <sup>(2)</sup>  | SO-24   | 1.5V/2.5V         | 0° to 125°C                      |

Note:

(1) Add suffix 'TR' for tape and reel.

(2) SC1185A provides improved output tolerance. See Output Voltage Table.

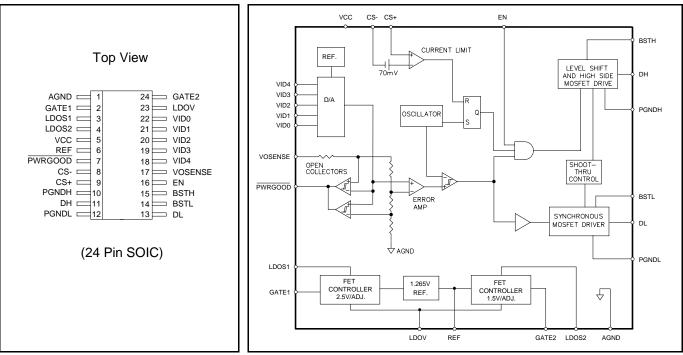

# PIN CONFIGURATION

Pentium is a registered trademark of Intel Corporation 1

**BLOCK DIAGRAM**

PRELIMINARY - January 6, 1999

### **ABSOLUTE MAXIMUM RATINGS**

| Parameter                               | Symbol           | Maximum     | Units |

|-----------------------------------------|------------------|-------------|-------|

| VCC to GND                              | V <sub>IN</sub>  | -0.3 to +7  | V     |

| PGND to GND                             |                  | ± 1         | V     |

| BST to GND                              |                  | -0.3 to +15 | V     |

| Operating Temperature Range             | T <sub>A</sub>   | 0 to +70    | °C    |

| Junction Temperature Range              | TJ               | 0 to +125   | °C    |

| Storage Temperature Range               | T <sub>STG</sub> | -65 to +150 | °C    |

| Lead Temperature (Soldering) 10 seconds | TL               | 300         | °C    |

| Thermal Impedance Junction to Ambient   | θ <sub>JA</sub>  | 80          | °C/W  |

| Thermal Impedance Junction to Case      | $\theta_{JC}$    | 25          | °C/W  |

## **ELECTRICAL CHARACTERISTICS**

Unless specified:  $V_{CC}$  = 4.75V to 5.25V; GND =  $P_{GND}$  = 0V;  $V_{OSENSE}$  =  $V_{O}$ ; 0mV < (CS+-CS-) < 60mV; LDOV = 11.4V to 12.6V;  $T_A$  = 0 to 70°C

| PARAMETER                    | CONDITIONS                                         | MIN      | TYP    | MAX     | UNITS   |

|------------------------------|----------------------------------------------------|----------|--------|---------|---------|

| Switching Section            |                                                    |          |        |         |         |

| Output Voltage               | $I_0 = 2A$ in Application Circuit                  | See      | Output | Voltage | Table   |

| Supply Voltage               | VCC                                                | 4.5      |        | 7       | V       |

| Supply Current               | VCC = 5.0V                                         |          | 8      | 15      | mA      |

| Load Regulation              | $I_{\rm O} = 0.8$ A to 15A                         |          | 1      |         | %       |

| Line Regulation              |                                                    |          | ±0.15  |         | %       |

| Current Limit Voltage        |                                                    | 60       | 70     | 85      | mV      |

| Oscillator Frequency         |                                                    | 125      | 140    | 160     | kHz     |

| Oscillator Max Duty Cycle    |                                                    | 90       | 95     |         | %       |

| Peak DH Sink/Source Current  | BSTH-DH = 4.5V, DH-PGNDH = 3.1V<br>DH-PGNDH = 1.5V | 1<br>100 |        |         | A<br>mA |

| Peak DL Sink/Source Current  | BSTL-DL = 4.5V, DL-PGNDL = 3.1V<br>DL-PGNDL = 1.5V | 1<br>100 |        |         | A<br>mA |

| Gain (A <sub>ol</sub> )      | VOSENSE to V <sub>o</sub>                          |          | 35     |         | dB      |

| VID Source Current           | $VIDx \le 2.4V$                                    | 1        | 10     |         | μA      |

| VID Leakage                  | VIDx = 5V                                          |          |        | 10      | μA      |

| Power good threshold voltage |                                                    | 88       |        | 112     | %       |

| Dead time                    |                                                    | 40       | 100    |         | ns      |

| Linear Sections              |                                                    |          |        |         |         |

| Quiescent current            | LDOV = 12V                                         |          |        | 5       | mA      |

| Output Voltage LDO1          |                                                    | 2.469    | 2.500  | 2.531   | V       |

| Output Voltage LDO2          |                                                    | 1.481    | 1.500  | 1.519   | V       |

| Reference Voltage            | Iref ≤ 100µA                                       | 1.246    | 1.265  | 1.284   | V       |

| Gain (A <sub>oL</sub> )      | LDOS (1,2) to GATE (1,2)                           |          | 90     |         | dB      |

| Load Regulation              | $I_0 = 0$ to 8A                                    |          |        | 0.3     | %       |

| Line Regulation              |                                                    |          |        | 0.3     | %       |

| Output Impedance             | $V_{GATE} = 6.5V$                                  |          | 1      | 1.5     | kΩ      |

| Gate Pulldown Impedance      | GATE(1,2)-AGND;VCC=LDOV=0V                         | 80       | 300    | 750     | kΩ      |

| VOSENSE Impedance            |                                                    | 10       |        |         | kΩ      |

PRELIMINARY - January 6, 1999

# **PIN DESCRIPTION**

| Pin | Pin Name                      | Pin Function                                                                                                    | 1                                                |

|-----|-------------------------------|-----------------------------------------------------------------------------------------------------------------|--------------------------------------------------|

| 1   | AGND                          | Small Signal Analog and Digital Ground                                                                          | -                                                |

| 2   | GATE1                         | Gate Drive Output LDO1                                                                                          |                                                  |

| 3   | LDOS1                         | Sense Input for LDO1                                                                                            |                                                  |

| 4   | LDOS2                         | Sense Input for LDO2                                                                                            | Top View                                         |

| 5   | VCC                           | Input Voltage                                                                                                   |                                                  |

| 6   | REF                           | Buffered Reference Voltage output                                                                               | AGND - 1 24 GATE2                                |

| 7   | PWRGOOD <sup>(1)</sup><br>CS- | Open collector logic output, high if V <sub>o</sub><br>within 10% of setpoint<br>Current Sense Input (negative) | GATE1  2 23 LDOV LDOS1 3 22 VID0 LDOS2 4 21 VID1 |

| 9   | CS+                           | Current Sense Input (negative)                                                                                  | _ VCC                                            |

| 10  | PGNDH                         | Power Ground for High Side Switch                                                                               | PWRGOOD 7 18 VID4                                |

| 11  | DH                            | High Side Driver Output                                                                                         | _ CS-                                            |

| 12  | PGNDL                         | Power Ground for Low Side Switch                                                                                |                                                  |

| 13  | DL                            | Low Side Driver Output                                                                                          | _ DH                                             |

| 14  | BSTL                          | Supply for Low Side Driver                                                                                      |                                                  |

| 15  | BSTH                          | Supply for High Side Driver                                                                                     | -                                                |

| 16  | EN <sup>(1)</sup>             | Logic low shuts down the converter;<br>High or open for normal operation.                                       | (24 Pin SOIC)                                    |

| 17  | VOSENSE                       | Top end of internal feedback chain                                                                              |                                                  |

| 18  | VID4 <sup>(1)</sup>           | Programming Input (MSB)                                                                                         |                                                  |

| 19  | VID3 <sup>(1)</sup>           | Programming Input                                                                                               | 1                                                |

| 20  | VID2 <sup>(1)</sup>           | Programming Input                                                                                               | 1                                                |

| 21  | VID1 <sup>(1)</sup>           | Programming Input                                                                                               | ]                                                |

| 22  | VID0 <sup>(1)</sup>           | Programming Input (LSB)                                                                                         | Note:                                            |

| 23  | LDOV                          | +12V for LDO section                                                                                            | (1) All logic level inputs and outputs are oper  |

| 24  | GATE2                         | Gate Drive Output LDO2                                                                                          | collector TTL compatible.                        |

PRELIMINARY - January 6, 1999

# OUTPUT VOLTAGE

Unless specified: 4.75V < VCC < 5.25V; GND = PGND = 0V; VOSENSE = V<sub>0</sub>; 0mV < (CS+-CS-) < 60mV; = 0°C < T<sub>j</sub> < 85°C

|                |       |       | Standard |       | 6     | A" Versio | n     |       |

|----------------|-------|-------|----------|-------|-------|-----------|-------|-------|

| PARAMETER      | VID   | MIN   | TYP      | MAX   | MIN   | TYP       | MAX   | UNITS |

|                | 43210 |       |          |       |       |           |       |       |

| Output Voltage | 01111 | 1.277 | 1.300    | 1.323 | 1.287 | 1.300     | 1.313 | V     |

|                | 01110 | 1.326 | 1.350    | 1.374 | 1.337 | 1.350     | 1.364 |       |

|                | 01101 | 1.375 | 1.400    | 1.425 | 1.386 | 1.400     | 1.414 |       |

|                | 01100 | 1.424 | 1.450    | 1.476 | 1.436 | 1.450     | 1.465 |       |

|                | 01011 | 1.478 | 1.500    | 1.523 | 1.485 | 1.500     | 1.515 |       |

|                | 01010 | 1.527 | 1.550    | 1.573 | 1.535 | 1.550     | 1.566 |       |

|                | 01001 | 1.576 | 1.600    | 1.624 | 1.584 | 1.600     | 1.616 |       |

|                | 01000 | 1.625 | 1.650    | 1.675 | 1.634 | 1.650     | 1.667 |       |

|                | 00111 | 1.675 | 1.700    | 1.726 | 1.683 | 1.700     | 1.717 |       |

|                | 00110 | 1.724 | 1.750    | 1.776 | 1.733 | 1.750     | 1.768 |       |

|                | 00101 | 1.782 | 1.800    | 1.818 | 1.782 | 1.800     | 1.818 |       |

|                | 00100 | 1.832 | 1.850    | 1.869 | 1.832 | 1.850     | 1.869 |       |

|                | 00011 | 1.881 | 1.900    | 1.919 | 1.881 | 1.900     | 1.919 |       |

|                | 00010 | 1.931 | 1.950    | 1.970 | 1.931 | 1.950     | 1.970 |       |

|                | 00001 | 1.980 | 2.000    | 2.020 | 1.980 | 2.000     | 2.020 |       |

|                | 00000 | 2.030 | 2.050    | 2.071 | 2.030 | 2.050     | 2.071 |       |

|                | 11111 | 1.970 | 2.000    | 2.030 | 1.970 | 2.000     | 2.030 |       |

|                | 11110 | 2.069 | 2.100    | 2.132 | 2.069 | 2.100     | 2.132 |       |

|                | 11101 | 2.167 | 2.200    | 2.233 | 2.167 | 2.200     | 2.233 |       |

|                | 11100 | 2.266 | 2.300    | 2.335 | 2.266 | 2.300     | 2.335 |       |

|                | 11011 | 2.364 | 2.400    | 2.436 | 2.364 | 2.400     | 2.436 |       |

|                | 11010 | 2.463 | 2.500    | 2.538 | 2.463 | 2.500     | 2.538 |       |

|                | 11001 | 2.561 | 2.600    | 2.639 | 2.561 | 2.600     | 2.639 |       |

|                | 11000 | 2.660 | 2.700    | 2.741 | 2.660 | 2.700     | 2.741 |       |

|                | 10111 | 2.758 | 2.800    | 2.842 | 2.758 | 2.800     | 2.842 |       |

|                | 10110 | 2.842 | 2.900    | 2.958 | 2.842 | 2.900     | 2.958 |       |

|                | 10101 | 2.940 | 3.000    | 3.060 | 2.940 | 3.000     | 3.060 |       |

|                | 10100 | 3.038 | 3.100    | 3.162 | 3.038 | 3.100     | 3.162 |       |

|                | 10011 | 3.136 | 3.200    | 3.264 | 3.136 | 3.200     | 3.264 |       |

|                | 10010 | 3.234 | 3.300    | 3.366 | 3.234 | 3.300     | 3.366 |       |

|                | 10001 | 3.332 | 3.400    | 3.468 | 3.332 | 3.400     | 3.468 |       |

|                | 10000 | 3.430 | 3.500    | 3.570 | 3.430 | 3.500     | 3.570 |       |

SC1185 SC1185A

PRELIMINARY - January 6, 1999

PRELIMINARY - January 6, 1999

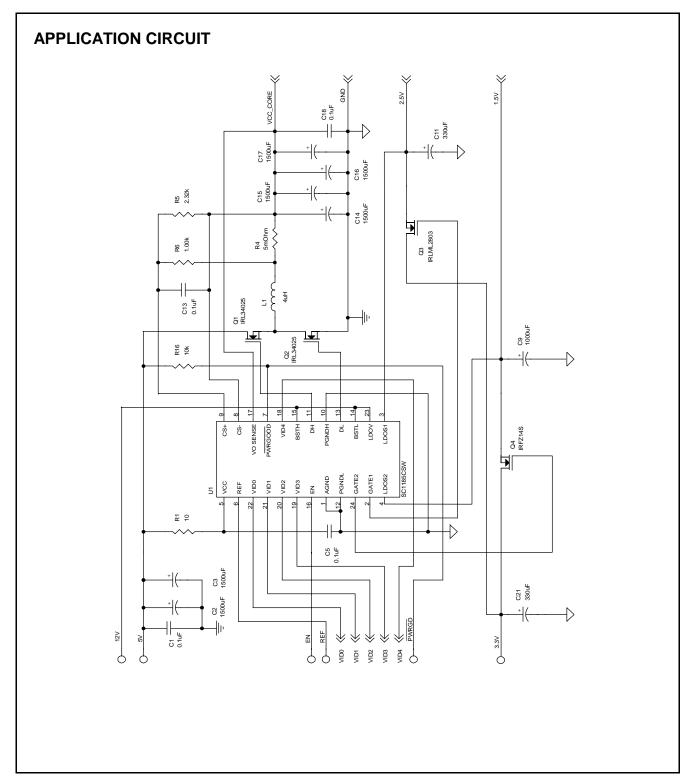

# MATERIALS LIST

| Qty. | Reference     | Part/Description | Vendor    | Notes                                                                                                                      |

|------|---------------|------------------|-----------|----------------------------------------------------------------------------------------------------------------------------|

| 4    | C1,C5,C13,C18 | 0.1µF Ceramic    | Various   |                                                                                                                            |

| 6    | C2,C3,C14-C17 | 1500µF/6.3V      | SANYO     | MV-GX or equiv. Low ESR                                                                                                    |

| 1    | C9            | 1000µF           |           |                                                                                                                            |

| 2    | C11,C21       | 330µF/6.3V       | Various   |                                                                                                                            |

| 1    | L1            | 4µH              |           | 8 Turns 16AWG on MICROMETALS T50-52D core                                                                                  |

| 2    | Q1,Q2         | See notes        | See notes | FET selection requires trade-off between efficiency and cost. Absolute maximum $R_{DS(ON)} = 22 \text{ m}\Omega$ for Q1,Q2 |

| 1    | Q3            | IRLML2803        | IR        | .25Ω 30V SOT23 (or equavilent)                                                                                             |

| 1    | Q4            | IRFZ14S          | IR        | Or equivalent                                                                                                              |

| 1    | R4            | 5mΩ              | IRC       | OAR-1 Series                                                                                                               |

| 1    | R5            | 2.32kΩ, 1%, 1/8W | Various   |                                                                                                                            |

| 1    | R6            | 1kΩ, 1%, 1/8W    | Various   |                                                                                                                            |

| 1    | R1            | 10Ω, 5%, 1/8W    | Various   |                                                                                                                            |

| 1    | U1            | SC1185CSW        | SEMTECH   |                                                                                                                            |

PRELIMINARY - January 6, 1999

7

PRELIMINARY - January 6, 1999

## LAYOUT GUIDELINES

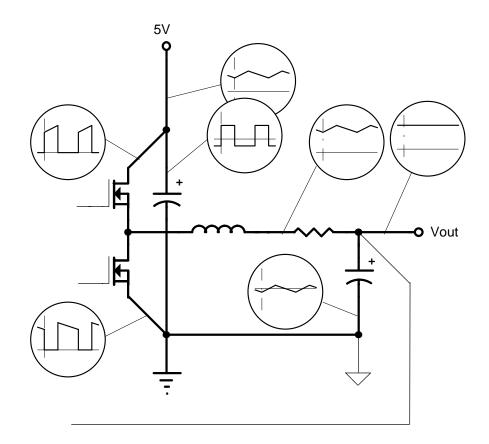

Careful attention to layout requirements are necessary for successful implementation of the SC1185 PWM controller. High currents switching at 140kHz are present in the application and their effect on ground plane voltage differentials must be understood and minimized.

1). The high power parts of the circuit should be laid out first. A ground plane should be used, the number and position of ground plane interruptions should be such as to not unnecessarily compromise ground plane integrity. Isolated or semi-isolated areas of the ground plane may be deliberately introduced to constrain ground currents to particular areas, for example the input capacitor and bottom FET ground.

2). The loop formed by the Input Capacitor(s) (Cin), the Top FET (Q1) and the Bottom FET (Q2) must be kept

as small as possible. This loop contains all the high current, fast transition switching. Connections should be as wide and as short as possible to minimize loop inductance. Minimizing this loop area will a) reduce EMI, b) lower ground injection currents, resulting in electrically "cleaner" grounds for the rest of the system and c) minimize source ringing, resulting in more reliable gate switching signals.

3). The connection between the junction of Q1, Q2 and the output inductor should be a wide trace or copper region. It should be as short as practical. Since this connection has fast voltage transitions, keeping this connection short will minimize EMI. The connection between the output inductor and the sense resistor should be a wide trace or copper area, there are no fast voltage or current transitions in this connection and length is not so important, however adding unnecessary impedance will reduce efficiency.

Layout diagram for the SC1185

## PRELIMINARY - January 6, 1999

4) The Output Capacitor(s) (Cout) should be located as close to the load as possible, fast transient load currents are supplied by Cout only, and connections between Cout and the load must be short, wide copper areas to minimize inductance and resistance.

5) The SC1185 is best placed over a quiet ground plane area, avoid pulse currents in the Cin, Q1, Q2 loop flowing in this area. PGNDH and PGNDL should be returned to the ground plane close to the package. The AGND pin should be connected to the ground side of (one of) the output capacitor(s). If this is not possible, the AGND pin may be connected to the ground path between the Output Capacitor(s) and the Cin, Q1, Q2 loop. Under no circumstances should AGND be returned to a ground inside the Cin, Q1, Q2 loop.

6) Vcc for the SC1185 should be supplied from the 5V

supply through a  $10\Omega$  resistor, the Vcc pin should be decoupled directly to AGND by a  $0.1\mu F$  ceramic capacitor, trace lengths should be as short as possible.

7) The Current Sense resistor and the divider across it should form as small a loop as possible, the traces running back to CS+ and CS- on the SC1185 should run parallel and close to each other. The  $0.1\mu F$  capacitor should be mounted as close to the CS+ and CS- pins as possible.

8) Ideally, the grounds for the two LDO sections should be returned to the ground side of (one of) the output capacitor(s).

Currents in various parts of the power section

PRELIMINARY - January 6, 1999

## **COMPONENT SELECTION**

#### SWITCHING SECTION

OUTPUT CAPACITORS - Selection begins with the most critical component. Because of fast transient load current requirements in modern microprocessor core supplies, the output capacitors must supply all transient load current requirements until the current in the output inductor ramps up to the new level. Output capacitor ESR is therefore one of the most important criteria. The maximum ESR can be simply calculated from:

$$\mathsf{R}_{\mathsf{ESR}} \leq \frac{\mathsf{V}_{\mathsf{t}}}{\mathsf{I}_{\mathsf{t}}}$$

Where

V<sub>t</sub> = Maximum transient voltage excursion

I<sub>t</sub> = Transient current step

For example, to meet a 100mV transient limit with a 10A load step, the output capacitor ESR must be less than  $10m\Omega$ . To meet this kind of ESR level, there are three available capacitor technologies.

|                  | Each Capacitor |             |              | To        | tal         |

|------------------|----------------|-------------|--------------|-----------|-------------|

| Technology       | С<br>(µF)      | ESR<br>(mΩ) | Qty.<br>Rqd. | С<br>(µF) | ESR<br>(mΩ) |

| Low ESR Tantalum | 330            | 60          | 6            | 2000      | 10          |

| OS-CON           | 330            | 25          | 3            | 990       | 8.3         |

| Low ESR Aluminum | 1500           | 44          | 5            | 7500      | 8.8         |

The choice of which to use is simply a cost/performance issue, with Low ESR Aluminum being the cheapest, but taking up the most space.

INDUCTOR - Having decided on a suitable type and value of output capacitor, the maximum allowable value of inductor can be calculated. Too large an inductor will produce a slow current ramp rate and will cause the output capacitor to supply more of the transient load current for longer - leading to an output voltage sag below the ESR excursion calculated above. The maximum inductor value may be calculated from:

$$L \le \frac{R_{ESR} C}{I_{t}} \left( V_{IN} - V_{O} \right)$$

The calculated maximum inductor value assumes 100% duty cycle, so some allowance must be made. Choosing an inductor value of 50 to 75% of the calculated maximum will guarantee that the inductor current will ramp

fast enough to reduce the voltage dropped across the ESR at a faster rate than the capacitor sags, hence ensuring a good recovery from transient with no additional excursions.

We must also be concerned with ripple current in the output inductor and a general rule of thumb has been to allow 10% of maximum output current as ripple current. Note that most of the output voltage ripple is produced by the inductor ripple current flowing in the output capacitor ESR. Ripple current can be calculated from:

$$I_{L_{RIPPLE}} = \frac{V_{IN}}{4 \cdot L \cdot f_{OSC}}$$

Ripple current allowance will define the minimum permitted inductor value.

POWER FETS - The FETs are chosen based on several criteria with probably the most important being power dissipation and power handling capability.

TOP FET - The power dissipation in the top FET is a combination of conduction losses, switching losses and bottom FET body diode recovery losses.

a) Conduction losses are simply calculated as:

$$\mathsf{P}_{\mathsf{COND}} = \mathsf{I}_{\mathsf{O}}^2 \cdot \mathsf{R}_{\mathsf{DS(on)}} \cdot \delta$$

where

$$\delta = \text{duty cycle} \approx \frac{V_O}{V_{IN}}$$

b) Switching losses can be estimated by assuming a switching time, if we assume 100ns then:

$$\mathsf{P}_{\mathsf{SW}} = \mathsf{I}_{\mathsf{O}} \cdot \mathsf{V}_{\mathsf{IN}} \cdot 10^{-2}$$

or more generally,

$$\mathsf{P}_{\mathsf{SW}} = \frac{\mathsf{I}_{\mathsf{O}} \cdot \mathsf{V}_{\mathsf{IN}} \cdot (\mathsf{t}_{\mathsf{r}} + \mathsf{t}_{\mathsf{f}}) \cdot \mathsf{f}_{\mathsf{OSC}}}{4}$$

c) Body diode recovery losses are more difficult to estimate, but to a first approximation, it is reasonable to assume that the stored charge on the bottom FET body diode will be moved through the top FET as it starts to turn on. The resulting power dissipation in the top FET will be:

$$\mathsf{P}_{\mathsf{R}\mathsf{R}} = \mathsf{Q}_{\mathsf{R}\mathsf{R}} \cdot \mathsf{V}_{\mathsf{I}\mathsf{N}} \cdot \mathsf{f}_{\mathsf{OSC}}$$

To a first order approximation, it is convenient to only consider conduction losses to determine FET suitability. For a 5V in; 2.8V out at 14.2A requirement, typical FET losses would be:

#### PRELIMINARY - January 6, 1999

Using 1.5X Room temp  $R_{\mbox{\tiny DS(ON)}}$  to allow for temperature rise.

| FET type | $R_{DS(on)}(m\Omega)$ | $P_{D}(W)$ | Package            |

|----------|-----------------------|------------|--------------------|

| IRL34025 | 15                    | 1.69       | D <sup>2</sup> PAK |

| IRL2203  | 10.5                  | 1.19       | D <sup>2</sup> PAK |

| Si4410   | 20                    | 2.26       | SO-8               |

BOTTOM FET - Bottom FET losses are almost entirely due to conduction. The body diode is forced into conduction at the beginning and end of the bottom switch conduction period, so when the FET turns on and off, there is very little voltage across it, resulting in low switching losses. Conduction losses for the FET can be determined by:

$$P_{\text{COND}} \!=\! I_{\text{O}}^2 \cdot R_{\text{DS(on)}} \cdot (1\!-\!\delta)$$

For the example above:

| FET type | $R_{DS(on)}(m\Omega)$ | $P_D(W)$ | Package            |

|----------|-----------------------|----------|--------------------|

| IRL34025 | 15                    | 1.33     | D <sup>2</sup> PAK |

| IRL2203  | 10.5                  | 0.93     | D <sup>2</sup> PAK |

| Si4410   | 20                    | 1.77     | SO-8               |

Each of the package types has a characteristic thermal impedance, for the TO-220 package, thermal impedance is mostly determined by the heatsink used. For the surface mount packages on double sided FR4, 2 oz printed circuit board material, thermal impedances of  $40^{\circ}$ C/W for the D<sup>2</sup>PAK and  $80^{\circ}$ C/W for the SO-8 are readily achievable. The corresponding temperature rise is detailed below:

|          | Temperature rise (°C) |            |  |  |  |

|----------|-----------------------|------------|--|--|--|

| FET type | Top FET               | Bottom FET |  |  |  |

| IRL34025 | 67.6                  | 53.2       |  |  |  |

| IRL2203  | 47.6                  | 37.2       |  |  |  |

| Si4410   | 180.8                 | 141.6      |  |  |  |

It is apparent that single SO-8 Si4410 are not adequate for this application, but by using parallel pairs in each position, power dissipation will be approximately halved and temperature rise reduced by a factor of 4.

INPUT CAPACITORS - since the RMS ripple current in the input capacitors may be as high as 50% of the output current, suitable capacitors must be chosen accordingly. Also, during fast load transients, there may be restrictions on input di/dt. These restrictions require useable energy storage within the converter circuitry, either as extra output capacitance or, more usually, additional input capacitors. Choosing low ESR input capacitors will help maximize ripple rating for a given size.

PRELIMINARY - January 6, 1999

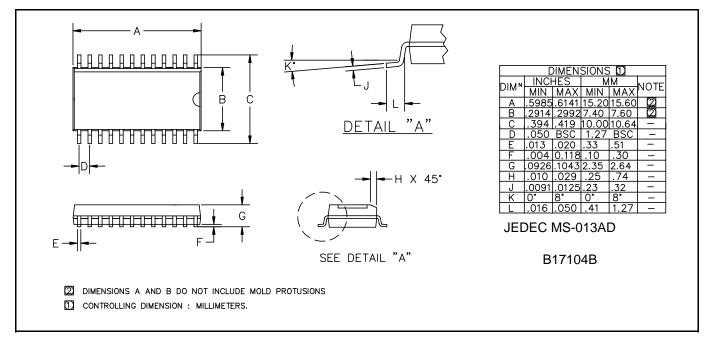

## OUTLINE DRAWING