SANYO

NMOS LSI

LM7001J, 7001JM

## **Direct PLL Frequency Synthesizers** for Electronic Tuning

## Features

• The LM7001J and LM7001JM are PLL frequency synthesizer LSIs for tuners, making it possible to make up high-performance AM/FM tuners easily.

No. 5262

- · These LSIs are software compatible with the LM7000, but do not include an IF calculation circuit.

- The FM VCO circuit includes a high-speed programmable divider that can divide directly.

- Seven reference frequencies: 1, 5, 9, 10, 25, 50, and 100 kHz

- Band-switching outputs (3 bits)

- Controller clock output (400 kHz)

- Clock time base output (8 Hz)

- · Serial input circuit for data input (using the CE, CL, and DATA pins)

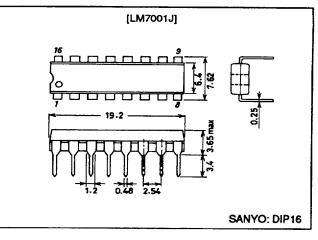

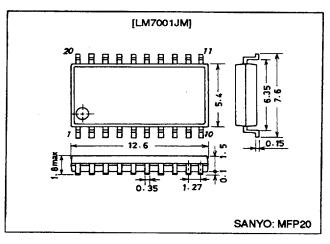

### Package Dimensions

unit: mm

3006B-DIP16

# SANYO Electric Co., Ltd. Semiconductor Business Headquarters TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110 JAPAN

7997076 0016302 918 🛲

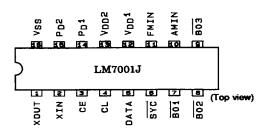

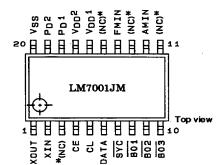

#### **Pin Assignments**

Note: \* NC pins must be left open.

## Specifications

## Absolute Maximum Ratings at $Ta = 25^{\circ}C$ , $V_{SS} = 0$ V

| Parameter                   | Parameter Symbol Conditions |                                         |                               | Unit |

|-----------------------------|-----------------------------|-----------------------------------------|-------------------------------|------|

| Maximum supply voltage      | V <sub>DD</sub> max         | V <sub>DD</sub> 1, V <sub>DD</sub> 2    | 0.3 to +7.0                   | V    |

| Maximum input voltage       | V <sub>IN</sub> 1 max       | CE, CL, DATA                            | -0.3 to +7.0                  | V    |

|                             | V <sub>IN</sub> 2 max       | Input pins other than V <sub>IN</sub> 1 | -0.3 to V <sub>DD</sub> + 0.3 | V    |

| Maximum output voltage      | V <sub>OUT</sub> 1 max      | SYC                                     | -0.3 to +7.0                  | V    |

|                             | V <sub>OUT</sub> 2 max      | BO1 to BO3                              | -0.3 to +13                   | V    |

|                             | V <sub>OUT</sub> 3 max      | Output pins other than VOUT1 and VOUT2  | -0.3 to V <sub>DD</sub> + 0.3 | V    |

| Maximum output current      | lout max                    | BO1 to BO3                              | 0 to 3.0                      | mA   |

| Allowable power dissipation |                             | Ta = 85°C: LM7001J (DIP16)              | 300                           | m₩   |

|                             | Pd max                      | Ta = 85°C: LM7001JM (MFP20)             | 180                           | mW   |

| Operating temperature       | Topr                        |                                         | -40 to +85                    | °C   |

| Storage temperature         | Tstg                        |                                         | -55 to +125                   | °C   |

#### Allowable Operating Ranges at Ta = -40 to +85°C, $V_{SS} = 0$ V

| Parameter Symbol                           |                   | Conditions                                      | Ratings               | Unit |

|--------------------------------------------|-------------------|-------------------------------------------------|-----------------------|------|

|                                            | V <sub>DD</sub> 1 | V <sub>DD</sub> 1, PLL circuit operating        | 4.5 to 6.5            | V    |

| Supply voltage                             | V <sub>DD</sub> 2 | V <sub>DD</sub> 2, crystal oscillator time base | 3.5 to 6.5            | V    |

| Input high-level voltage                   | VIH               | CE, CL, DATA                                    | 2.2 to 6.5            | v    |

| Input low-level voltage                    | VIL               | CE, CL, DATA                                    | 0 to 0.7              | V    |

|                                            | Vout1             | SYC                                             | 0 to 6.5              | V    |

| Output voltage                             | Vout2             | BOI to BO3                                      | 0 to 13               | V    |

| Output current                             | юл                | BO1 to BO3, V <sub>DD</sub> = 4.5 to 6.5 V      | 0 to 3.0              | mA   |

|                                            | f <sub>IN</sub> 1 | XIN, sine wave, capacitor coupled               | 1.0 to 7.2 typ to 8.0 | MHz  |

| have for success                           | f <sub>IN</sub> 2 | FMIN, sine wave, capacitor coupled*1, s*3 = 1   | 45 to 130             | MHz  |

| Input frequency                            | f <sub>IN</sub> 3 | FMIN, sine wave, capacitor coupled*2, s*3 = 1   | 5 to 30               | MHz  |

|                                            | f <sub>IN</sub> 4 | AMIN, sine wave, capacitor coupled, s*3 = 0     | 0.5 to 10             | MHz  |

| Crystal element for guaranteed oscillation | Xtal              | XIN to XOUT, $CI \le 30 \Omega$                 | 5.0 to 7.2 typ to 8.0 | MHz  |

|                                            | V <sub>IN</sub> 1 | XIN, sine wave, capacitor coupled               | 0.5 to 1.5            | Vrms |

| Input amplitude                            | V <sub>IN</sub> 2 | FMIN, sine wave, capacitor coupled 0.1 to       |                       | Vrms |

|                                            | V <sub>IN</sub> 3 | AMIN, sine wave, capacitor coupled 0.1 to 1.    |                       | Vrms |

Note: 1. fret = 25, 50, or 100 kHz

2. frot = Reference frequencies other than those for \*1. 3. "s" refers to the control bit in the serial data.

- 📖 7997076 0016303 854 📖

| Parameter                                 | Symbol            | Conditions                                                        | min                 | typ  | max  | Unit |

|-------------------------------------------|-------------------|-------------------------------------------------------------------|---------------------|------|------|------|

| Built-in feedback resistance              | R <sub>f1</sub>   | XIN                                                               |                     | 1.0  |      | MΩ   |

|                                           | R <sub>f2</sub>   | FMIN                                                              |                     | 500  |      | kΩ   |

|                                           | R <sub>f3</sub>   | AMIN                                                              |                     | 500  |      | kΩ   |

| Input high-level current                  | I <sub>IH</sub>   | CE, CL, DATA: V <sub>IN</sub> = 6.5 V                             |                     |      | 5.0  | μA   |

| input low-level current                   | ۱ <sub>۱</sub>    | CE, CL, DATA: VIN = 0 V                                           |                     |      | 5.0  | μА   |

|                                           | Vol1              | FMIN, AMIN: I <sub>OUT</sub> = 0.5 mA                             |                     |      | 3.5  | V    |

|                                           | VOL2              | SYC: I <sub>OUT</sub> = 0.1 mA, *1                                | 0.02                |      | 0.3  | v    |

| Output low-level voltage                  | V <sub>OL</sub> 3 | $\overline{BO1}$ to $\overline{BO3}$ : $I_{OUT} = 2.0 \text{ mA}$ |                     |      | 1.0  | V    |

|                                           | V <sub>OL</sub> 4 | $P_D1, P_D2: I_{OUT} = 0.1 \text{ mA}$                            |                     |      | 0.3  | v    |

| Output off leakage current                | IOFF1             | <u>SYC</u> : V <sub>OUT</sub> = 6.5 V                             |                     |      | 5.0  | μA   |

|                                           | IOFF2             | $\overline{BO1}$ to $\overline{BO3}$ : V <sub>OUT</sub> = 13 V    |                     |      | 3.0  | μΑ   |

| Output high-level voltage                 | V <sub>OH</sub>   | $P_D1, P_D2: I_{OUT} = -0.1 \text{ mA}$                           | 0.5 V <sub>DD</sub> |      |      | V    |

| High-level 3-state<br>off leakage current | OFFH              | $P_D1$ , $P_D2$ : $V_{OUT} = V_{DD}$                              |                     | 0.01 | 10.0 | nA   |

| Low-level 3-state<br>off leakage current  | <b>IOFFL</b>      | P <sub>D</sub> 1, P <sub>D</sub> 2: V <sub>OUT</sub> = 0 V        |                     | 0.01 | 10.0 | nA   |

|                                           | I <sub>DD</sub> 1 | V <sub>DD</sub> 1 + V <sub>DD</sub> 2: *2                         |                     | 25   | 40   | mA   |

| Current drain                             | I <sub>DD</sub> 2 | V <sub>DD</sub> 2: PLL block stopped                              |                     | 2.0  | 3.5  | mA   |

| Input capacitance                         | CIN               | FMIN                                                              | 1                   | 2    | 3    | pF   |

#### **Electrical Characteristics in the Allowable Operating Ranges**

Note: 1. V<sub>DD</sub> = 3.5 to 6.5 V

2. With a 7.2 MHz crystal connected between XIN and XOUT; f<sub>IN</sub>2 = 130 MHz, V<sub>IN</sub>2 = 100 mVrms, other input pins at V<sub>SS</sub>, output pins open.

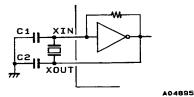

#### **Oscillator Circuit Example**

Kinseki, Ltd. HC43/U: 2114-84521 (1): CL = 10 pF, C1 = 15 (10 to 22) pF, C2 = 15 pF HC43/U: 2114-84521 (2): CL = 16 pF, C1 = 22 (15 to 33) pF, C2 = 33 pF

Nihon Denpa Kogyou, Ltd. NR-18: LM-X-0701: CL = 10 pF, C1 = 15 pF, C2 = 15 pF

Since the circuit constants in the crystal oscillator circuit depend on the crystal element used and the printed circuit board pattern, we recommend consulting with the manufacturer of the crystal element concerning this circuit.

79970760016304790 📟

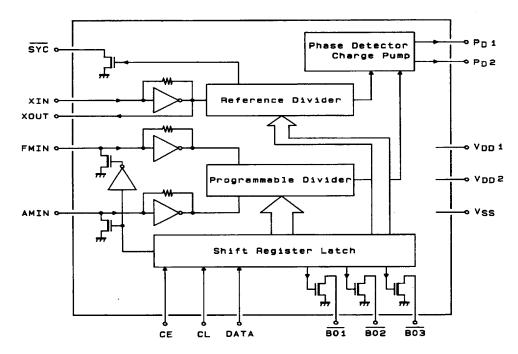

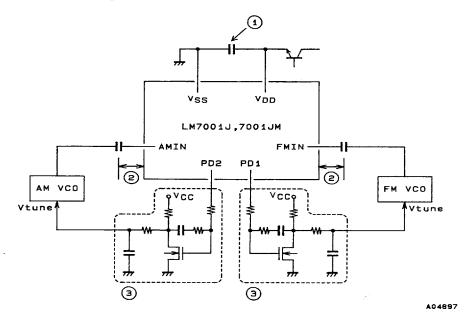

#### **Equivalent Circuit Block Diagram**

#### **Pin Functions**

| Symbol                                                | Description                                                                                                                                                                                                         |

|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SYC                                                   | Controller clock (400 kHz)                                                                                                                                                                                          |

| XIN, XOUT                                             | Crystal oscillator (7.2 MHz)                                                                                                                                                                                        |

| FMIN, AMIN                                            | Local oscillator signal input                                                                                                                                                                                       |

| CE, CL, DATA                                          | Data input                                                                                                                                                                                                          |

| BO1 to BO3                                            | Band data output. BOT can be used as a time base output (8 Hz).                                                                                                                                                     |

| V <sub>DD</sub> 1, V <sub>DD</sub> 2, V <sub>SS</sub> | Power supply (Apply power to both $V_{DD}1$ and $V_{DD}2$ when the PLL circuit is operating. $V_{DD}2$ is the crystal oscillator and time base power supply. Internal data cannot be maintained on $V_{DD}2$ only.) |

| P <sub>D</sub> 1, P <sub>D</sub> 2                    | Charge pump output                                                                                                                                                                                                  |

### - 📰 7997076 0016305 627 📰 -

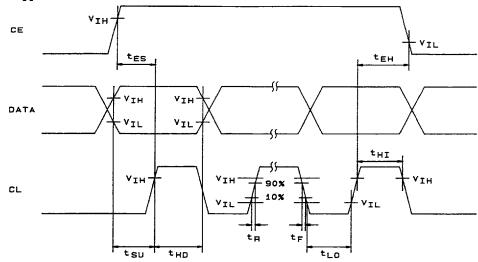

#### **Data Input Timing**

$V_{IH}$  = 2.2 to 6.5 V,  $V_{IL}$  = 0 to 0.7 V, Xtal = 5.00 to 7.20 (typ) to 8.00 MHz

Data acquisition: On the CL rising edge \_\_\_\_\_

Note: Data transfers must be started only after the crystal oscillator is operating normally, i.e., after a proper input signal has been supplied to XIN.

| Parameter             | Symbol          | Xtal: 7.20 MHz  | Xtal: for frequencies other than 7.2 MHz                              | Example: XIN = 2.048 MHz |  |

|-----------------------|-----------------|-----------------|-----------------------------------------------------------------------|--------------------------|--|

| Enable setup time     | tes             | At least 1.5 µs | At least $\left[\frac{1 \times 8}{f \times tal}\right] \times 1.35$   | At least 5.27 µs         |  |

| Enable hold time      | t <sub>EH</sub> | At least 1.5 μs | At least $\left[\frac{1 \times 8}{f \times tai}\right] \times 1.35$   | At least 5.27 µs         |  |

| Data setup time       | tsu             | At least 1.5 µs | At least $\left[\frac{1 \times 8}{f \text{ Xtal}}\right] \times 1.35$ | At least 5.27 µs         |  |

| Data hold time        | <sup>t</sup> HD | At least 1.5 µs | At least $\left[\frac{1 \times 8}{f \text{ Xtal}}\right] \times 1.35$ | At least 5.27 μs         |  |

| Clock low-level time  | ŧο              | At least 1.5 μs | At least $\left[\frac{1 \times 8}{f \text{ Xtal}}\right] \times 1.35$ | At least 5.27 µs         |  |

| Clock high-level time | î-HI            | At least 1.5 µs | At least $\left[\frac{1 \times 8}{f \text{ Xtal}}\right] \times 1.35$ | At least 5.27 µs         |  |

| Rise time             | t <sub>R</sub>  | Up to 1 µs      | Up to 1 µs                                                            | Up to 1 µs               |  |

| Fall time             | ۴.              | Up to 1 µs      | Up to 1 µs                                                            | Up to 1 µs               |  |

7997076 0016306 563 📟 -

A04896

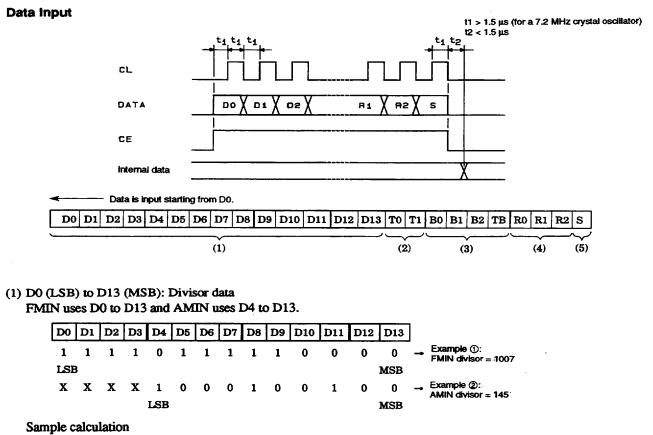

#### LM7001J, 7001JM

(1) FM 100 kHz steps ( $f_{ref} = 100$  kHz) FM VCO = 100.7 MHz (FM RF = 90.0 MHz, IF = 10.7 MHz) Divisor = 100.7 MHz (FM VCO) + 100 kHz ( $f_{ref}$ ) = 1007  $\rightarrow$  3EF<sub>(HEX)</sub>

(2) AM 10 kHz steps ( $f_{ref} = 10 \text{ kHz}$ ) AM VCO = 1450 kHz (AM RF = 1000 kHz, IF = 450 kHz) Divisor = 1450 kHz (AM VCO) + 10 kHz ( $f_{ref}$ ) = 145  $\rightarrow$  91<sub>(HEX)</sub>

(2) T0 and T1 are LSI test bits and both should be set to 0.

## (3) B0 to B2, TB: Band data

Time base data Note: \*: Determined by R0 to R3. See item (4) on next page. Input Output BO1 BO2 BO3 BO **B**1 **B**2 TB . \* . o ΤВ . . × ΤВ × TB × тв ТВ Don't care X: TB: 8 Hz 7997076 0016307 4TT 🖿

This Material Copyrighted By Its Respective Manufacturer

#### (4) R0 to R2: Reference frequency data

| R0 | R1 | R2 | f <sub>ref</sub> [kHz]<br>100 | BO1 | BO2 | BO3 |

|----|----|----|-------------------------------|-----|-----|-----|

| 0  | 0  | 0  | 100                           | 1   | 1   | 0   |

| 0  | 0  | 1  | 50                            | 1   | 1   | 0   |

| 0  | 1  | 0  | 25                            | 1   | 1   | 0   |

| 0  | 1  | 1  | 5                             | 0   | 0   | 1   |

| 1  | 0  | 0  | 10                            | 1   | 0   | 1   |

| 1  | 0  | 1  | 9                             | 1   | 0   | 1   |

| 1  | 1  | 0  | 1                             | 0   | 1   | 1   |

| 1  | 1  | 1  | 5                             | 0   | 0   | 1   |

Note: The values listed for BO1, BO2, and BO3 are for the case when the B0 to B2 data is set to all zeros.

#### (5) S: Divider selection data

1: FMIN, 0: AMIN

#### Notes on PLL IC Usage

#### 1. PLL IC printed circuit board patterns

#### ① Power supply pins

A capacitor must be inserted between the  $V_{DD}$  and  $V_{SS}$  power supply pins for noise exclusion. This capacitor must be located as close as possible to these pins.

② FMIN and AMIN pins

The coupling capacitors must be located as close as possible to these pins.

- ③ PD pins, low-pass filter Since those are high-impedance pins, they are susceptible to noise. Therefore, the pattern should be kept as short as possible and the area around this circuit should be covered by the ground pattern.

- 2. Initial states of the output ports ( $\overline{BO1}$  to  $\overline{BO3}$ )

The initial states of the output ports after power is applied are undefined until data has been transferred. In particular, it is possible for the  $\overline{BO1}$  and  $\overline{BO3}$  pins to output the internal clock, so data must be transferred as soon as possible.

However, note that the LSI cannot accept data until the crystal oscillator is operating normally.

7997076 0016308 336 📟

3. VCO

The VCO circuit is designed so that it does not stop oscillating even if the control voltage (Vtune) becomes 0 V. (This is because the PLL circuit could become deadlocked if the VCO stopped.)

No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace equipment, nuclear power control systems, vehicles, disaster/crime-prevention equipment and the like, the failure of which may directly or indirectly cause injury, death or property loss.

Anyone purchasing any products described or contained herein for an above-mentioned use shall:

① Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors and all their officers and employees, jointly and severally, against any and all claims and litigation and all damages, cost and expenses associated with such use:

- ② Not impose any responsibility for any fault or negligence which may be cited in any such claim or litigation on SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors or any of their officers and employees jointly or severally.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of December, 1995. Specifications and information herein are subject to change without notice.

7997076 0016309 272 🎟