## ASI4U

Universal Actuator-Sensor Interface IC Datasheet

## Features

- Universal application in AS-i Slave, Master, Repeater and Bus-Monitor components

- Support of AS-i Complete Specification V3.0, including all optional features

- Synchronous Data I/O Mode

- 4 Input / 4 Output operation in Extended Address Mode

- User write protection for Extended ID-Code 1

- Multiplexed Parameter Port

- Special AS-i Safety Mode

- Floating AS-i Transmitter and Receiver for high symmetrical high power applications

- On chip electronic inductor with current drive capability of 55mA

- Configurable LED outputs supporting all status indication modes defined by AS-i Complete Specification V3.0

- Several data preprocessing functions, including configurable data input filters and bit selective data inverting

- Improved additional addressing channel for easy module setup

- IR and CMOS input mode

- Activation by magic sequence

- Support of 8 / 16 MHz crystals by automatic frequency detection

- Clock Watchdog for high System Security

- Pin and function compatible to A<sup>2</sup>SI

## Description

ASI4U is a monolithic CMOS integrated circuit certified for AS-i (Actuator Sensor Interface) networks. AS-i networks are used for industrial automation.

AS-i is designed for easy and simple interconnection of binary sensors and actuators. It uses a two-wire unshielded cable to transport power and information.

ASI4U is a direct successor of the A<sup>2</sup>SI IC and can replace the A<sup>2</sup>SI.

AS-i Safety applications can use the special AS-i Safety Mode if fault reaction time is a concern.

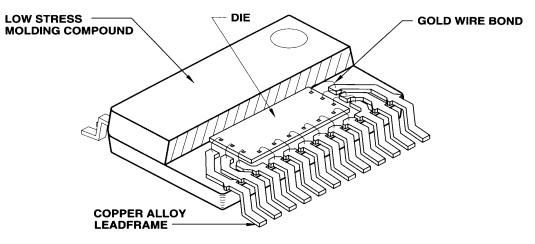

The device is available in SSOP28 package.

## **Application Support**

Configuration of the chip is handled through programming of the on-chip E<sup>2</sup>PROM.

ZMD provides a special

AS-Interface Programmer Tool (Ordering Code: ZMD ASI-Programmer)

to ease product evaluation and selection of different operation modes.

Further application support is available through the e-mail hotline <u>asi@zmd.de</u>

Copyright © 2006, ZMD AG, Rev. 1.5

All rights reserved. The material contained herein may not be reproduced, adapted, merged, translated, stored, or used without the prior written consent of the copyright owner. The Information furnished in this publication is preliminary and subject to changes without notice.

## Table of Contents

| T | able                     | <b>)</b> 0 | f Contents                                                              | Page     |

|---|--------------------------|------------|-------------------------------------------------------------------------|----------|

| 0 | RE/                      | ۹D T       | HIS FIRST                                                               | 4        |

|   | 0.1                      | IMP        | ORTANT NOTICE                                                           | 4        |

|   | 0.2                      |            | -SAFETY APPLICATIONS                                                    |          |

|   | 0.3                      | Ref        | PAIR OF ASI-SAFETY MODULES                                              | 4        |

| 1 | GEI                      | NER        | AL DEVICE SPECIFICATION                                                 | 5        |

|   | 1.1                      | ARS        | OLUTE MAXIMUM RATINGS (NON OPERATING)                                   | 5        |

|   | 1.2                      |            | ERATING CONDITIONS                                                      |          |

|   | 1.3                      |            | ALITY STANDARDS                                                         |          |

|   | 1.4                      | Pac        | KAGE PIN ASSIGNMENT                                                     | 7        |

| 2 | BAS                      | SIC F      | FUNCTIONAL DESCRIPTION                                                  | 9        |

|   | 2.1                      | Fun        | ICTIONAL BLOCK DIAGRAM                                                  | 9        |

|   | 2.2                      | GEN        | IERAL OPERATIONAL MODES                                                 | 11       |

|   | 2.3                      | SLA        | ve Mode                                                                 |          |

|   | 2.3.                     |            | AS-i communication channel                                              |          |

|   | 2.3.                     |            | IRD communication channel                                               |          |

|   | 2.3.                     |            | Parameter Port Pins                                                     |          |

|   | 2.3.                     |            | Data Port Pins                                                          |          |

|   | 2.3.                     | -          | Data Input Inversion                                                    |          |

|   | 2.3.                     |            | Data Input Filtering                                                    |          |

|   | 2.3.<br>2.3.             |            | Fixed Data Output Driving<br>Synchronous Data I/O Mode                  |          |

|   | 2.3.                     |            | 4 Input / 4 Output processing in Extended Address Mode                  | 13<br>13 |

|   | 2.3.                     |            | AS-i Safety Mode                                                        |          |

|   | 2.3.                     |            | Enhanced LED Status Indication                                          |          |

|   | 2.3.                     |            | Communication Monitor/Watchdog                                          |          |

|   | 2.3.                     |            | Write protection of ID_Code_Extension_1                                 |          |

|   | 2.3.                     | 14         | Summary of Master Calls                                                 |          |

|   | 2.4                      |            | Ster Mode                                                               |          |

|   | 2.5                      | Ε²Ρ        | ROM                                                                     | 18       |

| 3 | DET                      | AIL        | ED FUNCTIONAL DESCRIPTION                                               | 21       |

|   | 3.1                      |            | I RECEIVER                                                              |          |

|   | 3.2                      |            | I TRANSMITTER                                                           |          |

|   | 3.3                      |            | RESSING CHANNEL INPUT IRD                                               |          |

|   | 3.3.                     |            | General Slave Mode Functionality                                        |          |

|   | 3.3.                     |            | AC Current Input Mode                                                   |          |

|   | 3.3.                     |            | CMOS Input Mode                                                         |          |

|   | 3.3. <sup>,</sup><br>3.4 | -          | Master-, Repeater- and Monitor-Mode<br>ITAL INPUTS - DC CHARACTERISTICS |          |

|   | 3.4                      |            | ITAL INPUTS - DC CHARACTERISTICS                                        | -        |

|   | 3.6                      |            | AMETER PORT AND PST PIN                                                 |          |

|   | 3.6.                     |            | Slave Mode                                                              |          |

|   | 3.6.                     | -          | Parameter Multiplex Mode                                                |          |

|   | 3.6.                     | 3          | Special function of P0, P1 and P2                                       |          |

|   | 3.6.                     |            | Master-, Repeater-, Monitor Mode                                        |          |

|   | 3.7                      | Dat        | A PORT AND DSR PIN                                                      | 29       |

|   | 3.7.                     | •          | Slave Mode                                                              |          |

|   | 3.7.                     |            | Input Data Pre-Processing                                               |          |

|   | 3.7.                     | -          | Fixed Output Data Driving                                               |          |

|   | 3.7.                     |            | Synchronous Data I/O Mode                                               |          |

|   | 3.7.                     |            | Support of 4I/4O processing in Extended Address Mode, Profile 7.A.x.E.  |          |

|   | 3.7.<br>3.7.             | -          | Safety Mode Operation                                                   |          |

|   | 3.7.<br>3.7.             |            | Master-, Repeater-, Monitor Mode<br>Special function of DSR             |          |

|   | 5.7.                     | 0          |                                                                         |          |

Copyright © 2006, ZMD AG, Rev.1.5 All rights reserved. The material contained herein may not be reproduced, adapted, merged, translated, stored, or used without the prior written consent of the copyright owner. The Information furnished in this publication is preliminary and subject to changes without notice.

| 3.8 F  | AULT INDICATION INPUT PIN FID                                 |    |

|--------|---------------------------------------------------------------|----|

| 3.8.1  | Slave Mode                                                    |    |

| 3.8.2  | Master- and Monitor Mode                                      |    |

| 3.9 L  | .ED OUTPUTS                                                   | 40 |

| 3.9.1  | Slave Mode                                                    |    |

| 3.9.2  | Communication via Addressing Channel                          |    |

| 3.9.3  | Master-, Repeater-, Monitor Mode                              |    |

| 3.10   | OSCILLATOR PINS OSC1, OSC2                                    | 41 |

| 3.11   | IC RESET                                                      | 42 |

| 3.11.  | 1 Power On Reset                                              |    |

| 3.11.  | 2 Logic controlled Reset                                      | 43 |

| 3.11.  | 3 External Reset                                              | 43 |

| 3.12   | UART                                                          | 44 |

| 3.12.  | 1 AS- i input channel                                         | 44 |

| 3.12.  | 2 Addressing Channel                                          |    |

| 3.13   | MAIN STATE MACHINE                                            | 47 |

| 3.14   | COMMUNICATION MONITOR/WATCHDOG                                | 47 |

| 3.15   | TOGGLE WATCHDOG FOR 4I/4O PROCESSING IN EXTENDED ADDRESS MODE | 47 |

| 3.16   | WRITE PROTECTION OF ID_CODE_EXTENSION_1                       | 47 |

| 3.17   | Power Supply                                                  |    |

| 3.17.  | 1 Voltage Output Pins UOUT and U5R                            | 49 |

| 3.17.  | 2 Input Impedance (AS-i bus load)                             | 50 |

| 3.18   | THERMAL AND OVERLOAD PROTECTION                               | 50 |

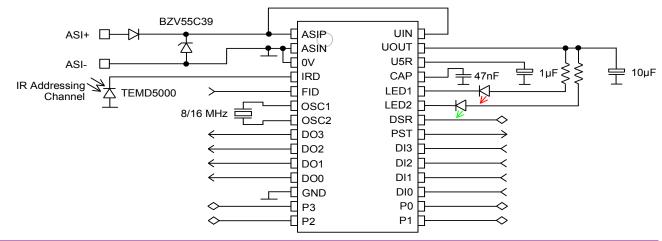

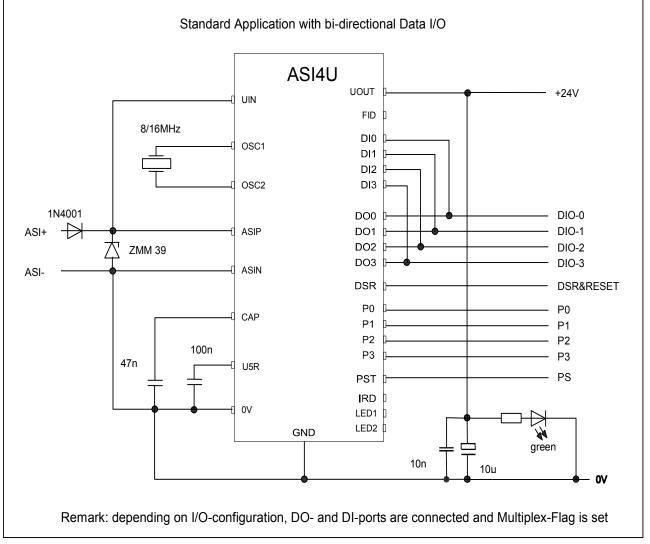

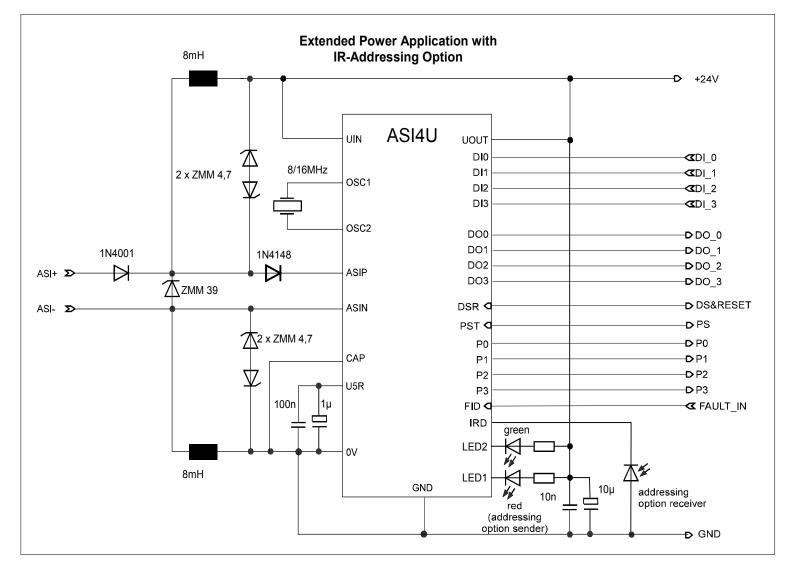

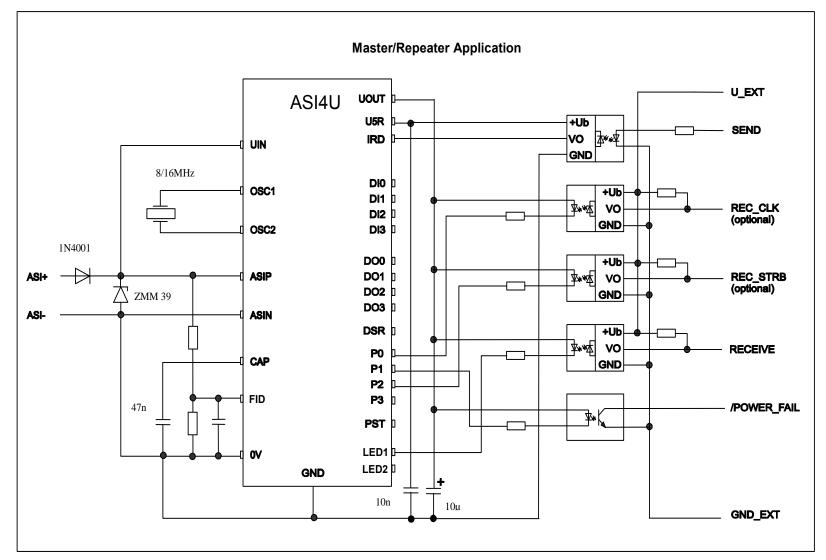

| 4 APPI | LICATION CIRCUITS                                             | 51 |

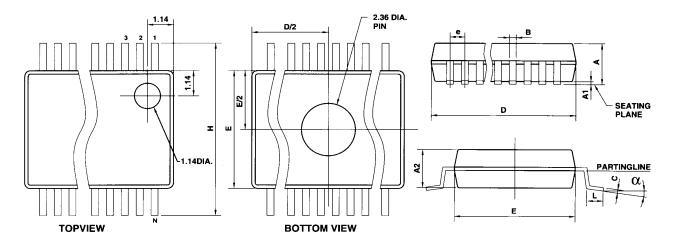

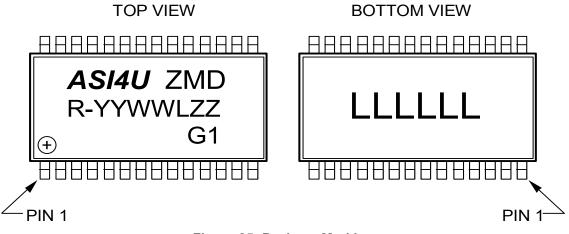

| 5 PACI | KAGE OUTLINE                                                  | 54 |

| 6 PACI | KAGE MARKING                                                  | 55 |

| 7 ORD  | ERING INFORMATION                                             | 55 |

| 8 RELA | ATED DOCUMENTS                                                | 56 |

| 9 RELA | ATED PRODUCTS                                                 | 56 |

| 10 CC  | NTACT INFORMATION                                             | 56 |

| 10.1   | ZMD SALES                                                     | 56 |

| 10.1   | ZMD SALES                                                     |    |

| 10.2   | AS-INTERNATIONAL ASSOCIATION                                  |    |

| 10.3   | ZMD DISTRIBUTION PARTNERS                                     |    |

| 10.4   |                                                               |    |

Copyright © 2006, ZMD AG, Rev.1.6 All rights reserved. The material contained herein may not be reproduced, adapted, merged, translated, stored, or used without the prior written consent of the copyright owner. The Information furnished in this publication is preliminary and subject to changes without notice.

## 0 Read this First

## 0.1 Important Notice

Products sold by ZMD are covered exclusively by the warranty, patent indemnification and other provisions appearing in ZMD standard "Terms of Sale". ZMD makes no warranty (express, statutory, implied and/or by description), including without limitation any warranties of merchantability and/or fitness for a particular purpose, regarding the information set forth in the Materials pertaining to ZMD products, or regarding the freedom of any products described in the Materials from patent and/or other infringement. ZMD reserves the right to discontinue production and change specifications and prices of its products at any time and without notice. ZMD products are intended for use in commercial applications. Applications requiring extended temperature range, unusual environmental requirements, or high reliability applications, such as military, medical life-support or life-sustaining equipment, are specifically not recommended without additional mutually agreed upon processing by ZMD for such applications.

ZMD reserves the right to change the detail specifications as may be required to permit improvements in the design of its products.

## 0.2 ASI-Safety Applications

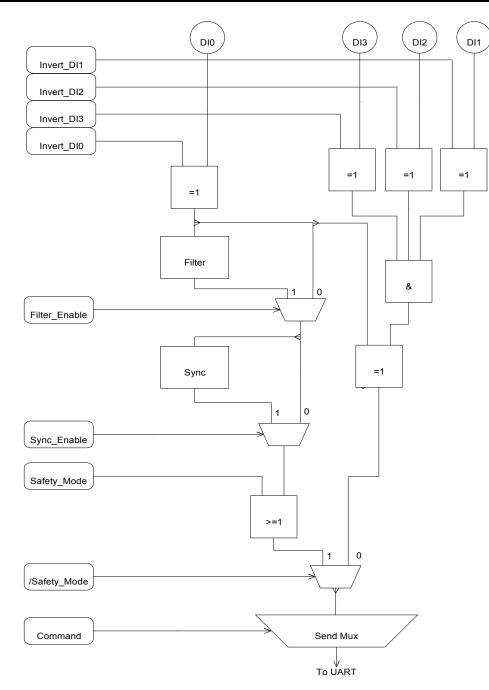

The ASI4U is designed to allow replacement of A<sup>2</sup>SI ICs in existing board layouts and applications. However, since the ASI4U provides additional data preprocessing functions at the data input channel, the fault reaction time of an AS-i Safety module could increase by 40ms if some of the new features become activated by intention, by accident or hardware fault.

ZMD strongly recommends the use of the new ASI4U Safety-Mode, if the ASI4U shall replace the A<sup>2</sup>SI in existing ASI-Safety designs. Only then, the same fault reaction times as with the A<sup>2</sup>SI are guaranteed. For compatibility with the modified data input routing in Safety Mode, the user has to adapt the safety code table stored in the external micro controller. Only such Safety Code Sequences that contain the value **1110** are permitted.

If the IC is operated in Safety Mode, the user must pay special attention that the *Synchronous Data I/O Mode* as well as the *Data Input Filters* remain disabled by appropriate E<sup>2</sup>PROM configuration.

Application of the ASI4U in Standard Mode (no Safety Mode enabled) for AS-i Safety products is basically possible, if an additional Fault Reaction Time of 40ms is taken into account.

The user shall also obey the additional security advice regarding "Production and Repair of AS-i Safety Slaves" that is available as an additional document form the ZMD web page <a href="http://www.zmd.biz">www.zmd.biz</a>.

## 0.3 Repair of ASI-Safety Modules

If an A<sup>2</sup>SI based ASI-Safety Module shall be repaired, it is <u>explicitly prohibited</u> to replace the A<sup>2</sup>SI IC with the newer ASI4U IC. This is to exclude safety relevant deviations of module properties that can result from the different data input paths an the above mentioned possible increase in Fault Reaction Time.

The user shall also obey the additional security advice regarding "Production and Repair of AS-i Safety Slaves" that is available as an additional document form the ZMD web page <u>www.zmd.biz</u>.

All rights reserved. The material contained herein may not be reproduced, adapted, merged, translated, stored, or used without the prior written consent of the copyright owner. The Information furnished in this publication is preliminary and subject to changes without notice.

#### 1 **General Device Specification**

#### 1.1 **Absolute Maximum Ratings (Non Operating)**

## **Table 1: Absolute Maximum Ratings**

| Symbol                 | Parameter                                                                         | Min  | Max                     | Unit | Note |

|------------------------|-----------------------------------------------------------------------------------|------|-------------------------|------|------|

| $V_{0V}, V_{GND}$      | Voltage reference                                                                 | 0    | 0                       | V    |      |

| V <sub>ASIP-ASIN</sub> | Voltage difference between ASIP and ASIN (V <sub>ASIP</sub> - V <sub>ASIN</sub> ) | -0.3 | 40                      | V    | 1    |

| $V_{ASIP-ASIN_P}$      | Pulse voltage between ASIP and ASIN ( $V_{ASIP}$ - $V_{ASIN}$ )                   | -0.3 | 50                      | V    | 2    |

| V <sub>ASIP</sub>      | Pulse voltage between ASIP and 0V ( $V_{ASIP} - V_{0V}$ )                         | -0.3 | 50                      | V    | 2, 3 |

| V <sub>ASIN</sub>      | Voltage between ASIN and 0V ( $V_{ASIN} - V_{0V}$ )                               | -6.0 | 6.0                     | V    | 3    |

| V <sub>UIN</sub>       | Power supply input voltage                                                        | -0.3 | 40                      | V    |      |

| $V_{\text{UIN}_{P}}$   | Pulse voltage at power supply input                                               | -0.3 | 50                      | V    | 2    |

| V <sub>inputs1</sub>   | Voltage at pins DI3 DI0, DO3 DO0, P3 P0, DSR, PST, LED1, LED2, FID, IRD, UOUT     | -0.3 | V <sub>UOUT</sub> + 0.3 | V    |      |

| V <sub>inputs2</sub>   | Voltage at pins OSC1, OSC2, CAP, U5R                                              | -0.3 | 7                       | V    |      |

| l <sub>in</sub>        | Input current into any pin except supply pins                                     | -50  | 50                      | mA   | 4    |

| Н                      | Humidity non-condensing                                                           |      |                         |      | 5    |

| V <sub>HBM1</sub>      | Electrostatic discharge – Human Body Model (HBM1)                                 | 3500 |                         | V    | 6    |

| V <sub>HBM2</sub>      | Electrostatic discharge – Human Body Model (HBM2)                                 | 2000 |                         | V    | 7    |

| V <sub>EDM</sub>       | Electrostatic discharge – Equipment Discharge Model (EDM)                         | 400  |                         | V    | 8    |

| $\theta_{\text{STG}}$  | Storage temperature                                                               | -55  | 125                     | °C   |      |

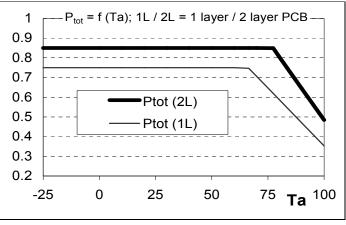

| P <sub>tot</sub>       | Total power dissipation                                                           |      | 0.85                    | W    | 9    |

| R <sub>thj</sub>       | Thermal resistance of SSOP 28 package                                             | 40   | 80                      | K/W  | 10   |

- 1 reverse polarity protection has to be performed externally

- 2 pulse with  $\leq$  50µs, repetition rate  $\leq$  0.5 Hz

- 3  $V_{ASIP\text{-}ASIN}$  and  $~V_{ASIP\text{-}ASIN\_P}$  must not be violated

- 4 Latch-up resistance, reference pin is 0V

- 5 Level 4 according to JEDEC-020A is guaranteed

- 6 HBM1: C = 100pF charged to  $V_{HBM1}$  with resistor R =  $1.5k\Omega$  in series, valid for ASIP-ASIN only.

- 7 HBM2: C = 100pF charged to  $V_{HBM2}$  with resistor R =  $1.5k\Omega$  in series, valid for all pins except ASIP-ASIN

- 8 EDM: C = 200pF charged to  $V_{EDM}$  with no resistor in series, valid for ASIP-ASIN only

at max. operating temperature, the allowed total

power dissipation depends on additional thermal resistance from package to ambient and on the operation ambient temperature as shown in Figure 1.

10 Single layer board,  $P_{tot}$  = 0.5W; air velocity = 0m/s  $\Rightarrow$  max. value; air velocity = 2.5m/s  $\Rightarrow$  min. value

Copyright © 2006, ZMD AG, Rev.1.6

9

All rights reserved. The material contained herein may not be reproduced, adapted, merged, translated, stored, or used without the prior written consent of the copyright owner. The Information furnished in this publication is preliminary and subject to changes without notice.

## 1.2 **Operating Conditions**

## **Table 2: Operating Conditions**

| Symbol                             | Parameter                                    | Min | Max. | Unit | Note |

|------------------------------------|----------------------------------------------|-----|------|------|------|

| V <sub>UIN</sub>                   | Positive supply voltage for IC operation     | 16  | 33.1 | V    | 1    |

| V <sub>0V</sub> , V <sub>GND</sub> | Negative supply voltage                      | 0   | 0    | V    |      |

| V <sub>ASIP</sub>                  | DC voltage at ASIP relating to $V_{0V}$      | 16  | 33.1 | V    | 2    |

| V <sub>ASIN</sub>                  | DC voltage at ASIN relating to $V_{0V}$      | -4  | 4    | V    | 2    |

| I <sub>UIN</sub>                   | Operating current at V <sub>UIN</sub> = 30V  |     | 6    | mA   | 3    |

| I <sub>CL1</sub>                   | Max. output sink current at pins DO3DO0, DSR |     | 10   | mA   |      |

| I <sub>CL2</sub>                   | Max. output sink current at pins P0P3, PST   |     | 10   | mA   |      |

| $\theta_{amb}$                     | Ambient temperature range, operating range   | -25 | 85   | °C   |      |

<sup>1</sup> DC-Parameter:

$V_{UINmin} = V_{UOUTmin} + V_{DROPmax}$

V<sub>UINmax</sub> = V<sub>UOUTmax</sub> + V<sub>DROPmin</sub>

Below  $V_{UINmin}$  the power supply block may not be able to provide the specified output currents at UOUT and U5R.

<sup>2</sup> Outside of these limits the send current shape and send current amplitude cannot be guaranteed.

$^{3}$  f<sub>c</sub> = 8.000 MHz, no load at any pin, transmitter turned off, digital state machine is in idle state

## Table 3: Crystal Frequency

| Symbol         | Parameter         | Nom.         | Unit | Note |

|----------------|-------------------|--------------|------|------|

| f <sub>c</sub> | Crystal frequency | 8.000/16.000 | MHz  | 4    |

<sup>4</sup> The IC automatically detects whether the crystal frequency is 8.000MHz or 16.000MHz and controls the internal clock circuit accordingly. The frequency detection is locked as soon as one AS-i telegram was correctly received **at any input channel**. It can be reset by Power On Reset only.

<u>Note:</u> In Slave Mode the locking occurs if a Master Call was received. In Master-/ Repeater-/Monitor Mode a Master Call or a Slave Response that was received on any input channel, triggers the frequency locking.

The ASI4U supports an integrated clock watchdog. If no crystal or clock oscillation is recognized for 150µs the IC generates a RESET event until clock oscillation is available.

More detailed oscillator pin definitions can be found in chapter 3.10 on page 41.

## 1.3 Quality Standards

The quality of the IC will be ensured according to the ZMD quality standards. Functional device parameters are valid for device operating conditions specified in chapter 1.2. Production device tests are performed within the recommended ranges of  $V_{ASIP}$  -  $V_{ASIN}$ ,  $V_{IN}$  -  $V_{0V}$ ,  $\theta$ amb = + 25°C (+ 85°C and - 25°C on sample base only) unless otherwise stated.

All rights reserved. The material contained herein may not be reproduced, adapted, merged, translated, stored, or used without the prior written consent of the copyright owner. The Information furnished in this publication is preliminary and subject to changes without notice.

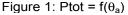

## 1.4 Package Pin Assignment

## Table 4: ASI4U Pin List

| Package<br>pin number | Name | Direction | Туре               | Description                                                                                                            |

|-----------------------|------|-----------|--------------------|------------------------------------------------------------------------------------------------------------------------|

| 1                     | ASIP | IN        | Analog             | AS-i Transmitter/Receiver input, to be connected to ASI+ lead of AS-i cable, via reverse polarity protection diode     |

| 2                     | ASIN | OUT       | Analog             | AS-i Transmitter/Receiver output, to be connected to ASI- lead of AS-i cable                                           |

| 3                     | 0V   |           | SUPPLY             | IC Ground<br>Common ground for all IC ports except ASIP/ASIN,<br>To be connected to ASIN if no external coils are used |

| 4                     | IRD  | IN        | Analog / CMOS (5V) | Addressing Channel input                                                                                               |

| 5                     | FID  | IN        | Pull-up            | Periphery Fault input                                                                                                  |

| 6                     | OSC2 | OUT       | Analog (5V)        | Crystal oscillator                                                                                                     |

| 7                     | OSC1 | IN        | Analog / CMOS (5V) | Crystal oscillator / External clock input                                                                              |

| 8                     | DO3  | OUT       | Open Drain         | Data port output D3                                                                                                    |

| 9                     | DO2  | OUT       | Open Drain         | Data port output D2                                                                                                    |

| 10                    | DO1  | OUT       | Open Drain         | Data port output D1                                                                                                    |

| 11                    | DO0  | OUT       | Open Drain         | Data port output D0                                                                                                    |

| 12                    | GND  |           | SUPPLY             | Digital I/O ground, to be connected with 0V                                                                            |

| 13                    | P3   | I/O       | Pull-up/Open Drain | Parameter port P3                                                                                                      |

| 14                    | P2   | I/O       | Pull-up/Open Drain | Parameter port P2 /<br>Receive Strobe output in Master Mode                                                            |

| 15                    | P1   | I/O       | Pull-up/Open Drain | Parameter port P1 /<br>Power Fail output in Master Mode                                                                |

| 16                    | P0   | I/O       | Pull-up/Open Drain | Parameter port P0 /<br>Data Clock output in Master Mode                                                                |

| 17                    | DI0  | IN        | Pull-up            | Data port input D0                                                                                                     |

| 18                    | DI1  | IN        | Pull-up            | Data port input D1                                                                                                     |

| 19                    | DI2  | IN        | Pull-up            | Data port input D2                                                                                                     |

| 20                    | DI3  | IN        | Pull-up            | Data port input D3                                                                                                     |

| 21                    | PST  | I/O       | Pull-up/Open Drain | Parameter Strobe output<br>(input function used for IC test purposes only)                                             |

| 22                    | DSR  | I/O       | Pull-up/Open Drain | Data Strobe output / Reset input                                                                                       |

Copyright © 2006, ZMD AG, Rev.1.6 All rights reserved. The material contained herein may not be reproduced, adapted, merged, translated, stored, or used without the prior written consent of the copyright owner. The Information furnished in this publication is preliminary and subject to changes without notice.

| Package<br>pin number | Name | Direction | Туре               | Description                                                                                                                        |  |  |  |

|-----------------------|------|-----------|--------------------|------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 23                    | LED2 | OUT       | Open Drain         | LED output "Enhanced Diagnosis", to be activated by<br><i>LED2_Active</i> bit in the Firmware region of the<br>E <sup>2</sup> PROM |  |  |  |

| 24                    | LED1 | I/O       | Pull-up/Open Drain | LED output "AS-i-Diagnosis" /<br>Addressing channel output<br>(input function used for IC test purposes only)                      |  |  |  |

| 25                    | CAP  | I/O       | Analog             | Filter control (Electronic Inductor)                                                                                               |  |  |  |

| 26                    | U5R  | OUT       | Analog             | Regulated internal/external 5V supply                                                                                              |  |  |  |

| 27                    | UOUT | OUT       | Analog             | Decoupled Actuator/Sensor supply                                                                                                   |  |  |  |

| 28                    | UIN  |           | SUPPLY             | Power supply input                                                                                                                 |  |  |  |

All open drain outputs are NMOS based. Pull-up properties at input stages are achieved by current sources referring to U5R.

Figure 2: ASI4U Package Pin Assignment

All rights reserved. The material contained herein may not be reproduced, adapted, merged, translated, stored, or used without the prior written consent of the copyright owner. The Information furnished in this publication is preliminary and subject to changes without notice.

## 2 Basic Functional Description

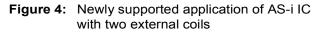

## 2.1 Functional Block Diagram

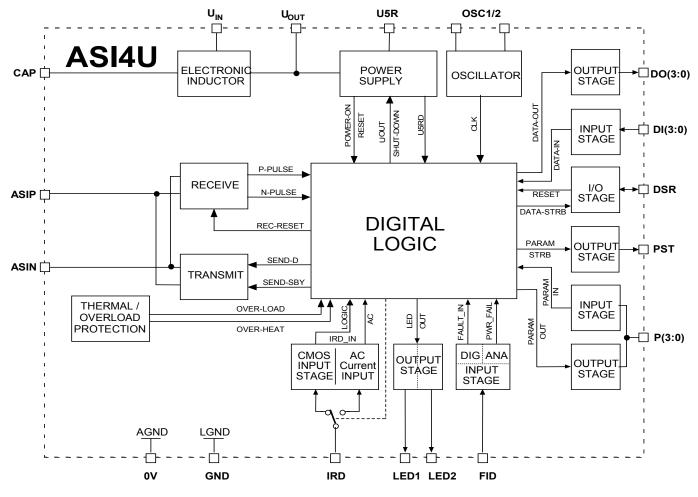

## Figure 3: Functional Block Diagram

Following device functions are associated with the different blocks of the IC:

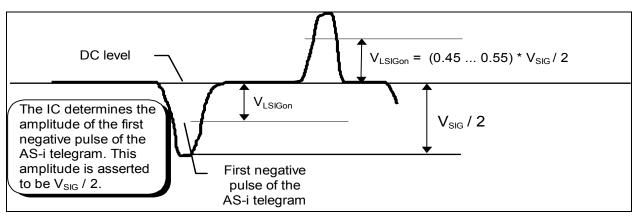

- **RECEIVE** The receive block converts the analog telegram waveform from the AS-i bus to a digital pulse coded signal that can be processed further by a digital UART circuit. The RECEIVE block is directly connected to the AS-i line pins ASIP and ASIN. It converts the differential AS-i telegram to a single ended signal and removes the DC offset by high pass filtering. To adapt quickly on changing signal amplitudes in telegrams from different network users, the amplitude of the first telegram pulse is measured by a 3 bit flash ADC and the threshold of a positive and a negative comparator is set accordingly to about 50% of the measured level. The comparators generate the P-Pulse and N-Pulse signals.

- **TRANSMIT** The transmit block transforms a digital response signal to a correctly shaped send current signal which is applied to the AS-i bus. Due to the inductive network behavior of the network the changing send current induces voltage pulses on the network line that overlay the DC operating voltage. The voltage pulses shall have sin<sup>2</sup>-wave shapes. Hence, the send current shape must follow the integral of the sin<sup>2</sup>-wave function.

All rights reserved. The material contained herein may not be reproduced, adapted, merged, translated, stored, or used without the prior written consent of the copyright owner. The Information furnished in this publication is preliminary and subject to changes without notice.

**DIGITAL LOGIC** The digital logic block contains UART, Main State Machine, E<sup>2</sup>PROM memory and other control logic. E<sup>2</sup>PROM write access and other I/O operations of the Main State Machine are supported in Slave Mode only (see description of general IC operational modes below). In Master Mode the IC is basically equivalent to a physical layer transceiver.

If Slave Mode is activated, the UART demodulates the received telegrams, verifies telegram syntax and timing and controls a register interface to the Main State Machine. After reception of a correct telegram, the UART generates appropriate Receive Strobe signals, that tell the Main State Machine to start further processing. The Main State Machine decodes the telegram information and starts respective I/O processes or E<sup>2</sup>PROM access. A second register interface is used to send data back to the UART for construction of a telegram response. The UART modulates the response data into a Manchester-II-coded bit stream that is used to control the TRANSMIT unit.

**ELECTRONIC INDUCTOR** The electronic inductor is basically a gyrator circuit. It provides an inductive behavior between the IC pins UIN and UOUT while the inductance is controlled by the capacitor on pin CAP. The inductor shall decouple the power regulator of the IC as well as the external load circuit from the AS-i bus and hence prevent cross talk or switching noise from disturbing the telegram communication on the bus.

The AS-i Complete Specification describes the input impedance behavior of a slave module by an equivalent circuit that consists of R, L and C in parallel. For example, a slave module in Extended Address Mode shall have R > 13.5 kOhm, L > 13.5 mH and C < 50pF. The electronic inductor of the ASI4U delivers values that are well within the required ranges for output currents up to 55mA. More detailed parameters can be found in chapter 3.17.2.

The electronic inductor requires an external capacitor of 10µF at pin UOUT for stability.

- **POWER** The power supply block consists of a bandgap referenced 5V-regulator as well as other reverence voltage and bias current generators for internal use. The 5V regulator requires an external capacitor at pin U5R of at least 1µF for stability. It can source up to 4mA for external use, however the power dissipation and the resulting device heating become a major concern, if too much current is drawn from the regulator.

- **OSCILLATOR** The oscillator supports direct connection of 8.000 MHz or 16.000 MHz crystals with a dedicated load capacity of 12pF and parasitic pin capacities of up to 8pF. The IC automatically detects the oscillation frequency of the connected crystal and controls the internal clock generator circuit accordingly.

After power-on reset the IC is set to 16.000 MHz operation by default. After about 200µs it will either switch to 8.000 MHz operation or remain in the 16.000 MHz mode. The frequency detection is active until the first AS-i telegram was successfully received in order to make sure the IC found the correct clock frequency setting. The detection result is locked thereafter to increase resistance against burst or other interferences.

The oscillator unit also contains a clock watch dog circuit that can generate an unconditioned IC reset if there was no clock oscillation for more than about 20µs. This is to prevent the IC from unpredicted behavior if no clock signal is available anymore.

THERMAL / OVERLOAD PROTECTION

The IC is self protected against thermal overheating and short circuiting of pin UOUT towards IC ground.

If the silicon die temperature rises above around 140°C for more than 2 seconds, the IC detects thermal overheating, switches off the electronic inductor, performs an IC reset and sets all analog blocks to power down mode. The 5V-regulator is of course also turned off in this state, however, there will still remain a voltage of about 3 ... 3.5V available at U5R that is derived from the internal start circuitry. The overheat protection state can only be left by power-cycling the AS-i voltage.

Shortcutting pin UOUT towards IC ground leads to the same IC behavior as thermal overheating.

# IRD CMOS /<br/>AC CURRENTThe IRD pin is input for the additional addressing channel in Slave Mode (see description of<br/>General IC Operational Modes below) or direct AS-i transmitter input in Master Mode. In<br/>Slave Mode it can be operated either in CMOS Mode or AC-current input mode. The later is<br/>provided for direct connection of a photo diode. More detailed information can be found in

Copyright © 2006, ZMD AG, Rev.1.6

All rights reserved. The material contained herein may not be reproduced, adapted, merged, translated, stored, or used without the prior written consent of the copyright owner. The Information furnished in this publication is preliminary and subject to changes without notice.

chapter 3.3 Addressing Channel Input IRD.

FID DIGITAL /<br/>ANALOGPin FID can be set to digital CMOS mode or analog voltage input mode. In Slave Mode it is<br/>set to CMOS operation, in Master Mode it works in analog mode and acts as input for the<br/>power fail comparator.

**INPUT STAGE** All digital inputs, except of the oscillator pins, have high voltage capabilities and partly Schmitt-Trigger and Pull-Up features. For more details see chapter 3.4 Digital Inputs - DC Characteristics.

## **OUTPUT**All digital output stages, except of the oscillator pins, have high voltage capabilities and are**STAGE**implemented as NMOS open drain buffers. Each pin can sink up to 10mA of current.

## 2.2 General Operational Modes

The ASI4U provides two main and two additional sub operational modes. Main operation modes divide in Slave Mode and Master Mode. Sub operation modes divide in Repeater Mode and Monitor Mode. The later were derived from Master Mode in providing different output signals at the Parameter Port.

A definition of which operational mode becomes active is made by programming the flags *Master\_Mode* and *Repeater\_Mode* in the *Firmware Area* of the E<sup>2</sup>PROM (see also Table 7 on page 18). The E<sup>2</sup>PROM is read out at every initialization of the IC. Online mode switching is not provided. The following configurations apply:

| Selected Operational Mode | Master Mode Flag | Repeater Mode Flag |

|---------------------------|------------------|--------------------|

| Slave Mode                | 0                | 0                  |

| Master Mode               | 1                | 0                  |

| Repeater Mode             | 1                | 1                  |

| Monitor Mode              | 0                | 1                  |

#### Table 5: Assignment of operational modes

In Slave Mode the ASI4U operates as fully featured AS-i Slave IC according to AS-i Complete Specification v3.0.

In Master Mode the ASI4U translates a digital output signal from the master control logic (etc. PLC, µP, ...) to a correctly shaped, analog AS-i pulse sequence and vice versa. Every AS-i telegram received is checked for consistency with the AS-i communication protocol specifications and if no errors were found, an appropriate receive strobe signal is generated.

Master Mode and Monitor Mode differ in the kind of signaled telegrams. In Master Mode a single Receive Strobe signal is provided validating every correctly received Slave Response while in Monitor Mode two different Receive Strobe signals are available displaying every correctly received Master and Slave telegram separately. The Monitor Mode is intended for use in intelligent slaves and bus monitors that provide own telegram decoding mechanisms but do not check for correct telegram timing or syntax.

The Repeater Mode is specifically provided for AS-i bus repeater applications.

## 2.3 Slave Mode

The Slave Mode is probably the most complex operational mode of the IC. The ASI4U does not only support all mandatory AS-i Slave functions but also a variety of additional features that shall make AS-i Slave module design very easy and flexible.

## 2.3.1 AS-i communication channel

In slave mode the ASI4U can work on two different communication channels, the AS-i channel and the IRD channel. The AS-i channel is directly connected to AS-i Bus via the pins ASIP and ASIN. A receiver and a transmitter unit are connected in parallel to the pins that allow fully bi-directional communication through ASIP and ASIN.

All rights reserved. The material contained herein may not be reproduced, adapted, merged, translated, stored, or used without the prior written consent of the copyright owner. The Information furnished in this publication is preliminary and subject to changes without notice.

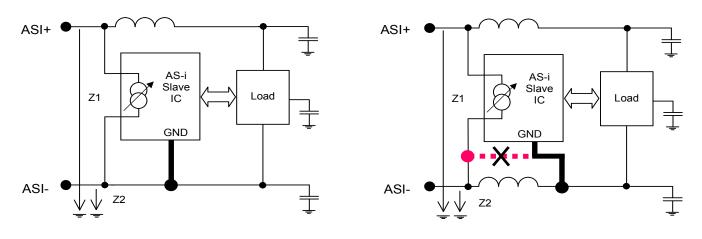

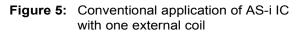

The ASI4U is the first IC that supports floating operation of the AS-i receiver and transmitter (within certain limits) in relation to IC ground. Thus far, the ASIN pin always had to be on the same potential like IC ground, preventing full symmetrical input circuits with external coils. The following figures illustrate the new functionality. If one compares the relation Z1 / Z2, which is a measure for symmetry of the AS-i module input towards machine ground, it becomes obvious that the new circuit is more symmetrical since Z1 and Z2 are more equal than in the conventional solution. Please note, that this is not a complete application circuit.

## 2.3.2 IRD communication channel

Datasheet

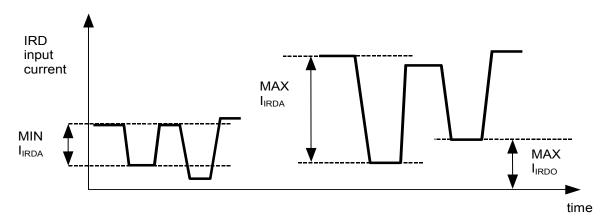

Besides the AS-i communication channel the ASI4U can also operate on a second input channel, the so called IRD Input Channel or Addressing Channel. In this mode the IRD pin is input for an AS-i signal in Manchester-II-coded format. The signal can either be an AC-current signal generated by a photo diode or a 5V-CMOS signal. The IC automatically detects the type of the signal and switches the input path accordingly.

Output pin in IRD communication mode is LED1. It transmits the slave response as inverted Manchester-IIcoded AS-i signal. The red LED, which is normally connected to LED1, can form the response transmitter in an optical communication system or LED1 can be directly connected to some external circuitry.

Activation of the IRD communication channel is achieved by a so called magic sequence, that is sent in advance of the desired communication. The construction of a magic sequence is described in detail in chapter 3.3 *Addressing Channel Input IRD* on page 22. The IRD communication mode is basically left by IC reset, except in one special case that is also described in that chapter.

## 2.3.3 Parameter Port Pins

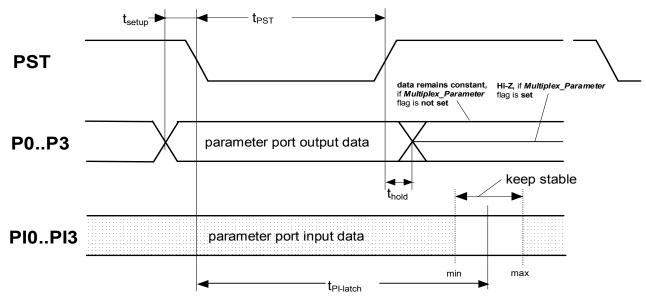

The ASI4U features a 4-bit wide parameter port and a related parameter strobe signal pin PST. There is a defined phase relation between a parameter output event, the parameter input sampling and the activation of the PST signal. Thus it can be used to trigger external logic or a micro controller to process the received parameter data or to provide new input data for the AS-i slave response.

AS-i Complete Specification V3.0 newly defines a bidirectional mode for parameter data. The ASI4U supports this feature, that can be activated by special E<sup>2</sup>PROM setting.

See chapter 3.6 Parameter Port and PST on page 26 for further details.

## 2.3.4 Data Port Pins

An important feature of the ASI4U is the 8-bit wide data port that consists of a 4-bit wide input section and a 4bit wide output section. The input and output sections work independently from each other allowing a maximum of 8 devices (4 input and 4 output devices) to be connected to the ASI4U. For special applications (compatibility), the so called Multiplex Mode can be activated that limits the output activation to a certain time frame. Thus, a 4-bit wide bi-directional data I/O Port can be realized by external connection of the corresponding data input and output pins.

All rights reserved. The material contained herein may not be reproduced, adapted, merged, translated, stored, or used without the prior written consent of the copyright owner. The Information furnished in this publication is preliminary and subject to changes without notice.

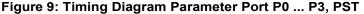

The data port is accompanied by the data strobe signal DSR. There is a defined phase relation between a data output event, the input data sampling and the activation of the DSR signal. Thus, it can be used to trigger external logic or a micro controller to process the received data or to provide new input data for the AS-i slave response. See chapter 3.7 Data Port and DSR on page 29 for further details.

## 2.3.5 Data Input Inversion

By default the logic signal (HIGH / LOW) that is present at the data input pins during the input sampling phase is transferred without modification to the send register, which is interfaced by the UART. By that, the signal becomes directly part of the slave response.

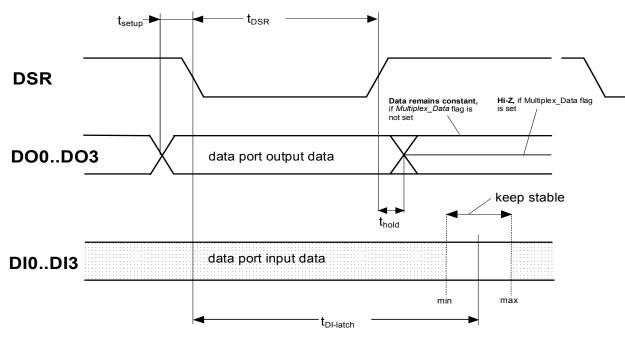

Some applications work with inverted logic levels. To avoid additional external inverters, the input signal can be inverted by the ASI4U before transferring it to the send register. The inversion of the input signals can either be done bit selective or jointly for all data input pins. See chapter 3.7.2 *Input Data Pre-Processing* on page 30.

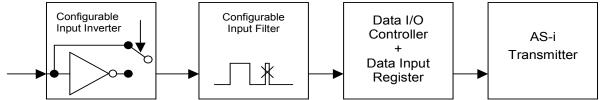

## 2.3.6 Data Input Filtering

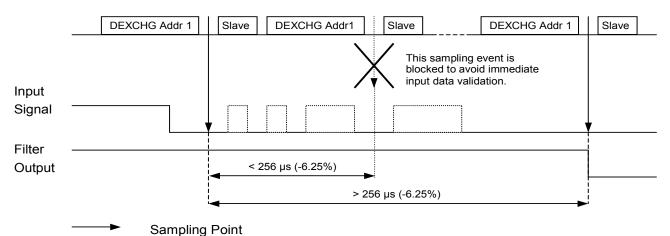

To prevent input signal bouncing from being transferred to the AS-i Master, the data input signals can be digitally filtered. Filter times can be configured in 7 steps from 128µs up to 8.192ms. Additionally there is a so called AS-i Cycle Mode available. If activated, the filter time is determined by the actual AS-i cycle time. For more detailed information refer to chapter 3.7.2 Input Data Pre-Processing on page 30.

The filter function can be enabled bit selective. Activation of the filters is done jointly either by E<sup>2</sup>PROM configuration or by the logic state of parameter port pin P2. See chapter 3.7.2 *Input Data Pre-Processing* on page 30.

## 2.3.7 Fixed Data Output Driving

The fixed data output driving feature is thought to ease board level design for similar products that do not require the full data output port width. The user can select one or more bits from the data output port to be driven by a distinct logic level instead by the data that was sent by the master. The distinct output data is stored in the E<sup>2</sup>PROM and can be set during final module configuration. Thus it is possible to signal the actual IC profile to some external circuitry and to allow reuse of certain board designs for different product applications.

See chapter 3.7.3 Fixed Output Data Driving on page 32 for further details.

## 2.3.8 Synchronous Data I/O Mode

AS-i Complete Specification V3.0 newly defines a synchronous data I/O feature, that allows a number of slaves in the network to switch their outputs at the same time and to have their inputs sampled jointly. This feature is especially useful if more than 4-bit wide data is to be provided synchronously to an application.

The synchronization point was defined to the data exchange event of the slave with the lowest address in the network. This definition relies on the cyclical slave polling with increasing slave addresses per cycle that is one of the basic communication principles of AS-i. The IC always monitors the data communication and detects the change from a higher to a lower slave address. If such a change was recognized, the IC assumes that the slave with the lower address has the lowest address in the network.

There are some special procedures that become active during the start of synchronous I/O mode operation and if more than three consecutive telegrams were sent to the same slave address. This is described in more detail in chapter 3.7.4 Synchronous Data I/O Mode on page 32.

## 2.3.9 4 Input / 4 Output processing in Extended Address Mode

A new feature of AS-i Complete Specification v3.0 is also support of 4-bit wide output data in Extended Address Mode. In Extended Address Mode it was, up to Complete Specification v2.11, only possible to send three data output bits from the master to the slave because telegram bit I3 is used to select between A- and B- slave type for extended slave addressing (up to 62 slaves per network). In normal address mode I3 carries output data for pin D3.

The new definition introduces a multiplexed data transfer, so that all 4-bits of the data output port can be used again. A first AS-i cycle transfers the data for a 2-bit output nibble only, while the second AS-i cycle transfers the data for the contrary 2-bit nibble. Nibble selection is done by the remaining third bit. To ensure continuous alternation of bit information I2 and thus continued data transfer to both nibbles, a special watchdog was implemented that observes the state of I2 bit. The watchdog can be activated or deactivated by E<sup>2</sup>RPOM setting. It provides a watchdog filter time of about 327ms.

All rights reserved. The material contained herein may not be reproduced, adapted, merged, translated, stored, or used without the prior written consent of the copyright owner. The Information furnished in this publication is preliminary and subject to changes without notice.

The multiplexed transfer of course increases the refresh time per output by a factor of two, however, some applications can tolerate this increase for the benefit of less external circuitry and better slave address efficiency. The sampling cycle of the data inputs remains unchanged since the meaning of 13 bit was not changed in the slave response with the definition of the Extended Address Mode.

More detailed information is described in chapter 3.7.5 *Support of 4I/4O processing in Extended Address Mode, Profile 7.A.x.E* on page 34.

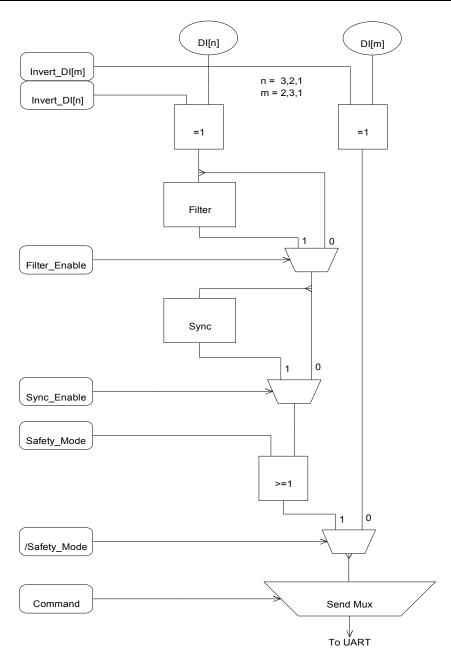

## 2.3.10 AS-i Safety Mode

The enhanced data input features described above require additional registers in the data input path that store the input values for a certain time before they hand them over to the AS-i transmitter. This causes a time delay in the input path that could lead to a delayed "turn off" event, if the registers were activated by intention or by accident in AS-i Safety Applications.

To safely exclude an activation of the enhanced data I/O features in Safety Applications, the IC provides a special Safety Mode that is strongly recommended to be used for AS-i Safety communication purposes. See chapter 3.7.6 Safety Mode Operation on page 34 for further details.

## 2.3.11 Enhanced LED Status Indication

ASI4U newly supports enhanced status indication by two LED outputs. A special mode for direct application of Dual-LEDs and the respective different signaling modes is also implemented. Compared to the A<sup>2</sup>SI, the former U5RD pin was reassigned as LED2 pin. Thus, compatibility to existing A<sup>2</sup>SI board layouts is still guaranteed. However, it will require to keep LED2 pin disabled (default state at delivery) in order to avoid short-circuiting of U5R to ground. More detailed information on the different signaling schemes and their activation can be found in chapter 3.9 LED outputs on page 40.

## 2.3.12 Communication Monitor/Watchdog

Data and Parameter communication are continuously observed by a communication monitor. If neither Data\_Exchange nor Write\_Parameter calls were addressed to and received by the IC within a time frame of about 41ms, a so called *No Data/Parameter Exchange* status is detected and signaled at LED1.

If the respective flags are set in the E<sup>2</sup>PROM the communication monitor can also act as communication watchdog, that initiates a complete IC reset after expiring of the watchdog timer. The watchdog mode can also be activated and deactivated by a signal at parameter port pin P0. For more detailed information see chapter 3.14 *Communication Monitor/Watchdog* on page 47.

## 2.3.13 Write protection of ID\_Code\_Extension\_1

As defined in AS-i Complete Specification v3.0 the ASI4U also supports write protection for ID\_Code\_Extension\_1. The feature allows the activation of new manufacturer protected slave profiles and is enabled by E<sup>2</sup>PROM setting. It is described in more detail in chapter 3.16 Write Protection of ID\_Code\_Extension\_1 on page 47

## 2.3.14 Summary of Master Calls

Table 6 on page 15 and the diagram at the following page show the complete set of Master Calls that are decoded by the ASI4U in Slave Mode. The "Enter Program Mode" call is intended for programming of the IC by the slave manufacturer only. It becomes deactivated as soon as the *Program\_Mode\_Disable* flag is set in the Firmware Area of the E<sup>2</sup>PROM.

## AS-i Complete Specification compliance note:

In order to achieve full compliance to the AS-i Complete Specification, the *Program\_Mode\_Disable* flag must be set by the manufacturer of AS-i slave modules during the final manufacturing and configuration process and before an AS-i slave device is delivered to field application users.

All rights reserved. The material contained herein may not be reproduced, adapted, merged, translated, stored, or used without the prior written consent of the copyright owner. The Information furnished in this publication is preliminary and subject to changes without notice.

ZENTRUM MIKROELEKTRONIK DRESDEN AG "ASI for you" IC

#### Datasheet

| Table 6: ASI4U M | laster Calls and Re | lated Slave Responses |

|------------------|---------------------|-----------------------|

|------------------|---------------------|-----------------------|

|                             |      |    |    |    |    | Mast | er Re | quest |    |            |     |     |     |    |    |    |          | Slave    | Resp     | onse     |    |    |

|-----------------------------|------|----|----|----|----|------|-------|-------|----|------------|-----|-----|-----|----|----|----|----------|----------|----------|----------|----|----|

| Instruction                 | MNE  | ST | CB | A4 | A3 | A2   | A1    | A0    | 14 | 13         | 12  | 11  | 10  | PB | EB | SB | 13       | 12       | 11       | 10       | PB | EB |

| Data Exchange               | DEXG | 0  | 0  | A4 | A3 | A2   | A1    | A0    | 0  | D3<br>~Sel | D2  | D1  | D0  | PB | 1  | 0  | D3<br>E3 | D2<br>E2 | D1<br>E1 | D0<br>E0 | PB | 1  |

| Write Parameter             | WPAR | 0  | 0  | A4 | A3 | A2   | A1    | A0    | 1  | P3<br>∼Sel | P2  | P1  | P0  | PB | 1  | 0  | P3<br>13 | P2<br>12 | P1<br>11 | P0<br>10 | PB | 1  |

| Address Assignment          | ADRA | 0  | 0  | 0  | 0  | 0    | 0     | 0     | A4 | A3         | A2  | A1  | A0  | PB | 1  | 0  | 0        | 1        | 1        | 0        | 0  | 1  |

| Write Extented ID<br>Code_1 | WID1 | 0  | 1  | 0  | 0  | 0    | 0     | 0     | 0  | ID3        | ID2 | ID1 | ID0 | PB | 1  | 0  | 0        | 0        | 0        | 0        | 0  | 1  |

| Delete Address              | DELA | 0  | 1  | A4 | A3 | A2   | A1    | A0    | 0  | 0 Sel      | 0   | 0   | 0   | PB | 1  | 0  | 0        | 0        | 0        | 0        | 0  | 1  |

| Reset Slave                 | RES  | 0  | 1  | A4 | A3 | A2   | A1    | A0    | 1  | 1<br>∼Sel  | 1   | 0   | 0   | PB | 1  | 0  | 0        | 1        | 1        | 0        | 0  | 1  |

| Read IO<br>Configuration    | RDIO | 0  | 1  | A4 | A3 | A2   | A1    | A0    | 1  | 0<br>Sel   | 0   | 0   | 0   | PB | 1  | 0  | 103      | 102      | 101      | 100      | PB | 1  |

| Read ID Code                | RDID | 0  | 1  | A4 | A3 | A2   | A1    | A0    | 1  | 0<br>Sel   | 0   | 0   | 1   | PB | 1  | 0  | ID3      | ID2      | ID1      | ID0      | PB | 1  |

| Read ID Code_1              | RID1 | 0  | 1  | A4 | A3 | A2   | A1    | A0    | 1  | 0<br>Sel   | 0   | 1   | 0   | PB | 1  | 0  | ID3      | ID2      | ID1      | ID0      | PB | 1  |

| Read ID Code_2              | RID2 | 0  | 1  | A4 | A3 | A2   | A1    | A0    | 1  | 0<br>Sel   | 0   | 1   | 1   | PB | 1  | 0  | ID3      | ID2      | ID1      | ID0      | PB | 1  |

| Read Status                 | RDST | 0  | 1  | A4 | A3 | A2   | A1    | A0    | 1  | 1<br>∼Sel  | 1   | 1   | 0   | PB | 1  | 0  | S3       | S2       | S1       | S0       | PB | 1  |

| Broadcast (Reset)           | BR01 | 0  | 1  | 1  | 1  | 1    | 1     | 1     | 1  | 0          | 1   | 0   | 1   | 1  | 1  |    | - no sl  | lave re  | espons   | se       |    |    |

| Enter Program Mode          | PRGM | 0  | 1  | 0  | 0  | 0    | 0     | 0     | 1  | 1          | 1   | 0   | 1   | 1  | 1  |    | - no sl  | lave re  | espon    | se       |    |    |

Note: In Extended Address Mode the "Select Bit" defines whether the A-Slave or B-Slave is being addressed. Depending on the type of master call bit I3 carries the select bit information (Sel = A-Slave) or the inverted select bit information (~Sel = B-Slave).

Copyright © 2006, ZMD AG, Rev.1.6

All rights reserved. The material contained herein may not be reproduced, adapted, merged, translated, stored, or used without the prior written consent of the copyright owner. The Information furnished in this publication is preliminary and subject to changes without notice.

16/57 Datasheet

"ASI for you" IC

|            |          | B-Slave with<br>Profile 0.A<br>(green shaded) |                         | ASI Master<br>Request<br>(black/green) | ASI Slave<br>Response<br>(blue) |                 |              |                            | No Slave<br>Response (blue<br>shaded) |

|------------|----------|-----------------------------------------------|-------------------------|----------------------------------------|---------------------------------|-----------------|--------------|----------------------------|---------------------------------------|

|            |          |                                               |                         |                                        |                                 |                 |              | /                          | X / _/                                |

| ADR != 0   | 12 11 10 | 000                                           | 001                     | 010                                    | 011                             | 100             | 101          | 110                        | 111                                   |

| CB 14 13   | I3=Sel   |                                               | (Slave Address          | != 0) AND (Proga                       | am Mode not act                 | vated)          |              |                            |                                       |

| 000        | Sel=0    | Data                                          | _Exchange /Sel D2 I     | D1 D0                                  |                                 |                 |              |                            |                                       |

| 001        | Sel=1    | Data                                          | _Exchange D3 D2 D       | D1 D0                                  | D3 D2 D1 D0                     |                 |              |                            |                                       |

| 010        | Sel=0    | -                                             | Parameter /Sel P2       |                                        |                                 |                 |              |                            | /                                     |

| 011        | Sel=1    |                                               | e_Parameter P3 P2 I     | P1 P0                                  | P3 P2 P1 P0                     |                 |              |                            |                                       |

| 100        | Sel=0    | Delete_Addr x0                                |                         |                                        |                                 |                 |              |                            |                                       |

| 101        | Sel=1    | T                                             |                         |                                        |                                 |                 |              |                            |                                       |

| 110        | Sel=0    | Rd_IO_Cfg <13:10>                             | Read_ID <i3:i0></i3:i0> | Read_ID_1 <i3:i0></i3:i0>              |                                 | Reset_Slave 0x6 | Broadcast    | Rd_Status <\$3:S0>         |                                       |

| 111        | Sel=1    | Rd_IO_Cfg <13:10>                             | Read_ID <i3:i0></i3:i0> | Read_ID_1 <i3:i0></i3:i0>              | Read_ID_2 <13:10>               | Reset_Slave 0x6 |              | Rd_Status/ <s3:s0></s3:s0> |                                       |

|            |          |                                               |                         |                                        |                                 |                 |              |                            | 1                                     |

| ADR == 0   | 12 11 10 | 000                                           | 001                     | 010                                    | 011                             | 100             | 101          | 1/10                       | 111                                   |

| CB 14 13   |          |                                               | (Slave Address          | == 0) AND (Prog                        | am Mode not act                 | tivated)        |              |                            | 1                                     |

| 000        |          |                                               |                         |                                        |                                 |                 | /            | <b> </b> /                 |                                       |

| 001        |          |                                               |                         | Address_Assignme                       |                                 |                 | /            | <u> </u>                   |                                       |

| 010<br>011 |          |                                               |                         |                                        | 0x6                             |                 | /            | +/                         |                                       |

|            |          |                                               |                         |                                        |                                 |                 |              |                            |                                       |

| 100<br>101 |          |                                               |                         | Write_Var_Ext_Cod                      | 0x0                             |                 | /            | /                          |                                       |

| 101        |          | Rd_IO_Cfg <13:10>                             | Read ID <13:10>         | Read ID 1<13:10>                       | Read ID 2 <13:10>               |                 | Broadcast    |                            |                                       |

| 110        |          |                                               |                         |                                        |                                 | Reset Slave 0x6 | EnterPmode   | Rd Status <s3:s0></s3:s0>  |                                       |

|            |          |                                               |                         |                                        |                                 |                 | EnterFillode |                            |                                       |

|            | 12 11 10 | 000                                           | 001                     | 010                                    | 011                             | 100             | 101          | 110                        | 111                                   |

| CB 14 13   |          |                                               | Progam Mode a           |                                        | ••••                            |                 |              |                            |                                       |

| 000        |          |                                               | 0                       |                                        |                                 |                 |              |                            |                                       |

| 001        |          | [                                             | Data_Exchange           | -                                      | 13 12 11 10                     | (EEPROM READ AG | CCESS)       | 1                          |                                       |

| 010        |          |                                               |                         |                                        |                                 |                 |              |                            |                                       |

| 011        |          | Wri                                           | ite_Parameter I3 I2 I   | 11 10                                  | 13 12 11 10                     | (EEPROM WRITE A |              |                            |                                       |

| 100        |          |                                               | _                       | Write_Var_ID_Code                      | ID3 ID2 ID1 ID0                 |                 |              |                            |                                       |

| 101        |          |                                               |                         |                                        | 0x0                             |                 |              |                            |                                       |

| 110        |          | Rd_IO_Cfg <13:10>                             | Read_ID <i3:i0></i3:i0> | Read_ID_1 <i3:i0></i3:i0>              | Read_ID_2 <13:10>               | Reset_Slave 0x6 | Broadcast    | Rd_Status <s3:s0></s3:s0>  | reserved                              |

| 111        |          | Rd_IO_Cfg <13:10>                             | Read ID < 3:10>         | Read_ID_1 <i3:i0></i3:i0>              | Read ID 2 < 3:10>               | Reset_Slave 0x6 |              | Rd Status <s3:s0></s3:s0>  |                                       |

## 2.4 Master Mode

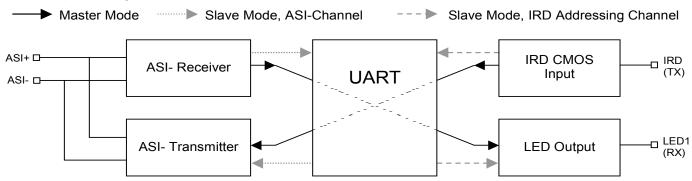

Master Mode and the related Repeater- and Monitor-Modes differ completely in their functional properties from the Slave Mode. While the IC can autonomously perform different tasks in Slave Mode, it will only act as physical layer transceiver in Master-, Repeater- and Monitor-Mode. The basic property of these modes is a modulation / demodulation of AS-i signals to Manchester-II-code and vice versa. The following figure shows the different data path configurations.

Figure 6: Data path in Master-, Repeater- and Monitor-Mode

Master-Mode, Repeater-Mode and Monitor-Mode differ from each other in the kind of signals that are available at the data I/O and parameter port pins of the IC. Following signal assignments are provided:

| Pin | Master Mode                                                                                            | Repeater Mode           | Monitor Mode                           |  |  |  |  |  |  |  |

|-----|--------------------------------------------------------------------------------------------------------|-------------------------|----------------------------------------|--|--|--|--|--|--|--|

| P0  | Receive Clock                                                                                          | Hi-Z                    | Receive Clock                          |  |  |  |  |  |  |  |

| P1  | Power Fail                                                                                             | Hi-Z                    | Power Fail                             |  |  |  |  |  |  |  |

| P2  | Receive Strobe – Slave Telegram                                                                        | Hi-Z                    | Receive Strobe – Slave Telegram        |  |  |  |  |  |  |  |

| P3  | Hi-Z                                                                                                   | Hi-Z                    | Receive Strobe – Master Telegram       |  |  |  |  |  |  |  |

| DI0 | Inverting of IRD input signal. If both inputs are on different level, the IRD input signal is inverted |                         |                                        |  |  |  |  |  |  |  |

| DI1 | before further processing, otherwise i                                                                 | t is directly forwarded | to the UART.                           |  |  |  |  |  |  |  |

| DI2 | Inverting of LED output signal. If both                                                                | inputs are on differer  | nt level, the LED output signal is in- |  |  |  |  |  |  |  |

| DI3 | verted after processing, otherwise it is                                                               | s directly forwarded to | the LED1 output.                       |  |  |  |  |  |  |  |

| DO0 | Hi-Z                                                                                                   | Hi-Z                    | Pulse Code Error                       |  |  |  |  |  |  |  |

| DO1 | Hi-Z                                                                                                   | Hi-Z                    | No Information Error                   |  |  |  |  |  |  |  |

| DO2 | Hi-Z                                                                                                   | Hi-Z                    | Parity Bit Error                       |  |  |  |  |  |  |  |

| DO3 | Hi-Z                                                                                                   | Hi-Z                    | Manchester-II-Code Error at IRD Input  |  |  |  |  |  |  |  |

More detailed signal descriptions can be found in chapters 3.6 Parameter Port and PST, 3.7 Data Port and DSR as well as 3.12 UART.

All rights reserved. The material contained herein may not be reproduced, adapted, merged, translated, stored, or used without the prior written consent of the copyright owner. The Information furnished in this publication is preliminary and subject to changes without notice.

## 2.5 E<sup>2</sup>PROM

The ASI4U provides an on-chip E<sup>2</sup>PROM with typical write times of 12.5 ms and read times of 110ns. For security reasons the memory area is structured in two independent data blocks and a single bit *Security* flag.

The data blocks are named User Area and Firmware Area. The Firmware Area contains all manufacturing related configuration data (i.e. selection of operational modes, ID codes, ...). It can be protected against undesired data modification by setting the *Program\_Mode\_Disable* flag to '1'.

The User Area contains only such data that is relevant for changes at the final application (i.e. field installation of slave module). The environment, where modifications of the user data may become necessary, can sometimes be rough and unpredictable. In order to ensure a write access cannot result in an undetected corruption of E<sup>2</sup>PROM data, additional security is provided when programming the User Area.

Any write access to the User Area (by calls *Address\_Assignment* or *Write\_ID\_Code1*) is accompanied by two write steps to the *Security* flag, one before and one after the actual modification of user data.

The following procedure is executed when writing to the User Area of the E<sup>2</sup>PROM:

- 1. The Security flag is programmed to '1'.

- 2. The content of the Security flag is read back, verifying it was programmed to '1'.

- 3. The user data is modified.

- 4. A read back of the written data is performed.

- 5. If the read back has proven successful programming of the user data, the *Security* flag is programmed back to '0'.

- 6. The content of the Security flag is read back, verifying it was programmed to '0'.

In addition to a read out of the data areas, the *Security* flag of the E<sup>2</sup>PROM is also read and evaluated during IC initialization. In case the value of the *Security* flag equals '1' (i.e. due to an undesired interruption of a User Area write access), the entire User Area data is treated as corrupted and the Slave Address is set to 0x0 in the corresponding volatile shadow registers during initialization. Thus the programming of the User Area data can be repeated.

| ASI4U internal<br>E <sup>2</sup> PROM Address [hex] | Bit<br>Position | EEPROM Cell Content    | EEPROM Register Content                                                                                                  |

|-----------------------------------------------------|-----------------|------------------------|--------------------------------------------------------------------------------------------------------------------------|

| 0                                                   | 0 3             | A0 A3                  | Slave address low nibble                                                                                                 |

| 1                                                   | 0               | A4                     | Slave address high nibble                                                                                                |

| 2                                                   | 0 2             | ID1_Bit0 ID1_Bit2      | ID_Code_Extension_1                                                                                                      |

| 2                                                   | 3               | ID1_Bit3               | <i>ID_Code_Extension_1</i> , A/B slave selection in extended address mode                                                |

| 3 7                                                 |                 |                        | Not implemented                                                                                                          |

| 8                                                   | 0 3             | ID_Bit0 ID_Bit3        | ID_Code                                                                                                                  |

| 9                                                   | 0 3             | ID2_Bit0 ID2_Bit3      | ID_Code_Extension_2                                                                                                      |

| А                                                   | 0 3             | IO_Bit0 IO_Bit3        | IO_Code                                                                                                                  |

| В                                                   | 0               | Multiplex_Data         | Multiplexed bi-directional Data Port mode                                                                                |

|                                                     | 1               | Multiplex_Paramter     | Multiplexed bi-directional Parameter Port mode                                                                           |

|                                                     | 2               | P0_Watchdog_Activation | Watchdog can be activated/deactivated by the logic value at parameter pin P0.<br>Watchdog_Active must <b>not</b> be set. |

|                                                     | 3               | Watchdog_Active        | Communication watchdog is continuously activated.                                                                        |

## Table 7: E<sup>2</sup>PROM Content

Copyright © 2006, ZMD AG, Rev.1.6

All rights reserved. The material contained herein may not be reproduced, adapted, merged, translated, stored, or used without the prior written consent of the copyright owner. The Information furnished in this publication is preliminary and subject to changes without notice.

Datasheet

## ZENTRUM MIKROELEKTRONIK DRESDEN AG "ASI for you" IC

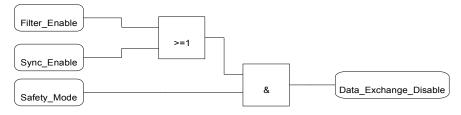

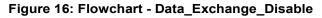

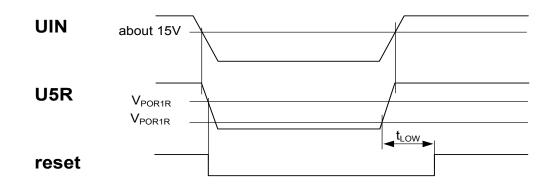

| ASI4U internal<br>E <sup>2</sup> PROM Address [hex] | Bit<br>Position | EEPROM Cell Content        | EEPROM Register Content                                                                                                                                                                                                                                                                                                                                                                             |