# LC33832P, S, M, PL, SL, ML-70/80/10

# 256 K (32768 words $\times$ 8 bits) Pseudo-SRAM

### **Overview**

The LC33832 series is composed of pseudo static RAM that operates on a single 5 V power supply and is organized as 32768 words  $\times$  8 bits. By using memory cells each composed of a single transistor and capacitor, together with peripheral CMOS circuitry, this series achieves ease of use with high density, high speed, and low power dissipation. The LC33832 series can easily accomplish auto-refresh and self-refresh by means of OE/RFSH input. As with asynchronous static RAM, WE input uses a system for incorporating input data at the WE rise, thereby facilitating interfacing with a microcomputer.

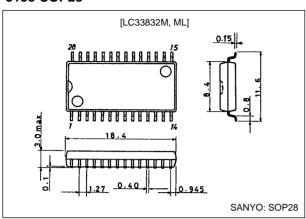

The LC33832 series features pin compatibility with 256 K static RAM (the LC36256A series), and available packages are the standard 28-pin DIP with widths of 600 mil or 300 mil, and the SOP with a width of 450 mil.

CE-only refresh can be accomplished by selecting address 256 (A0 to A7) within 4 ms.

### **Features**

- 32768 words × 8 bits configuration

- Single 5 V  $\pm 10\%$  power supply

- All input and output (I/O) TTL compatible

- · Fast access times and low power dissipation

- 4 ms refresh using 256 refresh cycle

- $\overline{\text{CE}}$ -only refresh, auto-refresh, and self-refresh

- Low-power version: 100 µA self-refresh current

- Package

DIP28-pin (600 mil) plastic package: LC33832P, PL DIP28-pin (300 mil) plastic package: LC33832S, SL SOP28-pin (450 mil) plastic package: LC33832M, ML

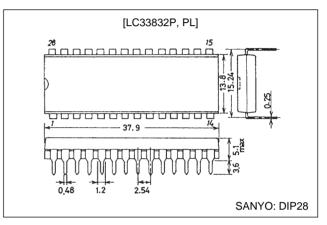

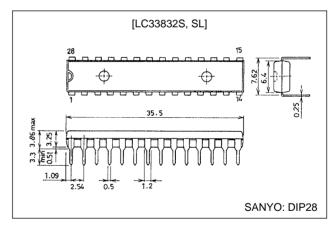

# **Package Dimensions**

unit: mm

3012A-DIP28

#### unit: mm

#### 3133-DIP28

•  $\overline{\text{CE}}$  access time/ $\overline{\text{OE}}$  access time/Cycle time/Current drain

| Parameter      |         | LC33832P, S, M, PL, SL, ML |                   |        |  |  |  |  |

|----------------|---------|----------------------------|-------------------|--------|--|--|--|--|

|                |         | -70                        | -80               | -10    |  |  |  |  |

| CE access time |         | 70 ns                      | 80 ns             | 100 ns |  |  |  |  |

| OE access time |         | 30 ns                      | 35 ns             | 40 ns  |  |  |  |  |

| Cycle time     |         | 115 ns                     | 115 ns 130 ns     |        |  |  |  |  |

| Operating      |         | 65 mA                      | 65 mA 60 mA 50 mA |        |  |  |  |  |

| Current drain  | Standby | 1 mA/100 µA (L version)    |                   |        |  |  |  |  |

SANYO Electric Co., Ltd. Semiconductor Bussiness Headquarters TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110-8534 JAPAN

#### 22897HA (OT)/52595TH (OT)/N1993JN/40893JN A8-9957, 58, 59, No. 4430-1/9

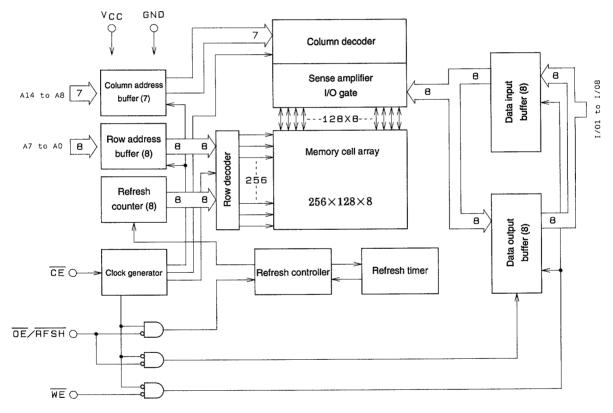

# **Block Diagram**

A01120

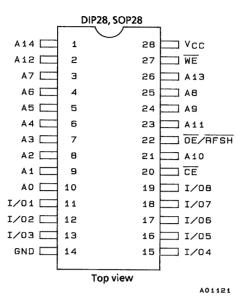

### **Pin Assignment**

#### **Pin Functions**

| A0 to A14       | Address input                      |

|-----------------|------------------------------------|

| WE              | Read/Write input                   |

| OE/RFSH         | Output-enable input/ refresh input |

| CE              | Chip-enable input                  |

| I/O1 to I/O8    | Data input/output                  |

| V <sub>CC</sub> | Power supply                       |

| GND             | Ground                             |

### **Functional Logic**

| CE | OE<br>/RFSH | WE | A0 to A7 | A8 to<br>A14 | I/O1<br>to I/O8 | State           |

|----|-------------|----|----------|--------------|-----------------|-----------------|

| Н  | Н           | Х  | Х        | Х            | HZ              | Standby         |

| L  | L           | Н  | VX       | VX           | OUT             | Read            |

| L  | Н           | L  | VX       | VX           | IN              | Write           |

| L  | н           | Н  | VX       | Х            | HZ              | CE-only refresh |

| н  | L           | Х  | Х        | Х            | HZ              | Self-refresh    |

| н  | NP          | Х  | Х        | Х            | HZ              | Auto-refresh    |

H .....High-level input of  $V_{IN}$  = 6.5 V to  $V_{IH}$  (min) L....Low-level input of  $V_{IN}$  =  $V_{IL}$  (max) to -1.0 V

X.....High- or low-level input

NP.....Negative-polarity pulse input

HZ.....High impedance

IN .....Input state

OUT.....Output state

# **Specifications**

### **Absolute Maximum Ratings**

| Parameter                    | Symbol              | Ratings      | Unit | Note |

|------------------------------|---------------------|--------------|------|------|

| Maximum supply voltage       | V <sub>CC</sub> max | -1.0 to +7.0 | V    | 1    |

| Input voltage                | V <sub>IN</sub>     | -1.0 to +7.0 | V    | 1    |

| Output voltage               | V <sub>OUT</sub>    | -1.0 to +7.0 | V    | 1    |

| Allowable power dissipation  | Pd max              | 600          | mW   | 1    |

| Output short-circuit current | I <sub>OUT</sub>    | 50           | mA   | 1    |

| Operating temperature        | Topr                | 0 to +70     | °C   | 1    |

| Storage temperature          | Tstg                | -55 to +150  | °C   | 1    |

Note: 1) Stresses greater than the above listed maximum values may result in damage to the device.

#### DC Recommended Operating Ranges at Ta = 0 to $+70^{\circ}C$

| Parameter                | Symbol          | min  | typ | max  | Unit | Note |

|--------------------------|-----------------|------|-----|------|------|------|

| Supply voltage           | V <sub>CC</sub> | 4.5  | 5.0 | 5.5  | V    | 2    |

| Input high level voltage | V <sub>IH</sub> | 2.4  |     | 6.5  | V    | 2    |

| Input low level voltage  | V <sub>IL</sub> | -1.0 |     | +0.8 | V    | 2    |

Note: 2) All voltages are referenced to GND.

#### DC Electrical Characteristics at Ta = 0 to $+70^{\circ}$ C, V<sub>CC</sub> = 5V $\pm$ 10%

| Parameter                 | Symbol            | Conditions                                                            | min | max               | Unit   | Note |     |    |     |

|---------------------------|-------------------|-----------------------------------------------------------------------|-----|-------------------|--------|------|-----|----|-----|

|                           |                   |                                                                       |     |                   | 70ns   |      | 65  |    |     |

| Operating current         | I <sub>CCA</sub>  | Average current during operation                                      |     | Access            | 80ns   |      | 60  | mA | 3,4 |

|                           |                   |                                                                       |     | time              | 100ns  |      | 50  |    |     |

| Standby current 1         | I <sub>CCS1</sub> | $\overline{CE} = \overline{OE}/\overline{RFSH} = V_{IH}$              |     |                   |        |      | 1   | mA |     |

| Standby ourrant 2         | I <sub>CCS2</sub> | $\Box$ CE = OE/RFSH = V <sub>CC</sub> –0.2V                           |     | 3832P, S          | 5, M   | 1    | mA  |    |     |

| Standby current 2         |                   |                                                                       |     | 3832PL,           | SL, ML |      | 100 | μA |     |

| Self-refresh current      |                   |                                                                       |     | LC33832P, S, M    |        |      | mA  |    |     |

| Sell-refresh current      | ICCSR             | $\overline{CE} = V_{CC} - 0.2V, \overline{OE}/\overline{RFSH} = 0.2V$ | LC3 | LC33832PL, SL, ML |        |      | 100 | μA |     |

| Input leakage current     | IIL               | $0V \le V_{IN} \le V_{CC}$ , pins other than test pin = 0V -10        |     |                   |        | +10  | μA  |    |     |

| Output leakage current    | I <sub>OL</sub>   | D <sub>OUT</sub> disable, 0V≤V <sub>OUT</sub> ≤V <sub>CC</sub>        |     |                   |        | -10  | +10 | μA |     |

| Output high level voltage | V <sub>OH</sub>   | I <sub>OUT</sub> = -5mA                                               |     |                   |        | 2.4  |     | V  |     |

| Output low level voltage  | V <sub>OL</sub>   | I <sub>OUT</sub> = 4.2mA                                              |     |                   |        |      | 0.4 | V  |     |

Note: 3) All current values are measured at minimal cycle rate. Since current flows immoderately, cycle times may become longer and shorter than shown here.

4) Dependent on output load. Maximum value is value during free state.

#### Input/Output Capacitance Characteristics at Ta = $25^{\circ}$ C, f = 1MHz, V<sub>CC</sub> = $5V\pm10\%$

| <u> </u>                            |                  | /   |     |      |                        |

|-------------------------------------|------------------|-----|-----|------|------------------------|

| Parameter                           | Symbol           | min | max | Unit | Test conditions        |

| Input capacitance (A0 to A14)       | C <sub>IN1</sub> |     | 5   | pF   | V <sub>IN1</sub> = 0 V |

| Input capacitance (CE, OE/RFSH, WE) | C <sub>IN2</sub> |     | 7   | pF   | V <sub>IN2</sub> = 0 V |

| Input/output capacitance            | C <sub>I/O</sub> |     | 10  | pF   | $V_{I/O} = 0 V$        |

Sampling inspections, and not full-lot inspections, are carried out for these parameters.

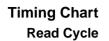

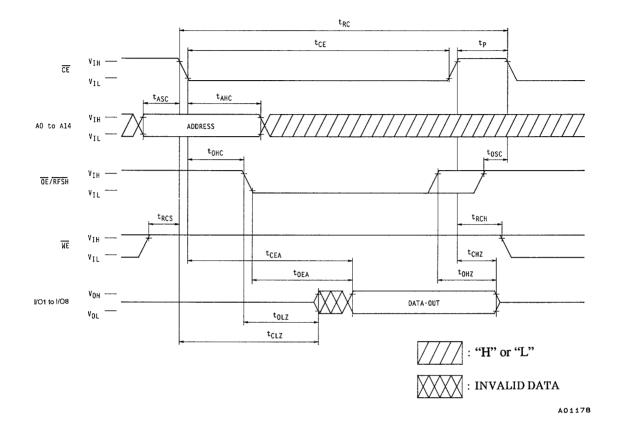

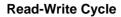

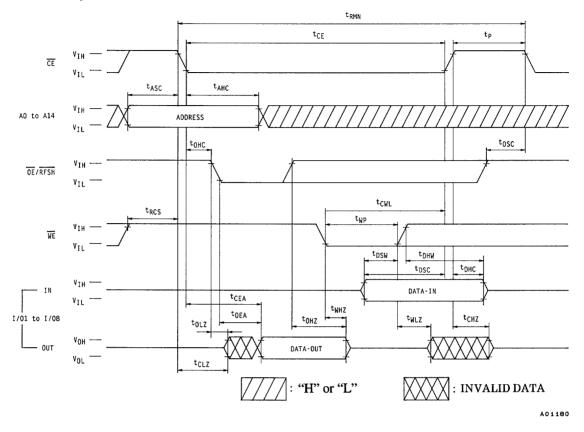

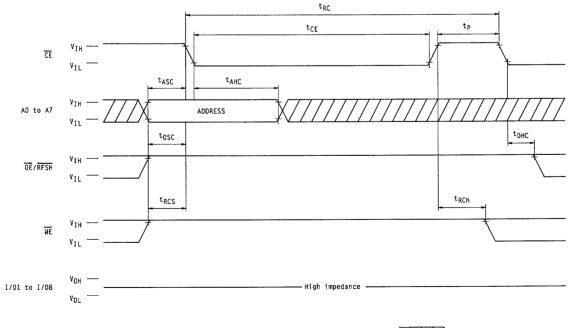

# AC Electrical Characteristics at Ta = 0 to +70°C, $V_{CC}$ 5V±10% (Notes 5, 6, 7, 8, 9)

|                                                                       |                  | LC33832P, S, M, PL, SL, ML |       |      |       |      |       |      |      |

|-----------------------------------------------------------------------|------------------|----------------------------|-------|------|-------|------|-------|------|------|

| Parameter                                                             | Symbol           | -7                         | 70    |      | -80   |      | 10    | Unit | Note |

|                                                                       |                  | min                        | max   | min  | max   | min  | max   |      |      |

| Random read,<br>write cycle time                                      | t <sub>RC</sub>  | 115                        |       | 130  |       | 160  |       | ns   |      |

| Read-write cycle time                                                 | t <sub>RMW</sub> | 165                        |       | 195  |       | 240  |       | ns   |      |

| CE pulse width                                                        | t <sub>CE</sub>  | 70                         | 10000 | 80   | 10000 | 100  | 10000 | ns   |      |

| CE precharge time                                                     | t <sub>P</sub>   | 35                         |       | 40   |       | 50   |       | ns   |      |

| CE access time                                                        | t <sub>CEA</sub> |                            | 70    |      | 80    |      | 100   | ns   |      |

| OE access time                                                        | t <sub>OEA</sub> |                            | 30    |      | 35    |      | 40    | ns   |      |

| CE output enable time                                                 | t <sub>CLZ</sub> | 10                         |       | 10   |       | 10   |       | ns   |      |

| OE output enable time                                                 | t <sub>OLZ</sub> | 0                          |       | 0    |       | 0    |       | ns   |      |

| WE output enable time                                                 | t <sub>WLZ</sub> | 0                          |       | 0    |       | 0    |       | ns   |      |

| CE output disable time                                                | t <sub>CHZ</sub> | 0                          | 20    | 0    | 25    | 0    | 30    | ns   | 10   |

| OE output disable time                                                | t <sub>OHZ</sub> | 0                          | 20    | 0    | 25    | 0    | 30    | ns   | 10   |

| WE output disable time                                                | t <sub>WHZ</sub> | 0                          | 20    | 0    | 25    | 0    | 30    | ns   | 10   |

| $\overline{\text{OE}}$ hold time for $\overline{\text{CE}}$           | t <sub>OHC</sub> | 0                          |       | 0    |       | 0    |       | ns   |      |

| $\overline{OE}$ setup time for $\overline{CE}$                        | tosc             | 10                         |       | 10   |       | 10   |       | ns   |      |

| Read command setup time                                               | t <sub>RCS</sub> | 0                          |       | 0    |       | 0    |       | ns   |      |

| Read command hold time                                                | t <sub>RCH</sub> | 0                          |       | 0    |       | 0    |       | ns   |      |

| Write pulse width                                                     | t <sub>WP</sub>  | 55                         |       | 60   |       | 70   |       | ns   |      |

| Write command hold time                                               | t <sub>WCH</sub> | 55                         |       | 60   |       | 70   |       | ns   |      |

| Write command lead time                                               | t <sub>CWL</sub> | 55                         |       | 60   |       | 70   |       | ns   |      |

| Input data setup time for $\overline{WE}$                             | t <sub>DSW</sub> | 30                         |       | 35   |       | 40   |       | ns   | 11   |

| Input data setup time for $\overline{CE}$                             | t <sub>DSC</sub> | 30                         |       | 35   |       | 40   |       | ns   | 11   |

| Input data hold time for $\overline{WE}$                              | t <sub>DHW</sub> | 0                          |       | 0    |       | 0    |       | ns   | 11   |

| Input data hold time for $\overline{CE}$                              | t <sub>DHC</sub> | 0                          |       | 0    |       | 0    |       | ns   | 11   |

| Address setup time for $\overline{CE}$                                | t <sub>ASC</sub> | 0                          |       | 0    |       | 0    |       | ns   | 12   |

| Address hold time for $\overline{CE}$                                 | t <sub>AHC</sub> | 15                         |       | 20   |       | 25   |       | ns   | 12   |

| Auto-refresh cycle time                                               | t <sub>FC</sub>  | 115                        |       | 130  |       | 160  |       | ns   |      |

| $\overline{RFSH}$ delay time for $\overline{CE}$                      | t <sub>RFD</sub> | 35                         |       | 40   |       | 50   |       | ns   |      |

| RFSH pulse width (auto-refresh)                                       | t <sub>FAP</sub> | 75                         | 8000  | 80   | 8000  | 80   | 8000  | ns   | 13   |

| RFSH precharge time (auto-refresh)                                    | t <sub>FP</sub>  | 30                         |       | 30   |       | 30   |       | ns   | 13   |

| RFSH active CE delay time (auto-refresh)                              | t <sub>FCE</sub> | 135                        |       | 160  |       | 190  |       | ns   | 13   |

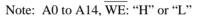

| RFSH pulse width (self-refresh)                                       | t <sub>FAS</sub> | 8000                       |       | 8000 |       | 8000 |       | ns   | 13   |

| $\overline{RFSH}$ precharge $\overline{CE}$ delay time (self-refresh) | t <sub>FRS</sub> | 135                        |       | 160  |       | 190  |       | ns   | 13   |

| Refresh time                                                          | t <sub>REF</sub> |                            | 4     |      | 4     |      | 4     | ms   |      |

| Rise and fall time                                                    | t <sub>T</sub>   | 3                          | 50    | 3    | 50    | 3    | 50    | ns   |      |

Continued on next page.

Continued from preceding page.

- Note: 5) To accomplish internal initialization,  $\overline{CE}$  and  $\overline{OE}/\overline{RFSH}$  are fixed at  $V_{IH}$  for an interval of 1 ms when  $V_{CC}$  reaches the specified voltage after power is switched on.

- 6) Measured at  $t_T = 5$  ns.

- 7) When measuring input signal timing,  $V_{IH}$  (min) and  $V_{IL}$  (max) are reference levels.

- 8) Measured using an equivalent of 100 pF and two standard TTL loads.

- 9)  $\overline{\text{OE}/\text{RFSH}}$  input functions as output-enable input ( $\overline{\text{OE}}$ ) when  $\overline{\text{CE}} = V_{\text{IL}}$ , and as refresh input ( $\overline{\text{RFSH}}$ ) when  $\overline{\text{CE}} = V_{\text{IH}}$ .

- 10) t<sub>CHZ</sub>, t<sub>OHZ</sub>, and t<sub>WHZ</sub> are defined as the time until output enters the open circuit state and the output voltage level becomes immeasurable.

- 11) As with ordinary static RAM, write data is incorporated at the rise of  $\overline{WE}$  input or  $\overline{CE}$  input, whichever is earlier, and write data is therefore held during  $t_{DSW}$ ,  $t_{DSC}$ ,  $t_{DHW}$ , or  $t_{DHC}$ .

- 12) Because address input is incorporated at the fall of  $\overline{CE}$ , the address is maintained during  $t_{ASC}$  or  $t_{AHC}$ .

- 13) Auto-refresh and self-refresh are determined by  $\overline{OE/RFSH}$  pulse width when  $\overline{CE} = V_{IH}$ , and are defined as auto-refresh when below  $t_{FAP}$  (max), or as self-refresh when above  $t_{FAS}$  (min). In order to activate  $\overline{CE}$  after the completion of each refresh,  $t_{FCE}$  must be assured for auto-refresh, or  $t_{FRS}$  must be assured for self-refresh.

Write Cycle

A01179

**CE**-Only Refresh Cycle

Note: A8 to A14: "H" or "L"

: "H" or "L"

A01181

#### Self-Refresh Cycle

- No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace equipment, nuclear power control systems, vehicles, disaster/crime-prevention equipment and the like, the failure of which may directly or indirectly cause injury, death or property loss.

- Anyone purchasing any products described or contained herein for an above-mentioned use shall:

- ① Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors and all their officers and employees, jointly and severally, against any and all claims and litigation and all damages, cost and expenses associated with such use:

- In the second second

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of February, 1997. Specifications and information herein are subject to change without notice.