## PLQ16R8-5 SERIES

#### **FEATURES**

- Ultra high-speed

- t<sub>PD</sub> = 5ns and f<sub>MAX</sub> = 118MHz

- 100% functionally and pin-for-pin compatible with industry standard 20-pin PAL® ICs

- Power-up reset function to enhance state machine design and testability

- Design support provided via SLICE and other CAD tools for Series 20 PAL devices

- Field-programmable on industry standard programmers

- Security fuse

- Individual 3-State control of all outputs

- Register Preload for testability

- Power-up 3-State

- 20-Pin DIP and 20-Pin PLCC

### DESCRIPTION

The Signetics PLQ16XX family consists of ultra high-speed 5ns versions of Series 20 PAI devices

The PLQ16XX family is 100% functional and pin-compatible with the 16L8, 16R8, 16R6, and 16R4 Series devices.

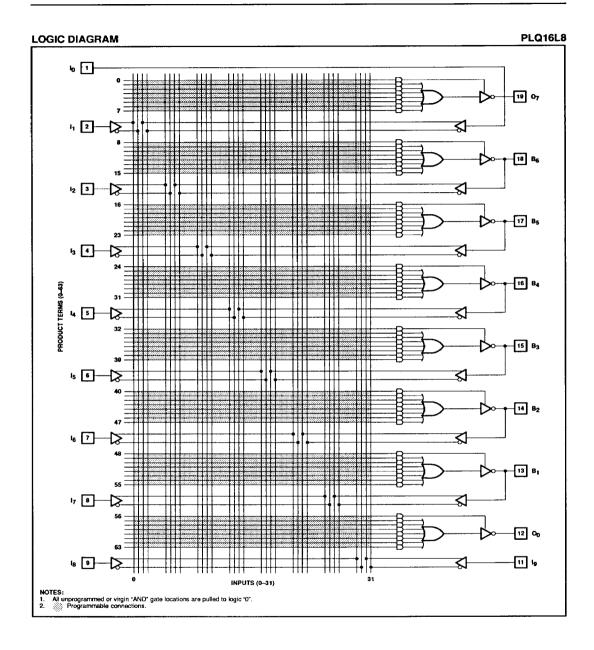

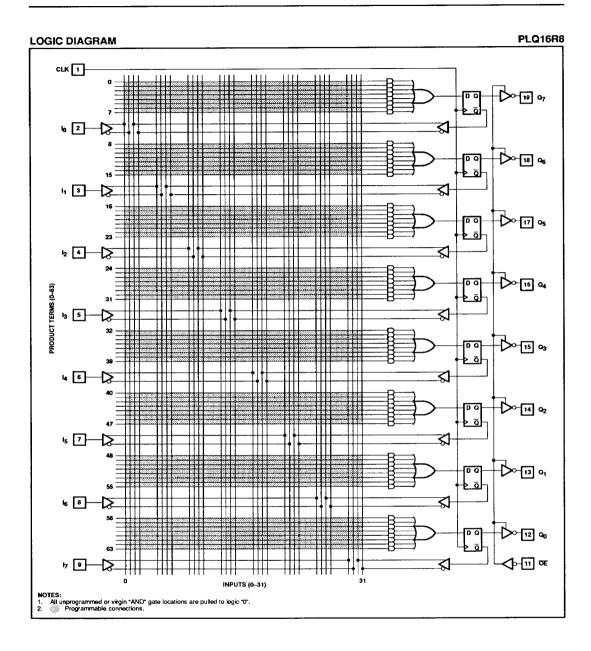

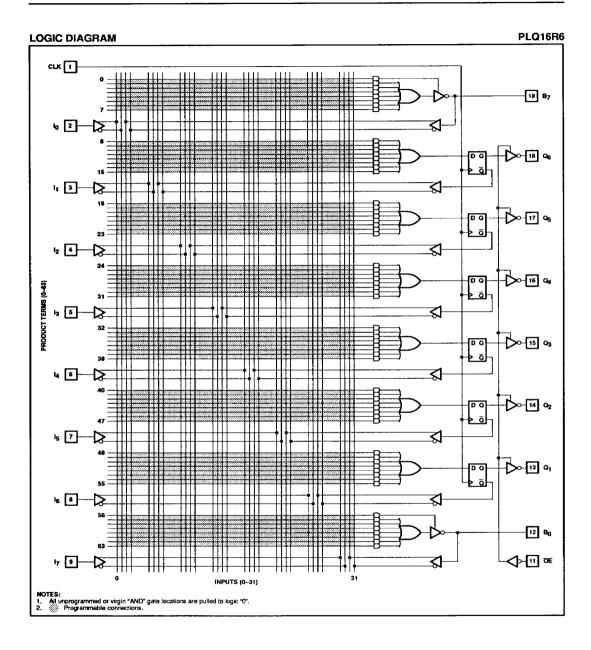

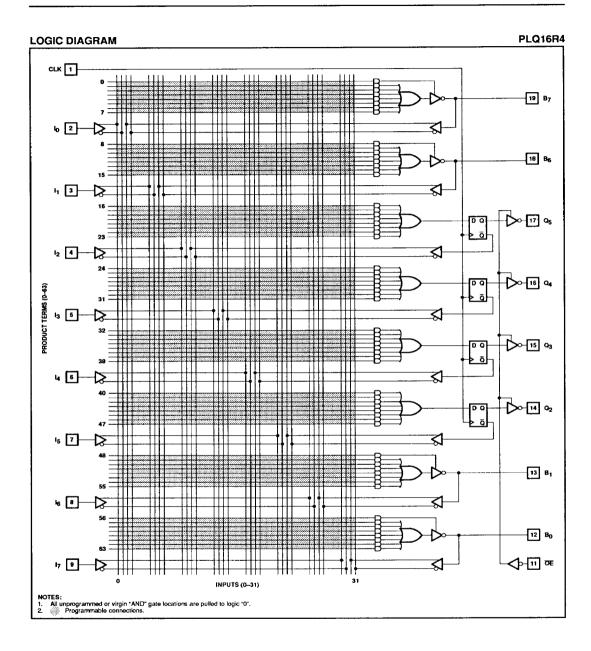

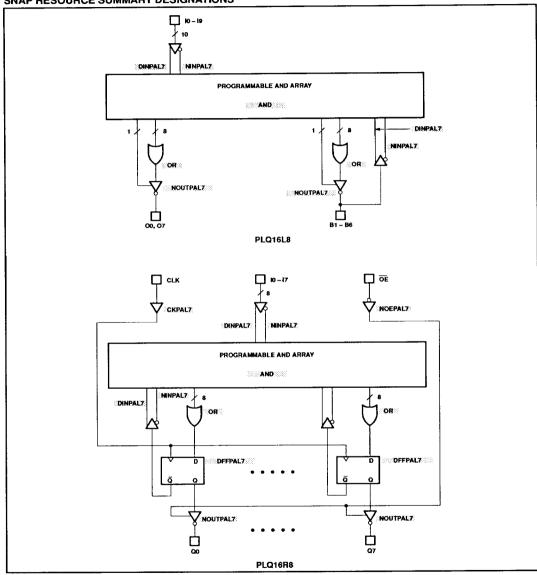

The sum of products (AND-OR) architecture is comprised of 64 programmable AND gates and 8 fixed OR gates. Multiple bidirectional pins provide variable input/output pin ratios. Individual 3-State control of all outputs and registers with feedback (R8, R6, R4) is also provided. Proprietary designs can be protected by programming the security fuse.

The PLQ16R8, R6, and R4 have D-type flip-flops which are loaded on the Low-to-High transition of the clock input.

In order to facilitate state machine design and testing, a power-up reset function has been incorporated into these devices to reset all internal registers to active-Low after a specific period of time.

The Signetics State-of-the-Art BiCMOS process, known as QUBiC, has been

employed to achieve higher levels of operating performance for the PLQ16XX family of PLDs. The QUBiC transistors have been optimized to provide two-thirds more speed at less than half the power consumed from products using our last generation of bipolar technology. QUBiC reduces on-chip delays and provides high output drive currents while consuming power at very low levels

The PLQ16XX family of devices are field programmable, enabling the user to quickly generate custom patterns using standard programming equipment. See the programmer section for qualified programmers.

The SLICE software package from Signetics supports easy design entry for the PLQ16XX series as well as other PLD devices from Signetics, The PLQ16XX series are also supported by other standard CAD tools for PAL-type devices.

Order codes are listed in the Ordering Information table.

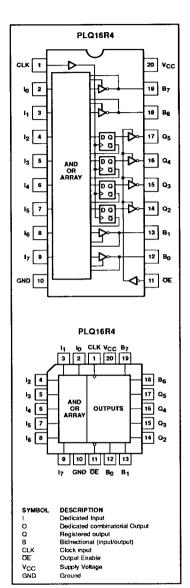

| DEVICE NUMBER | DEDICATED<br>INPUTS | COMBINATORIAL OUTPUTS | REGISTERED<br>OUTPUTS |

|---------------|---------------------|-----------------------|-----------------------|

| PLQ16L8       | 10                  | B (6 I/O)             | 0                     |

| PLQ16R8       | 8                   | 0                     | 8                     |

| PLQ16R6       | 8                   | 21/0                  | 6                     |

| PLQ16R4       | 8                   | 4 I/O                 | 4                     |

### ORDERING INFORMATION

| DESCRIPTION                                | ORDER CODE                                           |  |

|--------------------------------------------|------------------------------------------------------|--|

| 20-Pin Plastic Dual-In-Line<br>300mil-wide | PLQ16R8-5N<br>PLQ16R6-5N<br>PLQ16R4-5N<br>PLQ16L8-5N |  |

| 20-Pin Plastic Leaded Chip Carrier (PLCC)  | PLQ16R8-5A<br>PLQ16R6-5A<br>PLQ16R4-5A<br>PLQ16L8-5A |  |

The PLQ16XX series of devices are also processed to military requirements for operation over the military temperature range. For specifications and ordering information, consult the Signetics Military Data Handbook.

@PAL is a registered trademark of Advanced Micro Devices, Inc.

## PLQ16R8-5 SERIES

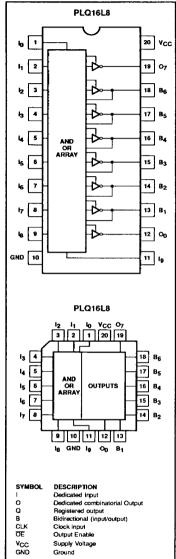

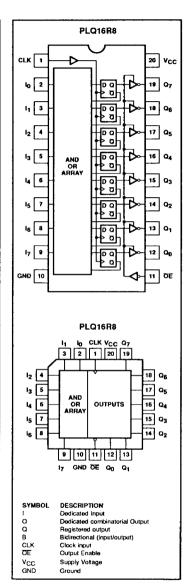

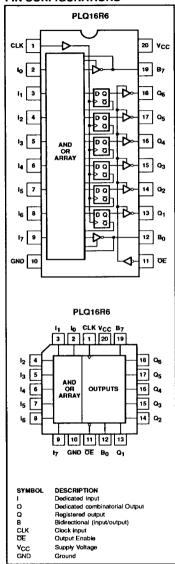

### PIN CONFIGURATIONS

## PLQ16R8-5 SERIES

#### PIN CONFIGURATIONS

## PLQ16R8-5 SERIES

# PLQ16R8-5 SERIES

## PLQ16R8-5 SERIES

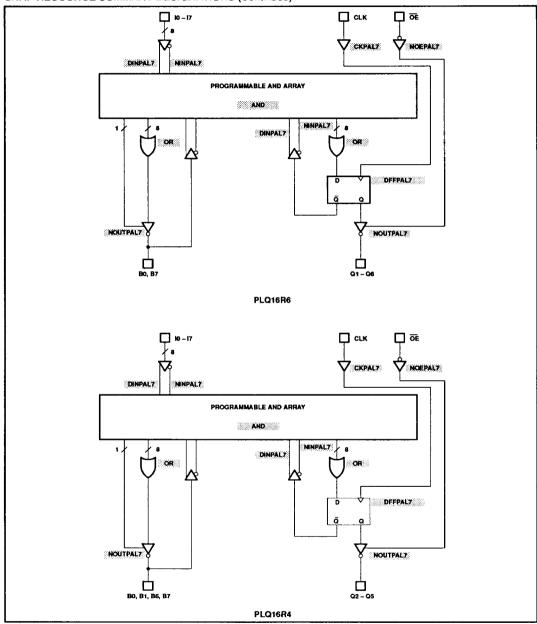

#### **FUNCTIONAL DESCRIPTIONS**

The PLQ16XX series utilizes the familiar sum-of-products implementation consisting of a programmable AND array and a fixed OR array. These devices are capable of replacing an equivalent of four or more SSI/MSI integrated circuits to reduce package count and board area occupancy, consequently improving reliability and design cycle over Standard Cell or gate array options. By programming the security fuse, proprietary designs can be protected from duplication.

The PLQ16XX series consists of four PAL-type devices. Depending on the particular device type, there are a variable number of combinatorial and registered outputs available to the designer. The PLQ16L8 is a combinatorial part with 8 user configurable outputs (6 bidirectional), while the other three devices, PLQ16R8, PLQ16R6, PLQ16R4, have respectively 8, 6, and 4 output registers.

### 3-State Outputs

The PLQ16XX series devices also feature 3-State output buffers on each output pin which can be programmed for individual control of all outputs. The registered outputs (Qn) are controlled by an external input (/OE), and the combinatorial outputs (On, Bn) use a product term to control the enable function.

#### Programmable Bidirectional Pins

The PLQ16XX products feature variable Input/Output ratios. In addition to 8 dedicated inputs, each combinatorial output pin of the registered devices can be individually programmed as an input or output. The PLQ16L8 provides 10 dedicated inputs and 6 Bidirectional I/O lines that can be individually configured as inputs or outputs.

#### **Output Registers**

The PLQ16R8 has 8 output registers, the 16R6 has 6, and the 16R4 has 4. Each output register is a D-type flip-flop which is loaded on the Low-to-High transition of the clock input. These output registers are capable of feeding the outputs of the registers back into the array to facilitate design of synchronous state machines.

#### Power-up Reset

By resetting all flip-flops to a logic Low, as the power is turned on, the PLQ16R8, R6, R4 enhance state machine design and initialization capability.

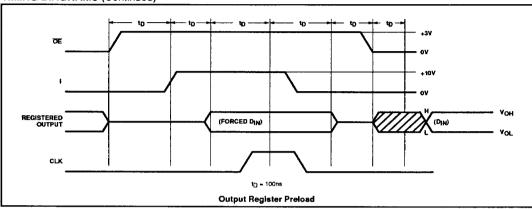

#### Register Preload

Preload function allows the register to be loaded from the output pins. This feature allows functional testing of sequential patterns by loading output states.

#### Power-up 3-State

All outputs will be disabled when V<sub>CC</sub> is 3.0V ± 20% (25°C). This special feature keeps outputs 3-Stated during power-up. Only when V<sub>CC</sub> reaches its normal operating range will device function normally.

#### Software Support

Like other Programmable Logic Devices from Signetics, the PLQ16XX series are supported by SLICE, the PC-based software development tool from Signetics. The PLQ16XX family of devices are also supported by standard CAD tools for PAL devices, including ABEL and CUPL.

SLICE is available free of charge to qualified users.

#### Logic Programming

The PLQ16XX series is fully supported by industry standard (JEDEC compatible) PLD CAD tools, including Signetics SLICE and SNAP design software packages. ABEL™ CUPL™ and PALASM® 90 design software packages also support the PLQ16XX architecture.

All packages allow Boolean and state equation entry formats. SNAP, ABEL and CUPL also accept, as input, schematic capture format.

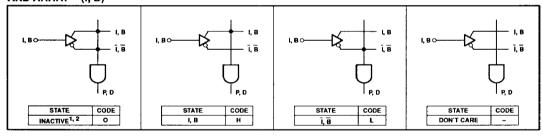

### AND ARRAY - (I, B)

### **VIRGIN STATE**

A factory shipped virgin device contains all fusible links intact, such that:

- All P<sub>n</sub> terms are disabled.

- 2. All Pn terms are active on all outputs.

ABEL is a trademark of Data I/O Corp. CUPL is a trademark of Logical Devices, Inc. PALASM is a registered trademark of AMD Corp.

# PLQ16R8-5 SERIES

### ABSOLUTE MAXIMUM RATINGS1

|                  |                           | RATINGS |      |                 |  |

|------------------|---------------------------|---------|------|-----------------|--|

| SYMBOL           | PARAMETER                 | MIN     | MAX  | UNIT            |  |

| Vcc              | Supply voltage            | -0.5    | +7.0 | V <sub>DC</sub> |  |

| V <sub>IN</sub>  | Input voltage             | -1.2    | +7.0 | V <sub>DC</sub> |  |

| V <sub>OUT</sub> | Output voltage            |         | +5.5 | V <sub>DC</sub> |  |

| I <sub>IN</sub>  | Input currents            | -30     | +30  | mA              |  |

| lout             | Output currents           |         | +100 | mA              |  |

| T <sub>stg</sub> | Storage temperature range | -65     | +150 | °C              |  |

### NOTE:

### **OPERATING RANGES**

|        |                                | RATINGS |       |                 |  |

|--------|--------------------------------|---------|-------|-----------------|--|

| SYMBOL | PARAMETER                      | MIN     | MAX   | UNIT            |  |

| Vcc    | Supply voltage                 | +4.75   | +5.25 | V <sub>DC</sub> |  |

| Tamb   | Operating free-air temperature | 0       | +75   | °C              |  |

#### THERMAL RATINGS

| TEMPERATURE                                |       |  |

|--------------------------------------------|-------|--|

| Maximum junction                           | 150°C |  |

| Maximum ambient                            | 75°C  |  |

| Allowable thermal rise ambient to junction | 75°C  |  |

<sup>1.</sup> Stresses above those listed may cause malfunction or permanent damage to the device. This is a stress rating only. Functional operation at these or any other condition above those indicated in the operational and programming specification of the device is not implied.

# PLQ16R8-5 SERIES

### DC ELECTRICAL CHARACTERISTICS

$0^{\circ}$ C  $\leq T_{amb} \leq +75^{\circ}$ C, 4.75V  $\leq V_{CC} \leq 5.25$ V

|                 | PARAMETER                      | TEST CONDITIONS                                                             | LIMITS |          |      |      |

|-----------------|--------------------------------|-----------------------------------------------------------------------------|--------|----------|------|------|

| SYMBOL          |                                |                                                                             | MIN    | TYP1     | MAX  | UNIT |

| Input voitag    | je <sup>2</sup>                |                                                                             |        |          |      |      |

| V <sub>IL</sub> | Low                            | V <sub>CC</sub> = MIN                                                       |        |          | 0.8  | ٧    |

| V <sub>IH</sub> | High                           | $V_{CC} = MAX$                                                              | 2.0    |          |      | V    |

| V <sub>IC</sub> | Clamp                          | V <sub>CC</sub> = MIN, I <sub>IN</sub> = -18mA                              | ·      | -0.8     | -1.5 | v    |

| Output volt     | age                            |                                                                             |        |          |      |      |

|                 |                                | V <sub>CC</sub> = MIN, V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub> |        |          |      |      |

| VOL             | Low                            | I <sub>OL</sub> = 24mA                                                      | -      |          | 0.5  | V    |

| V <sub>OH</sub> | High                           | $I_{OH} = -3.2 \text{ mA}$                                                  | 2.4    | <u> </u> |      | v    |

| Input curre     | nt                             |                                                                             |        |          |      |      |

|                 |                                | V <sub>CC</sub> = MAX                                                       |        |          |      |      |

| 1 <sub>IL</sub> | Low <sup>3</sup>               | $V_{IN} = 0.40V$                                                            |        |          | -250 | μА   |

| I <sub>IH</sub> | High <sup>3</sup>              | $V_{1N} = 2.7V$                                                             |        | 1        | 25   | μΑ   |

| i <sub>i</sub>  | Maximum input current          | $V_{IN} = 5.5V$ , $V_{CC} = MAX$                                            |        |          | 100  | μΑ   |

| Output cur      | rent                           |                                                                             |        |          |      |      |

|                 |                                | V <sub>CC</sub> = MAX                                                       |        |          |      |      |

| lozH            | Output leakage                 | $V_{OUT} = 2.7V$                                                            |        |          | 100  | μΑ   |

| lozL            | Output leakage                 | $V_{OUT} = 0.4V$                                                            |        |          | -100 | μΑ   |

| los             | Short circuit 4, 5             | V <sub>OUT</sub> = 0.5V                                                     | -30 _  |          | -130 | mA   |

| lcc             | V <sub>CC</sub> supply current | V <sub>CC</sub> = MAX                                                       |        | 160      | 180  | mA   |

| Capacitano      | ce <sup>6</sup>                |                                                                             |        |          |      |      |

| CIN             | Input                          | V <sub>CC</sub> = 5V                                                        |        |          |      |      |

|                 |                                | $V_{OUT} = 2.0V$                                                            |        | 8        |      | ρF   |

| Св              | I/O (B)                        | $V_{OUT} = 2V, f = 1MHz$                                                    |        | 8        |      | pF   |

#### NOTES:

- All typical values are at V<sub>CC</sub> = 5V, T<sub>amb</sub> = +25°C.

- 2. All voltage values are with respect to network ground terminal.

- Leakage current for bidirectional pins is the worst case of \$\(\frac{1}{11L}\) and \$\(\frac{1}{10ZL}\) or \$\(\frac{1}{1H}\) and \$\(\frac{1}{10ZH}\).

Test one at a time.

- 5. Duration of short circuit should not exceed 1 second.

- 6. These parameters are not 100% tested but periodically sampled.

## PLQ16R8-5 SERIES

### **AC ELECTRICAL CHARACTERISTICS**

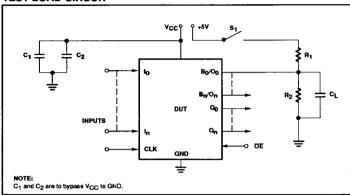

$R_1 = 200\Omega$ ,  $R_2 = 390\Omega$ ,  $0^{\circ}C \le T_{arch} \le +75^{\circ}C$ ,  $4.75V \le V_{CC} \le 5.25V$

|                  | PARAMETER                                                               |                   | то                | LIMITS           |     |      |

|------------------|-------------------------------------------------------------------------|-------------------|-------------------|------------------|-----|------|

| SYMBOL           |                                                                         | FROM              |                   | MIN <sup>1</sup> | MAX | TINU |

| Pulse Wid        | ith                                                                     |                   |                   |                  |     |      |

| t <sub>СКН</sub> | Clock High                                                              | CLK+              | CLK-              | 3.0              |     | ns   |

| ‡CKL             | Clock Low                                                               | CLK-              | CLK+              | 3.0              |     | ns   |

| t <sub>CKP</sub> | Period                                                                  | CLK+              | CLK+              | 6.0              |     | ns   |

| Setup & F        | lold time                                                               |                   |                   |                  |     |      |

| t <sub>IS</sub>  | Input                                                                   | Input or feedback | CLK+              | 4.0              |     | ns   |

| t <sub>IH</sub>  | Input                                                                   | CLK+              | Input or feedback | 0                |     | ns   |

| Propagati        | on delay                                                                |                   |                   |                  |     |      |

| t <sub>CKO</sub> | Clock                                                                   | CLK±              | Q±                |                  | 4.5 | ns   |

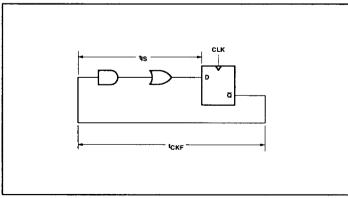

| t <sub>CKF</sub> | Clock <sup>3</sup>                                                      | CLK±              | ۵                 |                  | 2.5 | ns   |

| t <sub>PD</sub>  | Output (16L8, R6, R4) <sup>2</sup>                                      | I, B              | Output            |                  | 5.0 | ns   |

| t <sub>OE1</sub> | Output enable <sup>4</sup>                                              | ØE .              | Output enable     |                  | 6.0 | ns   |

| t <sub>OE2</sub> | Output enable <sup>4,5</sup>                                            | 1                 | Output enable     |                  | 8.0 | ns   |

| t <sub>OD1</sub> | Output disable <sup>4</sup>                                             | OE                | Output disable    |                  | 6.0 | ns   |

| t <sub>OD2</sub> | Output disable <sup>4,5</sup>                                           | ı                 | Output disable    |                  | 8.0 | ns   |

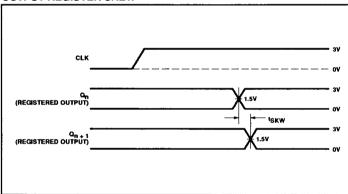

| tskw             | Output                                                                  | Q                 | Q                 |                  | 1.0 | ns   |

| \$PPR            | Power-Up Reset                                                          | V <sub>CC</sub> + | Q+                |                  | 8.0 | ns   |

| Frequenc         | y (16R8, R6, R4)                                                        |                   | •                 |                  |     |      |

|                  | No feedback 1/ (t <sub>CKL</sub> + t <sub>CKH</sub> ) <sup>6</sup>      |                   |                   |                  | 167 | MHz  |

| fmax             | Internal feedback 1/ (t <sub>IS</sub> + t <sub>CKF</sub> ) <sup>6</sup> |                   |                   |                  | 154 | MHz  |

|                  | External feedback 1/ (t <sub>IS</sub> + t <sub>CKO</sub> ) <sup>6</sup> |                   |                   |                  | 118 | MHz  |

For definitions of the terms, please refer to the Timing/Frequency Definitions tables. NOTES:

1. CL = 0pF while measuring minimum output delays.

2.  $t_{PD}$  test conditions:  $C_L = 50 pF$  (with jig and scope capacitance),  $V_{IH} = 3V$ ,  $V_{IL} = 0V$ ,  $V_{OH} = V_{OL} = 1.5V$ .

3. t<sub>CKF</sub> was calculated from measured Internal f<sub>MAX</sub>.

<sup>4.</sup> For 3-State output; output enable times are tested with C<sub>L</sub> = 50pF to the 1.5V level, and S<sub>1</sub> is open for high-impedance to High tests and dosed for high-impedance to Low tests. Output disable times are tested with  $C_L \cdot 5pF$ . High-to-High impedance to the state of the sta

frequency.

## PLQ16R8-5 SERIES

## **TEST LOAD CIRCUIT**

## **OUTPUT REGISTER SKEW**

## **CLOCK TO FEEDBACK PATH**

# PLQ16R8-5 SERIES

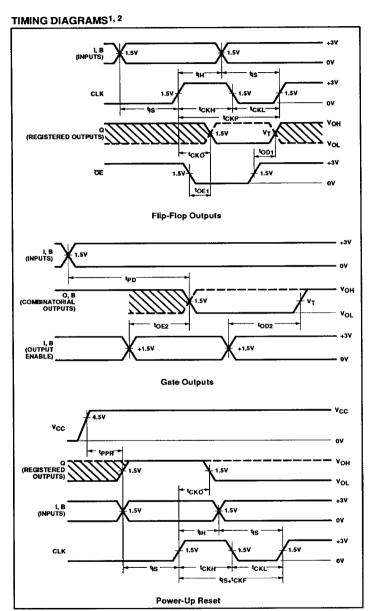

### TIMING DEFINITIONS

| SYMBOL           | PARAMETER                                                                                                                   |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------|--|

| t <sub>CKH</sub> | Width of input clock pulse.                                                                                                 |  |

| <sup>t</sup> CKL | interval between clock pulses.                                                                                              |  |

| t <sub>CKP</sub> | Clock period.                                                                                                               |  |

| tıs              | Required delay between beginning of valid input and positive transition of clock.                                           |  |

| t <sub>IH</sub>  | Required delay between positive transition of dock and end of valid input data.                                             |  |

| tckF             | Delay between positive transition of clock and when internal Q output of flip-flop becomes valid.                           |  |

| tско             | Delay between positive transition of clock and when outputs become valid (with OE Low).                                     |  |

| t <sub>OE1</sub> | Delay between beginning of<br>Output Enable Low and when<br>outputs become valid.                                           |  |

| t <sub>OD1</sub> | Delay between beginning of<br>Output Enable High and when<br>outputs are in the Off-State.                                  |  |

| t <sub>OE2</sub> | Delay between predefined<br>Output Enable High, and<br>when combinational outputs<br>become valid.                          |  |

| t <sub>OD2</sub> | Delay between predefined<br>Output Enable Low and when<br>combinational outputs are in<br>the Off-State.                    |  |

| tppR             | Delay between V <sub>CC</sub> (after power-on) and when flip-flop outputs become preset at "1" (internal Q outputs at "0"). |  |

| Þр               | Propagation delay between combinational inputs and outputs.                                                                 |  |

| t <sub>D</sub>   | Delay between each input change.                                                                                            |  |

### **FREQUENCY DEFINITIONS**

| <sup>f</sup> MAX | No feedback: Determined by the minimum clock period,  1/(tc <sub>KL</sub> + tc <sub>Kl</sub> ). Internal feedback: Determined by the internal delay from flip-flop outputs through the internal feedback and array to the flip-flop inputs, 1/(tis + tc <sub>K</sub> c). External feedback: Determined by clock-to-output delay and input setup time,  1/(tis + tc <sub>KC</sub> ). |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

#### NOTES:

- 1. Input pulse amplitude is 0V to 3V.

- 2. Input rise and fall times are 2.0ns typical.

March 16, 1992

102

## PLQ16R8-5 SERIES

### PROGRAMMING/SOFTWARE

Refer to Section 8 (Development Software) and Section 9 (Third-Party Programmer/ Software Support) of this data handbook for additional information.

# PLQ16R8-5 SERIES

**SNAP RESOURCE SUMMARY DESIGNATIONS**

# PLQ16R8-5 SERIES

## SNAP RESOURCE SUMMARY DESIGNATIONS (Continued)