## Description

NEC's µPB100474 is a very high-speed 100K interface ECL RAM organized as 1,024 words by 4 bits and designed with open-emitter, noninverted outputs. It is available in a 24-pin cerdip, 24-pin ceramic LCC, or 24-pin ceramic flatpack package.

## **Features**

- □ 1024-word by 4-bit organization

- □ 100K interface ECL

- Full voltage and temperature compensation

- Noninverted, open emitter outputs

- □ Fast access times

- 24-pin cerdip, ceramic LCC, and ceramic flatpack packaging

## **Ordering Information**

| Part Number          |      | Access<br>Time (max) | Supply<br>Current (min) | Package        |  |  |

|----------------------|------|----------------------|-------------------------|----------------|--|--|

| μPB100474B-6         |      | 6 ns                 | -450 mA                 | 24-pin ceramic |  |  |

|                      | B-8  | 8 ns                 | -220 mA                 | flatpack       |  |  |

|                      | B-10 | 10 ns                | -                       |                |  |  |

|                      | B-15 | 15 ns                | •                       |                |  |  |

| μPB100474D-8<br>D-10 |      | 8 ns                 | -220 mA                 | 24-pin cerdip  |  |  |

|                      |      | 10 ns                | -                       |                |  |  |

|                      | D-15 | 15 ns                | •                       |                |  |  |

| μPB100474K-4.5       |      | 4.5 ns               | -450 mA                 | 24-pin ceramic |  |  |

|                      | K-6  | 6 ns                 |                         | LCC            |  |  |

## Pin Configurations

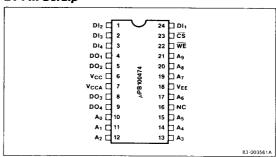

### 24-Pin Cerdip

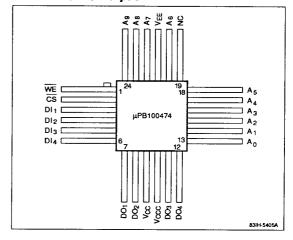

### 24-Pin Ceramic Flatpack

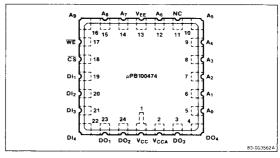

## 24-Pin Ceramic LCC

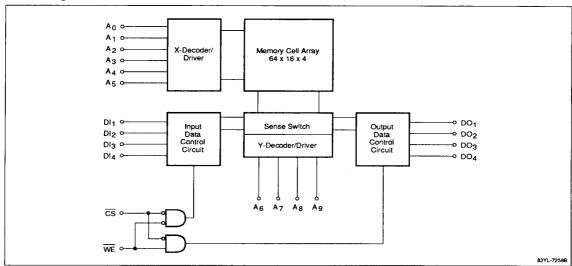

## **Block Diagram**

### Pin Identification

| Symbol                            | Function                                        |

|-----------------------------------|-------------------------------------------------|

| A <sub>0</sub> - A <sub>9</sub>   | Addresses                                       |

| DI <sub>1</sub> - DI <sub>4</sub> | Data inputs                                     |

| DO <sub>1</sub> - DO <sub>4</sub> | Data outputs                                    |

| WE                                | Write enable                                    |

| CS                                | Chip select                                     |

| Vcc                               | Power supply (current switches and bias driver) |

| VCCA                              | Power supply (output devices)                   |

| V <sub>EE</sub>                   | Power supply                                    |

| NC                                | No connection                                   |

## Capacitance

| Parameter          | Symbol | Min | Тур | Max | Unit |  |

|--------------------|--------|-----|-----|-----|------|--|

| Input capacitance  | CIN    | 4   |     |     | pF   |  |

| Output capacitance | Cout   |     | 5   |     | pF   |  |

## **Absolute Maximum Ratings**

| Supply voltage, VEE to VCC                              | -7.0 V to +0.5 |

|---------------------------------------------------------|----------------|

| Input voltage, V <sub>IN</sub>                          | +0.5 V to VEE  |

| Output current, I <sub>OUT</sub>                        | -30 mA to +0.1 |

| Storage temperature, T <sub>STG</sub>                   | -65 to +150 °C |

| Storage temperature under bias, T <sub>STG</sub> (Bias) | -55 to +125 °C |

Exposure to Absolute Maximum Ratings for extended periods may affect device reliability; exceeding the ratings could cause permanent damage. The device should be operated within the limits specified under DC and AC Characteristics.

## **Truth Table**

| cs | WE | DIN | Output | Function     |  |  |

|----|----|-----|--------|--------------|--|--|

| Н  | Х  | х   | L      | Not selected |  |  |

| L  | L  | L   | L      | Write 0      |  |  |

| L  | L  | Н   | L      | Write 1      |  |  |

| L  | н  | х   | Dout   | Read         |  |  |

#### Notes:

(1) X = don't care.

## **DC Characteristics**

$T_A = 0$  to +85°C;  $V_{EE} = -4.5$  V; output load = 50  $\Omega$  to -2.0 V

| Parameter                      | Symbol           | Min   | Тур | Max   | Unit | Test Conditions                                              |

|--------------------------------|------------------|-------|-----|-------|------|--------------------------------------------------------------|

| Output voltage, high           | V <sub>OH</sub>  | -1025 |     | 880   | mV   | V <sub>IN</sub> = V <sub>IH</sub> max or V <sub>IL</sub> min |

| Output voltage, low            | VoL              | -1810 |     | -1620 | mV   | V <sub>IN</sub> = V <sub>IH</sub> max or V <sub>IL</sub> min |

| Output threshold voltage, high | V <sub>OHC</sub> | -1035 |     |       | mV   | V <sub>IN</sub> = V <sub>IH</sub> min or V <sub>IL</sub> max |

| Output threshold voltage, low  | V <sub>OLC</sub> |       |     | -1610 | mV   | V <sub>IN</sub> = V <sub>IH</sub> min or V <sub>IL</sub> max |

| Input voltage, high            | V <sub>IH</sub>  | -1165 |     | -880  | mV   | Guaranteed input voltage high for all inputs                 |

| Input voltage, low             | V <sub>IL</sub>  | -1810 |     | -1475 | mV   | Guaranteed input voltage low for all inputs                  |

| Input current, high            | liH              |       |     | 220   | μΑ   | V <sub>IN</sub> = V <sub>IH</sub> max                        |

| Input current, low             | ljL              | 0.5   |     | 170   | μΑ   | For CS: V <sub>IN</sub> = V <sub>IL</sub> min                |

|                                |                  | -50   |     |       | μΑ   | For all others: V <sub>IN</sub> = V <sub>IL</sub> min        |

| Supply current                 | EE               | -220  |     |       | mA   | t <sub>AA</sub> = 8/10/15 ns; all inputs and outputs open    |

|                                |                  | -450  |     |       | mA   | $t_{AA} = 4.5/6$ ns; all inputs and outputs open (Note 2     |

#### Notes:

- (1) The device under test is mounted in a test socket and is measured at a thermal equilibrium established with a transverse air flow maintained at greater than 2.0 ms.

- (2) For the μPB100474-4.5/-6, take measures to reduce the thermal resistance and to keep the junction temperature less than 90 °C. Forced air and appropriate fins on the substrate on which the package is mounted, or on the package itself, are recommended. The thermal resistance of the junction to the case (bottom side) of an LCC or flatpack package is less than 10°C/W.

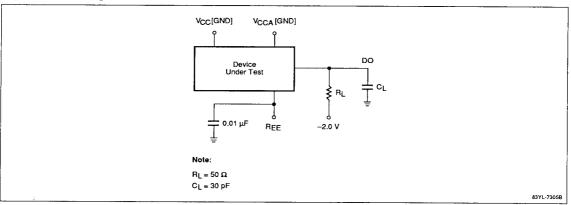

Figure 1. Loading Conditions Test Circuit

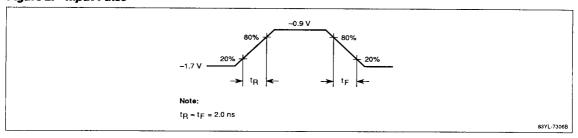

Figure 2. Input Pulse

26C-3

### **AC Characteristics**

$T_A = 0 \text{ to } +85^{\circ}\text{C}; V_{EE} = -4.5 \text{ V } \pm 5\%$

|                           | Symbol           | μPB100474-4.5 |     | μPB100474-6 |     | μPB100474-8 |     | μPB100474-10 |     | μPB100474-15 |     |      |

|---------------------------|------------------|---------------|-----|-------------|-----|-------------|-----|--------------|-----|--------------|-----|------|

| Parameter                 |                  | Min           | Max | Min         | Max | Min         | Max | Min          | Max | Min          | Max | Unit |

| Read Operation            |                  |               |     |             |     |             |     |              |     |              |     |      |

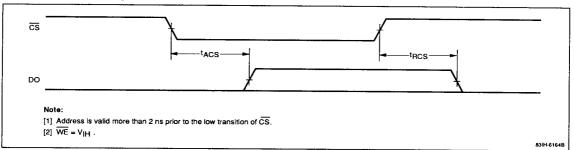

| Chip select access time   | t <sub>ACS</sub> |               | 4   |             | 4   |             | 5   |              | 6   |              | 8   | ns   |

| Chip select recovery time | tRCS             |               | 4   |             | 4   |             | 5   |              | 6   |              | 8   | ns   |

| Address access time       | t <sub>AA</sub>  |               | 4.5 |             | 6   |             | 8   |              | 10  |              | 15  | ns   |

| Write Operation           |                  |               |     |             |     |             |     |              |     |              |     |      |

| Write pulse width         | t <sub>W</sub>   | 4.5           |     | 6           |     | 6           |     | 10           |     | 15           |     | ns   |

| Data setup time           | twsp             | 1             |     | 1           |     | 1           |     | 2            |     | 2            |     | ns   |

| Data hold time            | twHD             | 1             |     | 1           |     | 1           |     | 2            |     | 2            |     | ns   |

| Address setup time        | twsa             | 1             |     | 1           |     | 1           |     | 3            |     | 3            |     | ns   |

| Address hold time         | twha             | 2             |     | 2           |     | 1           |     | 2            |     | 2            |     | ns   |

| Chip select setup time    | twscs            | 1             |     | 1           |     | 1           |     | 2            |     | 2            | -   | ns   |

| Chip select hold time     | twncs            | 1             |     | 1           |     | 1           |     | 2            |     | 2            |     | ns   |

| Write disable time        | tws              |               | 4   |             | 4   |             | 5   |              | 6   |              | 8   | ns   |

| Write recovery time       | twn              |               | 4.5 |             | 6   |             | 8   |              | 10  |              | 10  | ns   |

#### Notes:

- (1) The device under test is mounted in a test socket and is measured at a thermal equilibrium established with a transverse air flow maintained at greater than 2.0 m/sec.

- (2) For the µPB100474-4.5/-6, take measures to reduce the thermal resistance and to keep the junction temperature less than 90°C. Forced air and appropriate fins on the substrate on which the package is mounted, or on the package itself, are recommended. The thermal resistance of the junction to the case (bottom side) of an LCC or flatpack package is less than 10°C/W.

- (3) See figures 1 and 2 for loading conditions and input pulse timing. For the μPB100474-4.5/-6, C<sub>L</sub> = 5 pF. For the μPB100474-8/10/15, C<sub>L</sub> = 30 pF.

- (4) Output rise and fall times = 2 ns (typ).

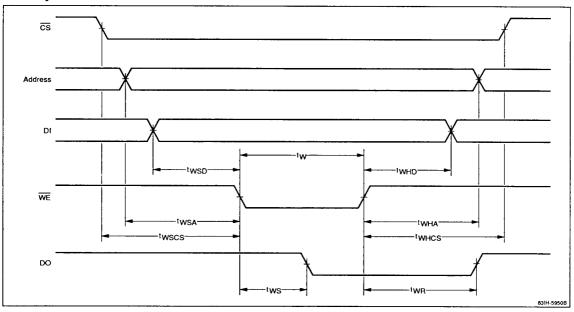

## **Timing Waveforms**

## Chip Select Access Cycle

26c

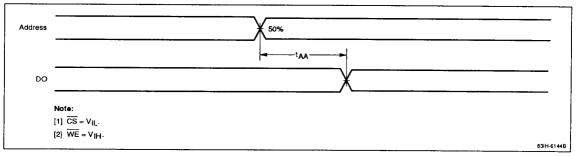

## Address Access Cycle

# Timing Waveforms (cont)

# Write Cycle