# MG3500/MG2580 HD H.264 CODEC DATA SHEET Advance Information

July 23, 2010 Document Release 1.4 Document Number: PN1100

Maxim Integrated Products 120 San Gabriel Drive Sunnyvale, CA 94086 United States 408-737-7600 http://www.maxim-ic.com/support

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642 or visit Maxim's website at www.maxim-ic.com.

Copyright © 2010 Maxim Integrated Products

This document contains advanced information and is subject to change without prior notice. Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. Maxim retains the right to make changes to its products or specifications to improve performance, reliability or manufactur-ability. All information in this document, including descriptions of features, functions, performance, technical specifications and availability, is subject to change without notice at any time. While the information furnished herein is held to be accurate and reliable, no responsibility will be assumed by Maxim for its use. Furthermore, the information contained herein does not convey to the purchaser of microelectronic devices any license under the patent right of any manufacturer.

Maxim products are not intended for use in life support products where failure of a Maxim product could reasonably be expected to result in death or personal injury. Anyone using a Maxim product in such an application without express written consent of an officer of Maxim does so at their own risk, and agrees to fully indemnify Maxim for any damages that may result from such use or sale.

# **MAXIM** is a registered trademark of Maxim Integrated Products, Inc.

All other products or service names used in this publication are for identification purposes only, and may be trademarks or registered

trademarks of their respective companies. All other trademarks or registered trademarks mentioned herein are the property of their

respective holders.

| 1.0: Description                                 | 13             |

|--------------------------------------------------|----------------|

| 1.1: Hardware Overview                           | 14             |

| 1.2: Support Tools                               | 18             |

| 2.0: Device Overview, Pin Assignments            | 21             |

| 2.1: Naming Conventions                          | 21             |

| 2.2: Pinout Diagrams                             | 22             |

| 2.3: Pin Descriptions (by Interface)             | 27             |

| 2.4: Power and Ground Pins                       | 52             |

| 2.5: Pin List by Power Group                     | 55             |

| 2.6: Hookup Recommendations when Interfaces A    |                |

| Unused 57                                        |                |

| 3.0: Device Configuration                        | 67             |

| 3.1: Reset                                       | 67             |

| 3.2: Boot modes for the MMEs and the ARM         | 67             |

| 3.3: Firmware Loader                             | 68             |

| 3.4: API Configuration                           | 68             |

| 3.5: Pin Multiplexing, GPIOs, etc.               | 68             |

| 3.6: Debug Mode                                  | 68             |

| 3.7: JTAG ID Register                            | 68             |

| 4.0: Device Operating Conditions                 | 71             |

| 4.1: Absolute Maximum Ratings                    | 71             |

| 4.2: Recommended Operation Conditions            | 71             |

| 4.3: Essential Characteristics                   | 72             |

| 4.4: Power Supply Currents for the Different Pow |                |

| Domains73                                        | CI             |

| 4.5: AC Timing                                   | 73             |

| 5.0: Block Level Operation                       | 97             |

| 5.1: Detailed Block Diagram                      | 97             |

| 5.2: Reset Logic                                 | 98             |

| 5.3: Clocks and PLLs                             | 99             |

| 5.4: Video Interfaces                            | 103            |

| 5.5: Video Scaling                               | 111            |

| 5.6: Audio Interfaces                            | 118            |

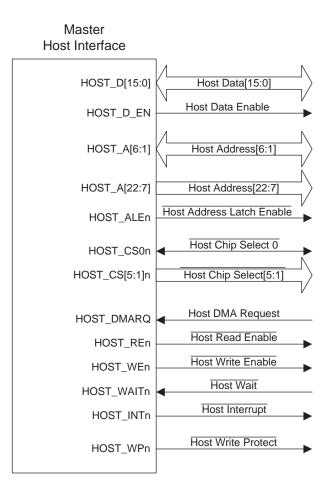

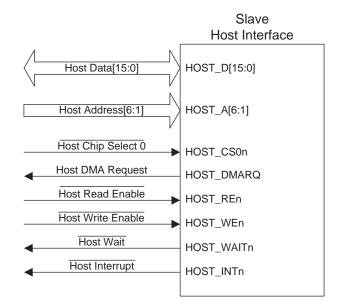

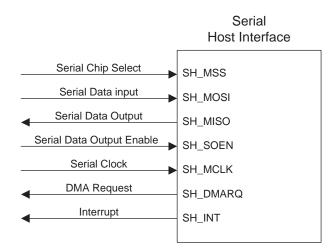

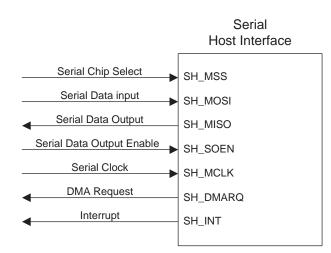

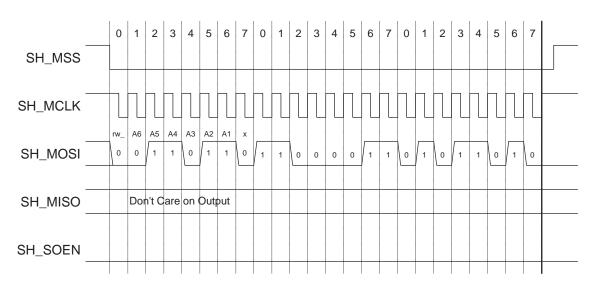

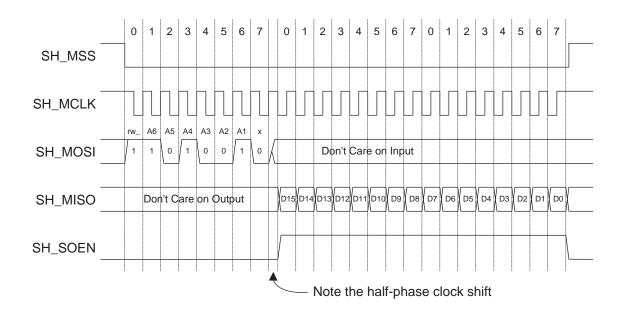

| 5.7: Host Interfaces                             | 120            |

| 5.8: Configuration and Status Register (CSR) Def |                |

| tion 132                                         | 1111           |

| 5.9: DMA Engine Register Definition              | 136            |

| 5.10: Bitstream Write Register Definition        | 144            |

| 5.11: Special Registers                          | 145            |

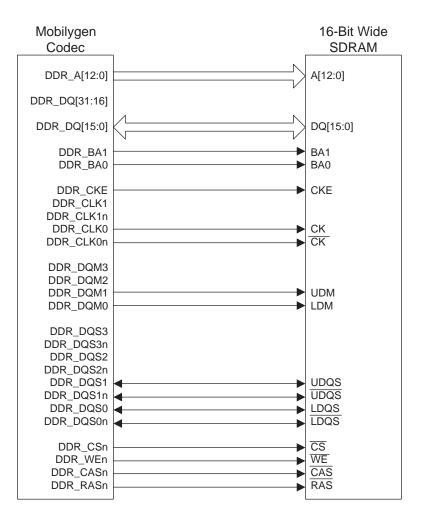

| 5.12: Memory Interfaces                          | 152            |

| 5.13: Serial Interfaces                          | 167            |

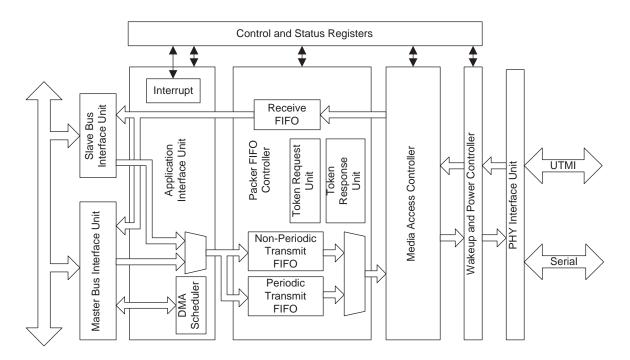

| 5.14: USB 2.0 On-the-Go Interface                | 178            |

| 5.15: Ethernet Media Access Controller           | 184            |

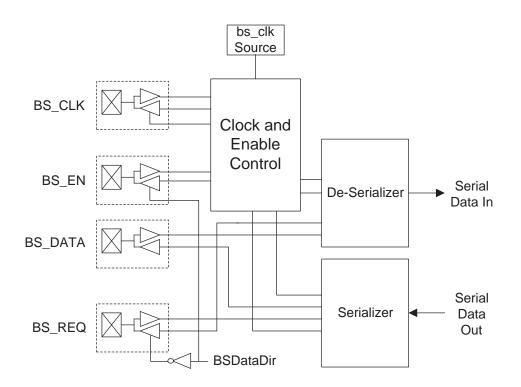

| 5.16: High-Speed Bitstreams                      | 184            |

| 6.0: System Design and Applications              | <b>193</b>     |

| 6.1: Power Supply Design and Recommendations     |                |

| 6.2: Power Supply Sequencing                     | 193            |

| 6.3: Reset timing Diagrams                       | 193            |

| 6.4: Oscillator Connections, Values and Formulas |                |

| 7.0: Ordering Information                        | <b>194 197</b> |

| 7.1: Product Information                         | 197            |

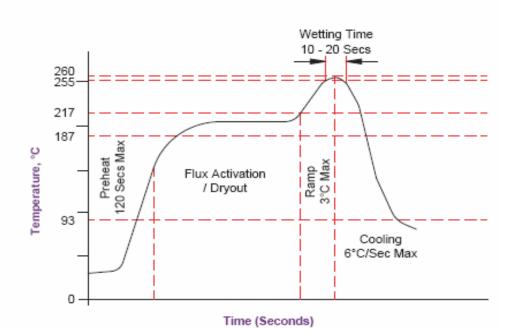

| 7.1: MG3500 Family Reflow Profile                | 197            |

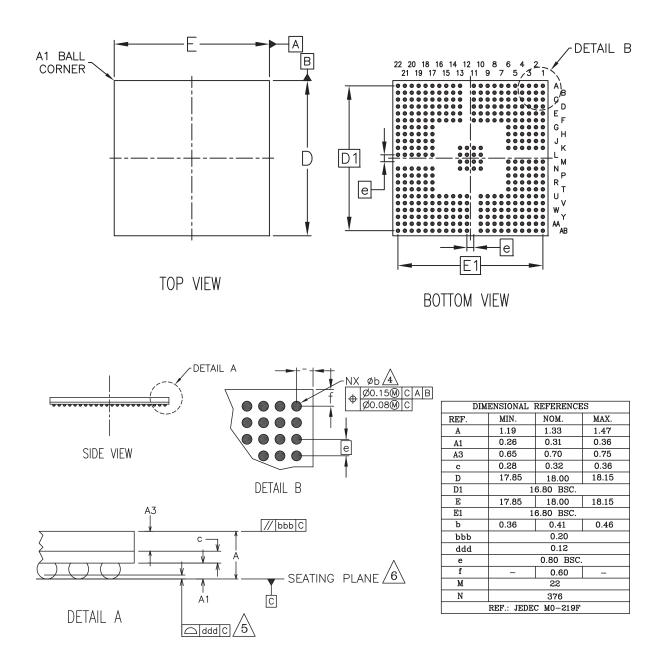

| 8.0: Packaging Information                       | 198<br>201     |

| 8.1: Package Diagram                             | 201            |

| U.I. I denage Diagram                            | <i>2</i> 01    |

| 8.2: Thermal Data |

|-------------------|

| 9.0: Marking      |

# Change Log

This section of the data sheet lists the changes that have occurred since the last release. Customers should be aware that not all releases are public, and therefore they might see gaps in the release numbering system.

| Revision | Page     | Section   | Change                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |  |

|----------|----------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| 0.18     | 71       | 4.1       | The Core power supply current was changed from 1000 mA. typical to 1000 mA. maximum.                                                                                                                                                    |  |  |  |  |  |  |  |  |  |

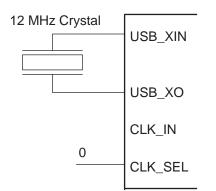

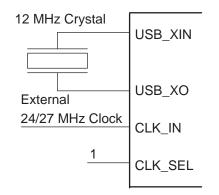

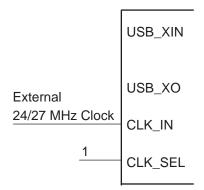

| 0.16     | 195      | 6.4.3     | A new section was added describing use when only an external clock is used.                                                                                                                                                             |  |  |  |  |  |  |  |  |  |

|          | 43       | 2.3.8     | Specified the resistance of the external USB Bias Current resistor.                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |

|          | 43       | 2.3.9     | Modified the timing specification for the SD and MMC Interface.                                                                                                                                                                         |  |  |  |  |  |  |  |  |  |

|          | 46       | 2.3.14    | Specified the resistance of the internal pull-up and pull-down resistors                                                                                                                                                                |  |  |  |  |  |  |  |  |  |

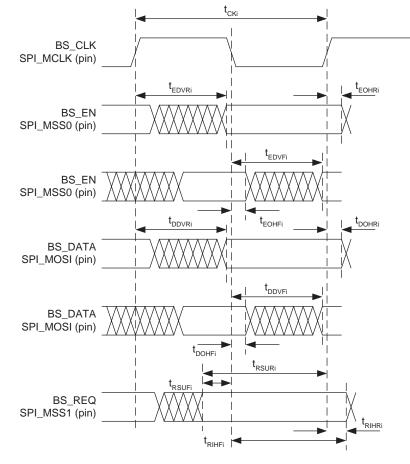

|          | 89       | 4.5.6     | Added a new section showing the bitstream timing.                                                                                                                                                                                       |  |  |  |  |  |  |  |  |  |

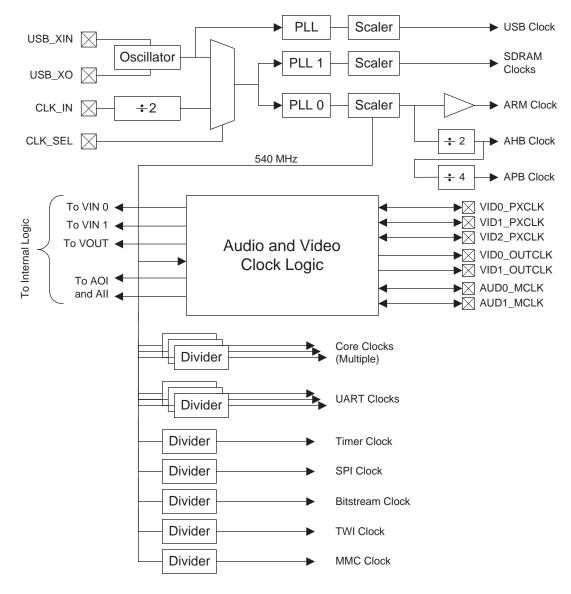

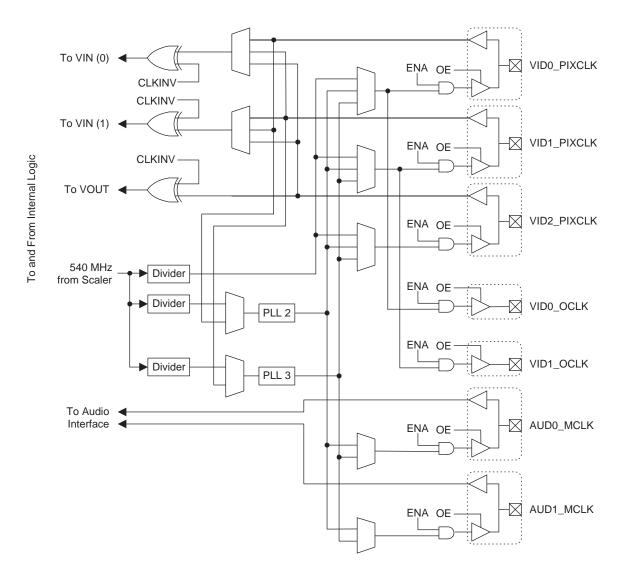

| 0.19     | 99       | 5.3       | This entire section was re-written to clarify the clock structure.                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |

| 0.19     | 111      | 5.5       | The definition of the VOUT register was altered.                                                                                                                                                                                        |  |  |  |  |  |  |  |  |  |

|          | 145      | 5.11      | The specification for the ChipID register was added.                                                                                                                                                                                    |  |  |  |  |  |  |  |  |  |

|          | 152      | 5.12      | The SDRAM Requirements for Various Profiles table was updated.                                                                                                                                                                          |  |  |  |  |  |  |  |  |  |

|          | 184      | 5.15      | Added note regarding the use of an external switch.                                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |

|          | 190      | 5.16.5    | Updated the Bitstream Register section.                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |  |

| 0.20     | Т        | hroughout | Made minor changes throughout the book.                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |  |

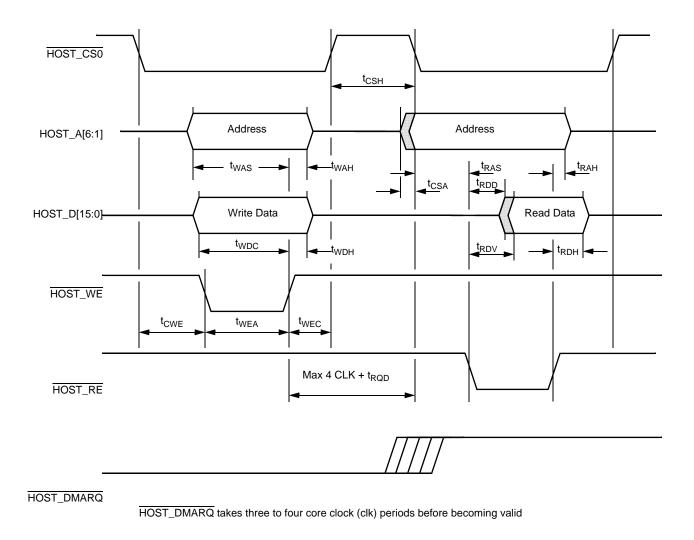

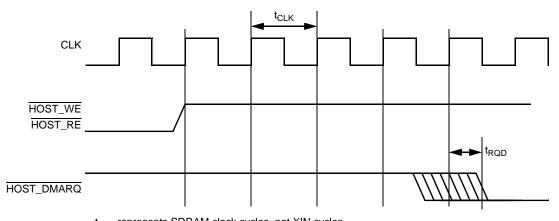

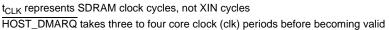

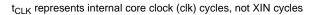

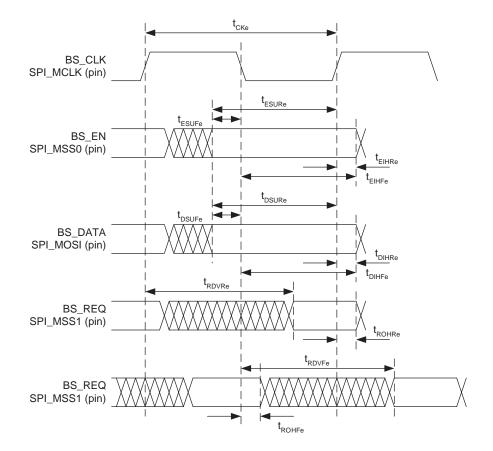

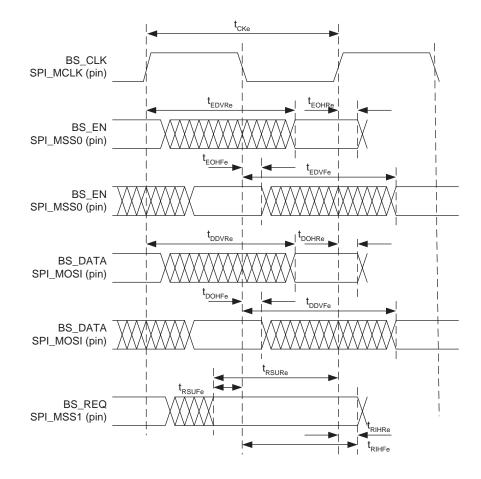

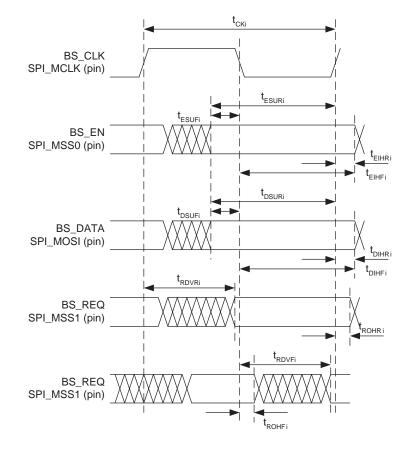

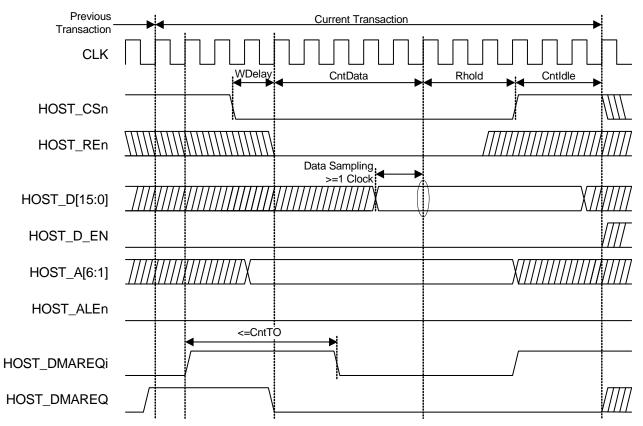

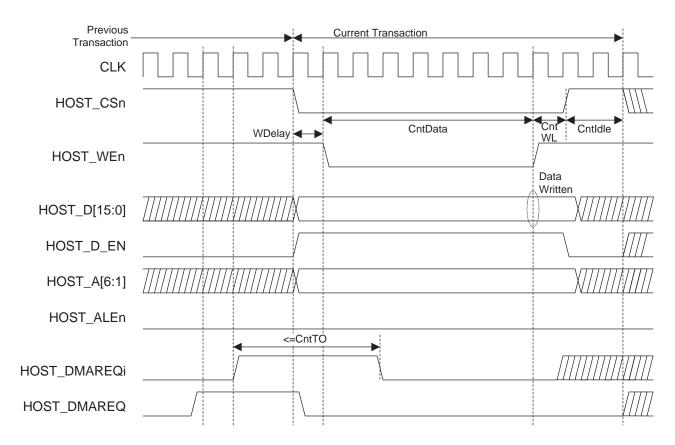

|          | 120      | 5.7.1     | Added timing diagrams showing Master Host Interface (MHIF) access timing.                                                                                                                                                               |  |  |  |  |  |  |  |  |  |

| 0.21     | Т        | hroughout | Valid value for EWait of EM1Config is 1; EM1Cmd register set to 0x00; removal of several reg-<br>isters, Slave Host Interface; Valid value for EM1 is 0; Corrections to S/PDIF and I2S I/Os; BFi-<br>fostatus changed to EM1fifostatus. |  |  |  |  |  |  |  |  |  |

| 1.0      | 14       | 1.1.2     | The heading title and description has been changed.                                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |

|          | 15       | 1.1.2     | Figure 1-2, only one independent video output is supported.                                                                                                                                                                             |  |  |  |  |  |  |  |  |  |

|          | 16 1.1.3 |           | The maximum pixel rate that VIP can process corresponds to the video input of resolution 1920x1080i at 30 frames per seconds.                                                                                                           |  |  |  |  |  |  |  |  |  |

|          | Т        | hroughout | Made editorial changes, added definitions, made updates and corrections to several diagrams and tables throughout the book.                                                                                                             |  |  |  |  |  |  |  |  |  |

| Revision | Page | Section | Change                                                                                                                                                                                                      |

|----------|------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1      | 71   | 4.1     | The core supply voltage has been changed to $1.05v \pm 5\%$ .                                                                                                                                               |

|          | 71   | 4.2     | The minimum, typical, and maximum ranges of the core supply voltage have been re-adjusted.                                                                                                                  |

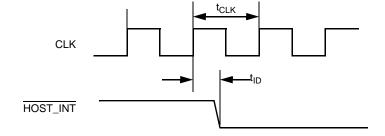

| l        | 78   | 4.5.2   | Modified the Video Interface Timing Diagram to incorporate the new t <sub>VCQ</sub> parameter.                                                                                                              |

|          | 78   | 4.5.2   | Modified Table 4-7 to indicate that VIDOUT_DATA is an output delay from VID_CLK for the standard definition video interface AC timing values. It also specifies the minimum and maximum timing value in ns. |

| l        | 78   | 4.5.2   | Modified Table 4-8 to indicate that VIDOUT_DATA is an output delay from VID_CLK for the high definition video interface AC timing values. It also specifies the minimum and maximum timing value in ns.     |

| l        | 78   | 4.5.2   | Modified Table 4-9 to indicate that VIDOUT_DATA is an output delay from VID_CLK for the high-speed video interface AC timing values. It also specifies the minimum and maximum timing value in ns.          |

| l        | 144  | 5.10    | Made corrections to the bit settings of the BiFiStatus and BiFiConfig registers.                                                                                                                            |

|          | 188  | 5.16.1  | Changed the description for the bitstream interface.                                                                                                                                                        |

| l        | 190  | 5.16.5  | Removed the old section "High-Speed Bitstream" since it is not supported.                                                                                                                                   |

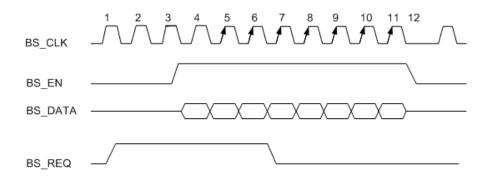

| l        | 189  | 5.16.4  | Modified Figure 5-39 to show signal BS-DATA is 8 bits long.                                                                                                                                                 |

| l        |      |         | Changed the definition for Cycle 7 of the waveform diagram.                                                                                                                                                 |

| l        | 189  | 5.16.4  | Changed the definition for Cycle 7 of the waveform diagram.                                                                                                                                                 |

| 1        | 190  | 5.16.5  | In Bitstream Control 2, removed the unsupported value 1 for BSClkEnMode, BSStopCond, and BSStrobeModeEn signals.                                                                                            |

| l        | 190  | 5.16.5  | Bitstream Interface Control registers 8, A, and C have been removed.                                                                                                                                        |

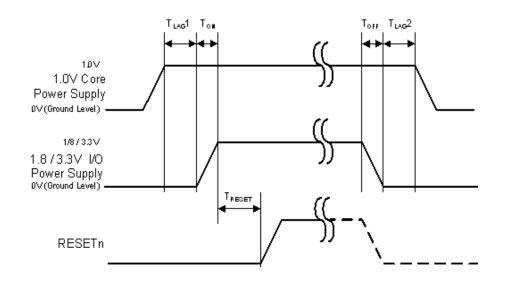

| l        | 193  | 6.2     | The second half of the RESETn signal in Figure 6-1has been removed.                                                                                                                                         |

| l        | 201  | 8.0     | Added a new Ordering Information section.                                                                                                                                                                   |

| 1.2      | 14   | 1.1     | Added Hardware Description section back.                                                                                                                                                                    |

| l        | 78   | 4.5.2   | Corrected the note below Table 4-7 to say the clock should be supplied by MG3500.                                                                                                                           |

| l        | 78   | 4.5.2   | Re-adjusted the t <sub>VCQ</sub> parameter in Figure 4-5.                                                                                                                                                   |

| l        | 78   | 4.5.2   | Re-adjusted the t <sub>VIH</sub> parameter in Figure 4-5.                                                                                                                                                   |

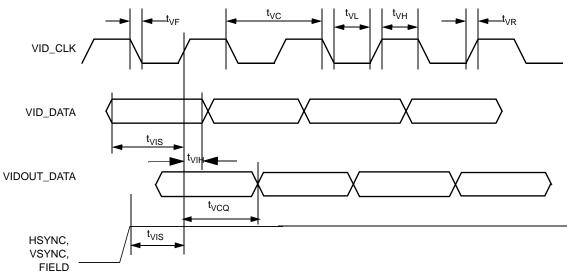

| l        | 81   | 4.5.3   | Inverted the AUD_LRCK signal in Figure 4-6.                                                                                                                                                                 |

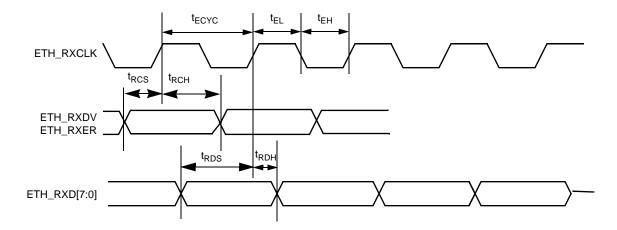

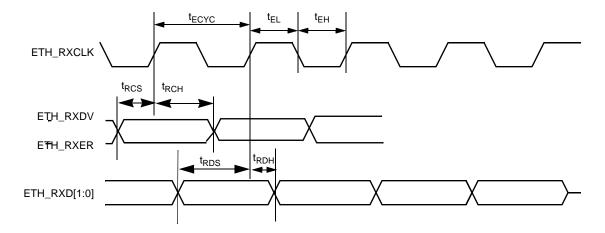

| l        | 81   | 4.5.3   | Re-adjusted the shaded area for ETH_RXDV and ETH_RXER signals in Figure 4-10.                                                                                                                               |

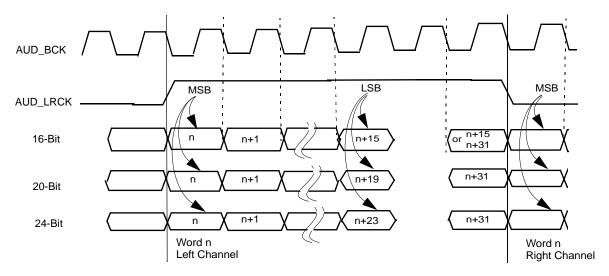

| l        | 81   | 4.5.3   | Modified the description for Figure 4-7.                                                                                                                                                                    |

| l        | 81   | 4.5.2   | Completely re-drew Figure 4-7.                                                                                                                                                                              |

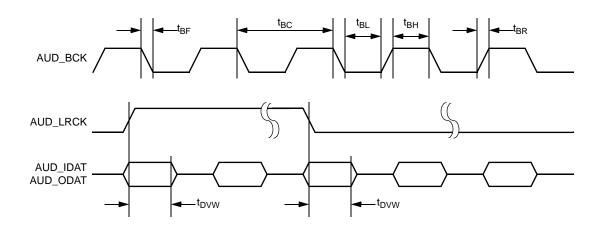

| l        | 84   | 4.5.4   | The ETH_TXD signal was corrected to ETH_RXD in Table 4-12.                                                                                                                                                  |

| l        | 84   | 4.5.4   | Changed the description for t <sub>ETH</sub> to indicate a clock High time in Table 4-12.                                                                                                                   |

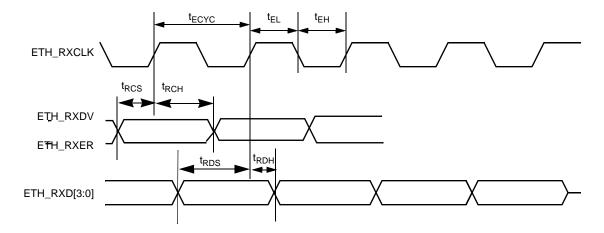

| l        | 86   | 4.5.4   | Changed signals ETH_RXDV and ETH_RXER in Table 4-14.                                                                                                                                                        |

| 1        | 86   | 4.5.4   | Changed the description for t <sub>ETH</sub> to indicate a clock High time in Table 4-14.                                                                                                                   |

| l        | 88   | 4.5.4   | Changed signals ETH_RXDV and ETH_RXER in Table 4-16.                                                                                                                                                        |

| 1        | 88   | 4.5.4   | Changed the ETH_RXDV signal in Table 4-16.                                                                                                                                                                  |

| 1        | 81   | 4.5.3   | Re-adjusted the shaded area for ETH_RXDV and ETH_RXER signals in Figure 4-14.                                                                                                                               |

|          | 203  | 9.0     | Removed the approval table from the Marking section.                                                                                                                                                        |

|          | 197  | 7.1.3   | Changed the maximum height.                                                                                                                                                                                 |

| Revision | Page | Section        | ection Change                                                                                                                                              |  |  |  |  |  |  |  |  |  |

|----------|------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| 1.3      | 11   | "SoC Features" | Separated Definitions of output ports for Audio Codecs and Decoders.                                                                                       |  |  |  |  |  |  |  |  |  |

|          | 11   | "SoC Features" | Changed SDRAM voltage for DDR_VDD.                                                                                                                         |  |  |  |  |  |  |  |  |  |

|          | 13   | 1.0            | Changed the description to provide a summary of both MG3500 and MG2580.                                                                                    |  |  |  |  |  |  |  |  |  |

|          | 13   | 1.0            | Changed Table 1-1 to specify the features of both MG3500 and MG2580.                                                                                       |  |  |  |  |  |  |  |  |  |

|          | 13   | 1.0            | Added the slave mode support for MG2580 in Table 1-1.                                                                                                      |  |  |  |  |  |  |  |  |  |

|          | 14   | 1.1.1          | Added the total number of macroblocks required for the H.264 Codec.                                                                                        |  |  |  |  |  |  |  |  |  |

|          | 14   | 1.1.2          | Changed the description for video processors and interfaces for clarity.                                                                                   |  |  |  |  |  |  |  |  |  |

|          | 15   | 1.1.2          | Added a note following the text describing Figure 1-2 to indicate that video composition fea-<br>tures are not available when two VIPs are used as inputs. |  |  |  |  |  |  |  |  |  |

|          | 15   | 1.1.2          | Added a column to Table 1-2 that shows video modes for the video composition.                                                                              |  |  |  |  |  |  |  |  |  |

|          | 16   | 1.1.4          | Added a note to indicate the supported formats for video output processor.                                                                                 |  |  |  |  |  |  |  |  |  |

|          | 16   | 1.1.7          | Modified the description for valid input and outputs for audio interfaces.                                                                                 |  |  |  |  |  |  |  |  |  |

|          | 17   | 1.1.12         | Removed IDE from the list of external devices that can communicate with the host interface.                                                                |  |  |  |  |  |  |  |  |  |

|          | 18   | 1.2            | Removed the evaluation applications and demonstration product applications supplied by Mo-<br>bilygen.                                                     |  |  |  |  |  |  |  |  |  |

|          | 19   | 1.2            | Changed the middle box at the bottom of Figure 1-4 to say Mobilygen Software.                                                                              |  |  |  |  |  |  |  |  |  |

|          | 31   | 2.3.3          | Added pin descriptions for MG2580 to Table 2-4.                                                                                                            |  |  |  |  |  |  |  |  |  |

|          | 46   | 2.3.14         | Indicated in Table 2-17 that GPIO_2-12, -13, and -15 are not applicable for MG2580.                                                                        |  |  |  |  |  |  |  |  |  |

|          | 57   | 2.6            | Indicated in Table 2-24 that VID23_MISO, _MOSI, and _MSS are not available for MG2580 for VIDEO_PORT 2/3.                                                  |  |  |  |  |  |  |  |  |  |

|          | 57   | 2.6            | Removed the descriptions for the USB and Ethernet pin names in Table 2-24.                                                                                 |  |  |  |  |  |  |  |  |  |

|          | 57   | 2.6            | Specified that USB_ADD is recommended for USB_REXT in Table 2-24.                                                                                          |  |  |  |  |  |  |  |  |  |

|          | 57   | 2.6            | Added a footnote to Table 2-24 that recommends a two-step procedure on how to connect the USB pins when the USB block is not used on MG3500.               |  |  |  |  |  |  |  |  |  |

|          | 71   | 4.0            | Changed the range for the DDR_VDD IO voltage in Table 4-2.                                                                                                 |  |  |  |  |  |  |  |  |  |

|          | 71   | 4.0            | Changed the operating conditions range for DDR_VREF in Table 4-2.                                                                                          |  |  |  |  |  |  |  |  |  |

|          | 86   | 4.5.4          | Changed ETH_RXER[3:0] to ETH_RXD[3:0] in Figure 4-12.                                                                                                      |  |  |  |  |  |  |  |  |  |

|          | 88   | 4.5.4          | Changed ETH_RXER[1:0] to ETH_RXD[1:0] in Figure 4-14.                                                                                                      |  |  |  |  |  |  |  |  |  |

|          | 125  | 5.7.1          | Specified the bit range for AddrInc and WEn in the "DevConfigAn Register" table.                                                                           |  |  |  |  |  |  |  |  |  |

|          | 126  | 5.7.1          | Specified the bit range for RHold in the "DevConfigBn Register" table.                                                                                     |  |  |  |  |  |  |  |  |  |

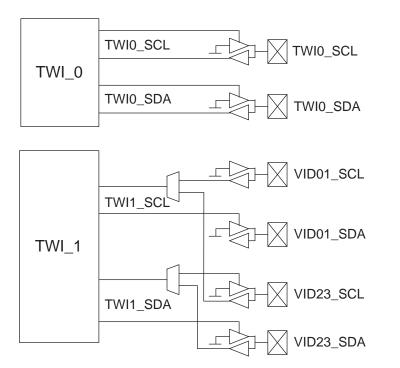

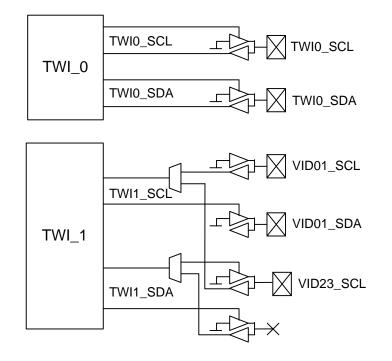

|          | 168  | 5.13.3         | Added a new section to describe TWI on MG2580. This includes description as well as a new diagram, Figure 5-33.                                            |  |  |  |  |  |  |  |  |  |

|          | 169  | 5.13.2         | Changed Figure 5-33 to show that VID23_SDA is not applicable to MG2580.                                                                                    |  |  |  |  |  |  |  |  |  |

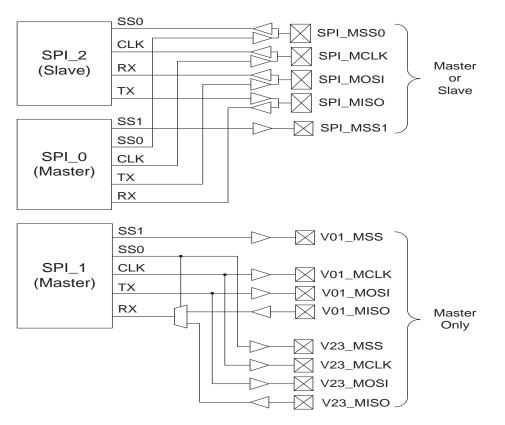

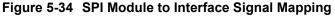

|          | 170  | 5.13.4         | Indicated that this section is about SPI on MG3500. Added a note to imply that V23 SPI port is not available on MG2580.                                    |  |  |  |  |  |  |  |  |  |

|          | 171  | 5.13.5         | Changed Figure 5-35 to show that VID23_MSS, VID23_MCLK, VID23_MOSI, and VID23_MISO are not applicable to MG2580.                                           |  |  |  |  |  |  |  |  |  |

|          | 171  | 5.13.5         | Added a new section for SPI on MG2580. This includes descriptions as well as a modified diagram, Figure 5-35.                                              |  |  |  |  |  |  |  |  |  |

|          | 173  | 5.13.8         | Indicated in the Serial I/O Control table that V23_MCLK_AltSeL and V23_MOSI_AltSeL are not available on MG2580.                                            |  |  |  |  |  |  |  |  |  |

|          | 173  | 5.13.8         | Indicated in the GPIO 2 Sel that table GPIO_2_12, GPIO_2_13, and GPIO_2_15 fields will have no effect on MG2580 since GPIO pins are not connected.         |  |  |  |  |  |  |  |  |  |

|          | 173  | 5.13.8         | Indicated in the GPIO 2 Pull-up Enable table GPIO_2_12, GPIO_2_13, and GPIO_2_15 fields will have no effect on MG2580 since GPIO pins are not connected.   |  |  |  |  |  |  |  |  |  |

|          | 173  | 5.13.8         | Indicated in the GPIO 2 Pull-up Enable table GPIO_2_12, GPIO_2_13, and GPIO_2_15 fields will have no effect on MG2580 since GPIO pins are not connected.   |  |  |  |  |  |  |  |  |  |

|          | 197  | 7.1.3          | Removed the part number to order MG2580A2 since this part will no longer be built.                                                                         |  |  |  |  |  |  |  |  |  |

| Revision | Page        | Section | Change                                                                                                                                                                                                                                                                                          |

|----------|-------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.4      | 29/30       | 2.3.2   | Changed VID0_PIXCLK and VID1_PIXCLK to IO                                                                                                                                                                                                                                                       |

|          | 40          | 2.3.6   | Added a note for DDR_DQ[31:16] and DDR_DQM[3:] pins are not connected in 16-bit mode                                                                                                                                                                                                            |

|          | 46          | 2.3.14  | Removed alternate functionality for GPIO_6 and GPIO_7                                                                                                                                                                                                                                           |

|          | 56          | 2.5     | Removed signal USB_VBUS from 3.3V Power Group                                                                                                                                                                                                                                                   |

|          | 71          | 4.2     | Updated ETH_VDD 3.3V +/- 5%                                                                                                                                                                                                                                                                     |

|          | 78          | 4.5.2   | Included tVH(min) and tVH(max) in Table 4-7, Table 4-8 and Table 4-9                                                                                                                                                                                                                            |

|          |             |         | Added HSYNC, VSYNC, and FRAME signals to the timing diagram. Clarified Setup and Hold time description with reference to VID_CLK for VID_DATA and VIDOUT_DATA.                                                                                                                                  |

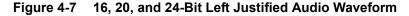

|          | 81          | 4.5.3   | Updated figure 4-6 as it was not readable in v1.3                                                                                                                                                                                                                                               |

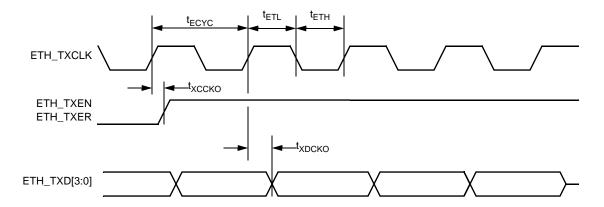

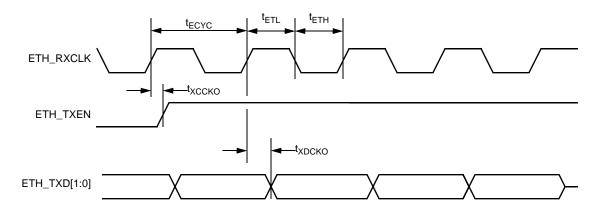

|          | 87/88       | 4.5.4   | Updated RMII Transmit/Receive Timing Diagram in Figure 4-13 by replacing TXCLK with RX-<br>CLK. Updated Tables 4-15 accordingly by removing transmit and replacing it with receive<br>clock Changed Min. and Max. values in Table 4-16 for ECYC-ETH_CLK, ETL- Low and ETH-<br>High Time signal. |

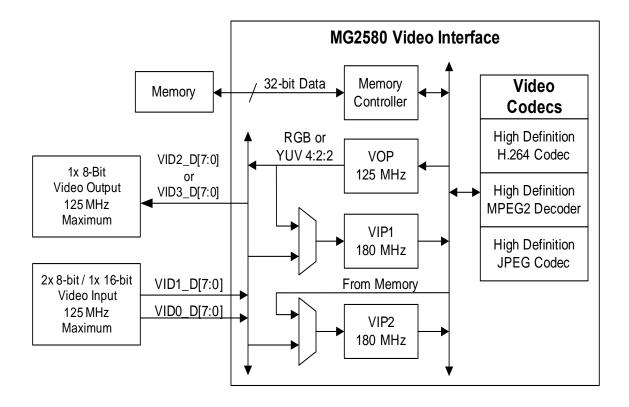

|          | 103/<br>104 | 5.4     | Included separate block diagrams for MG3500 and MG2580 video paths                                                                                                                                                                                                                              |

|          | 165         | 5.12.5  | Removed 512 byte page size under NAND flash bulleted item                                                                                                                                                                                                                                       |

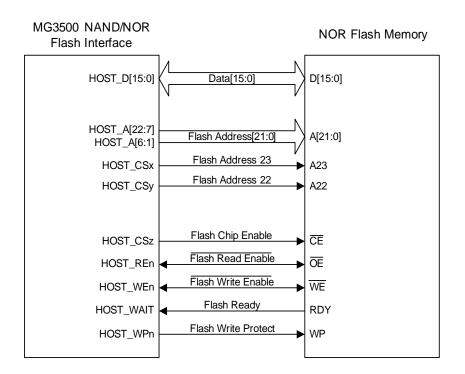

|          | 166         | 5.12.5  | Updated NAND/NOR Flash Interface connected to NOR Flash Memory Figure 5-30                                                                                                                                                                                                                      |

| Old Name   | New Name   | Old Name  | New Name | Old Name    | New Nam     |

|------------|------------|-----------|----------|-------------|-------------|

| ENET_COL   | ETH_COL    | HOST_A08  | HOST_A8  | DDR_D27     | DDR_DQ27    |

| ENET_RXD1  | ETH_RXD1   | HOST_A05  | HOST_A5  | DDR_D31     | DDR_DQ31    |

| ENET_RXERR | ETH_RXERR  | HOST_A06  | HOST_A6  | DDR_D29     | DDR_DQ29    |

| ENET_RXDV  | ETH_RXDV   | CF_WAITn  | CF_WAITn | DDR_D30     | DDR_DQ30    |

| ENET_CRS   | ETH_CRS    | HOST_A02  | HOST_A2  | DDR_D28     | DDR_DQ28    |

| ENET_RXCLK | ETH_RXCLK  | HOST_A09  | HOST_A9  | DDR_D24     | DDR_DQ24    |

| ENET_RXD0  | ETH_RXD0   | HOST_A07  | HOST_A7  | DDR_D26     | DDR_DQ26    |

| ENET_RXD2  | ETH_RXD2   | HOST_A03  | HOST_A3  | DDR_D23     | DDR_DQ23    |

| ENET_RXD7  | ETH_RXD7   | HOST_A04  | HOST_A4  | DDR_D21     | DDR_DQ21    |

| ENET_MDCLK | ETH_MDCLK  | HOST_A01  | HOST_A1  | DDR_D22     | DDR_DQ22    |

| ENET_RXD3  | ETH_RXD3   | DDR_A03   | DDR_A3   | DDR_D19     | DDR_DQ19    |

| ENET_MDIO  | ETH_MDIO   | DDR_A02   | DDR_A2   | DDR_D20     | DDR_DQ20    |

| ENET_RXD6  | ETH_RXD6   | DDR_A01   | DDR_A1   | DDR_D16     | DDR_DQ16    |

| ENET_RXD4  | ETH_RXD4   | DDR_A00   | DDR_A0   | DDR_D17     | DDR_DQ17    |

| ENET_TXD0  | ETH_TXD0   | DDR_A08   | DDR_A8   | DDR_D18     | DDR_DQ18    |

| ENET_RXD5  | ETH_RXD5   | DDR_A04   | DDR_A4   | JTAG_TEST   | TEST        |

| ENET_TXD2  | ETH_TXD2   | DDR_A07   | DDR_A7   | RESETn      | RESETn      |

| ENET_TXD4  | ETH_TXD4   | DDR_A06   | DDR_A6   | JTAG_T_SELL | JTAG_TAP_S  |

| ENET_TXEN  | ETH_TXEN   | DDR_A09   | DDR_A9   | VID1_OCLK   | VID1_OUTCL  |

| ENET_TXD3  | ETH_TXD3   | DDR_D05   | DDR_DQ5  | VID1_PXCLK  | VID1_PIXCLK |

| ENET_TXD5  | ETH_TXD5   | DDR_D00   | DDR_DQ0  | VID0_OCLK   | VID0_OUTCL  |

| ENET_TXERR | ETH_TXER   | DDR_D07   | DDR_DQ7  | VID0_PXCLK  | VID0_PIXCLK |

| ENET_TXCLK | ETH_TXCLK  | DDR_D04   | DDR_DQ4  | USB_VDD_D   | USB_DVDD    |

| ENET_TXD1  | ETH_TXD1   | DDR_D01   | DDR_DQ1  | USB_VDDA    | USB_AVDD    |

| ENET_TXD6  | ETH_TXD6   | DDR_D06   | DDR_DQ6  | USB_GNDA    | USB_AGND    |

| ENET_TXD7  | ETH_TXD7   | DDR_D02   | DDR_DQ2  | USB_GNDA    | USB_AGND    |

| HOST_D08   | HOST_D8    | DDR_D03   | DDR_DQ3  | USB_GNDA    | USB_AGND    |

| HOST_D09   | HOST_D9    | DDR_D14   | DDR_DQ14 | USB_VDDA    | USB_AVDD    |

| HOST_D04   | HOST_D4    | DDR_D08   | DDR_DQ8  | USB_VDDAC   | USB_ACVDD   |

| HOST_D05   | HOST_D5    | DDR_D15   | DDR_DQ15 | USB_GNDAC   | USB_ACGND   |

| HOST_D06   | HOST_D6    | DDR_DQ9   | DDR_DQ9  | USB_A_TST   | USB_ANA_TE  |

| HOST_D02   | HOST_D2    | DDR_D10   | DDR_DQ10 | VID3_FIELD  | VID23_GPIO  |

| HOST_D03   | HOST_D3    | DDR_VREF1 | DDR_VREF | VID3_VSYNC  | VID_DATA_16 |

| HOST_D07   | HOST_D7    | DDR_D13   | DDR_DQ13 | USB_VBUSD   | USB_D_VBUS  |

| HOST_D01   | HOST_D1    | DDR_D12   | DDR_DQ12 | VID3_HSYNC  | VID_DATA_17 |

| HOST_D00   | HOST_D0    | DDR_D11   | DDR_DQ11 | VID2_PXCIK  | VID2_PIXCLK |

| CF_IACKn   | CF_INPACKn | DDR_D25   | DDR_DQ25 |             |             |

# Table 1Pin Name Changes

# **SoC Features**

#### HD H.264 Codec

- Dual-Stream High-Definition (HD) or Standard-Definition (SD) H.264 Codecs

- Full-duplex HD or SD operation

- Dual Encode HD or SD or

- Dual Decode HD or SD

- H.264 Codec supports High, Main, and Baseline profiles

- H.264 Codec up to level 4.1

- H.264 Encoding or decoding up to 1920x1080i

- Programmable resolutions and frame rates

- Multi-stream SD encode or decode

- Video bit rates: 64 kbps 62.5 Mbps

- Macro-Block Level Adaptive Frame/Field (MBAFF) support

#### **MPEG-2** Decoder

- HD and SD decoder

- Enables real-time HD MPEG-2 to HD H.264 transcoding

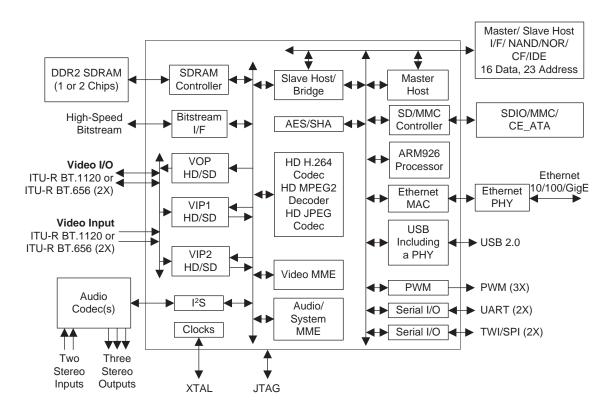

#### Block Diagram

• Multi-stream SD MPEG-2 decoding

# JPEG Codec

- JPEG Encoder and Decoder

- HD or SD MJPEG Support

- Exchangeable Image File Format (EXIF) Support

# Audio Codecs & Decoders

- High-fidelity, 2-channel AAC-LC codec

- MPEG-1/2 Audio Layer II codec (MP2)

- MPEG-1/2 Audio Layer I and III decoder (MP1 and MP3)

- Dolby Digital 5.1 decode and down mix

- G.711 Codec

- Flexible bit rates and sample rates

- Additional codecs planned

- One S/PDIF output port

- Two I<sup>2</sup>S Audio input ports and three I<sup>2</sup>S Audio output ports

#### Video Input Processors (VIPs)

- Flexible direct video inputs

- Two ITU-R BT.1120 parallel interfaces

- Four ITU-R BT.656 parallel interfaces

- Two advanced Video Input Processors (VIPs)

- Digital Image Stabilization

- Smooth Digital Zoom

#### Video Output Processor (VOP)

- HD or SD output support via ITU-R BT.1120 or ITU-R BT.656

- Multi-stream decode supports scaled PIP and multi-channel compositing on video output

- LCD Interface, 16-Bit, 18-bit or 8-bit RGB

- High-quality Video output video scaling

- Two overlay planes with alpha blending and cursor

- Generates optional external sync signals

# Integrated ARM926-EJ Processor

- 240 MHz general purpose processor

- 16 kByte Data Cache

- 16 kByte Instruction Cache

- 16 kByte Scratch Pad Memory

#### System Connectivity

- 10/100/GigE Ethernet MAC<sup>1</sup>

- USB 2.0 On-The-Go (OTG) ports including the physical layer

- High Speed Bit-stream I/O

- AES and SHA hardware acceleration

#### **Peripheral Interfaces**

- Secure Digital (SD), Secure Digital Input/ Output (SDIO), Multi-Media Card (MMC), and Consumer Electronics AT Attachment (CE-ATA)

- Compact FLASH, IDE

#### General Purpose Interfaces

- Two SPI or Two Wire Interface ports

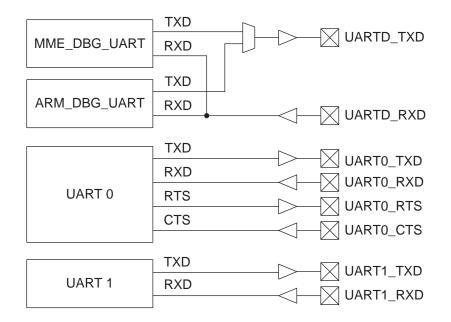

- Three UARTs

- Three Pulse Width Modulators

- Up to 72 GPIO, 8 dedicated

# System

- Core Voltage:  $1.05V \pm 5\%$

- SDRAM Voltage: 1.8V ±0.1V

- I/O Voltages: 1.8V, 2.5V, 3.3V ±10%

- On-Chip A/V PLLs driven from single crystal

#### Power Consumption (MG3500+SDRAM)

• H.264 HD 30fps + AAC Encode 750 mW

#### Packaging

• 376-ball FPBGA, 18x18mm, 0.8mm pitch, RoHS compliant

<sup>1.</sup> When both 10/100 and GigE need to be enabled, an external switch must be installed to select the clock.

# 1.0 Description

The Maxim High-Profile H.264 Codecs currently comprises two devices: MG3500 HD H.264 Codec SoC and MG2580 720p30 H.264 Codec SoC. The MG3500 HD H.264 Codec SoC is a full HD 1080p30 H.264 Codec. It is the ideal choice for any 1080p30 H.264 application as well as multi-channel D1 applications as found in the security surveillance space. Similarly, the MG2580 SoC is the cost-reduced version of the High-Profile H.264 Codecs that performs 720p30 H.264 and MJPEG encoding operations. The MG2580 is particularly adapted for both IP camera and H.264 webcam designs. Both chips encompass an ARM926-EJ processor as well as a complete set of System-On-a-Chip (SoC) features.

Table 1-1 shows the features for each of the devices. Specific information for both of these devices are covered in this datasheet.

All references to MG3500 throughout this manual also apply to the MG2580 as well unless stated otherwise.

| Feature                                                     | MG3500       | MG2580       |

|-------------------------------------------------------------|--------------|--------------|

| Standard Definition Codec                                   | $\checkmark$ | $\checkmark$ |

| High Definition H.264 Codec                                 | 1080p30      | 720p30       |

| MPEG-2 Decoder                                              | √            | $\checkmark$ |

| JPEG Codec                                                  | $\checkmark$ | $\checkmark$ |

| Video Input Ports Supported (8-bit or 16-bit)               | 2            | 1            |

| Frame Multiplexed Video Inputs                              | 4            | _            |

| Video Input Processors                                      | 2            | 2            |

| Video Output Ports Supported (8-bit or 16-bit) <sup>1</sup> | 1            | 1            |

| Video Output Prcessors                                      | 1            | 1            |

| Audio Input Ports                                           | 2            | 1            |

| Audio Codecs and Decoders                                   | $\checkmark$ | $\checkmark$ |

| High-Speed Bitstream I/O                                    | $\checkmark$ | -            |

| Embedded ARM926-EJ Processor                                | $\checkmark$ | $\checkmark$ |

| Master Mode Operation                                       | $\checkmark$ | $\checkmark$ |

| Slave Mode Operation                                        | $\checkmark$ | $\checkmark$ |

| Embedded 10/100/GigE Ethernet MAC                           | $\checkmark$ | $\checkmark$ |

| USB On-The-Go including Physical Layer                      | $\checkmark$ | $\checkmark$ |

| SD, SDIO, MMC, CE-ATA Peripheral Interface                  | $\checkmark$ | $\checkmark$ |

| Compact Flash                                               | $\checkmark$ | $\checkmark$ |

| 32-Bit SDRAM Interface                                      | $\checkmark$ | $\checkmark$ |

| SPI or Two-Wire Interface                                   | 3            | 2            |

| UARTs                                                       | 3            | 3            |

| Pulse Width Modulators                                      | 3            | 3            |

| GPIO, Shared                                                | 64           | 61           |

| GPIO, Dedicated                                             | 8            | 8            |

| Table 1-1 MG30 | 0 Family of High-Definition H.264 Codec |

|----------------|-----------------------------------------|

|----------------|-----------------------------------------|

1. The MG2580 supports 8-bit output only. MG3500 can support an 8-bit or 16-bit output.

#### 1.1 Hardware Overview

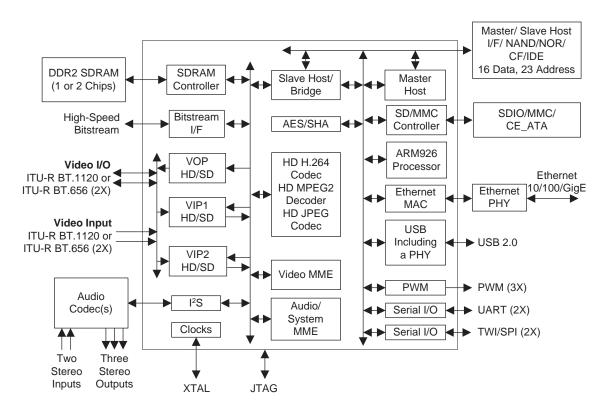

This section provides an overview of each of the blocks in the MG3500 SoC. See "Block Diagram" on page 11.

#### 1.1.1 Video Codecs

The MG3500 SoC includes efficient hardware implementations of two HD encoders and three HD decoders:

- H.264 Encoder/Decoder

- MPEG2 Decoder

- JPEG/MJPEG Encoder/Decoder

As shown in Figure 1-2, the H.264 Codec, MPEG2 Decoder and JPEG/MJPEG Codec are implemented as separate elements in order to support real time trans-coding from one format to another.

The H.264 Codec hardware pipeline allows the highest processing power at the lowest power consumption to support all of the H.264 tools for the High, Main, and Baseline profiles. The processing power that enables HD Encoding or Decoding can also be applied to Encoding or Decoding multiple reduced resolution or SD streams.

The H.264 Codec is capable of encoding or decoding up to 1920 pixels per line (horizontal) and up to 2000 lines (vertical) as long as the total number of 16x16 macroblocks does not exceed 8192 and the macroblocks per second does not exceed 244800.

The HD MPEG2 Decoder is also capable of decoding up to a maximum of 1920 pixels per line (horizontal) and 2000 lines (vertical). It does not have encoding capabilities.

The JPEG/MJPEG Codec is also capable of decoding up to a maximum of 1920 pixels per line (horizontal) and 2000 lines (vertical) for real time video, but in addition, it can encode or decode up to 8k by 8k still images that reside in the memory.

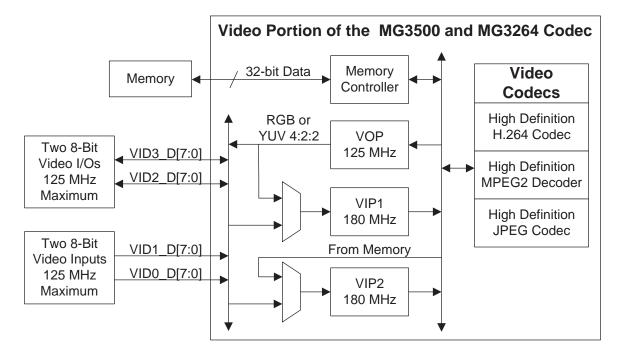

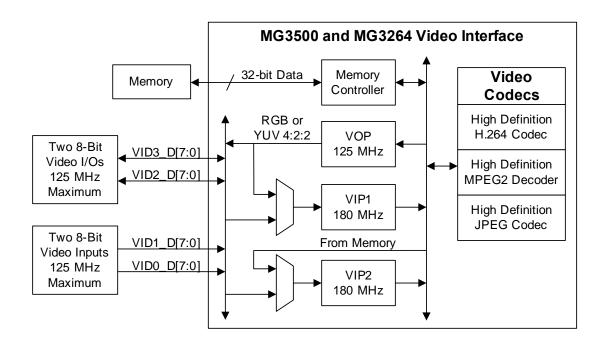

#### 1.1.2 Video Processors and Interfaces

As shown in Figure 1-2, the MG3500 SoC video path has two Video Input Processors (VIP: VIP1 and VIP2) and one Video Output Processor (VOP).

The Codec has two 8-bit video inputs (VID0 and VID1) that can be used either as two individual 8-bit ITU-R BT 656 video inputs or a single 16-bit ITU-R BT 1120 video input for HD inputs from an HDMI receiver or other HD input.

Additionally, the Codec provides two bi-directional ports (VID2 and VID3) that can be used either as an HD input or as an output (one 8-bit or one 16-bit output).

These bi-directional ports can be clocked at higher frequency to support non-standard video interfaces. These two 8-bit interfaces can be combined to create a single 16-bit HD ITU-R BT 1120 interface.

The bi-directional video ports can also be used to drive an LCD display in one of two modes. As an standard output, it can drive an 8-bit RGB LCD interface or it can be used as a 16-bit HD output. Two additional bits are available to drive an 18-bit RGB LCD interface.

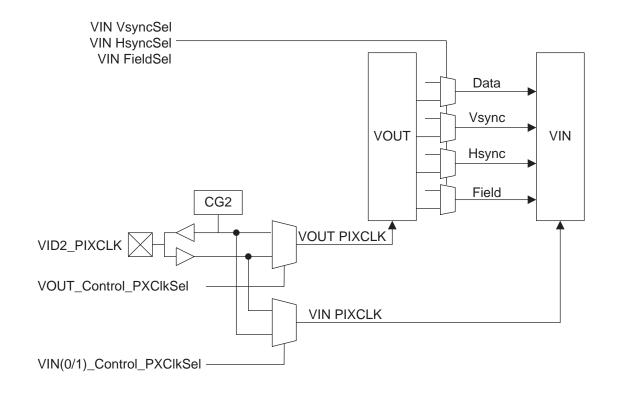

Each video input supports independent clocks and synchronization signals. The clock frequency can be driven over 100 MHz in order to support non-standard video inputs including HD sensors with 8-bit interfaces.

Figure 1-2 Block Diagram of the Video Input Section

The two VIPs and one VOP provide the capability of processing two independent video inputs and one independent video output. Together with the flexible Video Interfaces described above, the modes shown in Table 1-2 are supported.

**Note:** Video composition features, such as memory-based scaling or merging multiple videos into one screen are not available when two VIPs are both used as inputs.

| Video Mode | Video Inputs | Video Outputs | Video Composition |

|------------|--------------|---------------|-------------------|

| 1          | 1 HD         | 1 HD          | Yes               |

| 2          | 1 HD         | 1 SD          | Yes               |

| 3          | 2 HD         | None          | Not Available     |

| 4          | 2 SD         | 1 HD          | Not Available     |

| 5          | 1 SD + 1 HD  | 1 SD          | Not Available     |

| 6          | 2 SD         | 1 SD          | Not Available     |

Table 1-2 Video Modes

Note: The HD output can be used as an 18-bit LCD interface and an SD output can be used as an 8-bit LCD interface.

# 1.1.3 Video Input Processor

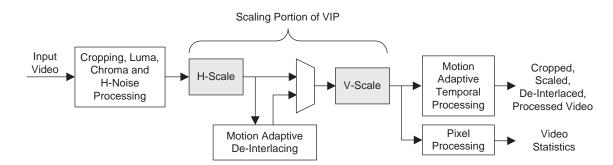

There are two identical Video Input Processors (VIPs) that perform high quality scaling, chroma and gamma adjustment, filtering, and the extraction of video analytics. The maximum pixel rate that the VIP can process corresponds to video input of resolution 1920x1080i at 30 frames per seconds.

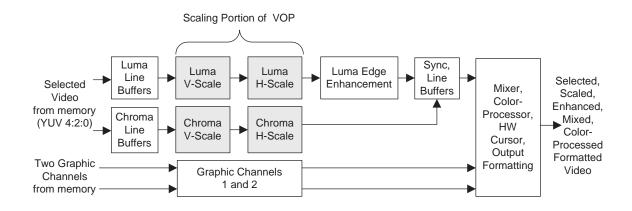

# 1.1.4 Video Output Processor

The Video Output Processor (VOP) performs high quality scaling of un-compressed video, overlays it with two graphic planes, performs gamma and chroma adjustment, overlays a hardware cursor, and outputs the combined video to a video port. Each graphic plane can be from 1 to 32 bits. Graphic planes using less than eight bits use a Look-Up Table (LUT).

**Note:** Some formats may not be possible depending on the output resolution and available system memory bandwidth. For example 32 bits/pixel modes are not possible for 1080i60 resolution output.

| Mode | Bits/Pixel | Format    | Mode | Bits/Pixel | Format       |  |  |  |  |

|------|------------|-----------|------|------------|--------------|--|--|--|--|

| 0    | 1          | Indexed   | 16   | 16         | RGB 4:4:4    |  |  |  |  |

| 1    | 1          | Grayscale | 17   | 16         | RGBα 4:4:4:4 |  |  |  |  |

| 2    | 2          | Indexed   | 18   | 16         | RGB 5:5:5    |  |  |  |  |

| 3    | 2          | Grayscale | 19   | 16         | RGBα 5:5:5:1 |  |  |  |  |

| 4    | 4          | Indexed   | 20   | 16         | RGB 5:6:5    |  |  |  |  |

| 5    | 4          | Grayscale | 21   | 16         | RGBα 5:6:4:1 |  |  |  |  |

| 6    | 8          | Indexed   | 24   | 32         | RGB 8:8:8    |  |  |  |  |

| 7    | 8          | Grayscale | 25   | 32         | RGBα 8:8:8:8 |  |  |  |  |

Table 1-3Video Output Modes

The video output can be either be YCbCr via an 8-bit ITU-R BT 656 interface, YCbCr via a 16-bit ITU-R BT 1120 interface, RGB via an 8-bit interface, or RGB via an 18-bit interface. In some of the output modes, the MG3500/MG2580 HD H.264 Codec SoC is also capable of generating optional external sync signals.

#### 1.1.5 Video Multi-Media Engine

The Video Multi-Media Engine (MME) is a proprietary Reduced Instruction Set Computer (RISC) that has been optimized for single cycle context switching and low power. The Video MME controls all aspects of the VIPs, Video Cores, and the VOP (see the MG3500/MG2580 HD H.264 Codec SoC Block Diagram on page 3 for more information).

# 1.1.6 Audio Multi-Media Engine

The Audio MME implements all audio Codecs in firmware.

# 1.1.7 Audio Interfaces

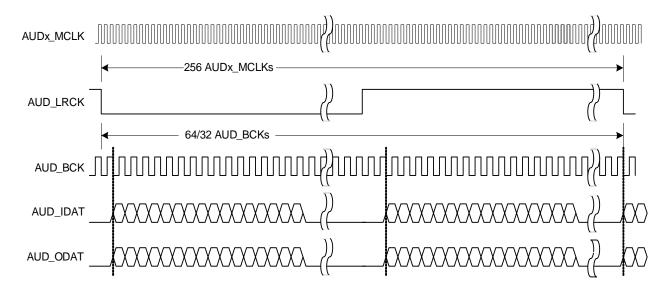

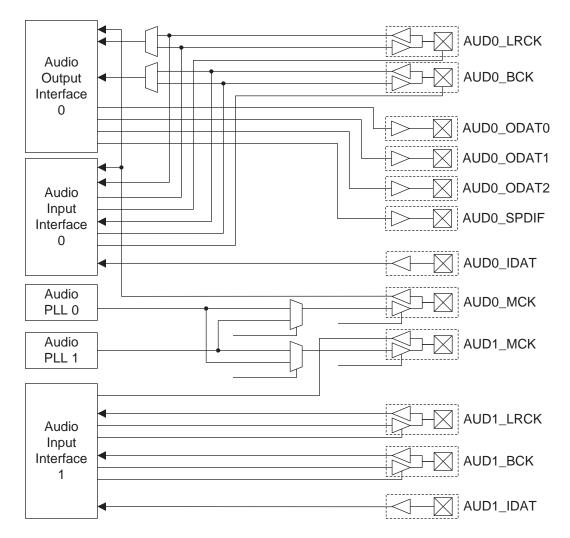

There are two  $I^2S$  inputs, three  $I^2S$  outputs, and one S/PDIF output. One of the two  $I^2S$  inputs is associated with one of the audio clocks. The other audio input, the three audio outputs, and the S/PDIF output must share a common clock and sample rate. The three  $I^2S$  outputs and the S/PDIF output must also share a common format.

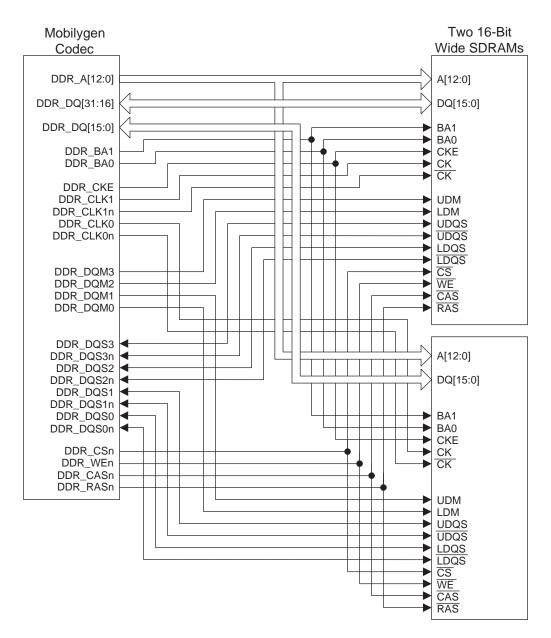

#### 1.1.8 SDRAM

The MG3500/MG2580 HD H.264 Codec SoC has a high performance memory subsystem that uses either a 16- or 32-bit wide external SDRAM. The SDRAM is DDR2, and runs up to 264 MHz.

# 1.1.9 ARM926-EJ

The MG3500/MG2580 HD H.264 Codec SoC has an embedded ARM926-EJ processor that runs at speeds up to 240 MHz. This processor is not used for Audio or Video Codec functions, so it is completely available to implement any required system level functions. Mobilygen provides Codec and Data Streaming APIs under Linux 2.6.20.

#### 1.1.10 Ethernet Media Access Controller

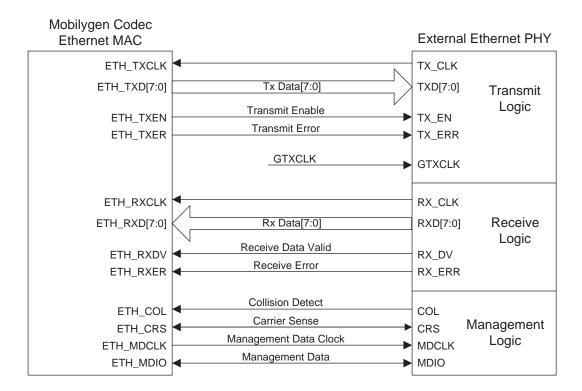

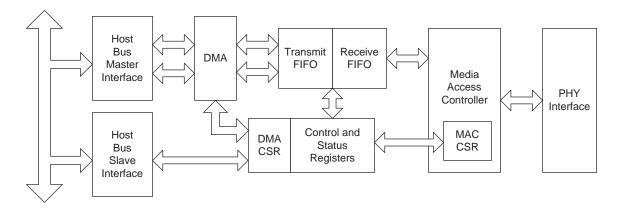

The Ethernet MAC supports 10/100/1000 Mbps Ethernet interfaces.<sup>1</sup> This is typically connected to an external Physical Layer (Phy) device but can also be connected directly to Ethernet switches that support Reverse MII interfaces.

# 1.1.11 USB 2.0

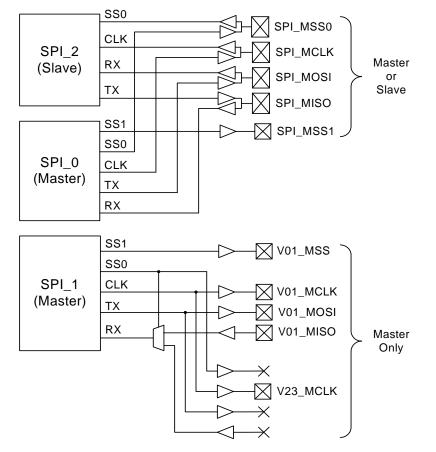

The USB interface is USB 2.0, High-Speed with the ability to operate as Device, Host, or On-The-Go (OTG) at speeds of up to 480 MHz. The USB interface includes the Physical Layer.

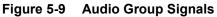

# 1.1.12 FLASH, IDE and Host Interface

The host interface can be used to communicate to external devices including NOR FLASH, NAND FLASH, and COMPACT FLASH, as well as other devices.

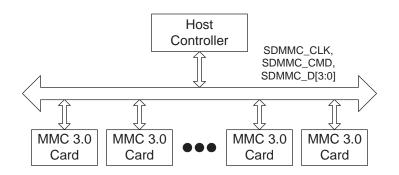

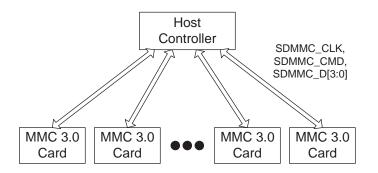

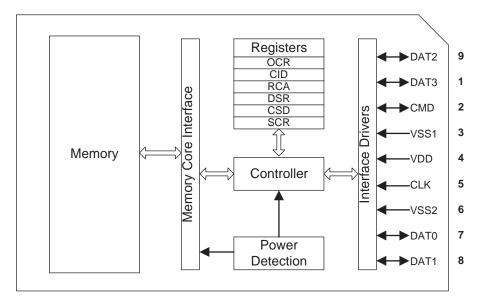

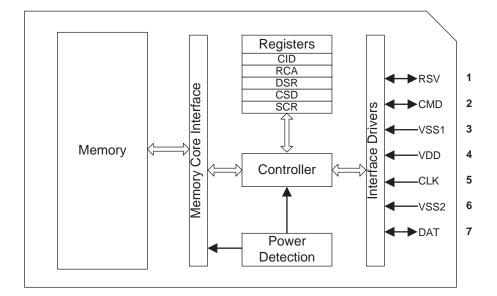

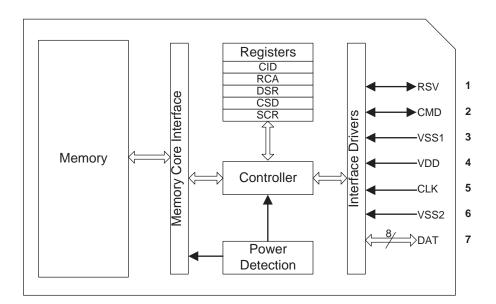

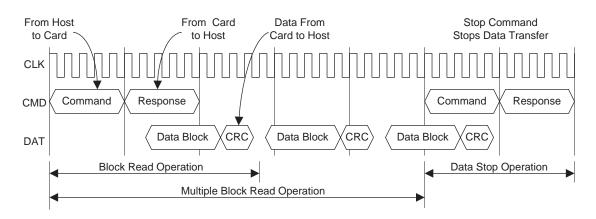

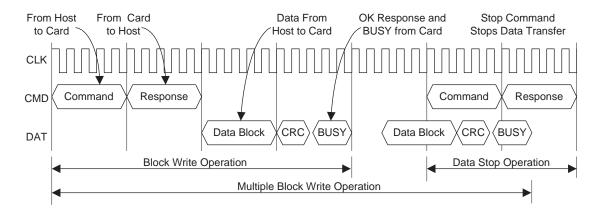

#### 1.1.13 SD/MMC Interface

The SD/MMC interface is designed to support Secure Digital (SD), Secure Digital Input/Output (SDIO), Multi-Media Card (MMC), and Consumer Electronics AT Attachment (CE-ATA) devices. This four-bit wide interface supports up to a 25 MHz clock rate (100 Mbits/sec. transfer rate).

#### 1.1.14 AES and SHA Hardware Acceleration

The MG3500 SoC design includes hardware acceleration for the Advanced Encryption Standard (AES) and Secure Hashing Algorithm (SHA). The AES accelerator supports CBC, CTR, ECB, and CCM modes with 128, 192, and 256 bit keys for secure data storage and transmission. The SHA accelerator supports the creation of 128, 224, and 256 bit digests for Digital Signatures and Digital Time Stamps.

#### 1.1.15 Serial and Misc. IO

The MG3500 SoC has several UARTs for communication, Pulse Width Modulators (PWMs) for control, I<sup>2</sup>C-compatible Two Wire Interfaces (TWIs) for device control, and Serial Peripheral Interfaces (SPIs) for device control.

The MG3500 SoC also has eight dedicated General Purpose Input/Output (GPIO) pins and up to 64 shared GPIO pins that can be used for system control. The shared GPIO pins are multiplexed with other functions and are only available when the primary function for the pin is not being used. For example, if your design does not require a SPI interface (see "SPI/Bitstream Interface Timing" on page 89), the four pins dedicated to that interface can be used as GPIO pins.

<sup>1.</sup> When both 10/100 and GigE need to be enabled, an external switch must be installed to select the clock.

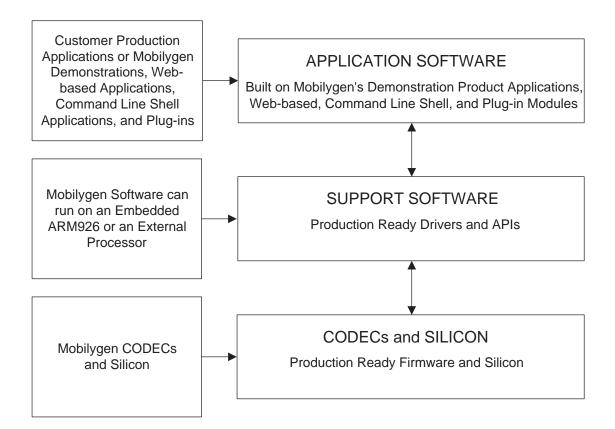

#### 1.2 Support Tools

This section provides an overview of the software and hardware development tools that are available to support the part.

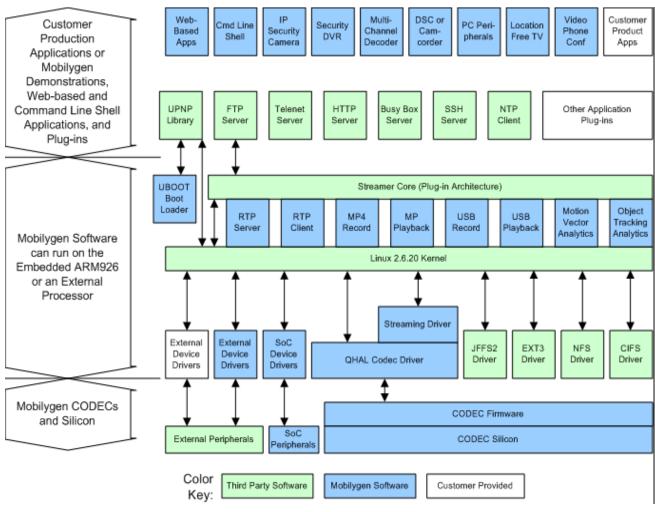

Figure 1-3 Software Architecture

The Mobilygen-developed MG3500 SoC software is developed for Linux 2.6.20. Mobilygen supplies these APIs and Drivers:

- Codec API

- qHAL Hardware Abstraction Layer

- Data Streaming API

- On-Chip Device Drivers

Figure 1-4 shows an expanded version of Figure 1-3 that has all of the elements of the system software included. In this figure:

- Blue boxes are applications, firmware, drivers, and silicon supplied by Mobilygen.

- Green boxes are applications that are available from third-party vendors (public domain or Linux vendors)

- White boxes are customer-written applications

Figure 1-4 Software Elements

**Note:** As shown in Figure 1-4, the Mobilygen supplied drivers and higher-level functions (the lower two-thirds of Figure 1-4) are production ready and fully supported by Mobilygen. The Customer Production Applications and Mobilygen Demonstration programs (the upper third of Figure 1-4) are available for customers to use as an advanced starting point, but are not production ready.

# 2.0 Device Overview, Pin Assignments

#### 2.1 Naming Conventions

The MG3500 SoC has both signal and power connections. Each signal has a unique name. Power connections do not necessarily have unique names.

The signals are organized by signal groups. The signal names typically have two parts separated by an underscore. When that is the case the first part represents the name of the signal group and the second part defines the function within that group. The signal group names do not have an underscore in them, so the first underscore separates the signal group name from the function name. The function name may have an underscore in it. Signals that are active low end with a lower case 'n'.

Power connection names also have two parts separated by an underscore. The first part represents the power domain, and the second part represents the power type.

All pins have a Primary function, and the name that is assigned to the pin reflects that primary function. Many of the pins have an Alternate (ALT) function that can be used if the primary function is not used. Some pins are capable of being used as General Purpose I/O pins (GPIO) is neither their primary or their secondary functions are being used. These pins are available for customer-assigned uses.

The pinout diagrams and tables in this section list the pins by their Primary name. The pinout tables also show the Alternate and GPIO capabilities of the pins if any are assigned to them.

#### 2.2 Pinout Diagrams

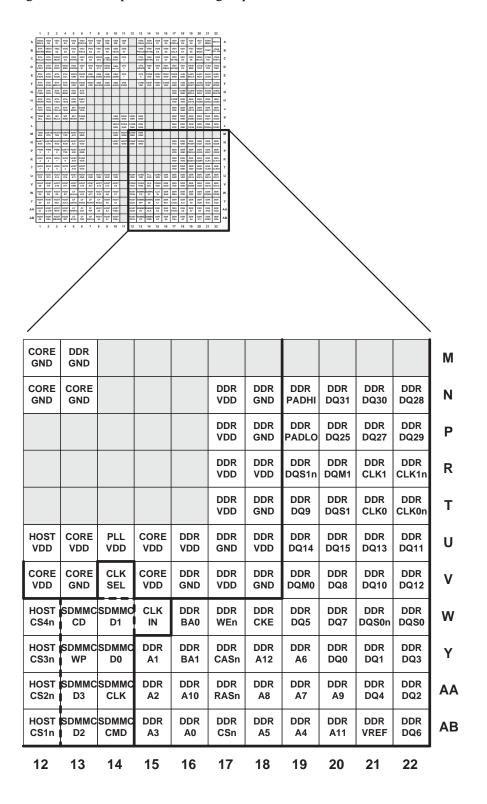

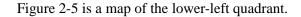

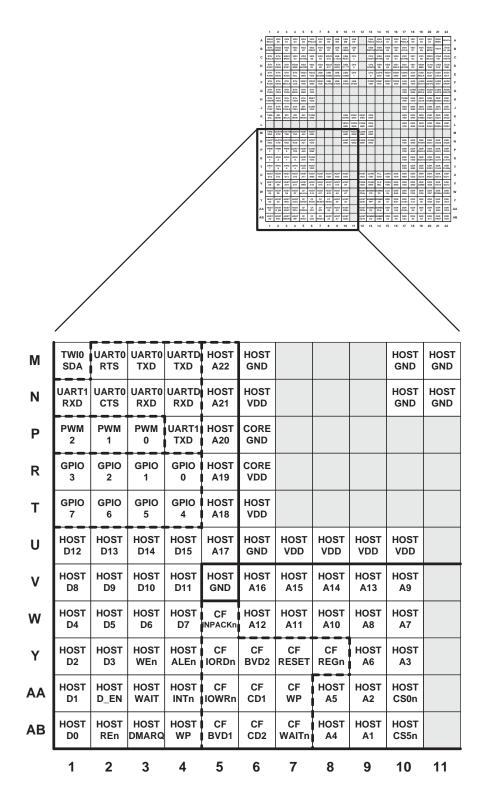

Figure 2-1 shows a map of all the signal positions.

|                          | CONFIG Group<br>VID01 Power                  |                                                |               |               |              |               |                |              |                            |               |                |              |              |                |                |              |               |                |             |               |               |               |                 |    |                            |

|--------------------------|----------------------------------------------|------------------------------------------------|---------------|---------------|--------------|---------------|----------------|--------------|----------------------------|---------------|----------------|--------------|--------------|----------------|----------------|--------------|---------------|----------------|-------------|---------------|---------------|---------------|-----------------|----|----------------------------|

|                          |                                              | VID23 Group USB Group<br>VID23 Power USB Power |               |               |              |               |                |              | VID01 Group<br>VID01 Power |               |                |              |              |                |                |              |               |                |             |               |               |               |                 |    |                            |

|                          |                                              | 1                                              | 2             | 3             | 4            | 5             | 6              | 7            | 8                          | 9             | 10             | 11           | 12           | 13             | 14             | 15           | 16            | 17             | 18          | 19            | 20            | 21            | 22              |    |                            |

|                          | Α                                            | VID23<br>MCLK                                  | VID2<br>D0    | VID2<br>D1    | VID2<br>D4   | VID2<br>D6    | VID2<br>PIXCLK | VID3<br>D2   | VID3<br>D6                 | USB<br>XIN    | USB<br>DM      | USB<br>DP    |              | VID0<br>FIELD  | VID0<br>OUTCLK | VID0<br>D1   | VID0<br>D5    | VID1<br>PIXCLK | VID1<br>D0  | VID1<br>D4    | VID1<br>D7    | VID01<br>MISO | RESETn          | A  | RESET Group<br>AUDIO Power |

| -                        | в                                            | ETH<br>RXERR                                   | VID23<br>MISO | VID2<br>D2    | VID2<br>D5   | VID2<br>D7    | VID2<br>FIELD  | VID3<br>D3   | VID3<br>D7                 | USB<br>XO     | USB<br>VBUS    | USB<br>ID    |              | VID0<br>PIXCLK | VID0<br>VSYNC  | VID0<br>D2   | VID0<br>D6    | VID1<br>OUTCLK | VID1<br>D1  | VID1<br>D5    | VID01<br>MOSI | TEST          | JTAG<br>TAP_SEL | в  | -                          |

|                          | с                                            | ETH<br>RXCLK                                   | ETH<br>RXDV   | VID23<br>MOSI | VID2<br>D3   | VID2<br>VSYNC | VID3<br>D0     | VID3<br>D4   | VID23<br>D16               | USB<br>D_VBUS | USB<br>REXT    | CFG<br>3     |              | CFG<br>HOST1   | VID0<br>HSYNC  | VID0<br>D3   | VID0<br>D7    | VID1<br>VSYNC  | VID1<br>D2  | VID1<br>D6    | VID01<br>MCLK | JTAG<br>TDI   | JTAG<br>TRSTn   | с  | JTAG Group<br>AUDIO Power  |

|                          | D                                            | ETH<br>RXD7                                    | ETH<br>RXD2   | ETH<br>RXD1   | VID23<br>MSS | VID2<br>HSYNC | VID3<br>D1     | VID3<br>D5   | VID23<br>D17               | VID23<br>GPIO | USB<br>ANA_TST | CFG<br>2     | V            | CFG<br>HOST0   | VID0<br>D0     | VID0<br>D4   | VID1<br>FIELD | VID1<br>HSYNC  | VID1<br>D3  | VID01<br>MSS  | JTAG<br>TDO   | JTAG<br>TCK   | JTAG<br>TMS     | D  |                            |

| ETH Group<br>ETH Power   | Е                                            | ETH<br>RXD6                                    | ETH<br>RXD3   | ETH<br>RXD0   | ETH<br>COL   | VID23<br>GND  | VID23<br>VDD   | USB<br>ACGND | USB<br>AGND                | USB<br>AGND   | USB<br>AGND    | CFG<br>1     |              | CFG<br>0       | CORE<br>VDD    | VID01<br>VDD | VID01<br>GND  | CORE<br>GND    | AUD<br>GND  | AUD1<br>MCLK  | AUD1<br>BCK   | AUD1<br>LRCK  | AUD1<br>IDAT    | E  | -                          |

|                          | F                                            | ETH<br>RXD5                                    | ETH<br>RXD4   | ETH<br>MDCLK  | ETH<br>CRS   | VID23<br>VDD  | VID23<br>GND   | VID23<br>VDD | USB<br>ACVDD               | USB<br>AVDD   | USB<br>AVDD    | USB<br>DVDD  |              | CORE<br>VDD    | VID01<br>VDD   | VID01<br>VDD | CORE<br>VDD   | AUD<br>GND     | AUD<br>VDD  | AUD0<br>ODAT1 | AUD0<br>ODAT2 | AUD0<br>IDAT  | AUD0<br>SPDIF   | F  | AUDIOGroup<br>AUDIO Power  |

|                          | G                                            | ETH<br>TXEN                                    | ETH<br>TXD4   | ETH<br>TXD0   | ETH<br>MDIO  | ETH<br>GND    | ETH<br>VDD     |              |                            |               |                |              |              |                |                |              |               | AUD<br>VDD     | CORE<br>GND | AUD0<br>MCLK  | AUD0<br>BCK   | AUD0<br>LRCK  | AUD0<br>ODAT0   | G  |                            |

|                          | н                                            | ETH<br>TXERR                                   | ETH<br>TXD5   | ETH<br>TXD3   | ETH<br>TXD2  | ETH<br>GND    | ETH<br>VDD     |              |                            |               |                |              |              |                |                |              |               | CORE<br>VDD    | DDR<br>VDD  | DDR<br>DQ18   | DDR<br>DQM2   | DDR<br>DQS2n  | DDR<br>DQS2     | н  | -                          |

| SPI Group                | J                                            | ETH<br>TXD7                                    | ETH<br>TXD6   | ETH<br>TXCLK  | ETH<br>TXD1  | SPI<br>MISO   | CORE<br>VDD    |              |                            |               |                |              |              |                |                |              |               | DDR<br>VDD     | DDR<br>GND  | DDR<br>DQ19   | DDR<br>DQ20   | DDR<br>DQ17   | DDR<br>DQ16     | J  |                            |

| HUST FOWER               | к                                            | TWI0<br>SCL                                    | SPI<br>MOSI   | SPI<br>MCLK   | SPI<br>MSS1  | SPI<br>MSS0   | CORE<br>GND    |              |                            |               | USB<br>DGND    | VID01<br>GND | VID01<br>GND | DDR<br>GND     |                |              |               | DDR<br>VDD     | DDR<br>GND  | DDR<br>DQM3   | DDR<br>DQ23   | DDR<br>DQ21   | DDR<br>DQ22     | к  |                            |

| TWI Group<br>HOST Power  | L                                            |                                                |               |               |              |               |                |              |                            |               | VID23<br>GND   | CORE<br>GND  | CORE<br>GND  | DDR<br>GND     |                |              |               | DDR<br>VDD     | DDR<br>GND  | DDR<br>DQ26   | DDR<br>DQ24   | DDR<br>DQS3n  | DDR<br>DQS3     | L  |                            |

|                          | М                                            | TWI0<br>SDA                                    | UARTO<br>RTS  | UART0<br>TXD  | UARTD<br>TXD | HOST<br>A22   | HOST<br>GND    |              |                            |               | HOST<br>GND    | HOST<br>GND  | CORE<br>GND  | DDR<br>GND     |                |              |               |                |             |               |               |               |                 | м  |                            |

| UART Group<br>HOST Power | N                                            | UART1<br>RXD                                   | UART0<br>CTS  | UART0<br>RXD  | UARTD<br>RXD | HOST<br>A21   | HOST<br>VDD    |              |                            |               | HOST<br>GND    | HOST<br>GND  | CORE<br>GND  | CORE<br>GND    |                |              |               | DDR<br>VDD     | DDR<br>GND  | DDR<br>PADHI  | DDR<br>DQ31   | DDR<br>DQ30   | DDR<br>DQ28     | N  |                            |

| PWM Group<br>HOST Power  | Р                                            | PWM<br>2                                       | PWM<br>1      | PWM<br>0      | UART1<br>TXD | HOST<br>A20   | CORE<br>GND    |              |                            |               |                |              |              |                |                |              |               | DDR<br>VDD     | DDR<br>GND  | DDR<br>PADLO  | DDR<br>DQ25   | DDR<br>DQ27   | DDR<br>DQ29     | Р  |                            |

| GPIO Group               | R                                            | GPIO<br>3                                      | GPIO<br>2     | GPIO<br>1     | GPIO<br>0    | HOST<br>A19   | CORE<br>VDD    |              |                            |               |                |              |              |                |                |              |               | DDR<br>VDD     | DDR<br>VDD  | DDR<br>DQS1n  | DDR<br>DQM1   | DDR<br>CLK1   | DDR<br>CLK1n    | R  | DDR Group<br>DDR Power     |

| HOST Power               | т                                            | GPIO<br>7                                      | GPIO<br>6     | GPIO<br>5     | GPIO<br>4    | HOST<br>A18   | HOST<br>VDD    |              |                            |               |                |              |              |                | CLK<br>HOS     |              |               | DDR<br>VDD     | DDR<br>GND  | DDR<br>DQ9    | DDR<br>DQS1   | DDR<br>CLK0   | DDR<br>CLK0n    | т  |                            |

|                          | U                                            | HOST<br>D12                                    | HOST<br>D13   | HOST<br>D14   | HOST<br>D15  | HOST<br>A17   | HOST<br>GND    | HOST<br>VDD  | HOST<br>VDD                | HOST<br>VDD   | HOST<br>VDD    |              | HOST<br>VDD  | CORE<br>VDD    | PLL<br>VDD     | CORE<br>VDD  | DDR<br>VDD    | DDR<br>GND     | DDR<br>VDD  | DDR<br>DQ14   | DDR<br>DQ15   | DDR<br>DQ13   | DDR<br>DQ11     | U  |                            |

|                          | v                                            | HOST<br>D8                                     | HOST<br>D9    | HOST<br>D10   | HOST<br>D11  | HOST<br>GND   | HOST<br>A16    | HOST<br>A15  | HOST<br>A14                | HOST<br>A13   | HOST<br>A9     |              | CORE<br>VDD  | CORE<br>GND    | CLK<br>SEL     | CORE<br>VDD  | DDR<br>GND    | DDR<br>VDD     | DDR<br>GND  | DDR<br>DQM0   | DDR<br>DQ8    | DDR<br>DQ10   | DDR<br>DQ12     | v  |                            |

| HOST Group               | w                                            | HOST<br>D4                                     | HOST<br>D5    | HOST<br>D6    | HOST<br>D7   | CF            | HOST<br>A12    | HOST<br>A11  | HOST<br>A10                | HOST<br>A8    | HOST<br>A7     |              | HOST<br>CS4n | SDMMC<br>CD    | SDMMC<br>D1    | CLK<br>IN    | DDR<br>BA0    | DDR<br>WEn     | DDR<br>CKE  | DDR<br>DQ5    | DDR<br>DQ7    | DDR<br>DQS0n  | DDR<br>DQS0     | w  |                            |

| HOST Power               | Y                                            | HOST<br>D2                                     | HOST<br>D3    | HOST<br>WEn   | HOST<br>ALEn | CF<br>IORDn   | CF<br>BVD2     | CF<br>RESET  | CF<br>REGn                 | HOST<br>A6    | HOST<br>A3     |              | HOST<br>CS3n | SDMMC<br>WP    | SDMMC<br>D0    | DDR<br>A1    | DDR<br>BA1    | DDR<br>CASn    | DDR<br>A12  | DDR<br>A6     | DDR<br>DQ0    | DDR<br>DQ1    | DDR<br>DQ3      | Y  |                            |

|                          | AA                                           | HOST<br>D1                                     | HOST<br>D_EN  | HOST          | HOST<br>INTn | CF<br>IOWRn   | CF<br>CD1      | CF<br>WP     | HOST<br>A5                 | HOST<br>A2    | HOST<br>CS0n   |              | HOST<br>CS2n | SDMMC<br>D3    | SDMMC<br>CLK   | DDR<br>A2    | DDR<br>A10    | DDR<br>RASn    | DDR<br>A8   | DDR<br>A7     | DDR<br>A9     | DDR<br>DQ4    | DDR<br>DQ2      | AA |                            |

|                          | AB                                           | HOST<br>D0                                     | HOST<br>REn   | HOST          | HOST<br>WP   | CF<br>BVD1    | CF<br>CD2      | CF<br>WAITn  | HOST<br>A4                 | HOST<br>A1    | HOST<br>CS5n   |              | HOST<br>CS1n | SDMMC<br>D2    | SDMMC<br>CMD   | DDR<br>A3    | DDR<br>A0     | DDR<br>CSn     | DDR<br>A5   | DDR<br>A4     | DDR<br>A11    | DDR<br>VREF   | DDR<br>DQ6      | AB |                            |

|                          |                                              | 1                                              | 2             | 3             | 4            | 5             | 6              | 7            | 8                          | 9             | 10             | 11           | 12           | 13             | 14             | 15           | 16            | 17             | 18          | 19            | 20            | 21            | 22              | I  |                            |

|                          | CF Group HOST Group<br>HOST Power HOST Power |                                                |               |               |              |               |                |              |                            |               |                | DMMC<br>HOST |              |                |                |              |               | Group<br>Power |             |               |               |               |                 |    |                            |

Figure 2-1 Map of all the MG3500 SoC Signal Positions (Top View)

| Figure 2-2 is a map of the upper-left quadrant | t. |

|------------------------------------------------|----|

|------------------------------------------------|----|

|   | 1             | 2             | 3             | 4            | 5             | 6              | 7            | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 10             | 11           |

|---|---------------|---------------|---------------|--------------|---------------|----------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------------|