### **General Description**

The MAX7389/MAX7390 replace ceramic resonators, crystals, and supervisory functions for microcontrollers in 3.3V and 5V applications.

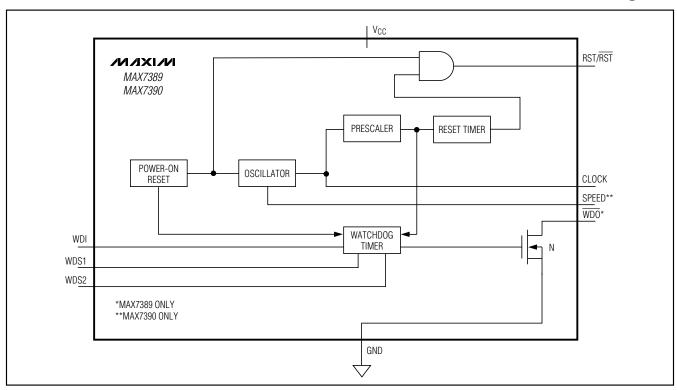

The MAX7389/MAX7390 provide a clock source, reset, and watchdog functions. The watchdog timer is pin programmable and provides watchdog timeout values in the 16ms to 2048ms range. The MAX7389 provides a separate watchdog output that is used as a status indicator or to control safety-critical system elements.

The MAX7390 features a clock-speed select that reduces the output frequency by half. This functionality allows the microcontroller to operate at reduced power and may be used to extend the time available to perform housekeeping tasks, such as writing data to flash during a power failure.

The MAX7389/MAX7390 clock outputs are factory programmed to a frequency in the 1MHz to 16MHz range. Four standard frequencies are available. Other frequencies are available upon request. The maximum operating supply current is 5.5mA with a clock frequency of 12MHz.

Unlike typical crystal and ceramic resonator oscillator circuits, the MAX7389/MAX7390 are resistant to EMI and vibration, and operate reliably at high temperatures. The high-output drive current and absence of high-impedance nodes make the oscillator invulnerable to dirty or humid operating conditions.

The MAX7389/MAX7390 are available in an 8-pin µMAX® package. The MAX7389/MAX7390 standard operating temperature range is from -40°C to +125°C.

### **Applications**

White Goods Handheld Products Automotive Portable Equipment Microcontroller Systems Appliances and Controls

µMAX is a registered trademark of Maxim Integrated Products, Inc.

#### Features

- **Robust Microcontroller Clock and Supervisor in a** Single Package

- ♦ Integrated Reset and Watchdog Functions

- ♦ Pin-Programmable Watchdog Timeout

- **♦** Speed Select

- ♦ +2.7V to +5.5V Operation

- **♦** Factory-Trimmed Oscillator

- ♦ Reset Valid Down to 1.1V Supply Voltage

- ♦ ±10mA Clock-Output Drive Current

- ♦ ±4% Total Accuracy for -40°C to +125°C

- ♦ ±2.75% Total Accuracy for 0°C to +85°C

- ♦ 5.5mA Operating Current (12MHz Version)

- ♦ -40°C to +125°C Temperature Range

- ♦ 8-Pin µMAX Surface-Mount Package

- ◆ 1MHz to 16MHz Factory Preset Frequency

## **Ordering Information**

| PART        | TEMP RANGE      | PIN-<br>PACKAGE | PKG<br>CODE |

|-------------|-----------------|-----------------|-------------|

| MAX7389srff | -40°C to +125°C | 8 µMAX          | U8-1        |

| MAX7390srff | -40°C to +125°C | 8 µMAX          | U8-1        |

Note: "s" is a placeholder for the reset output type. Insert the symbol found in Table 3 in the place of "s." "r" is a placeholder for the power-on reset (POR) voltage. Insert the symbol found in Table 2 in the place of "r." "ff" is a placeholder for the nominal output frequency. Insert the symbol found in Table 4 in the place of "ff." For example, MAX7389CMTP describes a device with 4.38V reset level, open-collector RST output, and a clock output frequency of 8MHz.

Typical Application Circuit, Functional Diagram, and Selector Guide appear at end of data sheet.

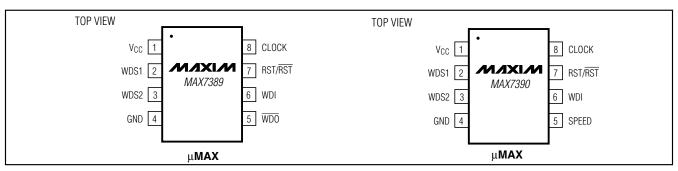

## **Pin Configurations**

Maxim Integrated Products 1

### **ABSOLUTE MAXIMUM RATINGS**

|                                         | CC + 0.3V)<br>±50mA | Operating Temperature Range | +150°C<br>+150°C to +150°C |

|-----------------------------------------|---------------------|-----------------------------|----------------------------|

| 8-Pin µMAX (derate 4.5mW/°C over +70°C) | 362mW               |                             |                            |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

(Typical Application Circuit,  $V_{CC} = +2.7V$  to +5.5V,  $T_A = -40^{\circ}C$  to  $+125^{\circ}C$ , 1MHz to 16MHz output frequency range, typical values at  $V_{CC} = +5.0V$ ,  $T_A = +25^{\circ}C$ , unless otherwise noted.) (Note 1)

| PARAMETER                                     | SYMBOL            | CONDITIONS                                                                 | MIN TYP                 | MAX                    | UNITS  |

|-----------------------------------------------|-------------------|----------------------------------------------------------------------------|-------------------------|------------------------|--------|

| POWER REQUIREMENTS                            |                   |                                                                            | ·                       |                        |        |

| Operating Supply Voltage                      | Vcc               |                                                                            | 2.7                     | 5.5                    | V      |

| Valid RST/RST Supply Voltage                  | \/oon             | $T_A = 0$ °C to +85°C                                                      |                         | 1.1                    | V      |

| Valid h31/h31 Supply Voltage                  | VCCR              | $T_A = -40^{\circ}C \text{ to } +125^{\circ}C$                             |                         | 1.18                   | V      |

| Operating Supply Current                      | lcc               | fclock = 12MHz                                                             |                         | 5.5                    | mA     |

| Operating Supply Current                      | 100               | f <sub>CLOCK</sub> = 8MHz                                                  |                         | 4.5                    | IIIA   |

| TRI-LEVEL ANALOG INPUTS: W                    | DS1, WDS          | 2                                                                          |                         |                        |        |

| Input-High Voltage Level                      |                   |                                                                            | V <sub>CC</sub> - 0.55V |                        | V      |

| Input-Middle Voltage Level                    |                   |                                                                            | 0.9                     | V <sub>CC</sub> - 1.1V | V      |

| Input-Low Voltage Level                       |                   |                                                                            |                         | 0.45                   | V      |

| LOGIC INPUT: WDI                              |                   |                                                                            |                         |                        |        |

| Input Leakage Current                         | I <sub>LEAK</sub> | Input high                                                                 |                         | 0.5                    | μΑ     |

| Logic-Input High Voltage                      | VIH               |                                                                            | 0.7 x V <sub>CC</sub>   |                        | V      |

| Logic-Input Low Voltage                       | V <sub>I</sub> L  |                                                                            |                         | 0.3 x V <sub>C</sub> C | V      |

| PUSH-PULL LOGIC OUTPUTS: I                    | RST/RST           |                                                                            |                         |                        |        |

| Output High                                   | Voh               | ISOURCE = 1mA                                                              | V <sub>CC</sub> - 1.5   |                        | V      |

| Output Low                                    | V <sub>OL</sub>   | I <sub>SINK</sub> = 3mA                                                    | 0.05                    | 0.4                    | V      |

| OPEN-DRAIN LOGIC OUTPUTS:                     | RST, PFO,         | WDO                                                                        |                         |                        |        |

| Output Low                                    | Volo              | I <sub>SINK</sub> = 3mA                                                    | 0.05                    | 0.4                    | V      |

| OUTPUT: CLOCK                                 |                   |                                                                            |                         |                        |        |

| Output High Voltage                           | Vohc              | ISOURCE = 5mA                                                              | V <sub>CC</sub> - 0.3   |                        | V      |

| Output Low Voltage                            | Volc              | I <sub>SINK</sub> = 5mA                                                    |                         | 0.3                    | V      |

| CLOCK Acquirect                               | for one           | $T_A = 0^{\circ}C \text{ to } +85^{\circ}C, V_{CC} = 5.0V$                 | -2.75                   | +2.75                  | %      |

| CLOCK Accuracy                                | fclock            | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}, V_{CC} = 5.0\text{V}$ | -4                      | +4                     | 70     |

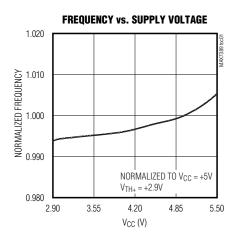

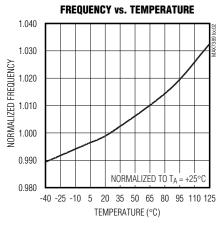

| Clock Frequency Temperature<br>Coefficient    |                   | V <sub>CC</sub> = 5.0V (Note 2)                                            | 140                     | 400                    | ppm/°C |

| Clock Frequency Supply Voltage<br>Coefficient |                   | T <sub>A</sub> = +25°C (Note 2)                                            | 0.67                    | 1                      | %/V    |

## **ELECTRICAL CHARACTERISTICS (continued)**

(Typical Application Circuit,  $V_{CC}$  = +2.7V to +5.5V,  $T_A$  = -40°C to +125°C, 1MHz to 16MHz output frequency range, typical values at  $V_{CC}$  = +5.0V,  $T_A$  = +25°C, unless otherwise noted.) (Note 1)

| PARAMETER                                                 | SYMBOL            | CONDITIONS                                                  |                                                       | MIN                       | TYP                        | MAX                       | UNITS             |

|-----------------------------------------------------------|-------------------|-------------------------------------------------------------|-------------------------------------------------------|---------------------------|----------------------------|---------------------------|-------------------|

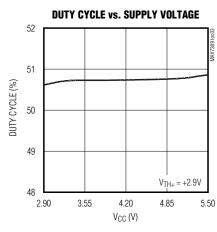

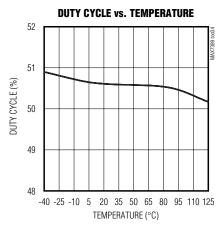

| CLOCK Duty Cycle                                          |                   | (Note 2)                                                    |                                                       | 45                        | 50                         | 55                        | %                 |

| CLOCK Output Jitter                                       |                   | Observation for 20s usin oscilloscope                       | Observation for 20s using a 500MHz oscilloscope       |                           | 310                        |                           | ps<br>RMS         |

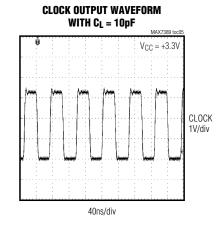

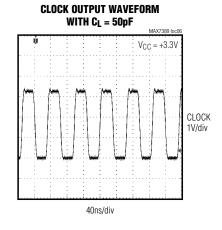

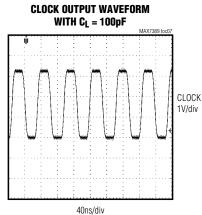

| Output Rise Time                                          | t <sub>R</sub>    | C <sub>LOAD</sub> = 10pF, 10% to 90                         | 0% of full scale (Note 2)                             |                           | 2.5                        | 7.0                       | ns                |

| Output Fall Time                                          | tF                | C <sub>LOAD</sub> = 10pF, 90% to 10% of full scale (Note 2) |                                                       |                           | 2.8                        | 7.5                       | ns                |

| INTERNAL POWER-ON RESET                                   |                   |                                                             |                                                       |                           |                            |                           |                   |

|                                                           | \/                | V <sub>CC</sub> rising, Table 2                             | T <sub>A</sub> = +25°C                                | V <sub>TH</sub><br>- 1.5% |                            | V <sub>TH</sub><br>+ 1.5% |                   |

| Reset Voltage                                             | V <sub>TH+</sub>  | VCC fishing, Table 2                                        | $T_A = -40^{\circ}\text{C to } + 125^{\circ}\text{C}$ | V <sub>TH</sub><br>- 2.5% |                            | V <sub>TH</sub><br>+ 2.5% | V                 |

|                                                           | V <sub>TH</sub> - | V <sub>CC</sub> falling                                     |                                                       |                           | 0.98 x<br>V <sub>TH+</sub> |                           |                   |

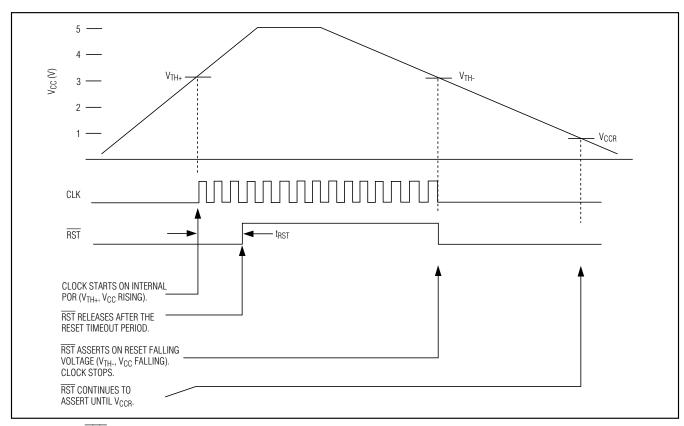

| Reset Timeout Period                                      | trst              | Figures 1, 2                                                |                                                       | 86                        | 135                        | 250                       | μs                |

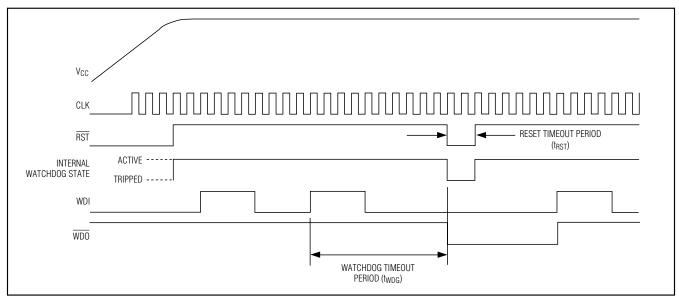

| WATCHDOG                                                  |                   |                                                             |                                                       |                           |                            |                           |                   |

|                                                           |                   | WDS1 = GND, WDS2 =                                          | OS2 = GND                                             |                           | 16                         | 22                        |                   |

|                                                           |                   | WDS1 = open, WDS2 = GND                                     |                                                       | 22                        | 32                         | 44                        |                   |

|                                                           |                   | WDS1 = V <sub>CC</sub> , WDS2 = GND                         |                                                       | 44                        | 64                         | 88                        | ms                |

| Watchdog Timeout Period                                   |                   | WDS1 = GND, WDS2 = open                                     |                                                       | 88                        | 128                        | 177                       |                   |

| (Figure 2)                                                | twDG              | WDS1 = open, WDS2 = open                                    |                                                       | 177                       | 256                        | 354                       |                   |

|                                                           |                   | WDS1 = V <sub>CC</sub> , WDS2 = open                        |                                                       | 354                       | 512                        | 708                       |                   |

|                                                           |                   | WDS1 = GND, WDS2 = V <sub>CC</sub>                          |                                                       | 708                       | 1024                       | 1416                      |                   |

|                                                           |                   | WDS1 = open, WDS2 = V <sub>CC</sub>                         |                                                       | 1416                      | 2048                       | 2832                      |                   |

|                                                           |                   | WDS1 = WDS2 = V <sub>CC</sub> (w                            | atchdog disabled)                                     |                           |                            |                           |                   |

| POWER FAIL                                                |                   |                                                             |                                                       |                           |                            |                           |                   |

| Power-Fail Select Threshold                               | VSEL              | PFI input                                                   |                                                       | 0.65 x<br>V <sub>CC</sub> |                            | 0.85 x<br>V <sub>CC</sub> | V                 |

| V <sub>CC</sub> Monitoring Threshold (Internal Threshold) | VITH              | V <sub>CC</sub> rising                                      |                                                       | 4.06                      | 4.38                       | 4.60                      | V                 |

| Internal Threshold Hysteresis                             | VIHYST            | V <sub>CC</sub> falling                                     |                                                       | 1.0                       | 2                          | 4.0                       | %V <sub>ITH</sub> |

| PFI Monitoring Threshold (External Threshold)             | V <sub>ETH</sub>  | PFI rising                                                  |                                                       | 0.9                       | 1.1                        | 1.4                       | V                 |

| External Threshold Hysteresis                             | VEHYST            | PFI falling                                                 |                                                       | 1.0                       | 3.5                        | 8.0                       | %V <sub>ETH</sub> |

**Note 1:** All parameters are tested at  $T_A = +25$ °C. Specifications over temperature are guaranteed by design.

Note 2: Guaranteed by design. Not production tested.

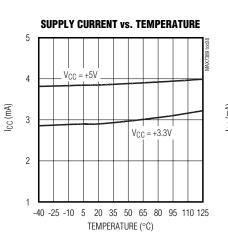

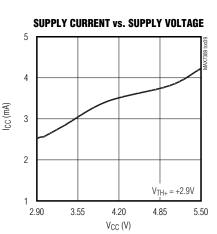

## Typical Operating Characteristics

(Typical Application Circuit, V<sub>CC</sub> = +5V, f<sub>CLOCK</sub> = 16MHz, T<sub>A</sub> = +25°C, unless otherwise noted.)

## Typical Operating Characteristics (continued)

(Typical Application Circuit, V<sub>CC</sub> = +5V, f<sub>CLOCK</sub> = 16MHz, T<sub>A</sub> = +25°C, unless otherwise noted.)

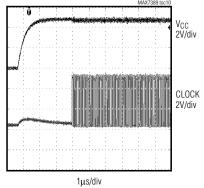

### **CLOCK SETTLING TIME FROM START**

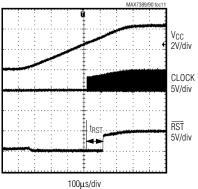

### POWER-ON RESET BEHAVIOR

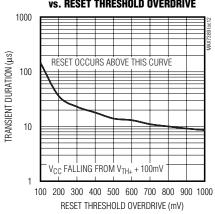

# MAXIMUM V<sub>CC</sub> TRANSIENT DURATION vs. RESET THRESHOLD OVERDRIVE

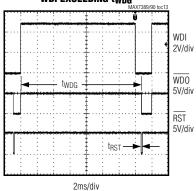

# RESPONSE OF $\overline{RST}$ AND $\overline{WDO}$ WDI EXCEEDING $t_{WDG}$

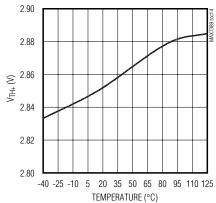

#### **RISING THRESHOLD vs. TEMPERATURE**

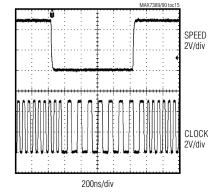

#### **CLOCK RESPONSE TO SPEED SELECT INPUT**

## Pin Description

| PIN     |         | NAME    | FUNCTION                                                                                                                                                                                                                                                                                                                                                                             |

|---------|---------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX7389 | MAX7390 | NAME    | FUNCTION                                                                                                                                                                                                                                                                                                                                                                             |

| 1       | 1       | Vcc     | Power Input. Connect $V_{CC}$ to the power supply. Bypass $V_{CC}$ to GND with a 1 $\mu$ F capacitor. Install the bypass capacitor as close to the device as possible.                                                                                                                                                                                                               |

| 2       | 2       | WDS1    | Watchdog Timeout Select Input 1. Connect WDS1 and WDS2 to V <sub>CC</sub> , GND, or V <sub>CC</sub> /2, as shown in Table 1, to set the watchdog timeout period.                                                                                                                                                                                                                     |

| 3       | 3       | WDS2    | Watchdog Timeout Select Input 2. Connect WDS2 and WDS1 to V <sub>CC</sub> , GND, or V <sub>CC</sub> /2, as shown in Table 1, to set the watchdog timeout period.                                                                                                                                                                                                                     |

| 4       | 4       | GND     | Ground                                                                                                                                                                                                                                                                                                                                                                               |

| 5       | _       | WDO     | Watchdog Output. Open-drain watchdog output asserts if WDI is not toggled within the watchdog timeout period.                                                                                                                                                                                                                                                                        |

| _       | 5       | SPEED   | Clock-Speed Select Input. Connect SPEED high for the factory-trimmed clock output frequency. Connect SPEED low to reduce the clock output frequency by half.                                                                                                                                                                                                                         |

| 6       | 6       | WDI     | Watchdog Input. A rising edge on WDI resets watchdog timer. If WDI does not receive a rising edge within the watchdog timeout period (twDG), RST/RST asserts. The watchdog timeout period is programmable through WDS1 and WDS2. Connect WDS1 and WDS2 to VCC to disable the watchdog timer.                                                                                         |

| 7       | 7       | RST/RST | Reset Output. Reset output is available in one of three configurations: push-pull RST, push-pull RST, or open-drain RST. The reset output is asserted if one of the following conditions occurs: whenever V <sub>CC</sub> is below the reset threshold level; for devices with WDI, reset output asserts when WDI does not receive a rising edge within the watchdog timeout period. |

| 8       | 8       | CLOCK   | Clock Output                                                                                                                                                                                                                                                                                                                                                                         |

## **Detailed Description**

The MAX7389/MAX7390 replace ceramic resonators, crystals, and supervisory functions for microcontrollers in 3.3V and 5V applications.

The MAX7389/MAX7390 provide a clock source, reset, and watchdog functions. The watchdog timer is pin programmable and provides watchdog timeout values in the 16ms to 2048ms range. The MAX7389 provides a separate watchdog output that is used as a status indicator or to control safety-critical system elements. The MAX7390 features a clock-speed switch that reduces the output frequency by half. This functionality allows the microcontroller to operate at reduced power and may be used to extend the time available to perform housekeeping tasks, such as writing data to flash during a power failure.

The integrated reset and watchdog functions provide the power-supply monitoring functions necessary to ensure correct microcontroller operation. The reset circuit has built-in power-supply transient immunity and provides both power-on reset and power-fail or brownout reset

functionality. Two standard factory-trimmed reset levels are available. The watchdog timer is programmable to eight individual timeout values and may be disabled for test purposes.

#### **Clock Output (CLOCK)**

The push-pull clock output (CLOCK) drives a ground-connected  $1k\Omega$  load or a positive supply connected  $500\Omega$  load to within 300mV of either supply rail. CLOCK remains stable over the full operating voltage range and does not generate short output cycles during either power-on or power-off. A typical startup characteristic is shown in the *Typical Operating Characteristics* section.

The MAX7390 clock output frequency is reduced by a factor of two by taking SPEED low. This functionality allows the microcontroller to operate at reduced power and may be used to extend the time available to perform housekeeping tasks.

#### Reset

The reset function drives the microcontroller reset input to prevent operation in the cases of the initial power-on setting, low power-supply voltages, and the failed

6 \_\_\_\_\_\_ /V|X|/M

watchdog operations. Three reset output versions are available: push-pull RST, push-pull RST, and open-drain RST. The reset timeout period (tRST) is nominally 135s.

#### Power-On Reset (POR)

The internal power-on reset (POR) circuit detects the power-supply voltage ( $V_{CC}$ ) level at startup. The POR circuit starts the oscillator when  $V_{CC}$  exceeds the reset rising threshold level ( $V_{TH+}$ ). The reset output remains asserted from the time  $V_{CC}$  crosses the  $V_{TH+}$  and continues to be asserted for the reset timeout period ( $t_{RST}$ ). Upon completion of the reset timeout, the reset output is released. See Figure 1.

#### Low-Voltage Lockout

The reset output asserts whenever V<sub>CC</sub> drops below the reset falling threshold, V<sub>TH-</sub>. The difference between the reset rising and falling threshold values is V<sub>TH+</sub> - (V<sub>TH-</sub>). The nominal hysteresis value is 2% of the reset rising threshold value. The reset detection circuitry provides filtering to prevent triggering on negative voltage spikes. See the *Typical Operating Characteristics* for a plot of

maximum transient duration without causing a reset pulse vs. reset comparator overdrive.

Figure 1 shows the reset output (RST/RST) behavior during power-up and brownout.

#### Watchdog

The watchdog function provides microprocessor monitoring by requiring the microprocessor to toggle an output pin to indicate correct operation. The WDI input monitors the port signal and resets the watchdog timer on receipt of a rising edge. If an edge is not received within the required watchdog timeout period, the watchdog circuit initiates a reset cycle and asserts the  $\overline{\text{WDO}}$  output (MAX7389 only). The internal watchdog circuits are reset and the watchdog timer restarts at the end of the reset cycle (RST/RST output releases). The  $\overline{\text{WDO}}$  output remains asserted until a valid edge is received on the WDI input, signifying correct microprocessor operation. The  $\overline{\text{WDO}}$  output can be used as a status indicator either to the microprocessor or to an external device, such as a fault-indicating LED or sounder. The

Figure 1. RST/RST Behavior During Power-Up and Brownout

WDO output is an open-drain output. The power-up condition of the WDO output is high (not asserted).

The operation of the watchdog and reset function is illustrated in Figure 2.

The watchdog timeout period is set to one of nine possible values by pin strapping WDS1 and WDS2. Each control input has three possible values assigned by connection to GND, V<sub>CC</sub>, or V<sub>CC</sub>/2 (see Table 1). One of the assigned values disables the watchdog function and is intended for customer use during test. The watchdog timer is disabled while the RST/RST output is asserted

**Table 1. Watchdog Timeout Periods**

| WDS1                      | WDS2                      | WATCHDOG TIMEOUT<br>PERIOD (ms) |     |      |  |

|---------------------------|---------------------------|---------------------------------|-----|------|--|

|                           |                           | MIN                             | TYP | MAX  |  |

| GND                       | GND                       | 11                              | 16  | 22   |  |

| V <sub>CC</sub> /2 = open | GND                       | 22                              | 32  | 44   |  |

| Vcc                       | GND 44                    |                                 | 64  | 88   |  |

| GND                       | V <sub>CC</sub> /2 = open | 88 128 1                        |     | 177  |  |

| V <sub>CC</sub> /2 = open | V <sub>CC</sub> /2 = open | 177                             | 256 | 354  |  |

| Vcc                       | V <sub>CC</sub> /2 = open | 354                             | 512 | 708  |  |

| GND                       | Vcc                       | 708 1024 1                      |     | 1416 |  |

| V <sub>CC</sub> /2 = open | Vcc                       | 1416 2048 2828                  |     |      |  |

| Vcc                       | V <sub>CC</sub>           | Disabled                        |     |      |  |

**Note:** WDS1 or WDS2 is pulled internally to V<sub>CC</sub>/2 if left floating.

## **Applications Information**

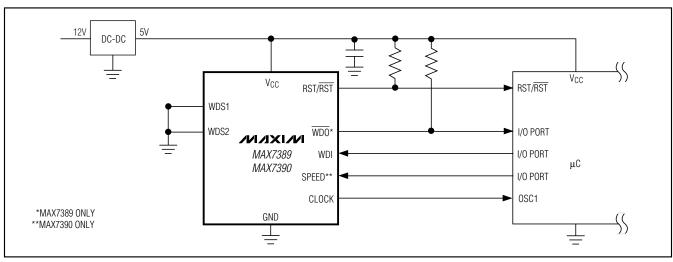

### Interfacing to a Microcontroller Clock Input

The CLOCK output is a push-pull, CMOS logic output, which directly drives any microprocessor ( $\mu$ P) or microcontroller ( $\mu$ C) clock input. There are no impedance-matching issues when using the MAX7389/MAX7390. Operate the MAX7389/MAX7390 and microcontroller (or other clock input device) from the same supply voltage level. Refer to the microcontroller data sheet for clock-input compatibility with external clock signals.

The MAX7389/MAX7390 require no biasing components or load capacitance. When using the MAX7389/MAX7390 to retrofit a crystal oscillator, remove all biasing components from the oscillator input.

#### **Power-Supply Considerations**

The MAX7389/MAX7390 operate with power-supply voltages in the 2.7V to 5.5V range. Power-supply decoupling is needed to maintain the power-supply rejection performance of the devices. Bypass V<sub>CC</sub> to GND with a 0.1µF surface-mount ceramic capacitor. Mount the bypass capacitor as close to the device as possible. If possible, mount the MAX7389/MAX7390 close to the microcontroller's decoupling capacitor so that additional decoupling is not required.

A larger-value bypass capacitor is recommended if the MAX7389/MAX7390 are to operate with a large capacitive load. Use a bypass capacitor value of at least 1000 times that of the output load capacitance.

Figure 2. Watchdog Timing Diagram

### **Output Jitter**

The MAX7389/MAX7390s' jitter performance is given in the *Electrical Characteristics* table as a peak-to-peak value obtained by observing the output of the device for 20s with a 500MHz oscilloscope. Jitter measurements are approximately proportional to the period of the output frequency of the device. Thus, a 4MHz part has approximately twice the jitter value of an 8MHz part.

The jitter performance of all clock sources degrades in the presence of mechanical and electrical interference.

Table 2. POR Voltage

| POWER-ON RESET VOLTAGE (V <sub>TH</sub> ) | r |

|-------------------------------------------|---|

| 4.38                                      | М |

| 3.96                                      | J |

| 3.44                                      | N |

| 3.34                                      | Р |

| 3.13                                      | Q |

| 2.89                                      | s |

| 2.82                                      | V |

| 2.5                                       | Х |

**Note:** Standard values are shown in bold. Contact factory for other POR voltage.

The MAX7389/MAX7390 are immune to vibration, shock, and EMI influences and thus provide a considerably more robust clock source than crystal- or ceramic-resonator-based oscillator circuits.

**Table 3. Reset Output Type**

| OUTPUT TYPE    | s |

|----------------|---|

| Push-pull RST  | А |

| Push-pull RST  | В |

| Open drain RST | С |

**Note:** Standard values are shown in bold. Contact factory for other output types.

**Table 4. Clock Output Frequency**

| CLOCK FREQUENCY (f <sub>CLOCK</sub> ) (MHz) | ff |

|---------------------------------------------|----|

| 4                                           | RD |

| 8                                           | TP |

| 12                                          | VB |

| 16                                          | WB |

Note: Contact factory for other frequencies.

## **Selector Guide**

| PART    | FREQUENCY<br>RANGE (MHz) | RESET<br>FUNCTION | WATCHDOG INPUT (WDI)/<br>WATCHDOG OUTPUT (WDO) | POWER-FAIL INPUT (PFI)/<br>POWER-FAIL OUTPUT (PFO) | SPEED | PIN-<br>PACKAGE |

|---------|--------------------------|-------------------|------------------------------------------------|----------------------------------------------------|-------|-----------------|

| MAX7387 | 1 to 16                  | Yes               | Yes/yes                                        | Yes/yes                                            | _     | 10 μMAX         |

| MAX7388 | 1 to 16                  | Yes               | Yes/no                                         | No/yes                                             | _     | 8 µMAX          |

| MAX7389 | 1 to 16                  | Yes               | Yes/yes                                        | No/no                                              | _     | 8 µMAX          |

| MAX7390 | 1 to 16                  | Yes               | Yes/no                                         | No/no                                              | Yes   | 8 µMAX          |

| MAX7391 | 1 to 16                  | Yes               | No/no                                          | Yes/no                                             | Yes   | 8 µMAX          |

Note: Other versions with different features are available. Refer to the MAX7387/MAX7388 and MAX7391 data sheets.

## \_Functional Diagram

## **Typical Application Circuit**

## Chip Information

PROCESS: BICMOS

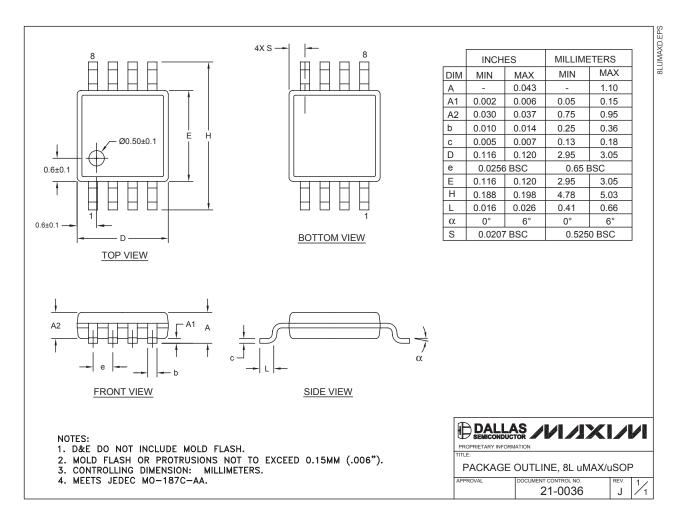

## Package Information

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.