### Manual October 1997

## microelectronics group

**Bell Labs Innovations**

## Field-Programmable Gate Arrays (FPGA) Qualification Manual

**Lucent Technologies**

## Lucent Technologies' Quality Policy

Lucent Technologies is committed to achieving sustained business excellence by integrating quality principles and methods into all we do at every level of our company to:

- Anticipate and meet customer needs and exceed their expectations, every time.

- Relentlessly improve how we work—to deliver the world's best and most innovative communications solutions—faster and more cost-effectively than our competitors.

## **Quality Principles**

- Customer Value—Drive actions from a desire to serve customers. Know current and emerging needs. Understand why customers buy from us and why they don't, and act on that knowledge to deliver superior value.

- Partnership—Build long-term relationships with customers and strategic suppliers based on shared objectives.

- Leadership—Develop leaders who set high expectations, live by our Lucent Values, and create an environment for serving customers and achieving business excellence.

- Ownership—Become personally involved in the success of the business. Turn good ideas into better ways of doing business—working together, taking prudent risks, learning from mistakes, and implementing improvements based on what we learn.

- Process—Manage work with a focus on results improving efficiency and productivity, delivering value to customers, and creating financial rewards for shareowners.

- Improvement—Make the plan-do-check cycle the way we operate—to achieve both continuous and breakthrough improvements in cost, cycle time, and quality.

- Management by Fact—Know what you want. Measure what you get. Act on the difference.

- Results Orientation—Establish and meet both short- and long-term commitments to all key stakeholders—customers, employees, shareholders, suppliers, partners, and society.

### **Shared Methods**

- Policy Deployment—To set, deploy, and reach goals and align efforts company wide.

- Process Management—To manage, improve, and streamline how we work to deliver greater value to customers.

- Problem-solving—To close the gaps that separate us from our goal to be the industry leader.

- Benchmarking—To set meaningful standards and learn from the successful practices of best-in-class companies.

- Management System Assessment—To improve the way we manage the business through systematic evaluation, feedback, and action.

## **Table of Contents**

### Contents

### Page Contents

## Page

| Lucent Technologies' Quality Policy                |    |

|----------------------------------------------------|----|

| Quality Principles                                 |    |

| Shared Methods                                     |    |

| Lucent Technologies' Quality Plan                  | 3  |

| Lucent Technologies' Product Qualification Process | 3  |

| Technology Qualification Plan                      |    |

| Testing                                            |    |

| Intrinsic Reliability Data                         |    |

| Lucent Technologies' Product Qualification Plan    | 4  |

| Qualification Review Board                         |    |

| FPGA Product Qualification Plan                    | 7  |

| 0.35 μm, 0.5 μm, 0.55 μm, and 0.6 μm CMOS          |    |

| Process Qualifications                             | 8  |

| Introduction                                       |    |

| High-Temperature Operating Bias (HTOB)             | 8  |

| Temperature Humidity Bias (THB)                    | 8  |

| Temperature Cycling (TC)                           | 8  |

| Thermal Shock (TS)                                 | 8  |

| Steam Bomb (SB)                                    | 8  |

| Bond Strength (BS) and Die Shear (DS)              | 8  |

| Summary                                            | 8  |

| 1.2 µm EEPROM CMOS Process Qualification           | 9  |

| Introduction                                       | 9  |

| High-Temperature Operating Bias (HTOB)             | 9  |

| Temperature Humidity Bias (THB)                    | 9  |

| Temperature Cycling (TC)                           | 9  |

| Thermal Shock (TS)                                 |    |

| Steam Bomb (SB)                                    |    |

| Bond Strength (BS) and Die Shear (DS)              | 9  |

| Summary                                            |    |

| Device Qualification Testing                       | 10 |

| Overview                                           | 10 |

| Environmental Tests                                | 10 |

| Mechanical Tests                                   | 11 |

| Electrical Tests                                   |    |

| Details of Electrostatic Discharge (ESD) Tests     | 13 |

| ESD Test Methods and Requirements                  |    |

| Details of Latch-Up Tests                          | 16 |

| Integrated Circuit Latch-Up Test Procedure per     |    |

| Lucent Technologies Method A88AL1006               |    |

| Latch-Up Test Details                              | 16 |

| Package Qualification                              |    |

| Introduction                                       | 18 |

| Qualification Status                               | 18 |

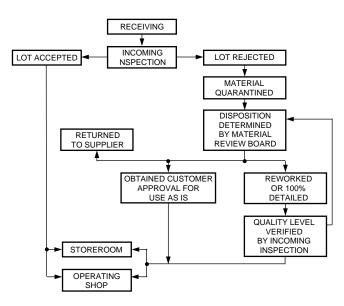

| Vendor Quality Monitoring                          | 26 |

| Overview                                           |    |

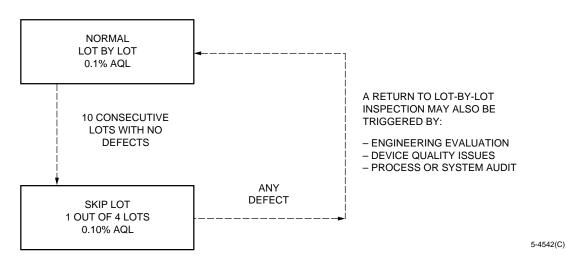

| Inspection                                         | 26 |

| Vendor Qualification                               |    |

| Vendor Commodity Teams                             | 26 |

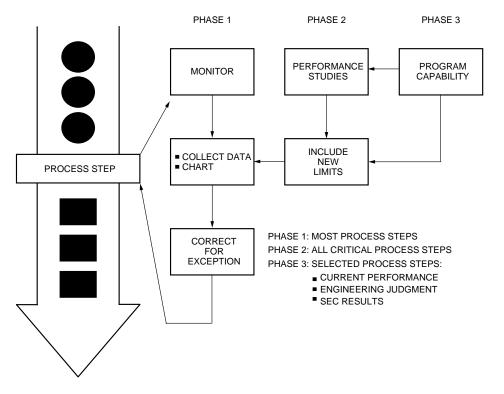

| Manufacturing Control and Improvement            |      |

|--------------------------------------------------|------|

| Line Monitor                                     |      |

| Zone Monitors                                    |      |

| Yield Model                                      |      |

| Statistical Process Control (SPC)                |      |

| Document Control                                 |      |

| Quality Conformance Inspection                   | . 32 |

| Reliability Monitoring Program                   | . 34 |

| Introduction                                     | . 34 |

| Device Failure Model                             |      |

| Measures of Reliability                          |      |

| Accelerated Stress Testing                       |      |

| Effects of Operating Voltage on Failure Rates    | . 35 |

| Time-Temperature Relationship                    |      |

| (Arrhenius Equation)                             |      |

| Assumed Activation Energies                      |      |

| Product Reliability Monitoring Plan              | . 35 |

| Three-Tier Testing Program                       |      |

| Reliability Testing Procedures                   |      |

| Product Families and Sampling Coverage           |      |

| Sample Selection and Sampling Universes          |      |

| Calculating Failure Rates                        | . 39 |

| Failure Mode Analysis (FMA)                      | . 39 |

| Corrective Action                                | . 40 |

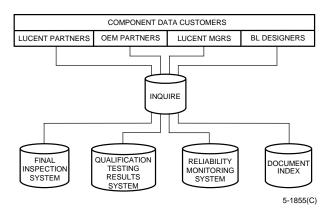

| INQUIRE Database                                 | . 41 |

| INQUIRE Database and Its Role in Quality         |      |

| Assurance                                        | . 41 |

| Qualification Test Data                          | . 41 |

| Reliability Monitoring Data                      | . 41 |

| Document Availability Information                | . 42 |

| Applications                                     | . 42 |

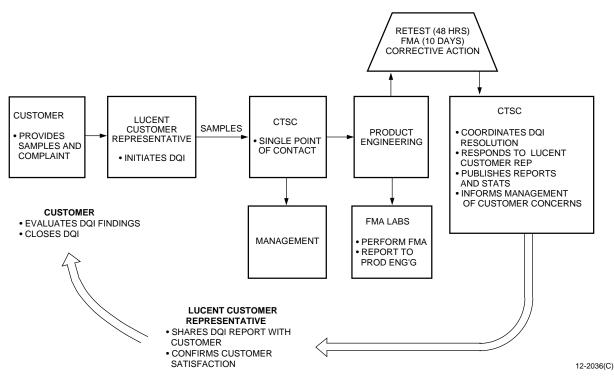

| Customer Support                                 | . 42 |

| Customer Service and the Device Quality Issue    |      |

| (DQI) Process                                    | . 42 |

| Device Qualification Test Procedures and Results |      |

| ATT3000 Series Qualification                     | . 44 |

| Qualification Strategy                           |      |

| ORCA 1C Series Qualification                     |      |

| Qualification Strategy                           | . 50 |

| ORCA 2C Series Qualification                     | . 53 |

| Qualification Strategy                           |      |

| ORCA 2CxxA (5.0 V) Series Qualification          |      |

| Qualification Strategy                           | . 57 |

| ORCA 2TxxA (3.3 V) Series Qualification          |      |

| Qualification Strategy                           | . 63 |

| ATT1700A Series Qualification                    | . 68 |

| Qualification Strategy                           |      |

|                                                  |      |

## Lucent Technologies' Quality Plan

The IC Division is committed to the ISO 9000-series quality system standards as a key element in attracting and retaining satisfied customers. Initially, we focused our efforts throughout the manufacturing locations, which were registered in 1993. In 1994 and 1995, we expanded our scope to include several of our worldwide design centers. These registrations and expansion plans are summarized in Table 1. We have also begun a two-year program to further expand our scope by registering additional worldwide design centers and our worldwide sales offices. These will be completed in 1997.

Table 1. ISO Registration Summary. (All of our manufacturing (mfg) facilities are ISO registered.)

| Mfg<br>Facilities | Yr. | Design<br>Centers | Yr. | Sales<br>Offices | Yr. |

|-------------------|-----|-------------------|-----|------------------|-----|

| Madrid            | 93  | Reading           | 93  | Framingham       | 95  |

| Singapore         | 93  | Allentown         | 93  | Santa Clara      | 96  |

| Bangkok           | 93  | Bracknell         | 94  | Bracknell        | 96  |

| Reading           | 93  | Madrid            | 94  | Munich           | 96  |

| Orlando           | 93  | Munich            | 94  | Tokyo            | 97  |

| Allentown         | 93  | Santa Clara       | 95  | Singapore        | 97  |

|                   |     | Singapore         | 95  | Berkeley Heights | 97  |

|                   |     | Taiwan            | 95  | Allentown        | 97  |

|                   |     | Framingham        | 96  |                  |     |

|                   |     | Tokyo             | 97  |                  |     |

## Lucent Technologies' Product Qualification Process

The process of qualifying a new product at Lucent Technologies is divided into two major efforts: qualification of a new technology and qualification of new device types or designs in the new technology.

Both of these qualifications are described in detail in this section.

### **Technology Qualification Plan**

Lucent Technologies' Process Qualification Plan for both new wafer fabrication and package technologies involves rigorous environmental, mechanical, and electrical testing to confirm technology robustness. Industry-standard tests are applied to test devices. Specialized tests to examine electrostatic discharge and latch-up parameters are also incorporated.

Prior to qualification and manufacture of devices using a new process technology, thousands of ICs from different device types involving multiple wafer lots are subjected to extended reliability tests, and extensive generic reliability tests are conducted.

After the technology is introduced into manufacture, a continuous quality improvement program is begun. Improvements are introduced into the technology, with new issues of the technology put into effect at a rate of about one per year.

Reliability and yield studies are performed on a standard evaluation circuit (SEC).

## Testing

Much of the evaluation of a new technology is done with an SEC. The SEC is tested with a very rigorous methodology, intended to ensure the device functions well beyond its intended operating range.

A voltage stress test is included to detect breakdown of any weak oxides. The device is required to be operational during this stress test. Functional testing is done before and after stress testing. Other tests are performed to detect low-level transistor leakage; these include a variety of hold time tests with various patterns. The same test routine is performed in at least three manufacturing stages: at wafer probe, after packaging, and at the end of reliability testing. Hold time and voltage guard band limits are built into the testing.

### Lucent Technologies' Product Qualification Process (continued)

### Intrinsic Reliability Data

### Electromigration

Electromigration is a well-known failure mechanism that affects continuity or isolation of interconnections. Interconnections are allowed a maximum failure budget of 10 FITS at a junction temperature of 85 °C over 40 years.

This failure mechanism follows a log-normal distribution. Activation energies, standard deviations, and median times to failure are measured separately for each level in the interconnect structure. For failure rate calculations, the die dissipates about 2 W of power. Measurements are made with current levels 10 to 20 times higher than the maximum allowed by the current density design rules.

### **Hot Electron Effects**

Device aging typically shows greater than 10 years to 10% Gm degradation under worst-case substrate current conditions. Actual devices should not be affected by charge injection mechanisms.

### **Mobile Ion Contamination**

Mobile ion contamination is checked at wafer level using a triangular voltage sweep (TVS) procedure.

### Time-Dependent Dielectric Breakdown (TDDB)

Extensive time-dependent dielectric breakdown measurements are made on specially designed large area test structures taken from the line monitor circuit. These devices are packed and put under test at electric fields as high as 6 mV/cm and temperatures as high as 150 °C. Both the thermal and voltage characteristics of the oxide failures are studied. The thermal activation energy is shown to be approximately 0.6 eV at an electric field of 6 mV/cm and a linear electric field acceleration parameter of three decades/(mV/cm). Correlations have been made with wafer-level tests using a gate oxide zone tester. This tester is used to routinely monitor oxide quality.

### Lucent Technologies' Product Qualification Plan

Lucent Technologies' product qualification plan involves rigorous environmental, mechanical, and electrical testing to confirm product soundness.

Industry-standard tests, generally derived from military methods, are applied to test devices; additional specialized tests are administered to determine electrostatic discharge and latch-up sensitivity.

Table 2 presents a menu of tests from which a qualification plan for a new device is developed. It gives the sample size and lot tolerance percent defective (LTPD) for each test. The qualification process is administered by the Qualification Review Board (QRB) described in this section.

Depending upon whether the qualification is for a package, die, or process change—or for a change in fabrication facilities—the QRB determines the tests from Table 2 to be administered. Tests normally required for a new qualification can be satisfied by a reference to recent successful testing on a similar product under appropriate conditions. The QRB maintains a database called the Qualification Testing Results System (QTRS) that contains accurate records of each qualification.

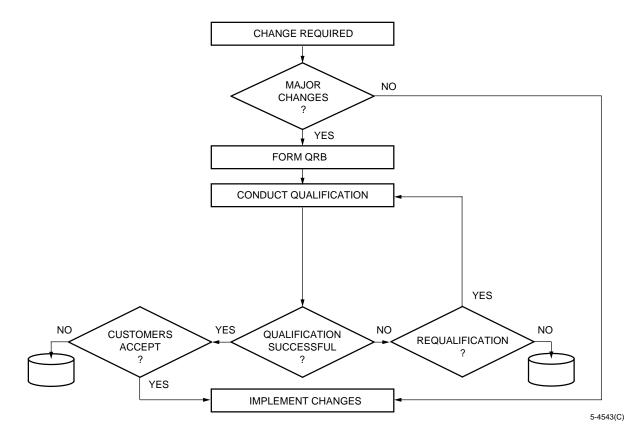

The QRB is also responsible for the requalification of any changes in design, fabrication, or packaging of integrated circuit products. The requalification process implemented by the QRB is shown in Figure 1. Note that the QRB determines the seriousness of the change and supervises the requalification. Note also that the customer is involved in the requalification process.

## Lucent Technologies' Product Qualification Process (continued)

### Table 2. IC Qualification Tests

| Test No./<br>Symbol | Test Description                           | Method                          | Sample Size | LTPD<br>(%) |

|---------------------|--------------------------------------------|---------------------------------|-------------|-------------|

| 1. LT–1 or          | High-Temperature Operating Bias, 125 °C    | M-1005                          | 195         | 2           |

| LT–2                | High-Temperature Operating Bias, 150 °C    | M-1005                          | 100         | 4           |

| 2. CL               | CLASS (Component Lead Assembly Simulation) | A88AL1005                       | 77          | 5           |

| 2a. C <i>n</i> PRE  | Moisture Sensitivity Level                 | A88AL1005                       | 77          | 5           |

| 3. BH               | Temperature-Humidity Bias                  | A89AL0135                       | 77          | 5           |

| 4. SB               | Steam Bomb                                 | A89AL0111                       | 77          | 5           |

| 5. TC               | Temperature Cycling                        | M-1010                          | 77          | 5           |

| 6. TS               | Thermal Shock                              | M-1011                          | 25          | 15          |

| 7. MR               | Moisture Resistance                        | M-1004                          | 38          | 10          |

| 8. LK               | Gross/Fine Leak                            | M-1014                          | 38          | 10          |

| 9. SA               | Salt Atmosphere                            | M-1009                          | 15          | 15          |

| 10. WV              | Internal Water Vapor                       | M-1018                          | 5           | 50          |

| 11. RT              | Low-Temperature Aging                      | A88AL1007                       | 77          | 5           |

| 12. SE              | Soft Error Rate                            | M-1032                          | 10          | _           |

| 13. PS              | Photo Sensitivity                          | —                               | 10          | 22          |

| 14. FL              | Flammability and O <sub>2</sub> Index      | <i>UL</i> * 94 and ASTM 2863-77 |             |             |

| 15. SR              | Solvent Resistance                         | M-2015                          | 15          | 15          |

| 16. IV              | Internal Visual                            | M-2014                          | 5           | 50          |

| 17. PD              | Physical Dimensions                        | M-2016                          | 15          | 15          |

| 18. SD              | Solderability                              | M-2003/<br>A89AL0006            | 4           | _           |

| 19. MS              | Mechanical Shock                           | M-2002                          | 38          | 10          |

| 20. VF              | Variable Frequency Vibration               | M-2007                          | 38          | 10          |

| 21. CA              | Constant Acceleration                      | M-2001                          | 38          | 10          |

| 22. SQ              | Mechanical Sequence                        | —                               | 38          | 10          |

| 23. LI              | Lead Integrity                             | M-2004                          | 15          | 15          |

| 24. BS              | Bond Strength                              | M-2011                          | 15          | 15          |

| 25. DS              | Die Shear Strength                         | M-2019                          | 5           | 50          |

| 26. XR              | X-Ray                                      | M-2012                          | 5           | 50          |

| 27. TQ              | End Torque                                 | M-2024                          | 15          | 15          |

| 28. ES              | Electrostatic Discharge (ESD)              | A91AL015/<br>X-19435            | 18          | _           |

| 29. LU              | Latch-up                                   | A88AL1006                       | 6           |             |

\* UL is a registered trademark of Underwriters Laboratories, Inc.

## **Qualification Review Board**

All new IC devices fabricated in any manufacturing process technology, as well as any changes in a process technology, must be qualified under the administration of the Qualification Review Board (QRB).

The QRB is a committee of Lucent Technologies Bell Labs Innovations and Lucent Technologies representatives who deal with the procedures and issues related to qualification or requalification of silicon integrated circuit devices or processing technologies. Such a qualification must take place before the device or processing technology can be shipped. A QRB is formed each time a new device type or process change is to be qualified. Each QRB consists of a core group, which defines the qualification needs, plus several additional members who act as auditors of the qualification and provide further expertise. The QRB may ask any member of Lucent Technologies to participate in a qualification review, should the need arise.

Every QRB includes experts in reliability engineering, design, or processing. It may also include specialists in packing, quality assurance, product engineering, processing, and electrostatic discharge phenomenon. All members must be satisfied with the completion of a qualification plan before they sign the completed plan. Control of product shipment prior to qualification, usually in the form of models, is the responsibility of the quality assurance representative of the QRB.

Figure 1. Requalification Process Flow

## **FPGA Product Qualification Plan**

Lucent Technologies' product qualification plan for *ORCA®* and ATT3000 Series FPGAs involves rigorous environmental, mechanical, and electrical testing to confirm product soundness.

Industry-standard tests are applied to test devices. Specialized tests to examine electrostatic discharge and latch-up parameters are also incorporated.

Lucent Technologies' FPGAs are qualified by a fourphase process: Lucent Technologies' 0.6  $\mu$ m/0.55  $\mu$ m/ 0.5  $\mu$ m/0.35  $\mu$ m CMOS processes, the design of the device itself, and the performance of a given die in a given package.

Since all Lucent Technologies FPGAs are manufactured using the Lucent Technologies  $0.6 \ \mu m$ ,  $0.55 \ \mu m$ ,  $0.5 \ \mu m$ , or  $0.35 \ \mu m$  CMOS processes, they are carefully monitored and tested. Regarding device design, since each of the devices in each series of FPGAs (ATT3000, ATT1Cxx, ATT2Cxx, ATT2Txx, OR2CxxA, or OR2TxxA) is a matrix of repetitive elements, the QRB determined that qualifying one of the six dies would qualify the design for the product family. Finally, the QRB determined the qualification testing necessary to qualify each die in a given package. Industry-standard tests were chosen, based on prior qualifications with the given package for prior CMOS designs in the same technology.

For example, if a prior qualification of a  $0.6 \,\mu m$  CMOS design had been performed with a larger die than the one in question, the only new tests needed would be electrostatic discharge (ESD) and latch-up.

However, if the die to be qualified was the largest 0.6  $\mu m$  CMOS design to be put in that package, more extensive testing would be required. A table of the tests performed is included in the section on package qualification.

# 0.35 $\mu\text{m}$ , 0.5 $\mu\text{m}$ , 0.55 $\mu\text{m}$ , and 0.6 $\mu\text{m}$ CMOS Process Qualifications

### Introduction

This section presents quality and reliability information for Lucent Technologies'  $0.35 \ \mu m$ ,  $0.5 \ \mu m$ ,  $0.55 \ \mu m$ , and  $0.6 \ \mu m$  advanced CMOS processes. These processes employ N- and P-channel LDD MOS transistors. The  $0.35 \ \mu m$  and  $0.5 \ \mu m$  processes also use three levels of metal, and the  $0.55 \ \mu m$  and  $0.6 \ \mu m$  processes use two levels of metal.

These technologies have been rigorously tested for reliability and manufacturability. Prior to qualification and manufacture of devices using these process technologies, approximately 10,000 devices were subjected to extended reliability tests and extensive generic reliability tests.

After introduction into manufacture, a continuous quality improvement program was begun. This report concentrates on the latest version of the technologies. New improvements are introduced into the technologies, with new issues put into effect at a rate of about one per year.

As part of the processes' qualification, the following tests are performed.

## High-Temperature Operating Bias (HTOB)

The main vehicle for studying HTOB is the standard evaluation circuit (SEC). After testing, the failed parts were examined with physical FMA techniques. On the SEC, electrical failure modes are easily correlated with failure locations. The failing parts were taken through electrical and physical FMA. Gate-level defects are caused by silicon particles at the gate level. Several programs are now in place to attack gate-level defects.

### **Temperature Humidity Bias (THB)**

Temperature humidity bias testing was performed on the SEC per Lucent Technologies' requirements of static bias at 85 °C and 85% relative humidity. THB is known to induce mechanical stress effects due to expansion of the plastic due to water absorption.

## Temperature Cycling (TC)

Temperature cycling was performed per MIL-STD-883C, Method 1010, Condition C.

## Thermal Shock (TS)

Thermal shock was performed per MIL-STD-883, Method-1011, which requires -65 °C to +125 °C, liquid to liquid, for 100 cycles.

## Steam Bomb (SB)

Steam bomb testing was run on the SEC test chips.

## Bond Strength (BS) and Die Shear (DS)

Bond strength was tested per the usual procedure in the models packaging shop at Allentown, PA. All packages for reliability evaluation were packaged at this shop. Die shear strength was also measured on these devices.

### Summary

The latest issues of the 0.35  $\mu$ m, 0.5  $\mu$ m, 0.55  $\mu$ m, and 0.6  $\mu$ m CMOS technologies meet or exceed requirements for qualification in all critical areas.

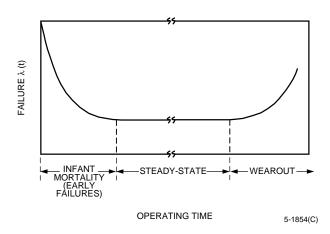

Infant mortality and long-term failure rates have decreased significantly with the lots processed with this log, and it is expected that further improvements will be made as part of a continuous quality improvement program.

## 1.2 μm EEPROM CMOS Process Qualification

### Introduction

This section presents quality and reliability information for the 1.2  $\mu$ m EEPROM CMOS process used to fabricate the ATT1700A family of serial PROMs. As part of process qualification, the following tests are performed.

## **High-Temperature Operating Bias (HTOB)**

The main vehicle for studying HTOB is the standard evaluation circuit (SEC). After testing, the failed parts were examined with physical FMA techniques. On the SEC, electrical failure modes are easily correlated with failure locations. The failing parts were taken through electrical and physical FMA. Gate-level defects are caused by silicon particles at the gate level. Several programs are now in place to attack gate-level defects.

## **Temperature Humidity Bias (THB)**

Temperature humidity bias testing was performed on the SEC per Lucent Technologies' requirements of static bias at 85 °C and 85% relative humidity. THB is known to induce mechanical stress effects due to expansion of the plastic due to water absorption.

## **Temperature Cycling (TC)**

Temperature cycling was performed per MIL-STD-883C, Method 1010, Condition C.

## Thermal Shock (TS)

Thermal shock was performed per MIL-STD-883, Method-1011, which requires -65 °C to +125 °C, liquid to liquid, for 100 cycles.

## Steam Bomb (SB)

Steam bomb testing was run on the SEC test chips.

### Bond Strength (BS) and Die Shear (DS)

Bond strength was tested per the usual procedure in the models packaging shop at Allentown, PA. All packages for reliability evaluation were packaged at this shop. Die shear strength was also measured on these devices.

### Summary

This latest issue of the 1.2  $\mu m$  CMOS technology meets or exceeds requirements for qualification in all critical areas.

## **Device Qualification Testing**

### Overview

Lucent Technologies' product quality program for the ATT3000 and ORCA Series FPGAs requires that the devices undergo a rigorous testing program prior to introduction. The program includes a series of life and environmental tests designed to accelerate failure probabilities in the die and package. As part of device qualification, the following tests are performed:

### **Environmental Tests**

- High-Temperature Operating Bias (HTOB) 150 °C,

4.1 V (3.3 V devices) or 150 °C, 6.2 V (5.0 V devices)

- Component Lead Assembly Simulation Sequence or CLASS (CL)

- Moisture Sensitivity Level (CnPRE) 30 °C to 85 °C/ 60% RH to 85% RH/6 hrs. to 168 hrs.

- Temperature Humidity Bias (THB) 85 °C/85% RH

- Autoclave (SB) 121 °C, 2 ATM

- Temperature Cycling (TC) –65 °C to +150 °C (air to air)

- Thermal Shock (TS) –55 °C to +125 °C (liquid to liquid)

- Moisture Resistance (MR)

- Salt Atmosphere or Corrosion (SA)

### **Mechanical Tests**

- Flammability and O2 Index (FL)

- Solvent Resistance (SR)

- Physical Dimensions (PD)

- Solderability (SD)

- Bond Strength (BS)

- Die Shear Strength (DS)

- X-Ray (XR)

### **Electrical Tests**

- Electrostatic Discharge (ESD) for Each Pin

- Latch-up (LU)

The specific tests used to qualify devices such as the Lucent Technologies' FPGA product family are described below. Test characteristics, parameters, allowed failure rates, and other details are included. Failure mode analysis (FMA) is used as an integral part of quality testing and surveillance to assess any performance flaw, determine corrective measures, and implement these measures to eliminate recurrence.

Test results are presented in the following section.

### **Environmental Tests**

### **High-Temperature Operating Bias (HTOB)**

HTOB testing, also called dynamic life testing, is performed at 150  $^{\circ}$ C/4.1 V (3.3 V devices) and 150  $^{\circ}$ C/6.2 V (5.0 V devices) to provide acceleration over the condition of use.

Dynamic operating life stress is considered to be more representative than static stress because the continual switching of internal circuit nodes more closely approximates the operation of the device in an actual system.

## Component and Lead Assembly Simulation Sequence or CLASS (CL)

This test involves heating, infrared solder simulation, and lead bending. It is a preconditioning test for THB.

### Moisture Sensitivity Level (CnPRE)

Moisture sensitivity level of a part is evaluated during the CLASS testing using JEDEC method A-113. This is summarized in Table 3.

### Table 3. Moisture Sensitivity Levels

| Moisture<br>Sensitivity<br>Level | Allowable Exposure to<br>Moisture at Customer's<br>Assembly Site | Moisture<br>Exposure During<br>Qualification<br>Testing |

|----------------------------------|------------------------------------------------------------------|---------------------------------------------------------|

| 1                                | Unlimited storage at up to 90% RH and 30 °C                      | 168 hrs. at 85%<br>RH and 85 °C                         |

| 2                                | One year storage at up to 60% RH and 30 °C                       | 168 hrs. at 60%<br>RH and 85 °C                         |

| 3                                | Up to 1 week storage at up to 60% RH and 30 °C                   | 192 hrs. at 60%<br>RH and 30 °C                         |

| 4                                | Up to 3 days storage at up to 60% RH and 30 °C                   | 78 hrs. at 60% RH<br>and 30 °C                          |

| 5                                | Up to 1 day storage at up to 60% RH and 30 °C                    | 48 hrs. at 60% RH<br>and 30 °C                          |

| 6                                | Up to 6 hrs. storage at up to 60% RH and 30 °C                   | 6 hrs. at 60% RH<br>and 30 °C                           |

## Device Qualification Testing (continued)

### **Temperature Humidity Bias (THB)**

Because a plastic package is inherently nonhermetic, the penetration of ambient moisture could damage the device due to galvanic action. Thus, temperature humidity bias and autoclave (steam bomb) tests are used to accelerate moisture ingression in order to determine the tolerance of the die to its presence.

THB testing is performed at an ambient temperature of 85 °C and a relative humidity of 85%. The sample devices are tested for 1,000 hours at 5 V, and go through presoak at 85 units/85 units for 96 hours.

### Autoclave (SB)

Autoclave, also known as steam bomb, is a storage test employing the environmental conditions of TA = 121 °C, 100% relative humidity, and 15 psig. This test is used as an additional stringent test to measure the moisture resistance of the packaging system and the susceptibility of the die to corrosion. As with THB testing, both package integrity and actual die construction play major roles in the results.

### **Temperature Cycle (TC)**

The compatibility of materials used in the fabrication of any device is essential to that device's reliability. Any appreciable mismatch in physical properties, such as thermal expansion coefficients, can cause long-term device failures.

In the temperature cycle test, devices are subjected to temperature extremes of -65 °C to +150 °C in nitrogenfilled chambers. One test cycle consists of a 10-minute dwell at each temperature extreme plus a transition time of approximately five minutes.

The gradual change of temperature and relatively long dwell times in an air ambient tend to uncover problems related to expansion rate differentials. Devices are electrically tested after 100 cycles.

### Thermal Shock (TS)

Just as with the temperature cycle test, the thermal shock test is designed to reveal differences in expansion coefficients for components of the packaging system. However, thermal shock creates a more severe stress in that the device is exposed to a sudden change in temperature due to the high thermal conductivity and capacity of the liquid ambient. Devices are placed in a fluorocarbon bath cooled to -65 °C. After remaining in the cold chamber for at least five minutes, the sample is transferred to an adjacent chamber filled with fluorocarbon at 125 °C and is held for an equivalent time. After 100 cycles, thermal shock end-point testing is performed.

### Moisture Resistance (MR)

This test evaluates, on an accelerated schedule, how well component parts and constituent materials resist deterioration from the high temperature and humidity that is typical of tropical environments. The test differs from the steady-state humidity test and derives its added effectiveness by employing temperature cycling, which alternates periods of condensation and drying. This is essential to developing the corrosion process and, in addition, produces a breathing action of moisture into partially sealed containers. The test is carried out per MIL-STD-883C (method 1004).

### Salt Atmosphere or Corrosion (SA)

This test is an accelerated laboratory corrosion test. It simulates the effects of seacoast atmosphere on devices and package elements. The test is carried out per MIL-STD-883C (method 1009).

### Low-Temperature Aging (RT)

This test studies device aging due to hot carrier effects. Since it is well known that hot carrier effects are more pronounced at lower temperatures, the devices are aged at -10 °C for 1,000 hours.

## **Mechanical Tests**

### Flammability and O2 Index (FL)

This test follows UL 94 and ASTM 2863-77 methods.

### Solvent Resistance (SR)

This test is performed per MIL-STD-883C (method 2015). Its purpose is to verify that the marking on the component parts will not become illegible when the parts are subjected to solvents. It also seeks to ensure the solvents will not cause deleterious mechanical or electrical damage, or deterioration of the materials or finishes used in the part.

## Device Qualification Testing (continued)

### Physical Dimensions (PD)

This test is performed to verify that the external physical dimensions of the device are in accordance with the applicable procurement document. The test is carried out per MIL-STD-883C (method 2016).

### Solderability Test (SD)

This test is conducted to determine the solderability of all terminations normally joined by soldering. The determination is made on the basis of the ability of these terminations to be wetted or coated by solder.

Test procedures verify whether treatment during the manufacturing process to facilitate soldering is satisfactory, and that such treatment has been applied to the required portion of the part which is designed to accommodate a solder connection.

The test includes an accelerated aging test which simulates at least six months' natural aging under a combination of storage conditions, each designed to produce particular deleterious effects. This test is carried out per MIL-STD-883C (method 2003).

### Bond Strength (BS)

This test measures bond strength and evaluates bond strength distributions, and can therefore be used to determine compliance with specified bond strength requirements of the product's acquisition document. The test is carried out per MIL-STD-883C (method 2011).

### Die Shear Strength (DS)

This test determines the integrity of materials and procedures used to attach semiconductor die or surfacemounted passive elements to package headers or other substrates. It is carried out per MIL-STD-883C (method 2019).

### X-Ray (XR)

This examination is performed to nondestructively detect defects within the sealed case, especially those resulting from the sealing process. It is also performed to discover internal defects such as foreign objects, improper interconnecting wires, and voids in the die attach material or in the glass when glass seals are used. The test is carried out per MIL-STD-883C (method 2012).

## **Electrical Tests**

### ESD Human-Body Model as per Lucent Technologies Method A97AL1494

Described later in this section, this qualification requires that each pin in the package be protected up to 1000 V from electrostatic discharge caused by human contact.

### ESD Charged-Body Model as per Lucent Technologies Method A97AL1494

Described later in this section, this qualification requires that each pin in the package be protected up to 1000 V from electrostatic discharge from any charged surface.

## Latch-Up as per Lucent Technologies Method A88AL1006

Described in detail later in this section, latch-up stressing includes three components:

- dc stressing of all inputs, outputs, and I/O pins

- Power supply overvoltage stressing

- Poststress ATE testing

Three unstressed, fully functional devices are used for each of the first two tests. A device is considered latched up if, due to the application of stress, the ICC current exceeds the manufacturer's maximum ICC current and remains at that level after the stress is removed. After three devices each are stressed using Test 1 and Test 2, all six devices must be functionally and parametrically retested per Test 3.

### Table 4. Latch-Up Qualification Summary

| Test | Test Type                   | Stress Limits*   |           |

|------|-----------------------------|------------------|-----------|

| 1    | I/O Stress                  | 200 mA           | ≤1.5 Vmax |

| 2    | Power Supply<br>Overvoltage | 1.5 Vmax ≤300 m. |           |

| 3    | Poststress ATE              | Must Pass        |           |

\* Refer to the Latch-Up Test Details section on page 16.

## Details of Electrostatic Discharge (ESD) Tests

### **ESD Test Methods and Requirements**

Source: Lucent Technologies Bell Laboratories Specification A97AL1494

### Purpose

This specification describes a uniform method for establishing electrostatic discharge (ESD) withstand thresholds. It also includes threshold requirements and reporting procedures. A97AL1494 includes pertinent graphics.

#### Scope

All packaged semiconductor devices, thin-film circuits, surface acoustic wave (SAW) devices, optoelectronic devices, and hybrid integrated circuits (HICs) containing any of these devices are to be evaluated according to this specification. The device thresholds are to be reported in the product design information (PDI) document. Device thresholds and corner pin thresholds are to be reported in the appropriate qualification documents.

### **Product Design Information (PDI)**

The PDI is the official Lucent Technologies document in which the responsible design and manufacturing organizations agree that the product information contained therein satisfies manufacturing, legal, and regulatory requirements; it also places certain manufacturing documents under formal change order control.

ESD testing is conducted before transmitting new PDIs and when existing PDIs are reissued due to process, design, packaging, or specification changes. Tests are conducted on the device and package that represent the product in all details presented in the PDI.

### **Types of Testing**

Two types of testing are required:

- Human-body model (HBM)

- Charged-device model (CDM)

#### **Pin Combinations to Be Tested**

For the human-body model, ESD stressing is performed according to the pin combinations outlined in accordance with Mil-Std-883, method 3015, EOS/ESD Association S6.1, and EIA/JESD22-A114:

- Stress each input (or output) pin while grounding all power supply pins

- Stress each power supply pin while grounding each differently named supply pin (or group of pins)

- Stress each input (or output) pin while grounding all output (or input) pins.

The power supply pins include VDD, VCC, VSS, VBB, GND, +VS, –VS, and VREF. Pins such as offset adjust, compensation, clocks, controls, address, data, and input are considered input pins. Output and input/output pins are considered output pins. In addition, do not test no connects (NCs). For the charged-device model (CDM), test each pin.

Voltage levels for HBM ESD testing include:

| 100 V | 500 V  | 2000 V |

|-------|--------|--------|

| 200 V | 1000 V | 4000 V |

Voltage levels for CDM ESD testing include:

| 100 V | 500 V  | 2000 V |

|-------|--------|--------|

| 200 V | 1000 V |        |

Any devices that fail at 500 V are tested further at 100 mV increments to determine threshold value.

### **Test Procedure Overview**

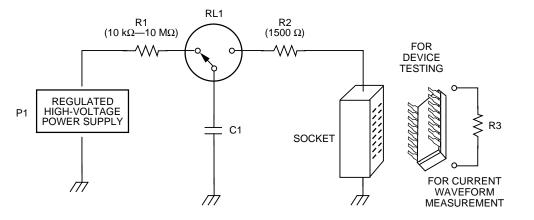

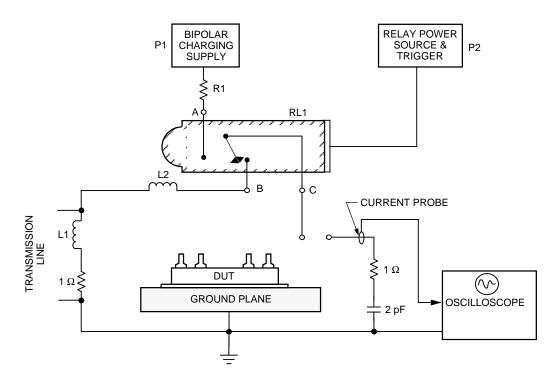

At least six devices are needed to obtain the HBM and CDM thresholds; prepare at least three of these for HBM testing and at least three more for the CDM tests. Carry out all testing at room temperature. Circuit schematics for HBM and CDM testing are shown in Figure 2 and Figure 3, respectively.

# Details of Electrostatic Discharge (ESD) Tests (continued)

#### Specific Test Procedure: HBM

Insert the first device under test (DUT) into the socket as shown in Figure 2. Start with the recommended voltage or with any desired level, as discussed above. At each voltage level, stress all pin combinations as described earlier in this section.

At each voltage level, apply one pulse of each polarity with a minimum 0.3 s interval between pulses to the DUT. Test the device, using the failure criteria specified later in this section. Record the PASS/FAIL results for each device. Use the device result for the next step, described below.

If the result is PASS, stress the same device or a new device at the next higher level as shown in the tables earlier in this section (when you reach the highest level, stop testing). If the result is FAIL, decrease the voltage to the next lower level, select a new device, and stress the new devices if step stress procedure is used. If there is no lower level, stop testing. Repeat these steps until the highest passing voltage for the device and the corner pins is determined.

During device testing procedures, it is allowable to separate polarity; in other words, to stress a device with one polarity and a new device with the opposite polarity. First, determine the threshold for each polarity, as described above. Then, report the threshold value with the lower magnitude.

These test procedures can be modified to fit special circumstances. For example, the withstand threshold is the highest level at which three out of three stressed devices pass. If the device does not pass any level, its threshold is 0 V.

### Specific Test Procedure: CDM

Prepare at least three samples. Place the first device onto the CDM testers. Start with the recommended (or any desired) voltage level, as discussed earlier in the section. All pins will be tested.

To perform CDM, charge the device with a positive potential by charging the package and discharging each pin. Repeat this procedure three times consecutively with a >0.1 s interval between discharges. Repeat the procedure for the negative polarity.

Follow the procedure detailed earlier in this section to determine the CDM threshold. This completes the CDM testing procedure.

#### **Summary of Pass Criteria**

Dependent upon device technology and customer requirements, devices shall meet 1000 V or 2000 V for HBM and 500 V CDM for all pins, 1000 V CDM for corner pins.

#### **Failure Criteria**

Parameters identified in the device specification are monitored for ESD testing. If a device cannot pass its own specifications, it is considered to have failed.

#### **Other Information**

The devices used for each of the above tests will not be used for any prior or future qualification tests. In addition, the test devices are handled with extreme care, using ESD preventative measures so as not to influence the test results. All operators wear grounding straps when handling the devices. The devices are transported in appropriate ESD protective packaging.

5-4356

### Details of Electrostatic Discharge (ESD) Tests (continued)

Figure 2. Circuit Schematic of Human-Body ESD Simulator

5-1787

## **Details of Latch-Up Tests**

### Integrated Circuit Latch-Up Test Procedure per Lucent Technologies Method A88AL1006

### Purpose

This section describes the latch-up stressing method Lucent Technologies uses to screen product for adequate latch-up immunity. This method was last revised 10/97 to align its procedure with JEDEC 17 and meet or exceed the pass/fail requirements of EIA/JESD78.

### **Test Procedure**

The latch-up testing procedure includes three tests:

- dc stressing of all inputs, outputs, and I/O pins

- Power supply overvoltage stressing

- Poststress ATE testing

Three unstressed, fully functional devices are used for each of the first two tests. Each DUT is stressed at  $25 \pm 10$  °C ambient temperature. The duration of the dc stimulus applied to the DUT is less than two seconds, and power supply levels are set to the manufacturer's maximum recommended operating level (Vmax). All six stressed devices must also pass all functional and parametric tests in order to be qualified.

### Biasing

Input pins not under test are biased initially high and alternately biased low. Output and I/O pins are left floating. This pin configuration applies, as long as it does not cause the DUT to malfunction.

If the DUT does malfunction due to this pin configuration, an alternate pin configuration more consistent with the intended device function may be determined by the responsible device qualification engineer. The engineer will record the alternate configuration in the comments section of the results report form.

## Latch-Up Test Details

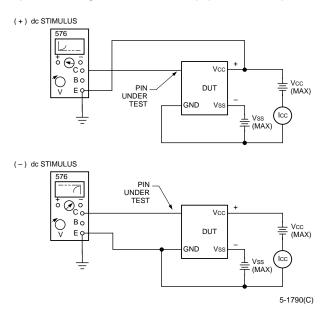

### Test 1: Stressing of Input, Output and I/O Pins

The I/O stress limits, detailed in Table 4, state a current and voltage limit. Current is forced into a pin under test via latch-up stress hardware, until either 200 mA or 1.5 Vmax is attained or latch-up occurs as defined above. For negative polarity I/O stress, current is extracted from the pin under test until either 200 mA or -0.5 Vmax is attained. With the power supply current clamped to 300 mA, the DUT is placed in the test socket, and the Vcc and Vss pins are connected to their respective potentials (Vmax). Then, the input pins not under test are biased high (repeated later, biased low) and the pin under test is current stressed first positively and then negatively.

After each stress, the dc stimulus is removed from the pin under test, and the IcC is observed to determine whether latch-up has occurred. Vcc and Vss are removed and reapplied before stressing the next pin in order to prevent possible high current damage to the DUT. This procedure is repeated until all inputs, outputs, and I/O pins are current stressed for both polarities and with inputs initially biased high and alternately biased low. The results are recorded on the results report form. Figure 4 illustrates equipment hookup.

Figure 4. Test 1: Equipment Hookup: I/O Stress

### Details of Latch-Up Tests (continued)

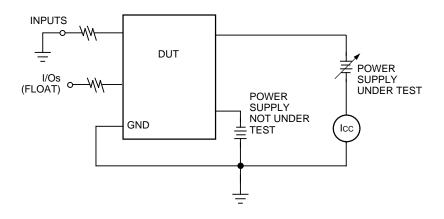

### Test 2: Power Supply Overvoltage Test

If the DUT has multiple power supplies, each power supply pin is stressed separately. The power supply pin(s) not under test are set to the manufacturer's recommended nominal voltage (Vnom) before the power supply pin under test is stressed.

The input and I/O pin configuration during this test is the same as for the tests detailed earlier in this section. See Figure 5 for equipment hookup. The DUT is placed in the test socket, and the voltage is raised on all power supply pins to Vnom. The voltage on the power supply pin under test is then raised to the power supply overvoltage limit (1.5 Vmax).

The voltage on the power supply pin under test is returned to Vnom, and the ICC is observed to determine whether latch-up has occurred. This procedure is repeated for each power supply pin. The results are recorded on the results report form.

5-1792

Figure 5. Test 2: Power Supply Overvoltage Stress Equipment Hookup

### Test 3 and Pass/Fail Criteria

A device is considered latched up if, due to the application of a stress, the ICC current exceeds the manufacturer's maximum ICC current and remains at that level after the stress is removed. Quantitatively, the allowed current increase cannot exceed 140% of the typical current at Vmax or 10 mA, whichever is greater. For both Test 1 and Test 2, all six devices must not exhibit latch-up when stressed at the levels shown in Table 4. In addition, all six devices must pass functional and parametric testing after latch-up stressing to ensure adequate immunity to moderate electrical overstress conditions.

## Package Qualification

### Introduction

This section will document the qualification test procedures and results for the devices in the Lucent Technologies FPGA product family. The QRB determined the qualification requirements of each die in a given package. Test results are presented in Table 5 for the ATT3000 Series (0.6  $\mu$ m), in Table 6 for the ATT3000 Series (0.55  $\mu$ m), in Table 7 for the *ORCA* 1C Series, in Table 8 for the *ORCA* 2C Series of FPGAs, in Table 9 for the *ORCA* 2CxxA (5.0 V) Series, in Table 10 for the *ORCA* 2TxxA (3.3 V) Series, and in Table 11 for the ATT1700A series of EEPROMs. For more detailed qualification information, please see the qualification test procedures and results at the end of this section. ESD and latch-up tests have been done on all of the FPGA families, with varying results for each device in each package. For the ATT3000 Series, the ESD results for the human-body model (ESD-HBM) varied from >2000 V to >3500 V, and the ESD results for the charged-device model (ESD-CDM) varied from >2500 V to >3000 V. Most devices passed LU Class IV. with a few passing only LU Class III. For the 1C Series of FPGAs, both ESD-HBM and ESD-CDM passed for >2000 V, which was the highest value tested. These devices also passed LU Class IV. For the 2C Series of devices, ESD-HBM passed for >2000 V and ESD-CDM passed for >1000 V, which, again, were the highest values tested. These devices also passed LU Class IV. For the 2CxxA (5.0 V) Series of devices, ESD-HBM passed for >2000 V and ESD-CDM varied from >1000 V to >2000 V. These devices passed LU Class II. For the 2TxxA (3.3 V) Series of devices, ESD-HBM passed for >2000 V and ESD-CDM passed for >1000 V. These devices passed LU Class II with a few passing Class III.

## **Qualification Status**

### Table 5. Qualification Status of ATT3000 Series FPGAs (0.6 µm)

| Device       | Qual No. | References       | Tests Performed | Status          |

|--------------|----------|------------------|-----------------|-----------------|

| 3020-68PLCC  | —        | Q92055, Q89166   | _               | Fully Qualified |

| 3020-84PLCC  | —        | Q92055, Q89166   |                 | Fully Qualified |

| 3020-100QFP  | —        | Q90001 or Q90111 |                 | Fully Qualified |

| 3030-44PLCC  | —        | Q92055, Q89166   |                 | Fully Qualified |

| 3030-68PLCC  | —        | Q92055, Q89166   |                 | Fully Qualified |

| 3030-84PLCC  | —        | Q92055, Q89166   |                 | Fully Qualified |

| 3030-100QFP  | —        | Q90001 or Q90111 |                 | Fully Qualified |

| 3030-100TQFP | —        | Q92055           |                 | Fully Qualified |

| 3042-84PLCC  | —        | Q92055, Q89166   |                 | Fully Qualified |

| 3042-100TQFP | QRB92.51 | Q92055           | ESD, LU         | Fully Qualified |

| 3042-100QFP  | QRB93.2  | Q90001 or Q90111 | ESD, LU         | Fully Qualified |

| 3042-132PPGA | —        | Q90137           | _               | Fully Qualified |

| 3064-84PLCC  | —        | Q92055, Q89027   |                 | Fully Qualified |

| 3064-132PPGA | —        | Q90137           |                 | Fully Qualified |

| 3064-160QFP  | —        | Q89129.1, Q90140 |                 | Fully Qualified |

| 3090-84PLCC  | Q92055   | Q90148, Q89027   | LT, ESD, LU     | Fully Qualified |

| 3090-160QFP  | —        | Q89129.1, Q90140 | _               | Fully Qualified |

| 3090-175PPGA | Q92054   | Q90137           | LT, ESD, LU     | Fully Qualified |

| 3090-208SQFP | —        | MR120, Q92055    | _               | Fully Qualified |

### Table 6. Qualification Status of ATT3000 Series FPGAs (0.55 $\mu\text{m})$

| Device       | Qual No. | References     | Tests Performed | Status          |

|--------------|----------|----------------|-----------------|-----------------|

| 3020-68PLCC  | _        | Q95273, Q89166 | _               | Fully Qualified |

| 3020-84PLCC  | —        | Q95273, Q89166 | _               | Fully Qualified |

| 3020-100QFP  | —        | Q95273, Q90111 | _               | Fully Qualified |

| 3030-44PLCC  | —        | Q95273, Q89166 | _               | Fully Qualified |

| 3030-68PLCC  | —        | Q95273, Q89166 | _               | Fully Qualified |

| 3030-84PLCC  | —        | Q95273, Q89166 | _               | Fully Qualified |

| 3030-100QFP  | —        | Q95273, Q90111 | _               | Fully Qualified |

| 3030-100TQFP | —        | Q95273, Q92055 | _               | Fully Qualified |

| 3042-84PLCC  | Q95273   | MR109, Q89166  | LT, ESD, LU     | Fully Qualified |

| 3042-100QFP  | —        | Q95273, Q90111 | _               | Fully Qualified |

| 3042-100TQFP | —        | Q95273, Q92055 | _               | Fully Qualified |

| 3042-132PPGA | —        | Q95273, Q90137 | _               | Fully Qualified |

| 3064-84PLCC  | —        | Q95273, Q89027 | _               | Fully Qualified |

| 3064-132PPGA | —        | Q95273, Q90137 | _               | Fully Qualified |

| 3064-160QFP  | —        | Q95273, Q90140 | _               | Fully Qualified |

| 3090-84PLCC  | Q96098   | Q95273, Q89027 | ESD, LU         | Fully Qualified |

| 3090-160QFP  | —        | Q95273, Q90140 | _               | Fully Qualified |

| 3090-175PPGA | —        | Q95273, Q90137 | _               | Fully Qualified |

| 3090-208SQFP | Q96099   | Q95273, MR120  | ESD, LU         | Fully Qualified |

### Table 7. Qualification Status of ORCA 1C Series FPGAs

| Device          | Qual No. | References       | Tests Performed | Status          |

|-----------------|----------|------------------|-----------------|-----------------|

| ATT1C03-84PLCC  |          | Q92167, Q92168   | _               | Fully Qualified |

| ATT1C03-100TQFP | _        | Q92167, QRB92.51 | _               | Fully Qualified |

| ATT1C03-132BQFP | —        | Q92167, Q92168   | —               | Fully Qualified |

| ATT1C03-208SQFP |          | Q92167, Q92168   | —               | Fully Qualified |

| ATT1C03-225CPGA |          | Q92167, Q92161   | _               | Fully Qualified |

| ATT1C03-225PPGA |          | Q92054, Q92167   | —               | Fully Qualified |

| ATT1C05-84PLCC  |          | Q92167, Q92168   | _               | Fully Qualified |

| ATT1C05-100TQFP |          | Q92167, QRB92.51 | —               | Fully Qualified |

| ATT1C05-132BQFP | —        | Q92167, Q92168   | —               | Fully Qualified |

| ATT1C05-208SQFP |          | Q92167, Q92168   | —               | Fully Qualified |

| ATT1C05-225PPGA | _        | Q92054, Q92167   | —               | Fully Qualified |

| ATT1C05-225CPGA |          | Q92167, Q92161   | —               | Fully Qualified |

| ATT1C05-240SQFP | Q92167   | —                | All major tests | Fully Qualified |

| ATT1C07-208SQFP |          | Q92167, Q92168   | —               | Fully Qualified |

| ATT1C07-240SQFP |          | Q92167, Q92168   | —               | Fully Qualified |

| ATT1C07-280CPGA |          | Q92167, Q92161   | —               | Fully Qualified |

| ATT1C07-304SQFP | Q94044   | Q92167, Q92168   | ESD             | Fully Qualified |

| ATT1C09-208SQFP | —        | Q92167, MR120    | —               | Fully Qualified |

| ATT1C09-240SQFP | —        | Q92167, MR141    | —               | Fully Qualified |

| ATT1C09-304SQFP |          | Q94044           | _               | Fully Qualified |

### Table 8. Qualification Status of ORCA 2C Series FPGAs

| Device              | Qual No. | References            | Tests Performed                        | Status          |

|---------------------|----------|-----------------------|----------------------------------------|-----------------|

| ATT2C04-84PLCC      | Q94291   | Q93234, T92222, MR109 | None                                   | Fully Qualified |

| ATT2C04-144TQFP     | —        | Q93234, Q93181        | None                                   | Fully Qualified |

| ATT2C04-160QFP      | Q95319   | Q93234, MR119         | ESD, LU                                | Fully Qualified |

| ATT2C04-208SQFP     | —        | Q93234, Q94124        | None                                   | Fully Qualified |

| ATT2C06-84PLCC      | —        | Q93234, T92222        | None                                   | Fully Qualified |

| ATT2C06-144TQFP     | —        | Q93234, Q93181        | None                                   | Fully Qualified |

| ATT2C06-160QFP      | —        | Q93234, MR119, Q95319 | None                                   | Fully Qualified |

| ATT2C06-208SQFP     | —        | Q93234, Q94124        | None                                   | Fully Qualified |

| ATT2C06-240SQFP     | —        | Q93234                | None                                   | Fully Qualified |

| ATT2C08-160QFP      | —        | Q93234, MR119, Q95319 | None                                   | Fully Qualified |

| ATT2C08-208SQFP     | —        | Q93234, Q94124        | None                                   | Fully Qualified |

| ATT2C08-240SQFP     |          | Q93234                | None                                   | Fully Qualified |

| ATT2C08-256PBGA     | —        | Q96068, Q95013        | None                                   | Fully Qualified |

| ATT2C08-304SQFP     | —        | Q93234, Q94046        | None                                   | Fully Qualified |

| ATT2C10-160QFP      | —        | Q93234, MR119, Q95319 | None                                   | Fully Qualified |

| ATT2C10-208SQFP     | —        | Q93234, Q94124        | None                                   | Fully Qualified |

| ATT2C10-240SQFP     | —        | Q93234                | None                                   | Fully Qualified |

| ATT2C10-256PBGA     | Q96068   | Q95013                | TC, SB, TS, PD, ESD,<br>LU             | Fully Qualified |

| ATT2C10-304SQFP     | Q95041   | Q94046                | SB, X-ray                              | Fully Qualified |

| ATT2C12-208SQFP     | —        | Q93234, Q94124        | None                                   | Fully Qualified |

| ATT2C12-240SQFP     | —        | Q93234                | None                                   | Fully Qualified |

| ATT2C12-256PBGA     | —        | Q96068, Q95013        | None                                   | Fully Qualified |

| ATT2C12-304SQFP     | —        | Q95041                | None                                   | Fully Qualified |

| ATT2C12-364CPGA     | —        | Q93231                | None                                   | Fully Qualified |

| ATT2C15-208SQFP     | Q94290   | Q93234, Q94124        | ESD, LU                                | Fully Qualified |

| ATT2C15-240SQFP     | Q93234   | Q94046                | LT, CL, BH, SB, TC, TS,<br>ESD, LU     | Fully Qualified |

| ATT2C15-304SQFP     | Q94046   | _                     | CL, BH, SB, TC, ESD,<br>LU             | Fully Qualified |

| ATT2C15-364CPGA     | Q93231   | Q94046, Q94290        | LT, TC, TS, SQ, ESD, LU                | Fully Qualified |

| ATT2C26-208SQFP-PQ2 | _        | Q94227                | None                                   | Fully Qualified |

| ATT2C26-240SQFP-PQ2 | _        | Q94227, Q95007        | None                                   | Fully Qualified |

| ATT2C26-304SQFP-PQ2 | Q94227   | _                     | LT, CL, BH, SB, TC, TS,<br>ESD, LU, PD | Fully Qualified |

| ATT2C40-208SQFP-PQ2 | QRB95.17 | Q95007                | PD                                     | Fully Qualified |

| ATT2C40-240SQFP-PQ2 | Q95007   | Q94227                | CL, BH, TC, PD, ESD,<br>LU             | Fully Qualified |

| ATT2C40-304SQFP-PQ2 |          | Q95007, Q94227        | None                                   | Fully Qualified |

### Table 9. Qualification Status of ORCA 2CxxA (5.0 V) Series FPGAs

| Device           | Qual No.              | References                             | Tests Performed                           | Status          |

|------------------|-----------------------|----------------------------------------|-------------------------------------------|-----------------|

| OR2C04A-84PLCC   | Q96235.2              | Q97176, EE97260, Q91016.3              | ESD, LU                                   | Fully Qualified |

| OR2C04A-100TQFP  | Q96236.1              | T96005, MR221                          | ESD, LU                                   | Fully Qualified |

| OR2C04A-144TQFP  | _                     | Q96365.1, MR225                        | None                                      | Fully Qualified |

| OR2C04A-160QFP   |                       | T96005, MR217                          | None                                      | Fully Qualified |

| OR2C04A-208SQFP  | _                     | T96005, MR229                          | None                                      | Fully Qualified |

| OR2C06A-84PLCC   | —                     | Q97176, EE97260, Q91016.3,<br>Q96235.2 | None                                      | Fully Qualified |

| OR2C06A-100TQFP  |                       | T96005, MR221                          | None                                      | Fully Qualified |

| OR2C06A-144TQFP  | _                     | Q96365.1, MR225                        | None                                      | Fully Qualified |

| OR2C06A-160QFP   |                       | T96005, MR217                          | None                                      | Fully Qualified |

| OR2C06A-208SQFP  |                       | T96005, MR229                          | None                                      | Fully Qualified |

| OR2C06A-240SQFP  |                       | EE95210.1, MR232                       | None                                      | Fully Qualified |

| OR2C06A-256PBGA  |                       | T95276.1, Q96068.1                     | None                                      | Fully Qualified |

| OR2C08A-84PLCC   | —                     | Q97176, EE97260, Q91016.3,<br>Q96235.2 | None                                      | Fully Qualified |

| OR2C08A-160QFP   | _                     | T96005, MR217                          | None                                      | Fully Qualified |

| OR2C08A-208SQFP  | _                     | T96005, MR229                          | None                                      | Fully Qualified |

| OR2C08A-240SQFP  | _                     | EE95210.1, MR232                       | None                                      | Fully Qualified |

| OR2C08A-256PBGA  |                       | T95276.1, Q96068.1                     | None                                      | Fully Qualified |

| OR2C10A-84PLCC   | —                     | Q97176, EE97260, Q91016.3,<br>Q96235.2 | None                                      | Fully Qualified |

| OR2C10A-160QFP   | _                     | T96005, MR217                          | None                                      | Fully Qualified |

| OR2C10A-208SQFP  | _                     | T96005, MR229                          | None                                      | Fully Qualified |

| OR2C10A-240SQFP  | _                     | EE95210.1, MR232                       | None                                      | Fully Qualified |

| OR2C10A-256PBGA  | _                     | T95276.1, Q96068.1                     | None                                      | Fully Qualified |

| OR2C10A-352PBGA  |                       | T95276.1                               | None                                      | Fully Qualified |

| OR2C12A-84PLCC   | —                     | Q97176, EE97260, Q91016.3,<br>Q96235.2 | None                                      | Fully Qualified |

| OR2C12A-208SQFP  | _                     | T96005, MR229                          | None                                      | Fully Qualified |

| OR2C12A-240SQFP  | _                     | EE95210.1, MR232                       | None                                      | Fully Qualified |

| OR2C12A-256PBGA  | _                     | T95276.1, Q96068.1                     | None                                      | Fully Qualified |

| OR2C12A-304SQFP  | _                     | EE95210.1, MR233                       | None                                      | Fully Qualified |

| OR2C12A-352PBGA  |                       | T95276.1                               | None                                      | Fully Qualified |

| OR2C15A-84PLCC   | —                     | Q97176, EE97260, Q91016.3,<br>Q96235.2 | None                                      | Fully Qualified |

| OR2C15A-208SQFP  | T96005.1 <sup>1</sup> | T96005, MR229                          | LT, CL, BH, SB, TC,<br>TS, XR, ESD, LU    | Fully Qualified |

| OR2C15A-208SQFP2 | —                     | EE95210.1, Q96406, MR243               | None                                      | Fully Qualified |

| OR2C15A-240SQFP  | —                     | EE95210.1, MR232                       | None                                      | Fully Qualified |

| OR2C15A-240SQFP2 | —                     | EE95210.1, MR244                       | None                                      | Fully Qualified |

| OR2C15A-256PBGA  | —                     | T95276.1, Q96068.1                     | None                                      | Fully Qualified |

| OR2C15A-304SQFP  | Q97037 <sup>2</sup>   | EE95210.1, T96005, MR233               | LT, CL, BH, C8PRE,<br>SB, TC, TS, XR, ESD | Fully Qualified |

1. Qual No. T96005.1 was created to conform with the package's code marking; therefore, tests performed are referenced from Qual No. T96005.

2. Qual No. Q97037 was created to conform with the package's code marking; therefore, tests performed are referenced from Qual No. EE95210.1.

### Table 9. Qualification Status of ORCA 2CxxA (5.0 V) Series FPGAs (continued)

| Device           | Qual No.              | References                            | <b>Tests Performed</b>                           | Status          |

|------------------|-----------------------|---------------------------------------|--------------------------------------------------|-----------------|

| OR2C15A-352PBGA  | T95276.2 <sup>3</sup> | T95276.1, Q95013, T96005              | LT, CL, BH, C6PRE,<br>SB, TC, TS, PD, XR,<br>ESD | Fully Qualified |

| OR2C15A-432EBGA  | —                     | Q96284.2, T95276.1                    | None                                             | Fully Qualified |

| OR2C26A-208SQFP2 | —                     | EE95210.1, MR243                      | None                                             | Fully Qualified |

| OR2C26A-240SQFP2 | —                     | EE95210.1, MR244                      | None                                             | Fully Qualified |

| OR2C26A-304SQFP2 | —                     | EE95210.1, MR245                      | None                                             | Fully Qualified |

| OR2C26A-352PBGA  | —                     | T95276.1                              | None                                             | Fully Qualified |

| OR2C26A-432EBGA  | —                     | Q96284.2, T95276.1                    | None                                             | Fully Qualified |

| OR2C40A-208SQFP2 | —                     | EE95210.1, Q95007, Q95204,<br>MR243   | None                                             | Fully Qualified |

| OR2C40A-240SQFP2 | _                     | EE95210.1, Q95007, MR244              | None                                             | Fully Qualified |

| OR2C40A-304SQFP2 | -                     | EE95210.1, Q95007,<br>Q94227.1, MR245 | None                                             | Fully Qualified |

| OR2C40A-432EBGA  | —                     | Q96284.2, T95276.1                    | None                                             | Fully Qualified |

| OR2C40A-600EBGA  | _                     | Q97048.1, Q96284.2                    | None                                             | In Process      |

1. Qual No. T96005.1 was created to conform with the package's code marking; therefore, tests performed are referenced from Qual No. T96005.

2. Qual No. Q97037 was created to conform with the package's code marking; therefore, tests performed are referenced from Qual No. EE95210.1.

3. Qual No. T95276.2 was created to conform with the package's code marking; therefore, tests performed are referenced from Qual No. T95276.1.

### Table 10. Qualification Status of ORCA 2TxxA (3.3 V) Series FPGAs

| Device          | Qual No. | References                                           | <b>Tests Performed</b>                    | Status          |

|-----------------|----------|------------------------------------------------------|-------------------------------------------|-----------------|

| OR2T04A-84PLCC  | Q96298.2 | Q91016.3, EE97260                                    | ESD, LU                                   | Fully Qualified |

| OR2T04A-100TQFP | Q96299.2 | Q96120, EE97260, MR221                               | Q96120, EE97260, MR221 ESD, LU Fully      |                 |

| OR2T04A-144TQFP | _        | Q96365.1, EE97260, MR225                             | None                                      | Fully Qualified |

| OR2T04A-160QFP  | —        | T96005, Q96270, MR217                                | None                                      | Fully Qualified |

| OR2T04A-208SQFP | _        | T96005, Q97193, Q97102.1, None Fully Q97053.1, MR229 |                                           | Fully Qualified |

| OR2T06A-84PLCC  | —        | Q91016.3, EE97260, Q96298.2                          | Q91016.3, EE97260, Q96298.2 None Fully Qu |                 |

| OR2T06A-100TQFP | _        | Q96120, EE97260, Q96299.2, MR221                     | None                                      | Fully Qualified |

| OR2T06A-144TQFP | —        | Q96365.1, EE97260, MR225                             | None                                      | Fully Qualified |

| OR2T06A-160QFP  | —        | T96005, Q96270, MR217                                | None                                      | Fully Qualified |

| OR2T06A-208SQFP | -        | T96005, Q97193, Q97102.1,<br>Q97053.1, MR229         | None                                      | Fully Qualified |

| OR2T06A-240SQFP | —        | EE95210.1, EE97260, MR232                            | None                                      | Fully Qualified |

| OR2T06A-256PBGA | _        |                                                      |                                           | Fully Qualified |

| OR2T08A-84PLCC  | —        | Q91016.3, EE97260, Q96298.2                          | None                                      | Fully Qualified |

| OR2T08A-160QFP  | —        | T96005, Q96270, MR217                                | None Fully Qual                           |                 |

| OR2T08A-208SQFP | -        | T96005, Q97193, Q97102.1,<br>Q97053.1, MR229         | None                                      | Fully Qualified |

| OR2T08A-240SQFP | —        | EE95210.1, EE97260, MR232                            | None                                      | Fully Qualified |

| OR2T08A-256PBGA | —        | T95276.1, EE97260, Q97100,<br>Q96068.1               | None                                      | Fully Qualified |

| OR2T10A-84PLCC  | —        | Q91016.3, EE97260, Q96298.2                          | None                                      | Fully Qualified |

| OR2T10A-160QFP  | —        | T96005, Q96270, MR217                                | None                                      | Fully Qualified |

| OR2T10A-208SQFP | —        | T96005, Q97193, Q97102.1,<br>Q97053.1, MR229         | None                                      | Fully Qualified |

| OR2T10A-240SQFP |          | EE95210.1, EE97260, MR232                            | None                                      | Fully Qualified |

| OR2T10A-256PBGA | -        | T95276.1, EE97260, Q97100,<br>Q96068.1               | None                                      | Fully Qualified |

| OR2T10A-352PBGA | _        | T95276.1, EE97260                                    | None                                      | Fully Qualified |

| OR2T12A-84PLCC  | —        | Q91016.3, EE97260, Q96298.2                          | None                                      | Fully Qualified |

| OR2T12A-208SQFP | -        | Q97053.1, MR229                                      |                                           | Fully Qualified |

| OR2T12A-240SQFP | _        | EE95210.1, EE97260, MR232                            | None                                      | Fully Qualified |

| OR2T12A-256PBGA | _        | T95276.1, EE97260, Q97100,<br>Q96068.1               | None Fully Qualifie                       |                 |

| OR2T12A-352PBGA | —        | T95276.1, EE97260                                    |                                           |                 |

| OR2T15A-84PLCC  |          | Q91016.3, EE97260, Q96298.2                          | None Fully Quali                          |                 |

| OR2T15A-208SQFP | _        | T96005, Q97193, Q97102.1,<br>Q97053.1, MR229         | 02.1, None Fully Qualifie                 |                 |

| OR2T15A-240SQFP | —        | EE95210.1, EE97260, MR232                            | None Fully Qualified                      |                 |

| OR2T15A-256PBGA |          |                                                      |                                           | Fully Qualified |

| OR2T15A-352PBGA |          | T95276.1, EE97260 None Fully Qua                     |                                           | Fully Qualified |

| OR2T15A-432EBGA | —        | Q96284.2, EE97260                                    | None                                      | Fully Qualified |

### Table 10. Qualification Status of ORCA 2TxxA (3.3 V) Series FPGAs (continued)

| Device           | Qual No. | References                                   | Tests Performed                                                         | Status          |