# TPS1100, TPS1100Y SINGLE P-CHANNEL ENHANCEMENT-MODE MOSFETS

SLVS078C - DECEMBER 1993 - REVISED AUGUST 1995

- Low  $r_{DS(on)} \dots 0.18 \Omega$  Typ at  $V_{GS} = -10 \text{ V}$

- 3 V Compatible

- Requires No External V<sub>CC</sub>

- TTL and CMOS Compatible Inputs

- $V_{GS(th)} = -1.5 \text{ V Max}$

- Available in Ultrathin TSSOP Package (PW)

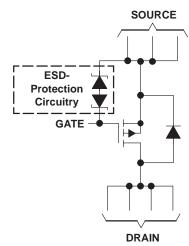

- ESD Protection Up to 2 kV Per MIL-STD-883C, Method 3015

#### description

The TPS1100 P-channel is single a enhancement-mode MOSFET. The device has been optimized for 3-V or 5-V power distribution in battery-powered systems by means of Texas Instruments LinBiCMOS™ process. With a maximum V<sub>GS(th)</sub> of -1.5 V and an I<sub>DSS</sub> of only 0.5 μA, the TPS1100 is the ideal high-side switch for low-voltage, portable battery-management systems where maximizing battery life is a primary concern. The low r<sub>DS(on)</sub> and excellent ac characteristics (rise time 10 ns typical) make the TPS1100 the logical choice for low-voltage switching applications such as power switches for pulse-width-modulated (PWM) controllers or motor/bridge drivers.

The ultrathin thin shrink small-outline package or TSSOP (PW) version with its smaller footprint and reduction in height fits in places where other P-channel MOSFETs cannot. The size advantage is especially important where board real estate is at a premium and height restrictions do not allow for a small-outline integrated circuit (SOIC) package.

#### schematic

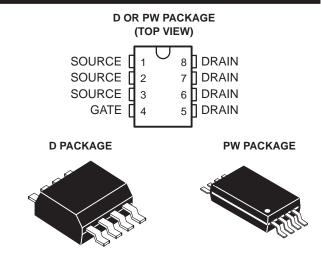

NOTE A: For all applications, all source pins should be connected and all drain pins should be connected.

#### **AVAILABLE OPTIONS**

|               | PACKAGED I           | CHIP FORM          |          |

|---------------|----------------------|--------------------|----------|

| TA            | SMALL OUTLINE<br>(D) | PLASTIC DIP<br>(P) | (Y)      |

| -40°C to 85°C | TPS1100D             | TPS1100PWLE        | TPS1100Y |

The D package is available taped and reeled. Add an R suffix to device type (e.g., TPS1100DR). The PW package is available only left-end taped and reeled (indicated by the LE suffix on the device type; e.g., TPS1100PWLE). The chip form is tested at 25°C.

Caution. This device contains circuits to protect its inputs and outputs against damage due to high static voltages or electrostatic fields. These circuits have been qualified to protect this device against electrostatic discharges (ESD) of up to 2 kV according to MIL-STD-883C, Method 3015; however, it is advised that precautions be taken to avoid application of any voltage higher than maximum-rated voltages to these high-impedance circuits.

LinBiCMOS is a trademark of Texas Instruments Incorporated.

SLVS078C - DECEMBER 1993 - REVISED AUGUST 1995

## description (continued)

Such applications include notebook computers, personal digital assistants (PDAs), cellular telephones, and PCMCIA cards. For existing designs, the D-packaged version has a pinout common with other p-channel MOSFETs in SOIC packages.

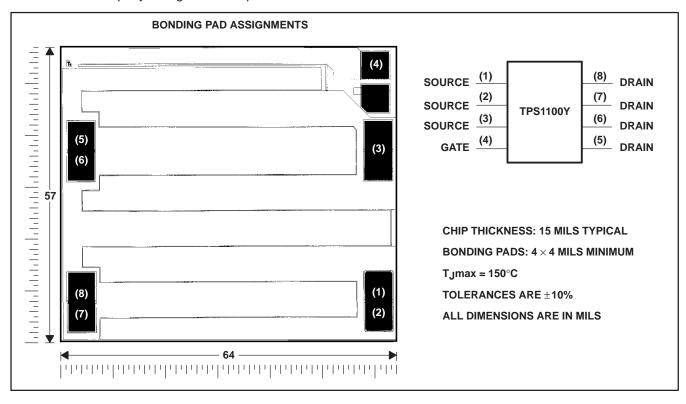

## **TPS1100Y** chip information

This chip, when properly assembled, displays characteristics similar to the TPS1100. Thermal compression or ultrasonic bonding may be used on the doped aluminum bonding pads. The chips may be mounted with conductive epoxy or a gold-silicon preform.

SLVS078C - DECEMBER 1993 - REVISED AUGUST 1995

# absolute maximum ratings over operating free-air temperature (unless otherwise noted)†

|                                                                                |                                        |             |                        |       | UNIT |  |

|--------------------------------------------------------------------------------|----------------------------------------|-------------|------------------------|-------|------|--|

| Drain-to-source voltage, V <sub>DS</sub>                                       |                                        |             |                        | -15   | V    |  |

| Gate-to-source voltage, VGS                                                    |                                        |             |                        |       |      |  |

|                                                                                |                                        | D package   | T <sub>A</sub> = 25°C  | ±0.41 |      |  |

|                                                                                | \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ |             | T <sub>A</sub> = 125°C | ±0.28 |      |  |

|                                                                                | $V_{GS} = -2.7 \text{ V}$              | PW package  | T <sub>A</sub> = 25°C  | ±0.4  |      |  |

|                                                                                |                                        | 1 W package | T <sub>A</sub> = 125°C | ±0.23 |      |  |

|                                                                                |                                        | D package   | T <sub>A</sub> = 25°C  | ±0.6  |      |  |

|                                                                                | V <sub>GS</sub> = -3 V                 | Браскаде    | T <sub>A</sub> = 125°C | ±0.33 | A    |  |

|                                                                                | VGS = -3 V                             | PW package  | T <sub>A</sub> = 25°C  | ±0.53 |      |  |

| Continuous drain current (T <sub>J</sub> = 150°C), I <sub>D</sub> <sup>‡</sup> |                                        |             | T <sub>A</sub> = 125°C | ±0.27 |      |  |

| Continuous drain current (1) = 150 G), ID                                      |                                        | D package   | T <sub>A</sub> = 25°C  | ±1    |      |  |

|                                                                                | V <sub>GS</sub> = -4.5 V               |             | T <sub>A</sub> = 125°C | ±0.47 |      |  |

|                                                                                |                                        | PW package  | $T_A = 25^{\circ}C$    | ±0.81 |      |  |

|                                                                                |                                        |             | T <sub>A</sub> = 125°C | ±0.37 |      |  |

|                                                                                |                                        | D package   | T <sub>A</sub> = 25°C  | ±1.6  |      |  |

|                                                                                | V <sub>GS</sub> = -10 V                | Браскаде    | T <sub>A</sub> = 125°C | ±0.72 |      |  |

|                                                                                | 1 4 6 5 - 10 4                         | PW package  | T <sub>A</sub> = 25°C  | ±1.27 |      |  |

|                                                                                |                                        | 1 W package | T <sub>A</sub> = 125°C | ±0.58 |      |  |

| Pulsed drain current, ID <sup>‡</sup>                                          |                                        |             | T <sub>A</sub> = 25°C  | ±7    | Α    |  |

| Continuous source current (diode conduction), IS                               | -1                                     | Α           |                        |       |      |  |

| Storage temperature range, T <sub>Stg</sub>                                    | -55 to 150                             | °C          |                        |       |      |  |

| Operating junction temperature range, T <sub>J</sub>                           | -40 to 150                             | °C          |                        |       |      |  |

| Operating free-air temperature range, TA                                       | -40 to 125                             | °C          |                        |       |      |  |

| Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds                   | 260                                    | °C          |                        |       |      |  |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### **DISSIPATION RATING TABLE**

| PACKAGE | $T_{\mbox{\scriptsize A}} \le 25^{\circ}\mbox{\scriptsize C}$ POWER RATING | DERATING FACTOR <sup>‡</sup><br>ABOVE T <sub>A</sub> = 25°C | T <sub>A</sub> = 70°C<br>POWER RATING | T <sub>A</sub> = 85°C<br>POWER RATING | T <sub>A</sub> = 125°C<br>POWER RATING |

|---------|----------------------------------------------------------------------------|-------------------------------------------------------------|---------------------------------------|---------------------------------------|----------------------------------------|

| D       | 791 mW                                                                     | 6.33 mW/°C                                                  | 506 mW                                | 411 mW                                | 158 mW                                 |

| PW      | 504 mW                                                                     | 4.03 mW/°C                                                  | 323 mW                                | 262 mW                                | 101 mW                                 |

<sup>‡</sup> Maximum values are calculated using a derating factor based on  $R_{\theta JA} = 158^{\circ}\text{C/W}$  for the D package and  $R_{\theta JA} = 248^{\circ}\text{C/W}$  for the PW package. These devices are mounted on an FR4 board with no special thermal considerations when tested.

<sup>‡</sup> Maximum values are calculated using a derating factor based on R<sub>θJA</sub> = 158°C/W for the D package and R<sub>θJA</sub> = 248°C/W for the PW package. These devices are mounted on a FR4 board with no special thermal considerations.

# TPS1100, TPS1100Y SINGLE P-CHANNEL ENHANCEMENT-MODE MOSFETS

SLVS078C - DECEMBER 1993 - REVISED AUGUST 1995

# electrical characteristics at $T_J = 25^{\circ}C$ (unless otherwise noted)

#### static

| PARAMETER           |                                                             | TEST CONDITIONS                                   |                               | TPS1100                |     | TPS1100Y |       |     | UNIT  |     |            |

|---------------------|-------------------------------------------------------------|---------------------------------------------------|-------------------------------|------------------------|-----|----------|-------|-----|-------|-----|------------|

|                     |                                                             | 1E31 CONDITIONS                                   |                               |                        | MIN | TYP      | MAX   | MIN | TYP   | MAX | ONIT       |

| V <sub>GS(th)</sub> | Gate-to-source threshold voltage                            | $V_{DS} = V_{GS}$ , $I_{D} = -250 \mu\text{A}$    |                               |                        | -1  | -1.25    | -1.50 |     | -1.25 |     | V          |

| V <sub>SD</sub>     | Source-to-drain voltage<br>(diode-forward<br>voltage)†      | I <sub>S</sub> = -1 A,                            | = -1 A, V <sub>GS</sub> = 0 V |                        |     | -0.9     |       |     | -0.9  |     | V          |

| I <sub>GSS</sub>    | Reverse gate current,<br>drain short circuited to<br>source | V <sub>DS</sub> = 0 V,                            | V <sub>GS</sub> = -12 V       |                        |     |          | ±100  |     |       |     | nA         |

| Inno                | Zero-gate-voltage drain                                     | V <sub>DS</sub> = -12 V,                          | \\oo = 0 \\                   | T <sub>J</sub> = 25°C  |     |          | -0.5  |     |       |     | μΑ         |

| IDSS                | current                                                     | VDS = -12 v,                                      | VGS - 0 V                     | T <sub>J</sub> = 125°C |     |          | -10   |     |       |     | μΑ         |

|                     |                                                             | $V_{GS} = -10 \text{ V}$                          | $I_D = -1.5 A$                |                        |     | 180      |       |     | 180   |     |            |

|                     | Static drain-to-source on-state resistance†                 | $V_{GS} = -4.5 \text{ V}$                         | $I_D = -0.5 A$                |                        |     | 291      | 400   |     | 291   |     | <b>~</b> 0 |

| rDS(on)             |                                                             | $V_{GS} = -3 V$                                   | I- 02A                        |                        |     | 476      | 700   |     | 476   |     | mΩ         |

|                     |                                                             | $V_{GS} = -3 \text{ V}$ $V_{GS} = -2.7 \text{ V}$ | ID = -0.2 A                   |                        |     | 606      | 850   |     | 606   |     |            |

| 9fs                 | Forward transconductance†                                   | $V_{DS} = -10 \text{ V},$                         | I <sub>D</sub> = -2 A         |                        |     | 2.5      |       |     | 2.5   |     | S          |

<sup>†</sup> Pulse test: pulse duration ≤ 300 μs, duty cycle ≤ 2%

# dynamic

| PARAMETER       |                                       | TEST CONDITIONS                                |                                            |                 | TPS1100, TPS1100Y |      |     | UNIT |

|-----------------|---------------------------------------|------------------------------------------------|--------------------------------------------|-----------------|-------------------|------|-----|------|

|                 |                                       |                                                |                                            |                 | MIN               | TYP  | MAX | UNIT |

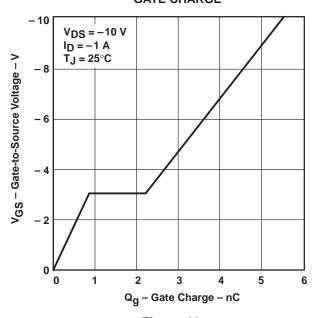

| Qg              | Total gate charge                     |                                                |                                            |                 |                   | 5.45 |     |      |

| Qgs             | Gate-to-source charge                 | $V_{DS} = -10 \text{ V},$                      | $V_{GS} = -10 \text{ V},$                  | $I_{D} = -1 A$  |                   | 0.87 |     | nC   |

| Q <sub>gd</sub> | Gate-to-drain charge                  |                                                |                                            |                 |                   | 1.4  |     |      |

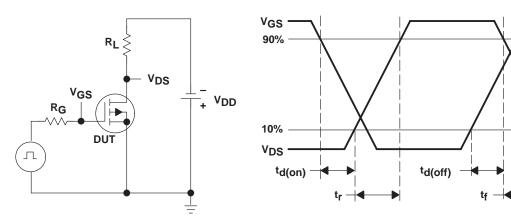

| td(on)          | Turn-on delay time                    |                                                | $R_L = 10 \Omega$ ,<br>See Figures 1 and 2 | $I_{D} = -1 A,$ |                   | 4.5  |     | ns   |

| td(off)         | Turn-off delay time                   | $V_{DD} = -10 \text{ V},$<br>$R_G = 6 \Omega,$ |                                            |                 |                   | 13   |     | ns   |

| t <sub>r</sub>  | Rise time                             |                                                |                                            |                 |                   | 10   |     |      |

| t <sub>f</sub>  | Fall time                             |                                                |                                            |                 |                   | 2    |     | ns   |

| trr(SD)         | Source-to-drain reverse recovery time | I <sub>F</sub> = 5.3 A,                        | di/dt = 100 A/μs                           |                 |                   | 16   |     |      |

0 V

## PARAMETER MEASUREMENT INFORMATION

Figure 1. Switching-Time Test Circuit

Figure 2. Switching-Time Waveforms

## **TYPICAL CHARACTERISTICS**

# **Table of Graphs**

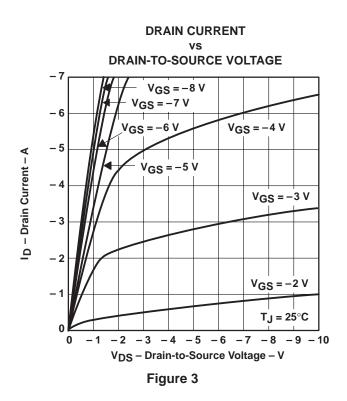

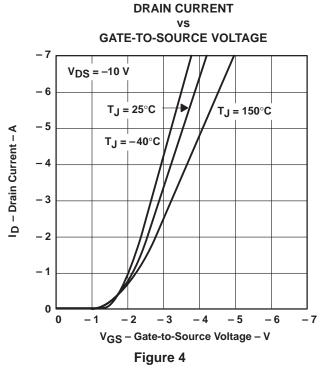

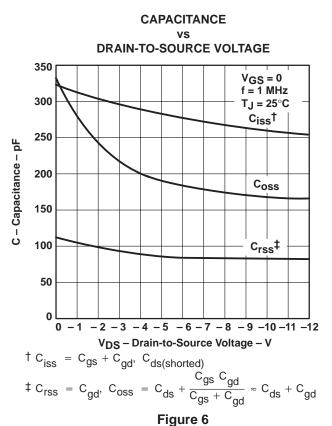

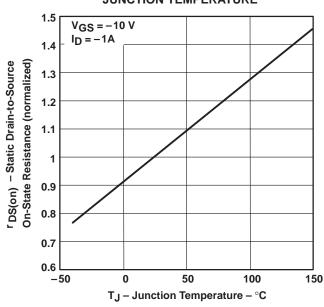

|                                                         |                            | FIGURE |

|---------------------------------------------------------|----------------------------|--------|

| Drain current                                           | vs Drain-to-source voltage | 3      |

| Drain current                                           | vs Gate-to-source voltage  | 4      |

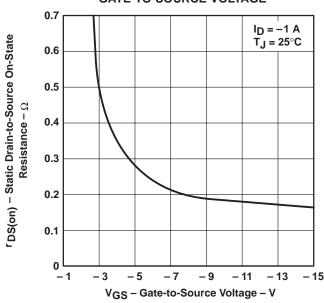

| Static drain-to-source on-state resistance              | vs Drain current           | 5      |

| Capacitance                                             | vs Drain-to-source voltage | 6      |

| Static drain-to-source on-state resistance (normalized) | vs Junction temperature    | 7      |

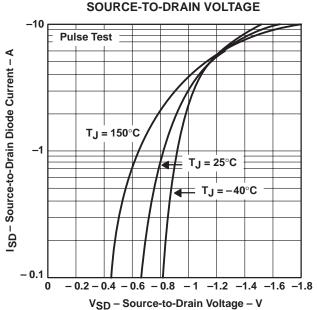

| Source-to-drain diode current                           | vs Source-to-drain voltage | 8      |

| Static drain-to-source on-state resistance              | vs Gate-to-source voltage  | 9      |

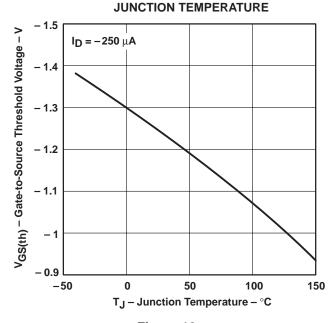

| Gate-to-source threshold voltage                        | vs Junction temperature    | 10     |

| Gate-to-source voltage                                  | vs Gate charge             | 11     |

#### **TYPICAL CHARACTERISTICS**

# **DRAIN CURRENT** 0.7 T<sub>J</sub> = 25°C 0.6 r DS(on) - Static Drain-to-Source $V_{GS} = -2.7 V_{GS}$ On-State Resistance – $\Omega$ 0.5 $V_{GS} = -3 V$ 0.4 $V_{GS} = -4.5 V$ 0.3 V<sub>GS</sub> = -10 V 0.2 0.1 - 0.1 - 10 ID - Drain Current - A

STATIC DRAIN-TO-SOURCE ON-STATE RESISTANCE

Figure 5

#### TYPICAL CHARACTERISTICS

# STATIC DRAIN-TO-SOURCE ON-STATE RESISTANCE (NORMALIZED)

# JUNCTION TEMPERATURE

Figure 7

# SOURCE-TO-DRAIN DIODE CURRENT VS

Figure 8

# STATIC DRAIN-TO-SOURCE ON-STATE RESISTANCE

# GATE-TO-SOURCE VOLTAGE

Figure 9

# GATE-TO-SOURCE THRESHOLD VOLTAGE vs

Figure 10

## TYPICAL CHARACTERISTICS

#### GATE-TO-SOURCE VOLTAGE vs GATE CHARGE

#### THERMAL INFORMATION

#### **DRAIN CURRENT DRAIN-TO-SOURCE VOLTAGE** 100 Single Pulse 0.001 s See Note A $Z_{\theta JA}$ – Transient Junction-to-Ambient 0.01 s Thermal Impedance – °C/W I<sub>D</sub> - Drain Current - A 10 0.1 s 10 s 0.1 DC T」= 150°C TA = 25°C 0.1 -0.0010.001 -0.1-10 - 100 V<sub>DS</sub> - Drain-to-Source Voltage - V Figure 12

# TRANSIENT JUNCTION-TO-AMBIENT THERMAL IMPEDANCE VS PULSE DURATION Single Pulse See Note A 10 0.1 0.001 0.01 1 1 10 t<sub>W</sub> - Pulse Duration - s

NOTE A: Values are for the D package and are FR4-board mounted only.

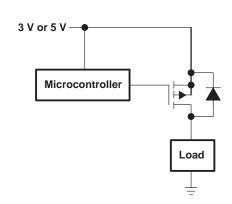

#### **APPLICATION INFORMATION**

Figure 13

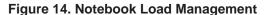

Figure 15. Cellular Phone Output Drive

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1998, Texas Instruments Incorporated