# L6563 L6563A

# Advanced transition-mode PFC controller

## Features

- Very precise adjustable output overvoltage protection

- Tracking boost function

- Protection against feedback loop failure (Latched shutdown)

- Interface for cascaded converter's PWM controller

- Input voltage feedforward (1/V<sup>2</sup>)

- Inductor saturation detection (L6563 only)

- Remote ON/OFF control

- Low (≤ 90µA) start-up current

- 5mA max. quiescent current

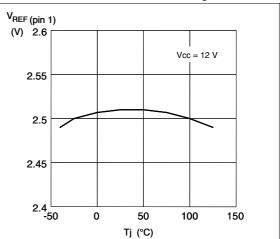

- 1.5% (@ T<sub>J</sub> = 25°C) internal reference voltage

- -600/+800 mA totem pole gate driver with active pull-down during UVLO

- SO14 package

# **Applications**

PFC pre-regulators for:

- HI-END AC-DC adapter/charger

- Desktop PC, server, WEB server

- IEC61000-3-2 OR JEIDA-MITI compliant SMPS, in excess of 350W

#### Table 1. Device summary

| Part number | Package | Packaging   |

|-------------|---------|-------------|

| L6563       | SO-14   | Tube        |

| L6563TR     | SO-14   | Tape & Reel |

| L6563A      | SO-14   | Tube        |

| L6563ATR    | SO-14   | Tape & Reel |

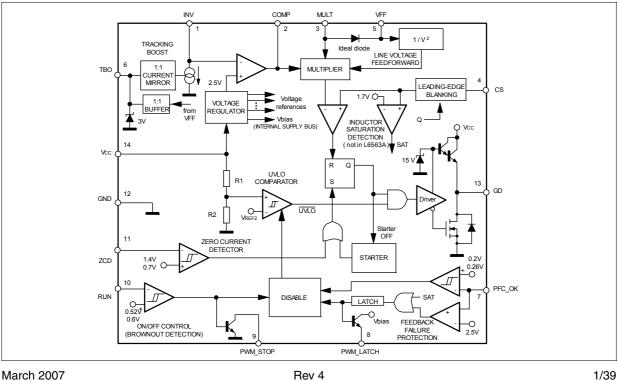

#### Figure 1. Block diagram

# Contents

| 1 | Desc | cription                                      |

|---|------|-----------------------------------------------|

|   | 1.1  | Pin connection                                |

|   | 1.2  | Pin description                               |

| 2 | Abso | olute maximum ratings6                        |

| 3 | Ther | mal data                                      |

| 4 | Elec | trical characteristics7                       |

| 5 | Турі | cal electrical performance 11                 |

| 6 | App  | lication information                          |

|   | 6.1  | Overvoltage protection                        |

|   | 6.2  | Feedback Failure Protection (FFP) 18          |

|   | 6.3  | Voltage Feedforward                           |

|   | 6.4  | THD optimizer circuit                         |

|   | 6.5  | Tracking Boost function                       |

|   | 6.6  | Inductor saturation detection (L6563 only) 27 |

|   | 6.7  | Power management/housekeeping functions       |

|   | 6.8  | Summary of L6563/A idle states                |

| 7 | Appl | lication examples and ideas 32                |

| 8 | Pack | age mechanical data 37                        |

| 9 | Revi | sion history                                  |

# 1 Description

The device is a current-mode PFC controller operating in Transition Mode (TM). Based on the core of a standard TM PFC controller, it offers improved performance and additional functions.

The highly linear multiplier, along with a special correction circuit that reduces crossover distortion of the mains current, allows wide-range-mains operation with an extremely low THD even over a large load range.

The output voltage is controlled by means of a voltage-mode error amplifier and a precise (1.5%  $@T_J = 25^{\circ}C)$  internal voltage reference. The stability of the loop and the transient response to sudden mains voltage changes are improved by the voltage feedforward function (1/V<sup>2</sup> correction).

Additionally, the IC provides the option for tracking boost operation (where the output voltage is changed tracking the mains voltage). The device features extremely low consumption ( $\leq$  90 µA before start-up and  $\leq$  5 mA running).

In addition to an effective two-step OVP that handles normal operation overvoltages, the IC provides also a protection against feedback loop failures or erroneous output voltage setting.

In the L6563 a protection is added to stop the PFC stage in case the boost inductor saturates. This function is not included in the L6563A. This is the only difference between the two part numbers.

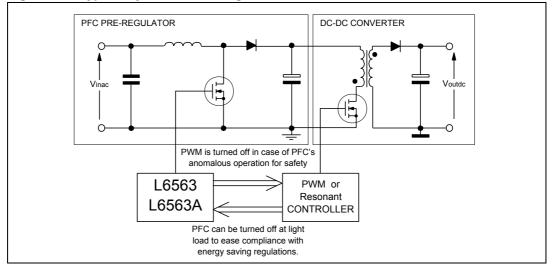

An interface with the PWM controller of the DC-DC converter supplied by the PFC preregulator is provided: the purpose is to stop the operation of the converter in case of anomalous conditions for the PFC stage (feedback loop failure, boost inductor's core saturation) in the L6563 only and to disable the PFC stage in case of light load for the DC-DC converter, so as to make it easier to comply with energy saving norms (Blue Angel, EnergyStar, Energy2000, etc.). The device includes disable functions suitable for remote ON/OFF control both in systems where the PFC pre-regulator works as a master and in those where it works as a slave.

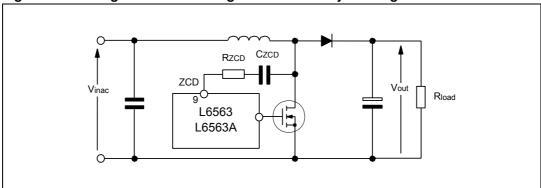

The totem-pole output stage, capable of 600 mA source and 800 mA sink current, is suitable to drive high current MOSFETs or IGBTs. This, combined with the other features and the possibility to operate with the proprietary Fixed-Off-Time control, makes the device an excellent low-cost solution for EN61000-3-2 compliant SMPS in excess of 350W.

Figure 2. Typical system block diagram

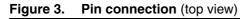

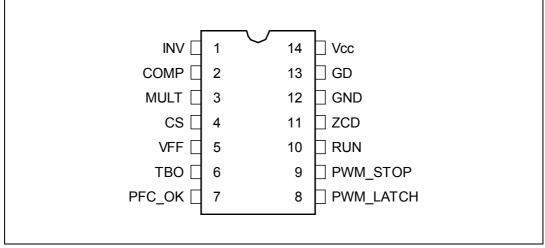

# 1.1 Pin connection

# 1.2 Pin description

### Table 2. Pin description

| Pin N° | Name | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | INV  | Inverting input of the error amplifier. The information on the output voltage of the PFC pre-<br>regulator is fed into the pin through a resistor divider.<br>The pin normally features high impedance but, if the tracking boost function is used, an<br>internal current generator programmed by TBO (pin 6) is activated. It sinks current from the<br>pin to change the output voltage so that it tracks the mains voltage.                                                                           |

| 2      | COMP | Output of the error amplifier. A compensation network is placed between this pin and INV (pin 1) to achieve stability of the voltage control loop and ensure high power factor and low THD.                                                                                                                                                                                                                                                                                                               |

| 3      | MULT | Main input to the multiplier. This pin is connected to the rectified mains voltage via a resistor divider and provides the sinusoidal reference to the current loop. The voltage on this pin is used also to derive the information on the RMS mains voltage.                                                                                                                                                                                                                                             |

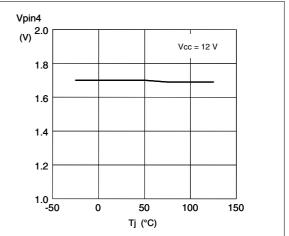

| 4      | CS   | Input to the PWM comparator. The current flowing in the MOSFET is sensed through a resistor, the resulting voltage is applied to this pin and compared with an internal reference to determine MOSFET's turn-off.<br>A second comparison level at 1.7V detects abnormal currents (e.g. due to boost inductor saturation) and, on this occurrence, shuts down the IC, reduces its consumption almost to the start-up level and asserts PWM_LATCH (pin 8) high. This function is not present in the L6563A. |

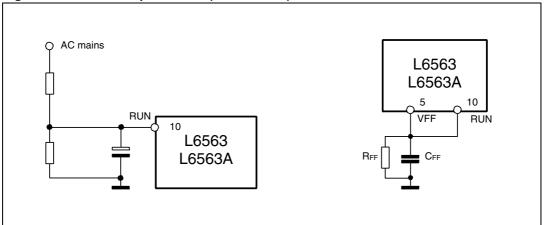

| 5      | VFF  | Second input to the multiplier for $1/V^2$ function. A capacitor and a parallel resistor must be connected from the pin to GND. They complete the internal peak-holding circuit that derives the information on the RMS mains voltage. The voltage at this pin, a DC level equal to the peak voltage at pin MULT (pin 3), compensates the control loop gain dependence on the mains voltage. Never connect the pin directly to GND.                                                                       |

| Pin N° | Name      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6      | ТВО       | Tracking Boost function. This pin provides a buffered VFF voltage. A resistor connected between this pin and GND defines a current that is sunk from pin INV (pin 1). In this way, the output voltage is changed proportionally to the mains voltage (tracking boost). If this function is not used leave this pin open.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 7      | PFC_OK    | PFC pre-regulator output voltage monitoring/disable function. This pin senses the output voltage of the PFC pre-regulator through a resistor divider and is used for protection purposes. If the voltage at the pin exceeds 2.5V the IC is shut down, its consumption goes almost to the start-up level and this condition is latched. PWM_LATCH pin is asserted high. Normal operation can be resumed only by cycling the Vcc. This function is used for protection in case the feedback loop fails. If the voltage on this pin is brought below 0.2V the IC is shut down and its consumption is considerably reduced. To restart the IC the voltage on the pin must go above 0.26V. If these functions are not needed, tie the pin to a voltage between 0.26 and 2.5 V. |

| 8      | PWM_LATCH | Output pin for fault signaling. During normal operation this pin features high impedance. If either a voltage above 2.5V at PFC_OK (pin 7) or a voltage above 1.7V on CS (pin 4) of L6563 is detected the pin is asserted high. Normally, this pin is used to stop the operation of the DC-DC converter supplied by the PFC pre-regulator by invoking a latched disable of its PWM controller. If not used, the pin will be left floating.                                                                                                                                                                                                                                                                                                                                |

| 9      | PWM_STOP  | Output pin for fault signaling. During normal operation this pin features high impedance. If the IC is disabled by a voltage below 0.5V on RUN (pin 10) the voltage at the pin is pulled to ground. Normally, this pin is used to temporarily stop the operation of the DC-DC converter supplied by the PFC pre-regulator by disabling its PWM controller. If not used, the pin will be left floating.                                                                                                                                                                                                                                                                                                                                                                    |

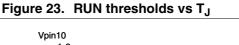

| 10     | RUN       | Remote ON/OFF control. A voltage below 0.52V shuts down (not latched) the IC and brings its consumption to a considerably lower level. PWM_STOP is asserted low. The IC restarts as the voltage at the pin goes above 0.6V. Connect this pin to VFF (pin 5) either directly or through a resistor divider to use this function as brownout (AC mains undervoltage) protection, tie to INV (pin 1) if the function is not used.                                                                                                                                                                                                                                                                                                                                            |

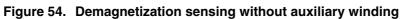

| 11     | ZCD       | Boost inductor's demagnetization sensing input for transition-mode operation. A negative-<br>going edge triggers MOSFET's turn-on.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 12     | GND       | Ground. Current return for both the signal part of the IC and the gate driver.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

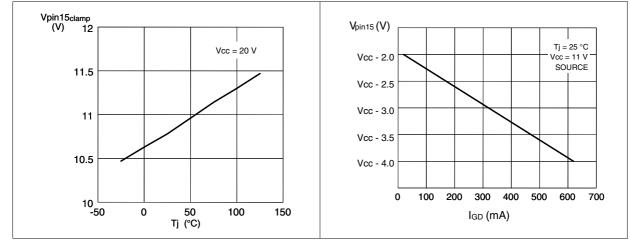

| 13     | GD        | Gate driver output. The totem pole output stage is able to drive power MOSFET's and IGBT's with a peak current of 600 mA source and 800 mA sink. The high-level voltage of this pin is clamped at about 12V to avoid excessive gate voltages.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 14     | VCC       | Supply Voltage of both the signal part of the IC and the gate driver.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

### Table 2. Pin description (continued)

# 2 Absolute maximum ratings

| Symbol                | Pin                   | Parameter                                  | Value                     | Unit |

|-----------------------|-----------------------|--------------------------------------------|---------------------------|------|

| V <sub>CC</sub>       | 14                    | IC supply voltage (Icc = 20mA)             | self-limited              | V    |

|                       | 2, 4 to 6, 8<br>to 10 | Analog inputs & outputs                    | -0.3 to 8                 | V    |

|                       | 1, 3, 7               | Max. pin voltage (I <sub>pin</sub> = 1 mA) | Self-limited              | V    |

| I <sub>PWM_STOP</sub> | 10                    | Max. sink current                          | 3                         | mA   |

| I <sub>ZCD</sub>      | 9                     | Zero current detector max. current         | -10 (source)<br>10 (sink) | mA   |

| P <sub>TOT</sub>      |                       | Power dissipation $@T_A = 50^{\circ}C$     | 0.75                      | W    |

| TJ                    |                       | Junction temperature operating range       | -25 to 150                | °C   |

| T <sub>STG</sub>      |                       | Storage temperature                        | -55 to 150                | °C   |

### Table 3. Absolute maximum ratings

# 3 Thermal data

#### Table 4. Thermal data

| Symbol            | Parameter                                   | Value | Unit |

|-------------------|---------------------------------------------|-------|------|

| R <sub>thJA</sub> | Maximum thermal resistance junction-ambient | 120   | °C/W |

# 4 Electrical characteristics

#### **Table 5. Electrical characteristics**

( -25°C < T<sub>J</sub> < +125°C, V<sub>CC</sub> = 12V, C<sub>o</sub> = 1nF between pin GD and GND, C<sub>FF</sub> =1µF between pin V<sub>FF</sub> and GND; unless otherwise specified)

| Symbol                                  | Parameter                | Test condition                                                                         | Min    | Тур  | Мах   | Unit |

|-----------------------------------------|--------------------------|----------------------------------------------------------------------------------------|--------|------|-------|------|

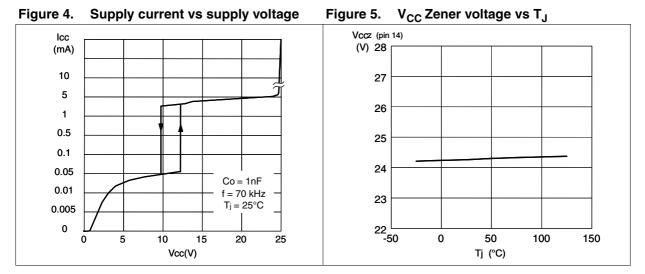

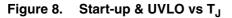

| Supply vol                              | tage                     |                                                                                        |        |      | -     |      |

| Vcc                                     | Operating range          | After turn-on                                                                          | 10.3   |      | 22    | V    |

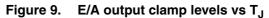

| Vcc <sub>On</sub>                       | Turn-on threshold        | (1)                                                                                    | 11     | 12   | 13    | V    |

| Vcc <sub>Off</sub>                      | Turn-off threshold       | (1)                                                                                    | 8.7    | 9.5  | 10.3  | V    |

| Hys                                     | Hysteresis               |                                                                                        | 2.3    |      | 2.7   | V    |

| VZ                                      | Zener Voltage            | lcc = 20 mA                                                                            | 22     | 25   | 28    | V    |

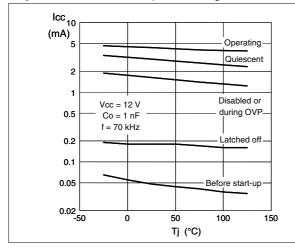

| Supply cu                               | rrent                    |                                                                                        |        |      |       |      |

| I <sub>start-up</sub>                   | Start-up current         | Before turn-on, Vcc = 10V                                                              |        | 50   | 90    | μA   |

| ۱ <sub>q</sub>                          | Quiescent current        | After turn-on                                                                          |        | 3    | 5     | mA   |

| I <sub>CC</sub>                         | Operating supply current | @ 70kHz                                                                                |        | 3.8  | 5.5   | mA   |

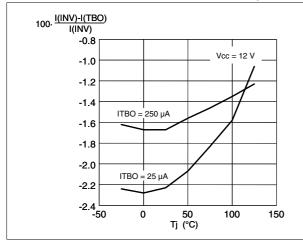

| 1                                       | Idle state quiescent     | Latched by PFC_OK > VthI or<br>Vcs > V <sub>CSdis</sub>                                |        | 180  | 250   | μA   |

| I <sub>qdis</sub>                       | Current                  | Disabled by PFC_OK < Vth or<br>RUN < V <sub>DIS</sub>                                  |        | 1.5  | 2.2   | mA   |

| ۱ <sub>q</sub>                          | Quiescent current        | During static/dynamic OVP                                                              |        | 2    | 3     | mA   |

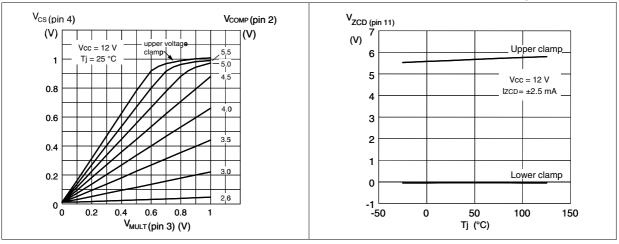

| Multiplier i                            | nput                     |                                                                                        |        |      |       |      |

| I <sub>MULT</sub>                       | Input bias current       | V <sub>MULT</sub> = 0 to 3 V                                                           |        | -0.2 | -1    | μA   |

| V <sub>MULT</sub>                       | Linear operation range   |                                                                                        | 0 to 3 |      |       | V    |

| V <sub>CLAMP</sub>                      | Internal clamp level     | I <sub>MULT</sub> = 1 mA                                                               | 9      | 9.5  |       | V    |

| $\frac{\Delta V_{cs}}{\Delta V_{MULT}}$ | Output max. slope        | V <sub>MULT</sub> =0 to 0.5V, V <sub>FF</sub> =0.8V<br>V <sub>COMP</sub> = Upper clamp | 2.2    | 2.34 |       | V/V  |

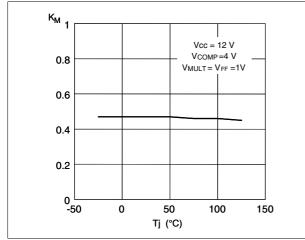

| K <sub>M</sub>                          | Gain <sup>(3)</sup>      | $V_{MULT} = 1 V, V_{COMP} = 4 V,$<br>$V_{VFF} = V_{MULT}$                              | 0.375  | 0.45 | 0.525 | v    |

| Error ampl                              | ifier                    |                                                                                        |        |      |       |      |

| M                                       | Voltage feedback input   | T <sub>J</sub> = 25 °C                                                                 | 2.465  | 2.5  | 2.535 |      |

| V <sub>INV</sub>                        | threshold                | 10.3 V < Vcc < 22 V <sup>(2)</sup>                                                     | 2.44   |      | 2.56  | V    |

|                                         | Line regulation          | Vcc = 10.3 V to 22V                                                                    |        | 2    | 5     | mV   |

| I <sub>INV</sub>                        | Input bias current       | TBO open, V <sub>INV</sub> = 0 to 4 V                                                  |        | -0.2 | -1    | μA   |

Table 5. Electrical characteristics (continued) $(-25^{\circ}C < T_J < +125^{\circ}C, V_{CC} = 12V, C_o = 1nF$  between pin GD and GND,  $C_{FF} = 1\mu F$  between pin V<sub>FF</sub>and GND; unless otherwise specified)

| Symbol                | Parameter                                        | Test condition                                                                 | Min | Тур  | Max  | Unit |

|-----------------------|--------------------------------------------------|--------------------------------------------------------------------------------|-----|------|------|------|

| VINVCLAMP             | Internal clamp level                             | I <sub>INV</sub> = 1 mA                                                        | 9   | 9.5  |      | V    |

| Gv                    | Voltage gain                                     | Open loop                                                                      | 60  | 80   |      | dB   |

| GB                    | Gain-bandwidth product                           |                                                                                |     | 1    |      | MHz  |

|                       | Source current                                   | $V_{COMP} = 4V, V_{INV} = 2.4 V$                                               | -2  | -3.5 | -5   | mA   |

| ICOMP                 | Sink current                                     | $V_{COMP} = 4V, V_{INV} = 2.6 V$                                               | 2.5 | 4.5  |      | mA   |

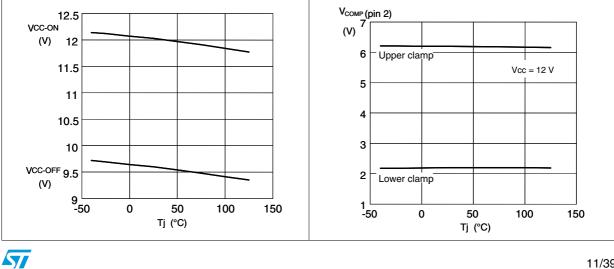

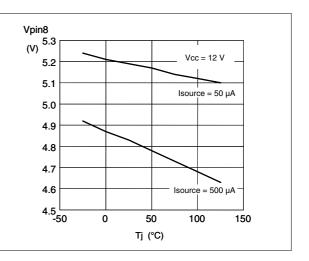

| N/                    | Upper clamp voltage                              | I <sub>SOURCE</sub> = 0.5 mA                                                   | 5.7 | 6.2  | 6.7  | V    |

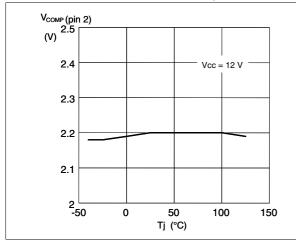

| V <sub>COMP</sub>     | Lower clamp voltage                              | $I_{SINK} = 0.5 \text{ mA}^{(2)}$                                              | 2.1 | 2.25 | 2.4  | V    |

| Current se            | nse comparator                                   |                                                                                | ·   |      |      |      |

| I <sub>CS</sub>       | Input bias current                               | $V_{CS} = 0$                                                                   |     |      | -1   | μA   |

| t <sub>LEB</sub>      | Leading edge blanking                            |                                                                                | 100 | 200  | 300  | ns   |

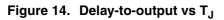

| td <sub>(H-L)</sub>   | Delay to output                                  |                                                                                |     | 120  |      | ns   |

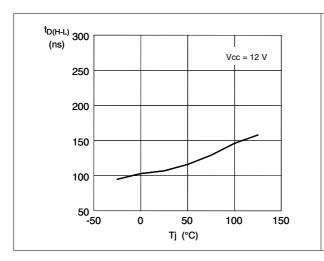

| V <sub>CSclamp</sub>  | Current sense reference<br>clamp                 | V <sub>COMP</sub> = Upper clamp,<br>V <sub>VFF</sub> = V <sub>MULT</sub> =0.5V | 1.0 | 1.08 | 1.16 | v    |

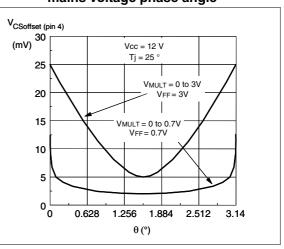

| Maa                   | Current sense offset                             | $V_{MULT} = 0, V_{VFF} = 3V$                                                   |     | 25   |      | mV   |

| Vcs <sub>offset</sub> |                                                  | $V_{MULT} = 3V, V_{VFF} = 3V$                                                  |     | 5    |      |      |

| V <sub>CSdis</sub>    | Ic latch-off level (L6563 only)                  | (2)                                                                            | 1.6 | 1.7  | 1.8  | V    |

| Output ove            | ervoltage                                        |                                                                                |     |      |      |      |

| I <sub>OVP</sub>      | Dynamic OVP triggering<br>current                |                                                                                | 17  | 20   | 23   | μA   |

| Hys                   | Hysteresis                                       | (4)                                                                            |     | 15   |      | μA   |

|                       | Static OVP threshold                             | (2)                                                                            | 2   | 2.15 | 2.3  | V    |

| Voltage fee           | edforward                                        |                                                                                | ·   |      |      |      |

| $V_{VFF}$             | Linear operation range                           | $R_{FF}$ = 47 k $\Omega$ to GND                                                | 0.5 |      | 3    | V    |

| ΔV                    | Dropout<br>V <sub>MULTpk</sub> -V <sub>VFF</sub> |                                                                                |     |      | 20   | mV   |

Table 5. Electrical characteristics (continued) $(-25^{\circ}C < T_J < +125^{\circ}C, V_{CC} = 12V, C_o = 1nF$  between pin GD and GND,  $C_{FF} = 1\mu F$  between pin  $V_{FF}$ and GND; unless otherwise specified)

| Symbol                | Parameter                                               | Test condition                      | Min  | Тур  | Max  | Unit |

|-----------------------|---------------------------------------------------------|-------------------------------------|------|------|------|------|

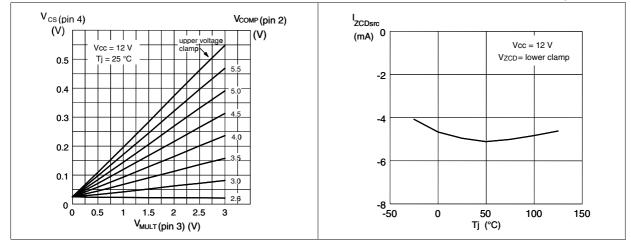

| Zero curre            | nt detector                                             |                                     |      |      |      |      |

| V <sub>ZCDH</sub>     | Upper clamp voltage                                     | I <sub>ZCD</sub> = 2.5 mA           | 5.0  | 5.7  |      | V    |

| V <sub>ZCDL</sub>     | Lower clamp voltage                                     | I <sub>ZCD</sub> = - 2.5 mA         | -0.3 | 0    | 0.3  | V    |

| V <sub>ZCDA</sub>     | Arming voltage<br>(positive-going edge)                 | (4)                                 |      | 1.4  |      | v    |

| V <sub>ZCDT</sub>     | Triggering voltage<br>(negative-going edge)             | (4)                                 |      | 0.7  |      | V    |

| I <sub>ZCDb</sub>     | Input bias current                                      | V <sub>ZCD</sub> = 1 to 4.5 V       |      |      | 1    | μA   |

| I <sub>ZCDsrc</sub>   | Source current capability                               |                                     | -2.5 |      |      | mA   |

| I <sub>ZCDsnk</sub>   | Sink current capability                                 |                                     | 2.5  |      |      | mA   |

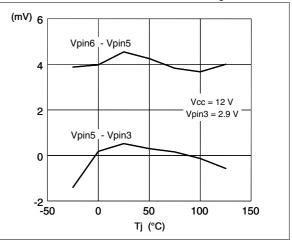

| Tracking b            | oost function                                           |                                     |      |      |      |      |

| ΔV                    | Dropout voltage<br>V <sub>VFF</sub> - V <sub>TBO</sub>  | I <sub>TBO</sub> = 0.25 mA          |      |      | 20   | mV   |

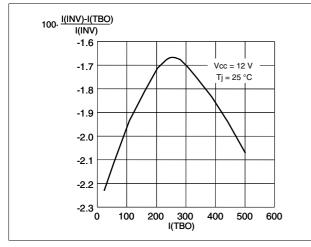

| I <sub>TBO</sub>      | Linear operation                                        |                                     | 0    |      | 0.25 | mA   |

|                       | I <sub>INV</sub> - I <sub>TBO</sub> current<br>mismatch | I <sub>TBO</sub> = 25 μA to 0.25 mA | -3.5 |      | 3.5  | %    |

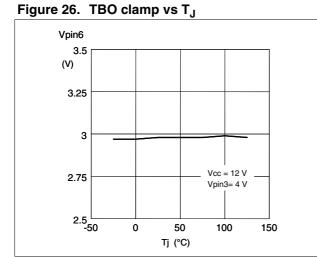

| V <sub>TBOclamp</sub> | Clamp voltage                                           | $V_{VFF} = 4V^{(2)}$                | 2.9  | 3    | 3.1  | V    |

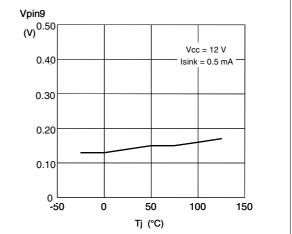

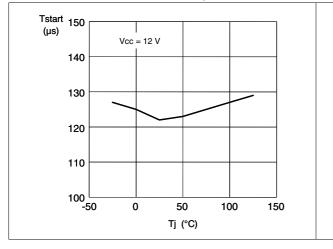

| PFC_OK                |                                                         |                                     | 1    |      |      |      |

| V <sub>thl</sub>      | Latch-off threshold                                     | Voltage rising <sup>(2)</sup>       | 2.4  | 2.5  | 2.6  | V    |

| V <sub>th</sub>       | Disable threshold                                       | Voltage falling <sup>(2)</sup>      |      | 0.2  |      | V    |

| V <sub>EN</sub>       | Enable threshold                                        | Voltage rising <sup>(2)</sup>       |      | 0.26 |      | V    |

| I <sub>PFC_OK</sub>   | Input bias current                                      | $V_{PFC_OK} = 0$ to 2.5V            |      | -0.1 | -1   | μA   |

| V <sub>clamp</sub>    | Clamp voltage                                           | I <sub>PFC_OK</sub> = 1 mA          | 9    | 9.5  |      | V    |

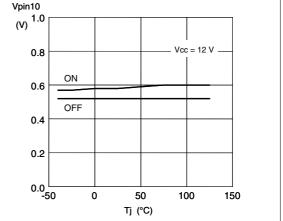

| PWM_LAT               | СН                                                      |                                     |      |      |      |      |

| I <sub>leak</sub>     | Low level leakage current                               | V <sub>PWM_LATCH</sub> =0           |      |      | -1   | μΑ   |

| V <sub>H</sub>        | High level                                              | I <sub>PWM_LATCH</sub> = -0.5 mA    | 3.7  |      |      | V    |

| PWM_STO               | P                                                       |                                     | 1    |      | •    | •    |

| I <sub>leak</sub>     | High level leakage current                              | V <sub>PWM_STOP</sub> = 6V          |      |      | 1    | μΑ   |

| VL                    | Low level                                               | $I_{PWM\_STOP} = 0.5 \text{ mA}$    |      |      | 1    | V    |

| V <sub>clamp</sub>    | Clamp voltage                                           | I <sub>PFC_OK</sub> = 2 mA          | 9    | 9.5  |      | V    |

#### Table 5. Electrical characteristics (continued)

( -25°C < T<sub>J</sub> < +125°C, V<sub>CC</sub> = 12V, C<sub>o</sub> = 1nF between pin GD and GND, C<sub>FF</sub> =1µF between pin V<sub>FF</sub> and GND; unless otherwise specified)

| Symbol              | Parameter            | Test condition                                       | Min  | Тур  | Max  | Unit |

|---------------------|----------------------|------------------------------------------------------|------|------|------|------|

| Run functi          | on                   |                                                      |      |      |      |      |

| I <sub>RUN</sub>    | Input bias current   | V <sub>RUN</sub> = 0 to 3 V                          |      |      | -1   | μA   |

| V <sub>DIS</sub>    | Disable threshold    | Voltage falling <sup>(2)</sup>                       | 0.5  | 0.52 | 0.54 | V    |

| V <sub>EN</sub>     | Enable threshold     | Voltage rising <sup>(2)</sup>                        | 0.56 | 0.6  | 0.64 | V    |

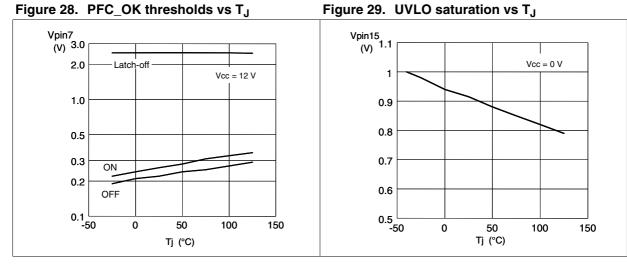

| Start time          |                      |                                                      |      | •    |      | 4    |

| t <sub>START</sub>  | Start timer period   |                                                      | 75   | 150  | 300  | μs   |

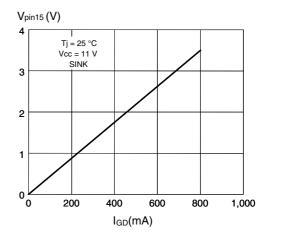

| Gate drive          | r                    | •                                                    |      |      |      | •    |

| M                   | Deservatively        | I <sub>GDsource</sub> = 20 mA                        |      | 2    | 2.6  | V    |

| V <sub>OHdrop</sub> | Dropout voltage      | I <sub>GDsource</sub> = 200 mA                       |      | 2.5  | 3    | V    |

| V <sub>OLdrop</sub> |                      | I <sub>GDsink</sub> = 200 mA                         |      | 1    | 2    | V    |

| t <sub>f</sub>      | Current fall time    |                                                      |      | 30   | 70   | ns   |

| t <sub>r</sub>      | Current rise time    |                                                      |      | 40   | 80   | ns   |

| V <sub>Oclamp</sub> | Output clamp voltage | I <sub>GDsource</sub> = 5mA; Vcc = 20V               | 10   | 12   | 15   | V    |

|                     | UVLO saturation      | Vcc=0 to Vcc <sub>On</sub> , I <sub>sink</sub> =10mA |      |      | 1.1  | V    |

(1), (2) Parameters tracking each other

(3) The multiplier output is given by:

$$V_{CS} = K_M \cdot \frac{V_{MULT} \cdot (V_{COMP} - 2.5)}{V_{VFF}^2}$$

(4) Parameters guaranteed by design, functionality tested in production.

#### **Typical electrical performance** 5

11/39

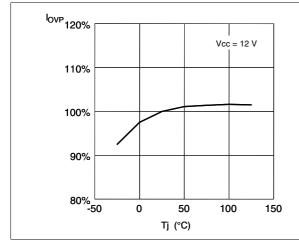

Figure 10. Static OVP level vs T<sub>J</sub>

Figure 12. Dynamic OVP current vs T<sub>J</sub> (normalized value)

Figure 11. Vcs clamp vs T<sub>J</sub>

Figure 13. Current-sense offset vs mains voltage phase angle

Figure 15. Ic latch-off level on current sense vs  $T_J$  (L6563 only)

### Figure 16. Multiplier characteristics @ $V_{FF}$ = 1V Figure 17. ZCD clamp levels vs $T_J$

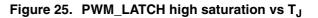

Figure 21. VFF & TBO dropouts vs T<sub>J</sub>

#### Figure 22. TBO current mismatch vs T<sub>J</sub>

Figure 24. TBO-INV current mismatch vs TBO currents

# 6 Application information

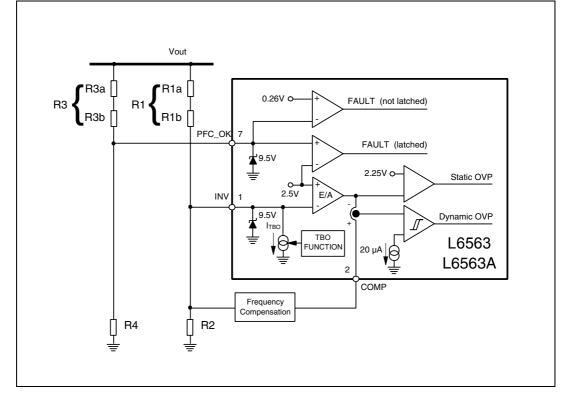

### 6.1 Overvoltage protection

Normally, the voltage control loop keeps the output voltage  $V_O$  of the PFC pre-regulator close to its nominal value, set by the ratio of the resistors R1 and R2 of the output divider. Neglecting the ripple components, under steady state conditions the current through R1 equals that through R2. Considering that the non-inverting input of the error amplifier is internally biased at 2.5V, the voltage at pin INV will be 2.5V as well, then:

#### **Equation 1**

$$I_{R2} = I_{R1} = \frac{2.5}{R2} = \frac{V_0 - 2.5}{R1}$$

If the output voltage experiences an abrupt change  $\Delta$ Vo the voltage at pin INV is kept at 2.5V by the local feedback of the error amplifier, a network connected between pins INV and COMP that introduces a long time constant. Then the current through R2 remains equal to 2.5/R2 but that through R1 becomes:

#### **Equation 2**

$$I'_{R1} = \frac{V_0 - 2.5 + \Delta V_0}{R1}$$

The difference current  $\Delta I_{R1} = I'_{R1} - I'_{R1} = \Delta V_O/R1$  will flow through the compensation network and enter the error amplifier (pin COMP). This current is monitored inside the IC and when it reaches about 18 µA the output voltage of the multiplier is forced to decrease, thus reducing the energy drawn from the mains. If the current exceeds 20 µA, the OVP is triggered (Dynamic OVP), and the external power transistor is switched off until the current falls approximately below 5 µA. However, if the overvoltage persists (e.g. in case the load is completely disconnected), the error amplifier will eventually saturate low hence triggering an internal comparator (Static OVP) that will keep the external power switch turned off until the output voltage comes back close to the regulated value. The output overvoltage that is able to trigger the OVP function is then:

#### **Equation 3**

$$\Delta V_{O} = R1 \cdot 20 \cdot 10^{-6}$$

An important advantage of this technique is that the overvoltage level can be set independently of the regulated output voltage: the latter depends on the ratio of R1 to R2, the former on the individual value of R1. Another advantage is the precision: the tolerance of the detection current is 15%, which means 15% tolerance on the  $\Delta V_O$ . Since it is usually much smaller than Vo, the tolerance on the absolute value will be proportionally reduced.

Example:  $V_0 = 400V$ ,  $\Delta V_0 = 40V$ . Then: R1 =  $40V/20\mu A = 2M\Omega$ ; R2 =  $2.5 \cdot 2M\Omega \cdot / (400 \cdot 2.5) = 12.58k\Omega$ . The tolerance on the OVP level due to the L6563/A will be  $40 \cdot 0.15 = 6$  V, that is  $\pm 1.36\%$ .

When either OVP is activated the quiescent consumption is reduced to minimize the discharge of the Vcc capacitor.

# 6.2 Feedback Failure Protection (FFP)

The OVP function above described is able to handle "normal" overvoltage conditions, i.e. those resulting from an abrupt load/line change or occurring at start-up. It cannot handle the overvoltage generated, for instance, when the upper resistor of the output divider (R1) fails open: the voltage loop can no longer read the information on the output voltage and will force the PFC pre-regulator to work at maximum ON-time, causing the output voltage to rise with no control.

A pin of the device (PFC\_OK) has been dedicated to provide an additional monitoring of the output voltage with a separate resistor divider (R3 high, R4 low, see *Figure 34*). This divider is selected so that the voltage at the pin reaches 2.5V if the output voltage exceeds a preset value, usually larger than the maximum Vo that can be expected, also including worst-case load/line transients.

Example:  $V_0 = 400$  V, Vox = 475V. Select: R3 = 3M $\Omega$ ; then: R4 = 3M $\Omega \cdot 2.5/(475 \cdot 2.5) = 15.87 k\Omega$ .

When this function is triggered, the gate drive activity is immediately stopped, the device is shut down, its quiescent consumption is reduced below 250  $\mu$ A and the condition is latched as long as the supply voltage of the IC is above the UVLO threshold. At the same time the pin PWM\_LATCH is asserted high. PWM\_LATCH is an open source output able to deliver 3.7V min. with 0.5 mA load, intended for tripping a latched shutdown function of the PWM controller IC in the cascaded DC-DC converter, so that the entire unit is latched off. To restart the system it is necessary to recycle the input power, so that the Vcc voltages of both the L6563/A and the PWM controller go below their respective UVLO thresholds.

The PFC\_OK pin doubles its function as a not-latched IC disable: a voltage below 0.2V will shut down the IC, reducing its consumption below 1 mA. In this case both PWM\_STOP and PWM\_LATCH keep their high impedance status. To restart the IC simply let the voltage at the pin go above 0.26 V.

Note that this function offers a complete protection against not only feedback loop failures or erroneous settings, but also against a failure of the protection itself. Either resistor of the PFC\_OK divider failing short or open or a PFC\_OK pin floating will result in shutting down the IC and stopping the pre-regulator.

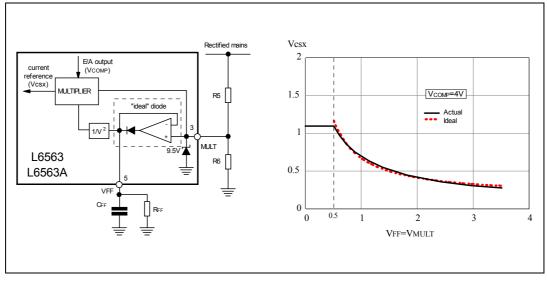

# 6.3 Voltage Feedforward

The power stage gain of PFC pre-regulators varies with the square of the RMS input voltage. So does the crossover frequency  $f_c$  of the overall open-loop gain because the gain has a single pole characteristic. This leads to large trade-offs in the design. For example, setting the gain of the error amplifier to get  $f_c = 20$  Hz @ 264 Vac means having  $f_c \cong 4$  Hz @ 88 Vac, resulting in a sluggish control dynamics. Additionally, the slow control loop causes large transient current flow during rapid line or load changes that are limited by the dynamics of the multiplier output. This limit is considered when selecting the sense resistor to let the full load power pass under minimum line voltage conditions, with some margin. But a fixed current limit allows excessive power input at high line, whereas a fixed power limit requires the current limit to vary inversely with the line voltage and allow overcoming all of the above-mentioned issues. It consists of deriving a voltage proportional to the input RMS voltage, feeding this voltage into a squarer/divider circuit ( $1/V^2$  corrector) and providing the resulting signal to the multiplier that generates the current reference for the inner current control loop (see *Figure 35*).

# Figure 35. Voltage feedforward: squarer-divider (1/V<sup>2</sup>) block diagram and transfer characteristic

In this way a change of the line voltage will cause an inversely proportional change of the half sine amplitude at the output of the multiplier (if the line voltage doubles the amplitude of the multiplier output will be halved and vice versa) so that the current reference is adapted to the new operating conditions with (ideally) no need for invoking the slow dynamics of the error amplifier. Additionally, the loop gain will be constant throughout the input voltage range, which improves significantly dynamic behavior at low line and simplifies loop design.

Actually, deriving a voltage proportional to the RMS line voltage implies a form of integration, which has its own time constant. If it is too small the voltage generated will be affected by a considerable amount of ripple at twice the mains frequency that will cause distortion of the current reference (resulting in high THD and poor PF); if it is too large there will be a considerable delay in setting the right amount of feedforward, resulting in excessive overshoot and undershoot of the pre-regulator's output voltage in response to large line voltage changes. Clearly a trade-off is required.

The device realizes Voltage Feedforward with a technique that makes use of just two external parts and that limits the feedforward time constant trade-off issue to only one direction. A capacitor  $C_{FF}$  and a resistor  $R_{FF}$ , both connected from the VFF (pin 5) pin to ground, complete an internal peak-holding circuit that provides a DC voltage equal to the peak of the rectified sine wave applied on pin MULT (pin 3).  $R_{FF}$  provides a means to discharge  $C_{FF}$  when the line voltage decreases (see *Figure 35*). In this way, in case of sudden line voltage rise,  $C_{FF}$  will be rapidly charged through the low impedance of the internal diode and no appreciable overshoot will be visible at the pre-regulator's output; in case of line voltage drop  $C_{FF}$  will be discharged with the time constant  $R_{FF}$ · $C_{FF}$  which can be in the hundred ms to achieve an acceptably low steady-state ripple and have low current distortion; consequently the output voltage can experience a considerable undershoot, like in systems with no feedforward compensation.

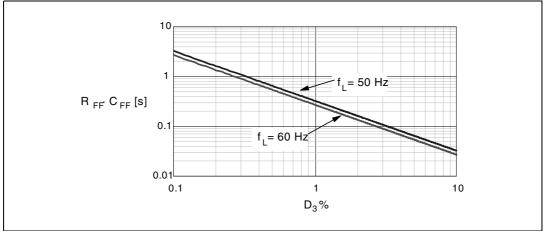

The twice-mains-frequency  $(2 \cdot f_L)$  ripple appearing across  $C_{FF}$  is triangular with a peak-topeak amplitude that, with good approximation, is given by:

#### **Equation 4**

$$\Delta V_{FF} = \frac{2V_{MULTpk}}{1 + 4f_{L}R_{FF}C_{FF}}$$

where  $f_L$  is the line frequency. The amount of  $3^{rd}$  harmonic distortion introduced by this ripple, related to the amplitude of its  $2 \cdot f_L$  component, will be:

#### **Equation 5**

$$\mathsf{D}_3\% = \frac{100}{2\pi\mathsf{f}_\mathsf{L}\mathsf{R}_\mathsf{FF}\mathsf{C}_\mathsf{FF}}$$

*Figure 36* shows a diagram that helps choose the time constant  $R_{FF}$ · $C_{FF}$  based on the amount of maximum desired 3<sup>rd</sup> harmonic distortion. Always connect  $R_{FF}$  and  $C_{FF}$  to the pin, the IC will not work properly if the pin is either left floating or connected directly to ground.

# Figure 36. $R_{FF} \cdot C_{FF}$ as a function of $3^{rd}$ harmonic distortion introduced in the input current

The dynamics of the voltage feedforward input is limited downwards at 0.5V (see *Figure 35*), that is the output of the multiplier will not increase any more if the voltage on the  $V_{FF}$  pin is below 0.5V. This helps to prevent excessive power flow when the line voltage is lower than the minimum specified value (brownout conditions).

### 6.4 THD optimizer circuit

The L6563/A is provided with a special circuit that reduces the conduction dead-angle occurring to the AC input current near the zero-crossings of the line voltage (crossover distortion). In this way the THD (Total Harmonic Distortion) of the current is considerably reduced.

A major cause of this distortion is the inability of the system to transfer energy effectively when the instantaneous line voltage is very low. This effect is magnified by the high-frequency filter capacitor placed after the bridge rectifier, which retains some residual voltage that causes the diodes of the bridge rectifier to be reverse-biased and the input current flow to temporarily stop.

To overcome this issue the device forces the PFC pre-regulator to process more energy near the line voltage zero-crossings as compared to that commanded by the control loop. This will result in both minimizing the time interval where energy transfer is lacking and fully discharging the high-frequency filter capacitor after the bridge.

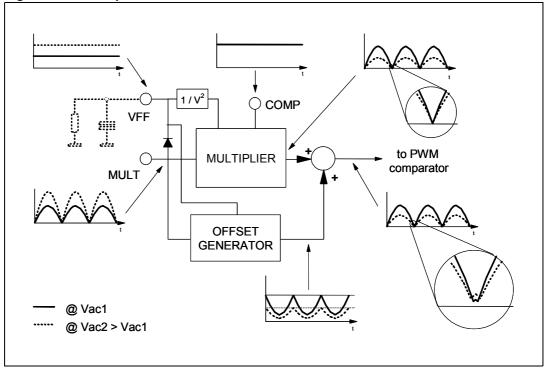

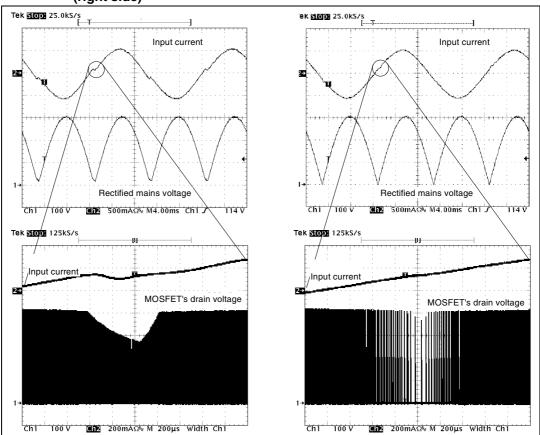

Figure 37 shows the internal block diagram of the THD optimizer circuit.

Figure 37. THD optimizer circuit

Figure 38. THD optimization: standard TM PFC controller (left side) and L6563/A (right side)

Essentially, the circuit artificially increases the ON-time of the power switch with a positive offset added to the output of the multiplier in the proximity of the line voltage zero-crossings. This offset is reduced as the instantaneous line voltage increases, so that it becomes negligible as the line voltage moves toward the top of the sinusoid. Furthermore the offset is modulated by the voltage on the  $V_{FF}$  pin (see *Section 6.3 on page 18* section) so as to have little offset at low line, where energy transfer at zero crossings is typically quite good, and a larger offset at high line where the energy transfer gets worse.

The effect of the circuit is shown in *Figure 38*, where the key waveforms of a standard TM PFC controller are compared to those of this chip.

To take maximum benefit from the THD optimizer circuit, the high-frequency filter capacitor after the bridge rectifier should be minimized, compatibly with EMI filtering needs. A large capacitance, in fact, introduces a conduction dead-angle of the AC input current in itself - even with an ideal energy transfer by the PFC pre-regulator - thus reducing the effectiveness of the optimizer circuit.

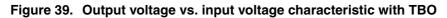

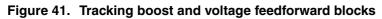

### 6.5 Tracking Boost function

In some applications it may be advantageous to regulate the output voltage of the PFC preregulator so that it tracks the RMS input voltage rather than at a fixed value like in conventional boost pre-regulators. This is commonly referred to as "tracking boost" or "follower boost" approach.

With this IC the function can be realized by connecting a resistor ( $R_T$ ) between the TBO pin and ground. The TBO pin presents a DC level equal to the peak of the MULT pin voltage and is then representative of the mains RMS voltage. The resistor defines a current, equal to V(TBO)/ $R_T$ , that is internally 1:1 mirrored and sunk from pin INV (pin 1) input of the error amplifier. In this way, when the mains voltage increases the voltage at TBO pin will increase as well and so will do the current flowing through the resistor connected between TBO and GND. Then a larger current will be sunk by INV pin and the output voltage of the PFC preregulator will be forced to get higher. Obviously, the output voltage will move in the opposite direction if the input voltage decreases.

To avoid undesired output voltage rise should the mains voltage exceed the maximum specified value, the voltage at the TBO pin is clamped at 3V. By properly selecting the multiplier bias it is possible to set the maximum input voltage above which input-to-output tracking ends and the output voltage becomes constant. If this function is not used, leave the pin open: the device will regulate a fixed output voltage.

Starting from the following data:

- Vin<sub>1</sub> = minimum specified input RMS voltage;

- Vin<sub>2</sub> = maximum specified input RMS voltage;

- Vo<sub>1</sub> = regulated output voltage @ Vin = Vin<sub>1</sub>;

- Vo<sub>2</sub> = regulated output voltage @ Vin = Vin<sub>2</sub>;

- Vox = absolute maximum limit for the regulated output voltage;

- $\Delta Vo = OVP$  threshold,

to set the output voltage at the desired values use the following design procedure:

1. Determine the input RMS voltage Vin<sub>clamp</sub> that produces Vo = Vox:

#### **Equation 6**

$$\operatorname{Vin}_{\operatorname{clamp}} = \frac{\operatorname{Vox} - \operatorname{Vo}_1}{\operatorname{Vo}_2 - \operatorname{Vo}_1} \cdot \operatorname{Vin}_2 - \frac{\operatorname{Vox} - \operatorname{Vo}_2}{\operatorname{Vo}_2 - \operatorname{Vo}_1} \cdot \operatorname{Vin}_1$$

and choose a value Vin<sub>x</sub> such that Vin<sub>2</sub> = Vin<sub>x</sub> < Vin<sub>clamp</sub>. This will result in a limitation of the output voltage range below Vox (it will equal Vox if one chooses Vin<sub>x</sub> = Vin<sub>clamp</sub>)

2. Determine the divider ratio of the MULT pin (pin 3) bias:

#### **Equation 7**

$$k = \frac{3}{\sqrt{2} \cdot Vin_x}$$

and check that at minimum mains voltage  ${\rm Vin}_1$  the peak voltage on pin 3 is greater than 0.65V.

3. Determine R1, the upper resistor of the output divider:

#### **Equation 8**

$$R1 = \frac{\Delta Vo}{20} \cdot 10^6$$

4. Calculate the lower resistor R<sub>2</sub> of the output divider and the adjustment resistor R<sub>T</sub>:

#### **Equation 9**

$$R2 = 2.5 \cdot R1 \cdot \frac{Vin_2 - Vin_1}{(Vo_1 - 2.5) \cdot Vin_2 - (Vo_2 - 2.5) \cdot Vin_1}$$

$$R_T = \sqrt{2} \cdot k \cdot R1 \cdot \frac{Vin_2 - Vin_1}{Vo_2 - Vo_1}$$

5. Check that the maximum current sourced by the TBO pin (pin 6) does not exceed the maximum specified (0.25mA):

#### **Equation 10**

$$I_{\text{TBOmax}} = \frac{3}{R_{\text{T}}} \le 0.25 \cdot 10^{-3}$$

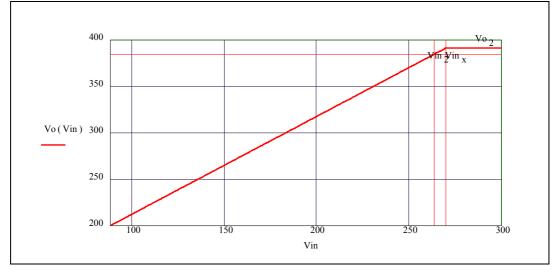

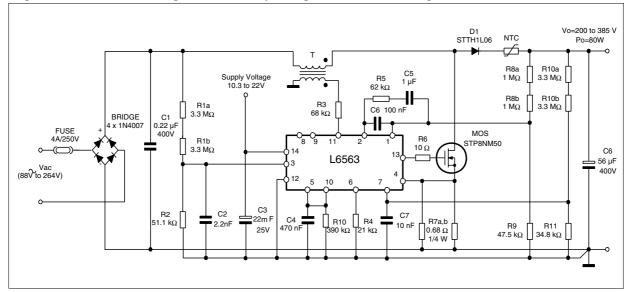

In the following Mathcad® sheet, as an example, the calculation is shown for the circuit illustrated in *Figure 40. Figure 41* shows the internal block diagram of the tracking boost function.

#### **Design data**

| Vin <sub>1</sub> := 88V  | Vo <sub>1</sub> := 200V |

|--------------------------|-------------------------|

| Vin <sub>2</sub> := 264V | Vo <sub>2</sub> := 385V |

| Vox ;= 400V              |                         |

| ∆Vo ;= 40V               |                         |

#### Step 1

$$Vin_{clamp} := \frac{Vox - Vo_{1}}{Vo_{2} - Vo_{1}} \cdot Vin_{2} - \frac{Vox - Vo_{2}}{Vo_{2} - Vo_{1}} \cdot Vin_{1}$$

$Vin_{clamp} = 278.27V$

choose: Vin<sub>x</sub>: = 270V

#### Step 2

k: =  $\frac{3}{\sqrt{2} \cdot \text{Vin}_{x}}$  k = 7.857 x 10<sup>-3</sup>

Step 3

R1:

$$=\frac{\Delta Vo}{20} \cdot 10^{6}$$

R1 = 2 x 10<sup>6</sup>  $\Omega$

### Step 4

R2: =

$$2.5 \cdot \text{R1} \cdot \frac{\text{Vin}_2 - \text{Vin}_1}{(\text{Vo}_1 - 2.5) \cdot \text{Vin}_2 - (\text{Vo}_2 - 2.5) \cdot \text{Vin}_1}$$

R2 = 4.762 x 10<sup>4</sup>  $\Omega$

$$R_{T} = k \cdot \sqrt{2} \cdot R1 \cdot \frac{Vin_{2} - Vin_{1}}{Vo_{2} - Vo_{1}} \qquad \qquad R_{T} = 2.114 \times 10^{4} \Omega$$

### Step 5

$$I_{\text{TBOmax}}$$

: =  $\frac{3}{R_{\text{T}}} \cdot 10^3$   $I_{\text{TBOmax}}$  = 0.142 mA

$$Vo(Vi): = V_{MULTpk} \leftarrow k \cdot \sqrt{2} \cdot Vi \qquad Vo(Vin_1) = 200V$$

$$V_{TBO} \leftarrow if(V_{MULTpk} < 3, V_{MULTpk}, 3) \qquad Vo(Vin_2) = 385V$$

$$2.5 \cdot \left(1 + \frac{R1}{R2}\right) + V_{TBO} \cdot \frac{R1}{R_T} \qquad Vo(Vin_X) = 391.307V$$

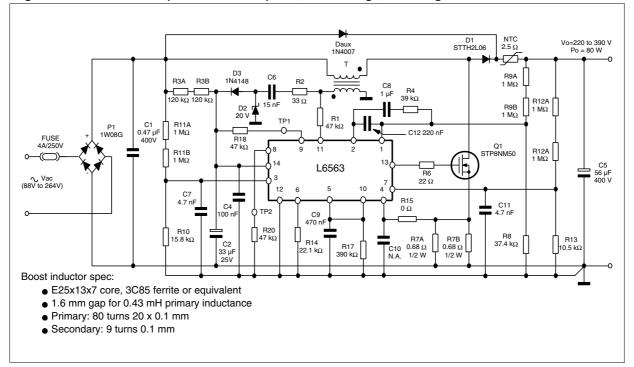

Figure 40. 80W, wide-range-mains PFC pre-regulator with tracking boost function active

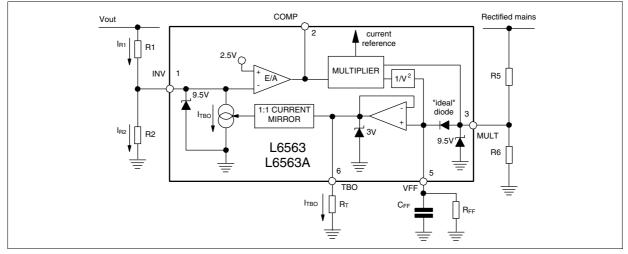

# 6.6 Inductor saturation detection (L6563 only)

Boost inductor's hard saturation may be a fatal event for a PFC pre-regulator: the current upslope becomes so large (50-100 times steeper, see *Figure 42*) that during the current sense propagation delay the current may reach abnormally high values. The voltage drop caused by this abnormal current on the sense resistor reduces the gate-to-source voltage, so that the MOSFET may work in the active region and dissipate a huge amount of power, which leads to a catastrophic failure after few switching cycles.

However, in some applications such as ac-dc adapters, where the PFC pre-regulator is turned off at light load for energy saving reasons, even a well-designed boost inductor may occasionally slightly saturate when the PFC stage is restarted because of a larger load demand. This happens when the restart occurs at an unfavorable line voltage phase, so that the output voltage may drop significantly below the rectified peak voltage. As a result, in the

boost inductor the inrush current coming from the bridge rectifier adds up to the switched current and, furthermore, there is little or no voltage available for demagnetization.

To cope with a saturated inductor, the L6563 is provided with a second comparator on the current sense pin (CS, pin 4) that stops and latches off the IC if the voltage, normally limited within 1.1V, exceeds 1.7V. Also the cascaded DC-DC converter can be stopped via the PWM\_LATCH pin that is asserted high. In this way the entire system is stopped and enabled to restart only after recycling the input power, that is when the Vcc voltages of the L6563 and the PWM controller go below their respective UVLO thresholds. System safety will be considerably increased.

To better suit the applications where a certain level of saturation of the boost inductor needs to be tolerated, the L6563A does not support this protection function.

## 6.7 Power management/housekeeping functions

A special feature of this IC is that it facilitates the implementation of the "housekeeping" circuitry needed to coordinate the operation of the PFC stage to that of the cascaded DC-DC converter. The functions realized by the housekeeping circuitry ensure that transient conditions like power-up or power down sequencing or failures of either power stage be properly handled.

This device provides some pins to do that. As already mentioned, one communication line between the IC and the PWM controller of the cascaded DC-DC converter is the PWM\_LATCH pin, which is normally open when the PFC works properly and goes high if it loses control of the output voltage (because of a failure of the control loop) or if the boost inductor saturates, with the aim of latching off the PWM controller of the cascaded DC-DC converter as well (*Section 6.2: Feedback Failure Protection (FFP) on page 18* for more details).

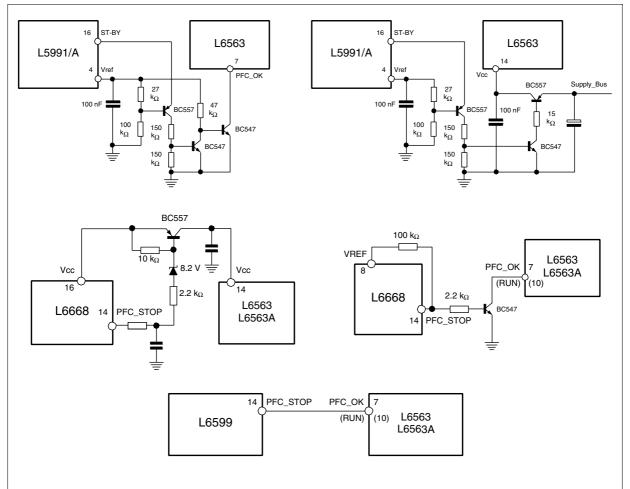

A second communication line can be established via the disable function included in the PFC\_OK pin (*Section 6.2 on page 18* for more details ). Typically this line is used to allow the PWM controller of the cascaded DC-DC converter to shut down the L6563/A in case of light load, to minimize the no-load input consumption. Should the residual consumption of the chip be an issue, it is also possible to cut down the supply voltage. Interface circuits like those shown in *Figure 43*, where the L6563/A works along with the L5991, PWM controller with standby function, can be used. Needless to say, this operation assumes that the cascaded DC-DC converter stage works as the master and the PFC stage as the slave or, in other words, that the DC-DC stage starts first, it powers both controllers and enables/disables the operation of the PFC stage.

# Figure 43. Interface circuits that let DC-DC converter's controller IC disable the L6563/A at light load

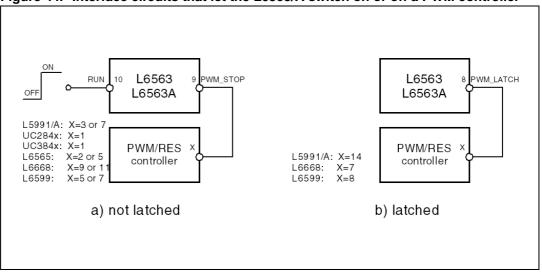

The third communication line is the PWM\_STOP pin (pin 9), which works in conjunction with the RUN pin (pin 10). The purpose of the PWM\_STOP pin is to inhibit the PWM activity of both the PFC stage and the cascaded DC-DC converter. The pin is an open collector, normally open, that goes low if the device is disabled by a voltage lower than 0.52V on the RUN pin. It is important to point out that this function works correctly in systems where the PFC stage is the master and the cascaded DC-DC converter is the slave or, in other words, where the PFC stage starts first, powers both controllers and enables/disables the operation of the DC-DC stage.

This function is quite flexible and can be used in different ways. In systems comprising an auxiliary converter and a main converter (e.g. desktop PC's silver box or hi-end LCD-TV), where the auxiliary converter also powers the controllers of the main converter, the pin RUN can be used to start and stop the main converter. In the simplest case, to enable/disable the PWM controller the PWM\_STOP pin can be connected to either the output of the error amplifier (*Figure 44 a*) or, if the chip is provided with it, to its soft-start pin (*Figure 44 b*). The use of the soft-start pin allows the designer to delay the start-up of the DC-DC stage with respect to that of the PFC stage, which is often desired. An underlying assumption in order for that to work properly is that the UVLO thresholds of the PWM controller are certainly higher than those of the L6563/A.

Figure 44. Interface circuits that let the L6563/A switch on or off a PWM controller

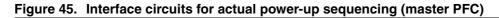

If this is not the case or it is not possible to achieve a start-up delay long enough (because this prevents the DC-DC stage from starting up correctly) or, simply, the PWM controller is devoid of soft start, the arrangement of *Figure 45* lets the DC-DC converter start-up when the voltage generated by the PFC stage reaches a preset value. The technique relies on the UVLO thresholds of the PWM controller.

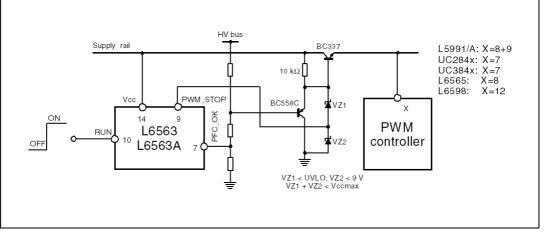

Another possible use of the RUN and PWM\_STOP pins (again, in systems where the PFC stage is the master) is brownout protection, thanks to the hysteresis provided.

Brownout protection is basically a not-latched device shutdown function that must be activated when a condition of mains undervoltage is detected. This condition may cause overheating of the primary power section due to an excess of RMS current. Brownout can also cause the PFC pre-regulator to work open loop and this could be dangerous to the PFC stage itself and the downstream converter, should the input voltage return abruptly to its rated value. Another problem is the spurious restarts that may occur during converter power down and that cause the output voltage of the converter not to decay to zero monotonically. For these reasons it is usually preferable to shutdown the unit in case of brownout.

IC shutdown upon brownout can be easily realized as shown in *Figure 46* The scheme on the left is of general use, the one on the right can be used if the bias levels of the multiplier and the  $R_{FF}$ - $C_{FF}$  time constant are compatible with the specified brownout level and with the specified holdup time respectively.

In *Table 6* it is possible to find a summary of all of the above mentioned working conditions that cause the device to stop operating.

#### Figure 46. Brownout protection (master PFC)

## 6.8 Summary of L6563/A idle states

| Condition                   | Caused or revealed by       | PWM_LATCH<br>(pin 8)          | PWM_STOP<br>(pin 9) | Typical IC consumption | IC behavior             |

|-----------------------------|-----------------------------|-------------------------------|---------------------|------------------------|-------------------------|

| UVLO                        | Vcc < 8.7 V                 | Open                          | Open                | 50 µA                  | Auto-restart            |

| Feedback<br>disconnected    | PFC_OK > 2.5 V              | Active (high)                 | Open                | 180 µA                 | Latched                 |

| Saturated<br>Boost Inductor | Vcs > 1.7 V<br>(L6563 only) | Active (high)<br>(L6563 only) | Open                | 180 μA<br>(L6563 only) | Latched<br>(L6563 only) |

| AC Brownout                 | RUN < 0.52 V                | Open                          | Active (low)        | 1.5 mA                 | Auto-restart            |

| Standby                     | PFC_OK < 0.2 V              | Open                          | Open                | 1.5 mA                 | Auto-restart            |

#### Table 6. Summary of L6563/A idle states

# 7 Application examples and ideas

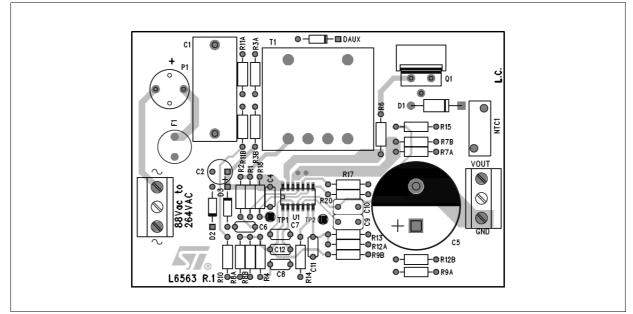

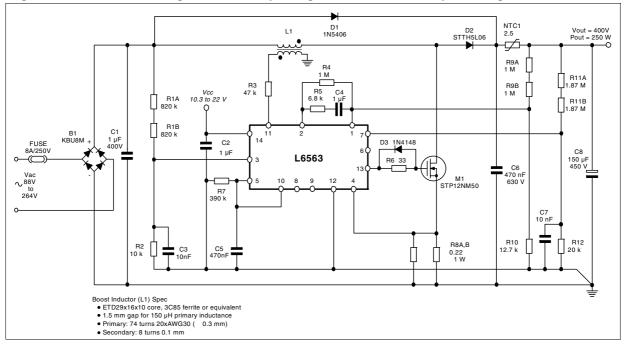

Figure 47. Demo board (EVAL6563-80W) 80W, Wide-range, Tracking Boost: Electrical schematic

Figure 48. EVAL6563-80W: PCB and component layout (Top view, real size: 64 x 94 mm)

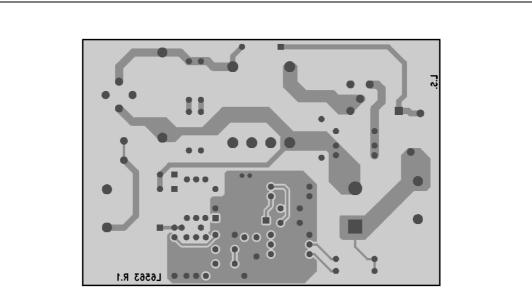

Figure 49. EVAL6563-80W: PCB layout, soldering side (Top view)

#### Table 7. EVAL6563-80W: Evaluation results at full load

| Vin (V <sub>AC</sub> ) | Pin (W) | Vo (V <sub>DC</sub> ) | ∆Vo<br>(V <sub>pk-pk</sub> ) | Po (W) | ղ <b>(%)</b> | PF    | THD (%) |

|------------------------|---------|-----------------------|------------------------------|--------|--------------|-------|---------|

| 90                     | 85.3    | 219.4                 | 16.6                         | 79.64  | 93.4         | 0.999 | 3.7     |

| 115                    | 84.9    | 244.1                 | 15.0                         | 80.80  | 95.2         | 0.998 | 4.3     |

| 135                    | 83.7    | 263.7                 | 13.9                         | 80.16  | 95.8         | 0.997 | 4.8     |

| 180                    | 83.5    | 307.6                 | 14.5                         | 80.28  | 96.1         | 0.993 | 6.0     |

| 230                    | 85.2    | 356.7                 | 13.0                         | 81.33  | 95.5         | 0.984 | 7.7     |

| 265                    | 85.0    | 390.6                 | 12.1                         | 80.85  | 95.1         | 0.974 | 9.5     |

Note: Measurements done with the line filter shown in Figure 51.

Table 8. EVAL6563-80W: Evaluation results at half load

| Vin (V <sub>AC</sub> ) | Pin (W) | Vo (V <sub>DC</sub> ) | ∆Vo<br>(V <sub>pk-pk</sub> ) | Po (W) | ղ <b>(%)</b> | PF    | THD (%) |

|------------------------|---------|-----------------------|------------------------------|--------|--------------|-------|---------|

| 90                     | 43.4    | 219.9                 | 8.6                          | 40.90  | 94.2         | 0.997 | 4.8     |

| 115                    | 42.6    | 244.5                 | 7.7                          | 40.10  | 94.1         | 0.994 | 5.7     |

| 135                    | 43.1    | 264.0                 | 7.3                          | 40.39  | 93.7         | 0.989 | 6.5     |

| 180                    | 43.8    | 307.7                 | 7.7                          | 40.31  | 92.0         | 0.978 | 8.4     |

| 230                    | 45.6    | 356.8                 | 6.8                          | 41.03  | 90.0         | 0.951 | 9.6     |

| 265                    | 46.0    | 390.7                 | 6.7                          | 40.63  | 88.3         | 0.920 | 14.2    |

Note:

Measurements done with the line filter shown in Figure 51.

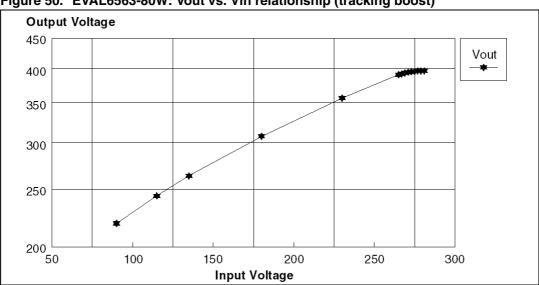

Figure 50. EVAL6563-80W: Vout vs. Vin relationship (tracking boost)

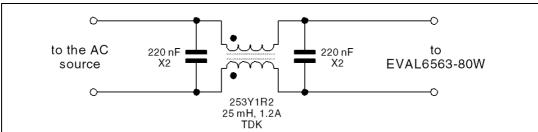

Figure 51. Line filter (not tested for EMI compliance) used for EVAL6563-80W evaluation

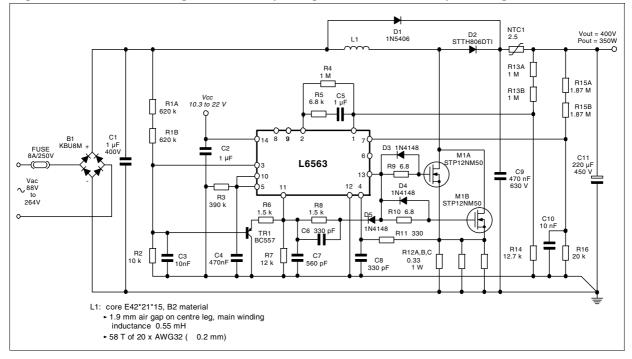

Figure 52. 250W, wide-range-mains PFC pre-regulator with fixed output voltage

Figure 53. 350W, wide-range-mains PFC pre-regulator with fixed output voltage and FOT control

57

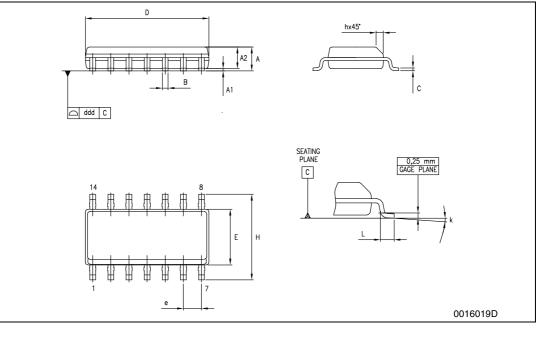

# 8 Package mechanical data

In order to meet environmental requirements, ST offers these devices in ECOPACK® packages. These packages have a Lead-free second level interconnect . The category of second level interconnect is marked on the package and on the inner box label, in compliance with JEDEC Standard JESD97. The maximum ratings related to soldering conditions are also marked on the inner box label. ECOPACK is an ST trademark. ECOPACK specifications are available at: www.st.com

| Dim.  |                      | mm.  |      | inch  |       |       |  |

|-------|----------------------|------|------|-------|-------|-------|--|

|       | Min                  | Тур  | Max  | Min   | Тур   | Max   |  |

| А     | 1.35                 |      | 1.75 | 0.053 |       | 0.069 |  |

|       |                      |      |      |       |       |       |  |

| A1    | 0.10                 |      | 0.30 | 0.004 |       | 0.012 |  |

| A2    | 1.10                 |      | 1.65 | 0.043 |       | 0.065 |  |

| В     | 0.33                 |      | 0.51 | 0.013 |       | 0.020 |  |

| С     | 0.19                 |      | 0.25 | 0.007 |       | 0.01  |  |

| D (1) | 8.55                 |      | 8.75 | 0.337 |       | 0.344 |  |

| Е     | 3.80                 |      | 4.0  | 0.150 |       | 0.157 |  |

| е     |                      | 1.27 |      |       | 0.050 |       |  |

| Н     | 5.8                  |      | 6.20 | 0.228 |       | 0.244 |  |

| h     | 0.25                 |      | 0.50 | 0.01  |       | 0.02  |  |

| L     | 0.40                 |      | 1.27 | 0.016 |       | 0.050 |  |

| k     | 0° (min.), 8° (max.) |      |      |       |       |       |  |

| ddd   |                      |      | 0.10 |       |       | 0.004 |  |

#### Table 9. SO-14 Mechanical data

#### Figure 56. Package dimensions

# 9 Revision history

### Table 10. Revision history

| Date          | Revision | Changes                                                                                                                                                      |  |  |

|---------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 13-Nov-2004   | 1        | First issue                                                                                                                                                  |  |  |

| 24-Sep-2005   | 2        | Changed the maturity from "Preliminary data" to "Datasheet"                                                                                                  |  |  |

| 17-Nov-2006   | 3        | Added new part number L6563A ( <i>Table 2</i> )<br>Updated the <i>Section 4 on page 7</i> & <i>Section 7 on page 32</i> the<br>document has been reformatted |  |  |

| 12-Mar-2007 4 |          | Replaced block diagram, added <i>Figure 37 on page 21</i> and minor editor changes.                                                                          |  |  |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2007 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com