Order this document by MC68330/D

# MC68330V

# Technical Summary Integrated CPU32 Processor

The MC68330 is one of Motorola's CPU32-based M68300 Family of high-performance 32-bit integrated processors. The MC68330 combines on a single integrated circuit an enhanced M68000-compatible processor with a variety of circuits typically used to integrate a processor into the overall computer system. Devoid of the selection of peripheral circuits found on most M68300 products, the MC68330 gives the designer access to the higher performance of the CPU32 with minimized external glue logic, while allowing the greatest freedom in selecting needed peripheral and custom circuits. The MC68330 is also ideal for applications needing 32-bit CISC processor performance from a lower cost 16-bit memory system.

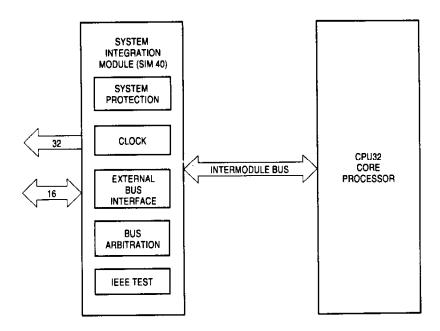

The MC68330's high level of functional integration results in reductions in component count, power consumption, board space, and cost while yielding higher system reliability and shorter design time. In an idle state, the MC68330 requires only a trickle of current, making it ideal for battery-powered applications. The 3.3-V MC68330V is particularly attractive to applications on a very tight power budget. Complete code compatibility with the MC68000 affords the designer access to a broad base of established real-time kernels, operating systems, languages, applications, and development tools, many of which are oriented towards embedded control. Figure 1 shows a simplified block diagram of the MC68330.

The primary features of the MC68330 are as follows:

- · High Functional Integration on a Single Piece of Silicon

- CPU32—MC68020-Derived 32-Bit Central Processor Unit

- Upward Object-Code Compatible with MC68000 and MC68010

- Additional 32-Bit MC68020 Instructions and Addressing Modes

- Unique Embedded Control Instructions

- Fast Two-Clock Register Instructions—10,045 Dhrystones/Second

- System Integration Module (SIM40) Incorporates Many Functions Typically Relegated to External PALs, TTL, and ASIC, such as:

- System Configuration

- System Protection

- Chip-Select and Wait-State Generation

- -- Clock Generation

- Dynamic Bus Sizing

- Up to 16 Discrete I/O Lines

- · 32 Address Lines, 16 Data Lines

- External Bus Interface

- Periodic Interrupt Timer

- Interrupt Response

- -- Bus Arbitration

- IEEE 1149.1 Boundary Scan (JTAG)

- Power-On Reset

This document contains information on a product under development. Motorola reserves the right to change or discontinue this product without notice.

- Power Consumption Control

- Static HCMOS Technology Reduces Power in Normal Operation

- -- Low-Voltage Operation at 3.3 V ±0.3 V (MC68330V only)

- Programmable Clock Generator Throttles Frequency

- LPSTOP Provides an Idle State for Lowest Standby Current

- 0–16.78 MHz or 0–25.16 MHz Operation

- 132-Pin Plastic Quad Flat Pack (PQFP) or 128-Pin 14 x 20 mm PQFP

As a low-voltage part, the MC68330V can operate with a 3.3-V power supply. MC68330 is used throughout this document to refer to both the low-voltage and standard 5-V parts since both are functionally equivalent.

Figure 1. MC68330 Simplified Block Diagram

### M68300 FAMILY

The MC68330 is one of a series of components in the Motorola M68300 family. Other members of the family include the MC68302, MC68331, MC68332, MC68F333, and MC68340.

### **ORGANIZATION**

The M68300 family of integrated processors and controllers is built on an M68000 core processor, an onchip bus, and a selection of intelligent peripherals appropriate for a set of applications. The CPU32 is a powerful central processor with nearly the performance of the MC68020. A system integration module (SIM40) incorporates the external bus interface and many of the smaller circuits that typically surround a microprocessor for address decoding, wait-state insertion, interrupt prioritization, clock generation, arbitration, watchdog timing, and power-on reset timing.

Each member of the M68300 family is distinguished by its selection of peripherals. Peripherals are chosen to address specific applications but are often useful in a wide variety of applications. The peripherals may be highly sophisticated timing or protocol engines that have their own processors, or they may be more traditional peripheral functions, such as UARTs and timers. Since each major function is designed in a standalone module, each module might be found in many different M68300 family parts. Driver software written for a module on one M68300 part can be used to run the same module that appears on another part.

### **ADVANTAGES**

By incorporating so many major features into a single M68300 family chip, a system designer can realize significant savings in design time, power consumption, cost, board space, pin count, and programming. The equivalent functionality can easily require 20 separate components. Each component might have 16–64 pins, totaling over 350 connections. Most of these connections require interconnects or are duplications. Each connection is a candidate for a bad solder joint or misrouted trace. Each component is another part to qualify, purchase, inventory, and maintain. Each component requires a share of the printed circuit board. Each component draws power, which is often used to drive large buffers to get the signal to another chip. The cumulative power consumption of all the components must be available from the power supply. The signals between the CPU and a peripheral might not be compatible nor run from the same clock, requiring time delays or other special design considerations.

In an M68300 family component, the major functions and glue logic are all properly connected internally, timed with the same clock, fully tested, and uniformly documented. Power consumption stays well under a watt, and a special standby mode drops current well under a milliamp during idle periods. Only essential signals are brought out to pins. The primary package is the surface-mount plastic quad flat pack for the smallest possible footprint.

### MC68330 SIGNALS

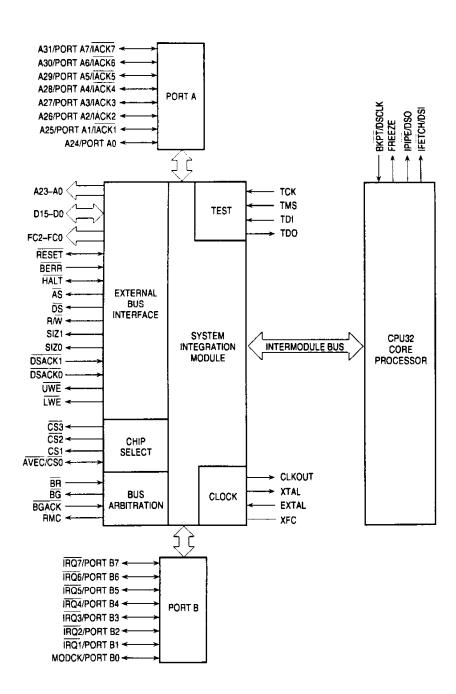

Figure 2 is a detailed diagram showing the components and signals.

**MOTOROLA**

**INTEGRATED CPU32 PROCESSOR**

Figure 2. MC68330 Detailed Block Diagram

### CENTRAL PROCESSOR UNIT

The CPU32 is a powerful central processor that supervises system functions, makes decisions, manipulates data, and directs I/O. A special debugging mode simplifies processor emulation during system debug.

### CPU32

The CPU32 is an M68000 family processor specially designed for use as a 32-bit core processor and for operation over the intermodule bus (IMB). Designers used the MC68020 as a model and included advances of the later M68000 family processors, resulting in an instruction execution performance of 4 MIPS (VAX-equivalent) at 25.16 MHz.

The powerful and flexible M68000 architecture is the basis of the CPU32. MC68000 (including the MC68HC000 and the MC68EC000) and MC68010 user programs will run unmodified on the CPU32. The programmer can use any of the eight 32-bit data registers for fast manipulation of data and any of the eight 32-bit address registers for indexing data in memory. The CPU32 can operate on data types of single bits, binary-coded decimal (BCD) digits, and 8, 16, and 32 bits. Peripherals and data in memory can reside anywhere in the 4-Gbyte linear address space. A supervisor operating mode protects system-level resources from the more restricted user mode, allowing a true virtual environment to be developed.

Flexible instructions for data movement, arithmetic functions, logical operations, shifts and rotates, bit set and clear, conditional and unconditional program branches, and overall system control are supported, including a fast  $32 \times 32$  multiply and 32-bit conditional branches. Instructions such as table lookup and interpolate and low-power stop (LPSTOP) support specific requirements of embedded control applications. Many addressing modes complement these instructions, including predecrement and postincrement, which allow simple stack and queue maintenance and scaled indexing for efficient table accesses. Data types and addressing modes are supported orthogonally by all data operations and with all appropriate addressing modes. Position-independent code is easily written.

The CPU32 is specially optimized to run with the MC68330's 16-bit data bus. Most instructions execute in one-half the number of clocks compared to the original MC68000, yielding an overall 1.6 times the performance of the same-speed MC68000 and measuring 10,045 Dhrystones/sec @ 25.16 MHz (6,742 Dhrystones/sec @ 16.78 MHz).

Like all M68000 family processors, the CPU32 recognizes interrupts of seven different priority levels and allows the peripheral to vector the processor to the desired service routine. Internal trap exceptions ensure proper instruction execution with good addresses and data, allow operating system intervention in special situations, and permit instruction tracing. Hardware signals can either terminate or rerun bad memory accesses before instructions process data incorrectly.

The CPU32 offers the programmer full 32-bit data processing performance with complete M68000 compatibility, yet with more compact code than is available with RISC processors. The CPU32 is identical in all CPU32-based M68300 family products.

### BACKGROUND DEBUG MODE

A special operating mode is available in the CPU32 in which normal instruction execution is suspended while special on-chip microcode performs the functions of a debugger. Commands are received over a dedicated, high-speed, full-duplex serial interface. Commands allow the manual reading or writing of CPU32 registers, reading or writing of external memory locations, and diversion to user-specified patch code. This background debug mode permits a much simpler emulation environment while leaving the processor chip in the target system, running its own debugging operations.

**MOTOROLA**

INTEGRATED CPU32 PROCESSOR

### **ON-CHIP PERIPHERALS**

To improve total system throughput and reduce part count, board size, and cost of system implementation, the M68300 family integrates on-chip peripheral modules and typical glue logic. On the MC68330, only the system integration module (SIM40) resides on chip with the CPU32.

The processor communicates with these modules over the on-chip intermodule bus (IMB). This backbone of the chip is similar to traditional external buses with address, data, clock, interrupt, arbitration, and handshake signals. Because bus masters (like the CPU32), peripherals, and the SIM40 can be on the chip, the IMB ensures that communication between these modules is fully synchronized and that arbitration and interrupts can be handled in parallel with data transfers, greatly improving system performance. Internal accesses across the IMB may be monitored from outside the chip, if desired.

Each module operates independently. No direct connections between peripheral modules are made inside the chip; however, external connections could, for instance, link a serial output to a DMA control line. Modules and their registers are relocatable and are accessed in the CPU32 memory map for easy access by general M68000 instructions. Each module may be assigned its own interrupt level, response vector, and arbitration priority. Since each module is a self-contained design and adheres to the IMB interface specifications, the modules may appear on other M68300 family products, retaining the investment in the software drivers for the module. The MC68330's SIM40 also appears on the MC68340.

# **SYSTEM INTEGRATION MODULE (SIM40)**

The SIM40 provides the external bus interface for the CPU32. It also eliminates much of the glue logic that typically supports the microprocessor and its interface with the peripheral and memory system. The SIM40 provides programmable circuits to perform address decoding and chip selects, wait-state insertion, interrupt handling, clock generation, bus arbitration, watchdog timing, discrete I/O, and power-on reset timing. A boundary scan test capability is also provided.

### **EXTERNAL BUS INTERFACE**

The external bus interface (EBI) handles the transfer of information between the internal CPU32 and memory, peripherals, or other processing elements in the external address space. Based on the MC68030 bus, the external bus provides up to 32 address lines and 16 data lines. Address extensions identify each bus cycle as supervisor or user privilege level and as instruction or data access. The data bus allows dynamic sizing for 8- or 16-bit bus accesses. Synchronous transfers for the CPU32 can be made in as little as two clock cycles. Asynchronous transfers allow the memory system to signal the CPU32 when the transfer is complete and to note the number of bits in the transfer. An external master can arbitrate for the bus using a three-line handshaking interface.

### SYSTEM CONFIGURATION AND PROTECTION

The M68000 family of processors is designed with the concept of providing maximum system safeguards. System configuration and various monitors and timers are provided in the MC68330. Power-on reset circuitry is a part of the SIM40. A bus monitor ensures that the system does not lock up when there is no response to a memory access. The bus fault monitor can reset the processor when a catastrophic bus failure occurs. Spurious interrupts are detected and handled appropriately. A software watchdog can pull the processor out of an infinite loop. With the periodic interupt timer, an interrupt can be sent to the CPU32 with programmable regularity for DRAM refresh, time-of-day clock, task switching, etc.

**INTEGRATED CPU32 PROCESSOR**

MOTOROLA

### **CLOCK SYNTHESIZER**

The clock synthesizer generates the clock signals used by all internal operations as well as a clock output used by external devices. The clock synthesizer can operate with an inexpensive 32768-Hz watch crystal or an external oscillator for reference, using an internal phase-locked loop and voltage-controlled oscillator. At any time, software can select clock frequencies from 131 kHz to 16.78 MHz or 25.16 MHz, favoring either low power consumption or high performance. Alternately, an external clock can directly drive the clock signal at the operating frequency. With its fully static HCMOS design, it is possible to completely stop the system clock without losing the contents of the internal registers.

### CHIP-SELECT AND WAIT-STATE GENERATION

Four programmable chip selects provide signals to enable external memory and peripheral circuits, providing all handshaking and timing signals with up to 175-ns access times with a 25.16-MHz system clock (265 ns @ 16.78 MHz). Each chip select signal has an associated base address and an address mask that determine the addressing characteristics of that chip select. Address space and write protection can be selected for each. The block size can be selected from 256 bytes up to 4 Gbytes in increments of 2<sup>n</sup>. Accesses can be preselected for either 8- or 16-bit transfers. Fast synchronous termination or up to three wait states can be programmed, whether or not the chip select signals are used. External handshakes can also signal the end of a bus transfer. A system can boot from reset out of 8-bit-wide memory, if desired.

### INTERRUPT HANDLING

Seven input signals are provided to trigger an external interrupt, one for each of the seven priority levels supported. Seven separate outputs can indicate the priority level of the interrupt being serviced. An input can direct the processor to a default service routine, if desired. Interrupts at each priority level can be preprogrammed to go to the default service routine. For maximum flexibility, interrupts can be vectored to the correct service routine by the interrupting device.

#### DISCRETE I/O PINS

When not used for other functions, 16 pins can be programmed as discrete input or output lines.

### **IEEE 1149.1 TEST**

To aid in system diagnostics, the MC68330 includes dedicated user-accessible test logic that is fully compliant with the IEEE 1149.1 standard for boundary scan testability, often referred to as JTAG (Joint Test Action Group).

### POWER CONSUMPTION MANAGEMENT

The MC68330 is very power efficient due to its advanced  $0.8-\mu$  HCMOS process technology and its static logic design. The resulting power consumption is typically 240 mW in full operation @ 16.78 MHz (370 mW @ 25.16 MHz)—far less than the comparable discrete component implementation the MC68330 can replace. For applications employing reduced voltage operation, selection of the MC68330V, which requires only a 3.3-V power supply, reduces current consumption by 40–60% in all modes of operation (as well as reducing noise emissions).

The MC68330 has many additional methods of dynamically controlling power consumption during operation. The frequency of operation can be lowered under software control to reduce current consumption when performance is less critical. Running a special LPSTOP instruction shuts down the active circuits in the CPU32 and SIM40 module, halting instruction execution. Power consumption in this standby mode is reduced to about 300  $\mu$ W. Processing and power consumption can be resumed by resetting the part or by generating an interrupt, which can be done with the SIM40's periodic interrupt timer.

**MOTOROLA**

**INTEGRATED CPU32 PROCESSOR**

### **PHYSICAL**

The MC68330 is available as 0–16.78 MHz and 0–25.16 MHz, 0°C to +70°C and -40°C to +85°C, and 5.0 V  $\pm 5\%$  and 3.3 V  $\pm 0.3$  supply voltages (reduced frequencies at 3.3 V). Multiple power and ground leads minimize ground bounce and ensure proper isolation of different sections of the chip, including the clock oscillator. Either 132 or 120 pins are used for signals and power. The MC68330 is available in a PQFP with 0.25-in or 0.5-mm lead spacing.

### **ELECTRICAL SPECIFICATIONS**

### **MAXIMUM RATINGS**

| Rating                      | Symbol           | Value        | Unit |

|-----------------------------|------------------|--------------|------|

| Supply Voltage              | Vcc              | -0.3 to +7.0 | ٧    |

| Input Voltage               | Vin              | -0.3 to +7.0 | ٧    |

| Operating Temperature Range | TA               | 0 to 70      | °C   |

| Storage Temperature Range   | T <sub>sta</sub> | -55 to 150   | °C   |

The following ratings define a range of conditions in which the device will operate without being damaged. However, sections of the device may not operate normally while being exposed to the electrical extremes. This device contains circuitry to protect against damage due to high static voltages or electrical fields; however, it is advised that normal precautions be taken to avoid application of any voltages higher than maximum-rated voltages to this high-impedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate logic voltage level (e.g., either GND or VCC).

### THERMAL CHARACTERISTICS

| Characteristic     | Symbol | Value | Unit |

|--------------------|--------|-------|------|

| Thermal Resistance | ΑLθ    |       | °C/W |

| 132-Pin PQFP       |        | 42    |      |

| 128-Pin PQFP       |        | TBD   |      |

### **POWER CONSIDERATIONS**

The average chip-junction temperature, TJ, in °C can be obtained from:

$$T_{J} = T_{A} + (P_{D} \cdot \theta_{JA}) \tag{1}$$

where:

T = Ambient Temperature, °C

θ, IA = Package Thermal Resistance, Junction-to-Ambient, °C/W

PD = PINT + PI/O

PINT = ICC x VCC, Watts—Chip Internal Power

PI/O = Power Dissipation on Input and Output Pins—User Determined

For most applications, PI/O < PINT and can be neglected.

An approximate relationship between PD and TJ (if PI/O is neglected) is:

$$P_D = K + (T_J + 273^{\circ}C)$$

(2)

Solving Equations (1) and (2) for K gives:

$$K = P_D \cdot (T_A + 273^{\circ}C) + \theta_{JA} \cdot P_D^2$$

(3)

where K is a constant pertaining to the particular part. K can be determined from Equation (3) by measuring PD (at thermal equilibrium) for a known TA. Using this value of K, the values of PD and TJ can be obtained by solving Equations (1) and (2) iteratively for any value of TA.

**MOTOROLA**

**INTEGRATED CPU32 PROCESSOR**

### **AC ELECTRICAL SPECIFICATION DEFINITIONS**

The AC specifications presented consist of output delays, input setup and hold times, and signal skew times. All signals are specified relative to an appropriate edge of the clock and possibly to one or more other signals.

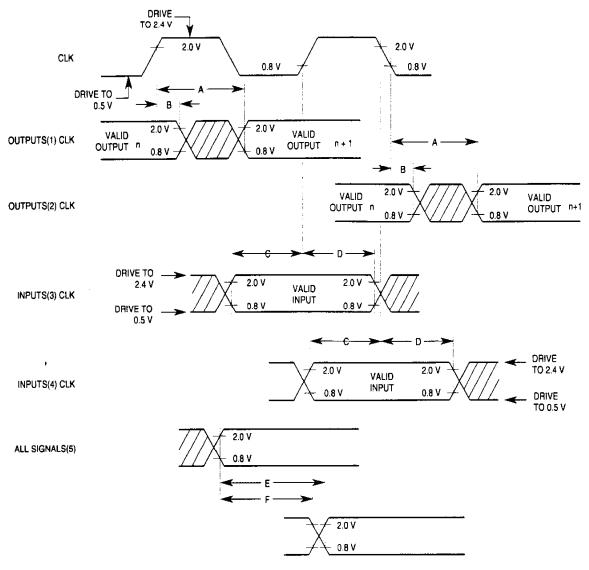

The measurement of the AC specifications is defined by the waveforms shown in Figure 3. To test the parameters guaranteed by Motorola, inputs must be driven to the voltage levels specified in the figure. Outputs are specified with minimum and/or maximum limits, as appropriate, and are measured as shown. Inputs are specified with minimum setup and hold times, and are measured as shown. Finally, the measurement for signal-to-signal specifications is shown.

Note that the testing levels used to verify conformance to the AC specifications do not affect the guaranteed DC operation of the device as specified in the DC electrical characteristics.

The MC68330V low voltage parts can operate up to 8.39 MHz or 16.78 MHz with a 3.3 V  $\pm$ 0.3 V supply. Separate part numbers are used to distinguish the operation of the parts according to the supply voltage. MC68330 is used throughout the specifications to refer to the 16.78- or 25.16-MHz parts at 5.0 V  $\pm$ 5%. MC68330V is used throughout the specifications to refer to the 8.39- or 16.78-MHz parts at 3.3 V  $\pm$ 0.3 V.

#### **NOTE**

The electrical specifications for the MC68330 25.16 MHz at 5.0 V  $\pm 5\%$  and the 3.3 V  $\pm 0.3$  V specifications for both the 8.39- and 16.78-MHz parts are preliminary.

#### NOTES:

- 1. This output timing is applicable to all parameters specified relative to the rising edge of the clock.

- 2. This output timing is applicable to all parameters specified relative to the falling edge of the clock.

- 3. This input timing is applicable to all parameters specified relative to the rising edge of the clock.

- 4. This input timing is applicable to all parameters specified relative to the falling edge of the clock.5. This timing is applicable to all parameters specified relative to the assertion/negation of another signal.

### LEGEND:

- A. Maximum output delay specification.

- B. Minimum output hold time.

- C. Minimum input setup time specification.

- D. Minimum input hold time specification.

- E. Signal valid to signal valid specification (maximum or minimum).

- F. Signal valid to signal invalid specification (maximum or minimum).

Figure 3. Drive Levels and Test Points for AC Specifications

**MOTOROLA**

INTEGRATED CPU32 PROCESSOR

# DC ELECTRICAL SPECIFICATIONS (See notes (a), (b), (c) corresponding to part operation,

GND = 0 Vdc, TA = 0 to 70°C; see numbered notes.)

| Characteristic                                                                                                                                                                                                                                                    | Symbol          | Min                   | Max                      | Unit     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------------|--------------------------|----------|

| Input High Voltage (Except Clock)                                                                                                                                                                                                                                 | ViH             | 2.0                   | Vcc                      |          |

| input Low Voltage                                                                                                                                                                                                                                                 | VIL             | GND                   | 0.8                      | ٧        |

| Clock Input High Voltage (EXTAL, X1)                                                                                                                                                                                                                              | VIHC            | 0.7 + V <sub>CC</sub> | V <sub>CC</sub> + 0.3    | V        |

| Undershoot                                                                                                                                                                                                                                                        | _               | _                     | -0.8                     | V        |

| Input Leakage Current (All Input-Only Pins)  Vin = VCC or GND                                                                                                                                                                                                     | lin             | -2.5                  | 2.5                      | μА       |

| Hi-Z(Off-State) Leakage Current (All Non-Crystal Outputs and I/O Pins—See Note 1) V <sub>in</sub> = 0.5/2.4 V                                                                                                                                                     | loz             | -20                   | 20                       | μА       |

| Signal Low Input Current  V <sub>IL</sub> = 0.8 V  TMS, TDI  Signal High Input Curent                                                                                                                                                                             | ΙL              | -0.2                  | -0.015                   | mA       |

| V <sub>IH</sub> = 2.0 V TMS, TDI                                                                                                                                                                                                                                  | lн              | -0.2                  | -0.015                   | mA       |

| Output High Voltage (See Notes 1 and 2) IOH = -0.8 mA, VCC = 4.75 V (All Non-Crystal Outputs except HALT, RESET)                                                                                                                                                  | Voн             | 2.4                   |                          | ٧        |

| Output Low Voltage (See Note 1) $I_{OL} = 2.0 \text{ mA}$ CLKOUT, FREEZE, IPIPE, IFETCH $I_{OL} = 3.2 \text{ mA}$ A23-A0, D15-D0, FC2-FC0, SIZ1, SIZ0 $I_{OL} = 5.3 \text{ mA}$ All Other Output-Only and Group 2 I/O Pins $I_{OL} = 15.3 \text{ mA}$ HALT, RESET | V <sub>OL</sub> | _                     | 0.5<br>0.5<br>0.5<br>0.5 | V        |

| Total Supply Current at 5 V ±5% @ 16.78 MHz RUN (see Note 3) STOP (VCO Off)                                                                                                                                                                                       | ICC<br>SICC     | -                     | 120<br>300               | mA<br>μA |

| Power Dissipation at 5 V ±5% @ 16.78 MHz                                                                                                                                                                                                                          | PD              | _                     | 630                      | mW       |

| Total Supply Current at 3.3 V ±0.3 V @ 8.39 MHz RUN (see Note 4) STOP (VCO Off)                                                                                                                                                                                   | ICC<br>SICC     | _                     | TBD<br>TBD               | mA<br>μA |

| Power Dissipation at 3.3 V ±0.3 V @ 8.39 MHz                                                                                                                                                                                                                      | PD              | _                     | TBD                      | mW       |

| Input Capacitance (See Notes 1 and 5) All Input-Only Pins All I/O Pins                                                                                                                                                                                            | Cin             | <del>-</del> -        | 10<br>20                 | pF       |

| Load Capacitance (See Note 5)                                                                                                                                                                                                                                     | CL              | _                     | 100                      | pF       |

#### NOTES:

- (a) The electrical specifications in this document for both the 8.39 and 16.78 MHz @ 3.3 V ±0.3 V are preliminary and apply only to the appropriate MC68330V low-voltage part.

- (b) The 25.16 MHz @ 5.0 V ±5% electrical specifications are preliminary.

- (c) For extended temperature parts T<sub>A</sub> = -40 to +85°C. These specifications are preliminary.

Input-Only Pins: BERR, BGACK, BKPT, BR, DSACK1, DSACK0, EXTAL, TCK, TDI, TMS

Output-Only Pins: A23-A0, AS, BG, CLKOUT, CS3-CS1, DS, FC2-FC0, FREEZE, IFETCH, IPIPE, LWE, RMC, R/W, SIZ1, SIZ0, TDO, UWE Input/Output Pins:

- Group 1: D15-D0

- Group 2: A31-A24, CSO, IRQ7- IRQ1, MODCK

- Group 3: HALT, RESET

- VOH specification for HALT and RESET is not applicable because they are open-drain pins.

- Supply current measured with system clock frequency of 16.78 MHz @ 5.25 V.

**INTEGRATED CPU32 PROCESSOR**

**MOTOROLA**

- Supply current measured with system clock frequency of 8.39 MHz @ 3.6 V. Capacitance is periodically sampled rather than 100% tested.

**MOTOROLA**

**INTEGRATED CPU32 PROCESSOR**

# AC ELECTRICAL SPECIFICATIONS CONTROL TIMING (See notes (a), (b), (c)

corresponding to part operation, GND = 0 Vdc, TA = 0 to 70°C; see numbered notes; see Figure 4.)

|                         |                                                                        |                     | 3.    | 3 V                                     | 3.3 V    | or 5.0 V                                | 5.   | 0 V                                     |      |

|-------------------------|------------------------------------------------------------------------|---------------------|-------|-----------------------------------------|----------|-----------------------------------------|------|-----------------------------------------|------|

| Num                     | Characteristic                                                         | Symbol              | 8.39  | MHz                                     | 16.7     | 8 MHz                                   | 25.1 | 6 MHz                                   | Unit |

|                         |                                                                        |                     | Min   | Max                                     | Min      | Max                                     | Min  | Max                                     |      |

|                         | System Frequency1                                                      | fsys                | đc    | 8.39                                    | dc       | 16.78                                   | dc   | 25.16                                   | MHz  |

|                         | Crystal Frequency                                                      | fXTAL               | 25    | 50                                      | 25       | 50                                      | 25   | 50                                      | kHz  |

|                         | On-Chip VCO System Frequency                                           | fsys                | 0.13  | 8.39                                    | 0.13     | 16.78                                   | 0.13 | 25.16                                   | MHz  |

|                         | On-Chip VCO Frequency Range                                            | fvco                | 0.1   | 16.78                                   | 0.1      | 33.5                                    | 0.1  | 50.3                                    | MHz  |

|                         | External Clock Operation                                               | f <sub>sys</sub>    | 0     | 8.39                                    | 0        | 16.78                                   | 0    | 25.16                                   | MHz  |

|                         | PLL Start-up Time <sup>2</sup>                                         | t <sub>rc</sub>     |       | 20                                      | _        | 20                                      | _    | 20                                      | ms   |

|                         | Limp Mode Clock Frequency <sup>3</sup> SYNCR X-bit = 0 SYNCR X-bit = 1 | flimp               | _     | f <sub>sys</sub> /2<br>f <sub>sys</sub> | <u>-</u> | f <sub>sys</sub> /2<br>f <sub>sys</sub> | -    | f <sub>sys</sub> /2<br>f <sub>sys</sub> | kHz  |

|                         | CLKOUT stability <sup>4</sup>                                          | ∆CLK                | 1     | +1                                      | -1       | +1                                      | ~1   | +1                                      | %    |

| 15                      | CLKOUT Period in Crystal Mode                                          | t <sub>cyc</sub>    | 119.2 | _                                       | 59.6     | _                                       | 39.7 | _                                       | ns   |

| 1B <sup>6</sup>         | External Clock Input Period                                            | <sup>t</sup> EXTcvc | 119.2 | _                                       | 59.6     | _                                       | 39.7 | -                                       | ns   |

| 1C <sup>7</sup>         | External Clock Input Period with PLL                                   | <sup>t</sup> EXTcvc | 119.2 | _                                       | 59.6     | _                                       | 39.7 | _                                       | пѕ   |

| 2,38                    | CLKOUT Pulse Width in Crystal Mode                                     | tcw                 | 56    | _                                       | 28       | _                                       | 18.7 | _                                       | ns   |

| 2B, 3B <sup>9</sup>     | CLKOUT Pulse Width in External Mode                                    | †EXTCW              | 53.6  |                                         | 26.8     | -                                       | 17.9 | -                                       | ns   |

| 2C,<br>3C <sup>10</sup> | CLKOUT Pulse Width in External w/PLL<br>Mode                           | tEXTCW              | 59.6  | _                                       | 29.8     | _                                       | 19.9 | -,                                      | ns   |

| 4,5                     | CLKOUT Rise and Fall Times                                             | t <sub>Crf</sub>    | -     | 10                                      | —        | 5                                       | _    | 4                                       | ns   |

#### NOTES:

- (a) The electrical specifications in this document for both the 8.39 and 16.78 MHz @ 3.3 V ±0.3 V are preliminary and apply only to the appropriate MC68330V low-voltage part.

- (b) The 25.16 MHz @ 5.0 V  $\pm$ 5% electrical specifications are preliminary.

- (c) For extended-temperature parts,  $T_A = -40$  to +85°C. These specifications are preliminary.

- 1. All internal registers retain data at 0 Hz.

- Assumes that a stable V<sub>CCSYN</sub> is applied, that an external filter capacitor with a value of 0.1 μF is attached to

the XFC pin, and that the crystal oscillator is stable. Lock time is measured from power-up to RESET release.

This specification also applies to the period required for PLL lock after changing the W and Y frequency control

bits in the synthesizer control register (SYNCR) while the PLL is running, and to the period required for the clock

to lock after LPSTOP.

- Determined by the initial control voltage applied to the on-chip VCO. The X-bit in the SYNCR controls a divide-bytwo scaler on the system clock output.

- CLKOUT stability is the average deviation from programmed frequency measured at maximum f<sub>sys</sub>.

Measurement is made with a stable external clock input applied using the PLL.

- All crystal mode clock specifications are based on using a 32.768-kHz crystal for the input.

- 6. When using the external clock input mode (MODCK reset value = 0 V), the minimum allowable tEXTcyc period will be reduced when the duty cycle of the signal applied to EXTAL exceeds 5% tolerance. The relationship between external clock input duty cycle and minimum tEXTcyc is expressed:

Minimum  $t_{EXTCyC}$  period = minimum  $t_{EXTCW}$  / (50% – external clock input duty cycle tolerance). Minimum external clock low and high times are based on a 45% duty cycle.

- 7. When using the external clock input mode with the PLL (MODCK reset value = 0 V), the external clock input duty cycle can be at a minimum 20% to produce a CLKOUT with a 50% duty cycle.

- 8. For crystal mode operation, the minimum CLKOUT pulse width is based on a 47% duty cycle.

- For external clock mode operation, the minimum CLKOUT pulse width is based on a 45% duty cycle, with a 50% duty cycle input clock.

- 10. For external clock w/PLL mode operation, the minimum CLKOUT pulse width is based on a 50% duty cycle.

**INTEGRATED CPU32 PROCESSOR**

**MOTOROLA**

- 11. For external clock mode, there is a 10–40 ns skew between the input clock signal and the output CLKOUT signal from the MC68330. Clock skew is measured from the rising edges of the clock signals.

- 12. For external clock mode w/PLL, there is a 5 ns skew between the input clock signal and the output CLKOUT signal from the MC68330. Clock skew is measured from the rising edges of the clock signals.

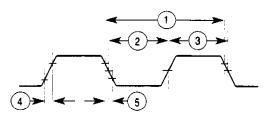

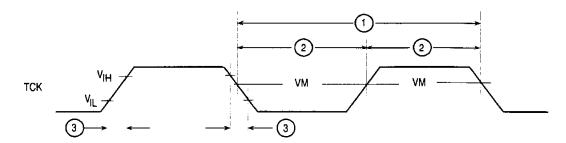

NOTES: 1. All timing except two and three is measured with respect to 0.8 V and 2.0 V.

2. Two and three are measured from 1.5 V to 1.5 V.

Figure 4. Clock Output Timing Diagram

## AC TIMING SPECIFICATIONS (See notes (a), (b), (c) corresponding to part operation, GND = 0 Vdc,

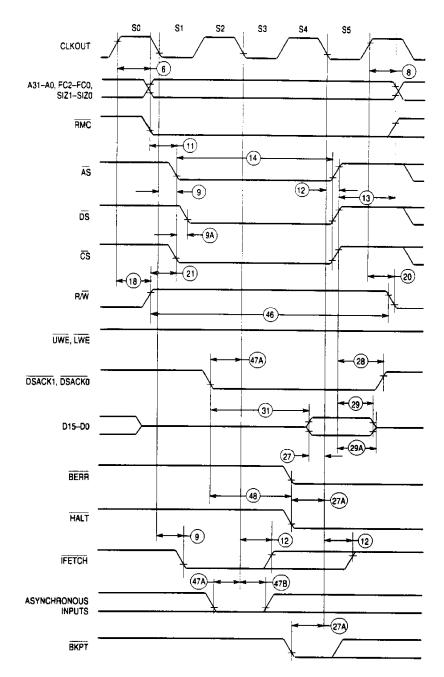

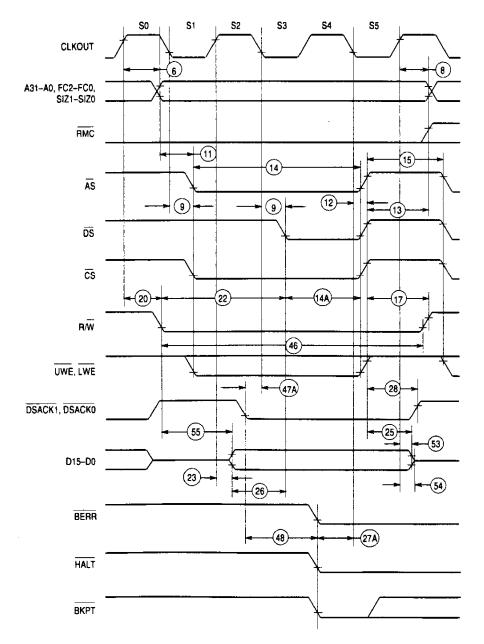

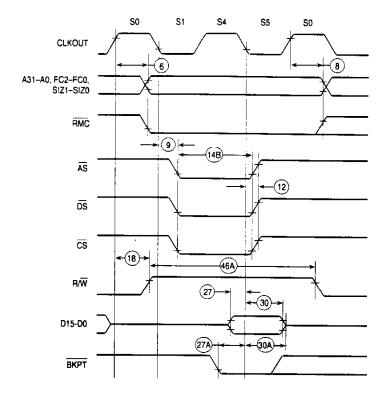

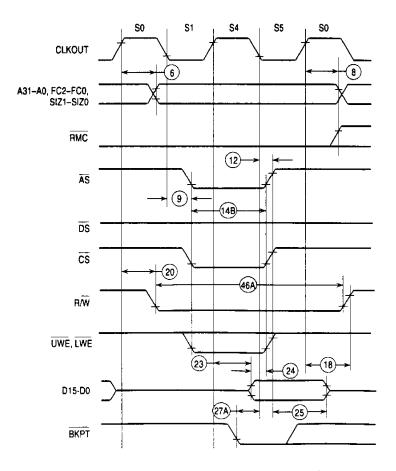

TA = 0 to 70°C; see numbered notes; see Figures 5–14.)

|                  |                                                                                |                    | 3.3  | 3 V | 3.3 V | 5.0 V | 5.0   | V   |      |

|------------------|--------------------------------------------------------------------------------|--------------------|------|-----|-------|-------|-------|-----|------|

| Num              | Characteristic                                                                 | Symbol             | 8.39 | MHz | 16.78 | MHz   | 25.16 | MHz | Unit |

|                  |                                                                                |                    | Min  | Max | Min   | Max   | Min   | Max | 1    |

| 6                | CLKOUT High to Address, FC, SIZ, AMC Valid                                     | <sup>t</sup> CHAV  | 0    | 60  | 0     | 30    | 0     | 20  | ns   |

| 7                | CLKOUT High to Address, Data, FC, SIZ, RMC<br>High Impedance                   | <sup>†</sup> CHAZx | 0    | 120 | 0     | 60    | 0     | 40  | пѕ   |

| 8                | CLKOUT High to Address, FC, SIZ, RMC Invalid                                   | <sup>†</sup> CHAZn | 0    | _   | 0     | _     | 0     | _   | пѕ   |

| 99               | CLKOUT Low to AS, DS, CS, UWE, LWE, IFETCH, IPIPE, IACKx Asserted              | †CLSA              | 3    | 60  | 3     | 30    | 3     | 20  | ns   |

| 9A <sup>2</sup>  | AS, CS to DS Asserted (Read)                                                   | †STSA              | -30  | 30  | -15   | 15    | -6    | 6   | ns   |

| 11               | Address, FC, SIZ, RMC Valid to AS, CS (and DS Read), UWE, LWE Asserted         | <sup>†</sup> AVSA  | 30   | _   | 15    | _ "   | 10    | _   | ns   |

| 12               | CLKOUT Low to AS, DS, CS, UWE, LWE, IFETCH, IPIPE, IACKX Negated               | tCLSN              | 3    | 60  | 3     | 30    | 3     | 20  | ns   |

| 13               | AS, DS, CS, UWE, LWE, IACKx Negated to Address, FC, SIZ Invalid (Address Hold) | <sup>†</sup> SNAI  | 30   | _   | 15    | _     | 10    | _   | ns   |

| 14 /             | AS, CS, UWE, LWE, (and DS Read) Width Asserted                                 | †SWA               | 200  | _   | 100   |       | 70    | _   | ns   |

| 14A              | DS Width Asserted (Write)                                                      | tswaw              | 90   |     | 45    | _     | 30    | _   | ns   |

| 14B              | AS, CS, UWE, LWE, IACKx (and DSRead) Width Asserted (Fast Termination Cycle)   | tswdw              | 80   | _   | 40    | _     | 30    |     | ns   |

| 15 <sup>3</sup>  | AS, DS, CS, UWE, LWE Width Negated                                             | tsn                | 80   | _   | 40    |       | 30    | _   | ns   |

| 16               | CLKOUT High to AS, DS, UWE, LWE, R/W<br>High Impedance                         | tCHSZ              | _    | 120 | _     | 60    | _     | 40  | ns   |

| 17               | AS, DS, CS, UWE, LWE Negated to R/W High                                       | <sup>†</sup> SNRN  | 30   |     | 15    | _     | 10    | _   | ns   |

| 18               | CLKOUT High to R/W High                                                        | <sup>t</sup> CHRH  | 0    | 60  | 0     | 30    | 0     | 20  | ns   |

| 20               | CLKOUT High to R/W Low                                                         | <sup>‡</sup> CHRL  | 0    | 60  | 0     | 30    | 0     | 20  | ns   |

| 219              | R/W High to AS, CS Asserted                                                    | <sup>†</sup> RAAA  | 30   |     | 15    |       | 10    | _   | ns   |

| 22               | R/W Low to DS Asserted (Write)                                                 | <sup>t</sup> RASA  | 140  | _   | 70    | _     | 47    | _   | ns   |

| 23               | CLKOUT High to Data-Out Valid                                                  | tCHDO              |      | 60  | 1     | 30    | _     | 20  | ns   |

| 24               | Data-Out Valid to Negating Edge of AS, CS, UWE, LWE (Fast Termination Write)   | <sup>†</sup> DVASN | 30   | _   | 15    | 1     | 10    |     | ns   |

| 25               | DS, CS, Negated to Data-Out Invalid (Data-Out Hold)                            | tsndoi             | 30   | _   | 15    | _     | 10    | _   | ns   |

| 26               | Data-Out Valid to DS Asserted (Write)                                          | <sup>t</sup> DVSA  | 30   |     | 15    |       | 10    | -   | ns   |

| 27               | Data-In Valid to CLKOUT Low (Data Setup)                                       | †DICL              | 10   | _   | 5     | _     | 5     |     | ns   |

| 27A              | Late BERR, HALT, BKPT Asserted to CLKOUT Low (Setup Time)                      | <sup>t</sup> BELCL | 40   | _   | 20    |       | 10    | _   | ns   |

| 28               | AS, DS, UWE, LWE Negated to DSACKx<br>BERR, HALT Negated                       | tSNDN              | 0    | 160 | O     | 80    | 0     | 50  | ns   |

| 29 <sup>4</sup>  | DS, CS Negated to Data-In Invalid (Data-In Hold)                               | tSNDi              | 0    |     | 0     |       | 0     |     | ns   |

| 29A <sup>4</sup> | DS, CS Negated to Data-In High Impedance                                       | tSHDI              |      | 120 | _     | 60    |       | 40  | ns   |

**INTEGRATED CPU32 PROCESSOR**

**MOTOROLA**

# AC TIMING SPECIFICATIONS (Continued)

|                   |                                                                  |                    | 3.3  | 3 V                      | 3.3 V | /5.0 V                   | 5.0   | 0 V                                           |        |

|-------------------|------------------------------------------------------------------|--------------------|------|--------------------------|-------|--------------------------|-------|-----------------------------------------------|--------|

| Num               | Characteristic                                                   | Symbol             | 8.39 | MHz                      | 16.78 | MHz                      | 25.16 | MHz                                           | Unit   |

|                   |                                                                  |                    | Min  | Max                      | Min   | Max                      | Min   | Max                                           | 1      |

| 30 <sup>4</sup>   | CLKOUT Low to Data-In Invalid (Fast Termination Hold)            | tCLDI              | 30   | _                        | 15    | _                        | 10    |                                               | ns     |

| 30A <sup>4</sup>  | CLKOUT Low to Data-In High Impedance                             | <sup>†</sup> CLDH  | _    | 180                      | _     | 90                       | _     | 60                                            | ns     |

| 31 <sup>5</sup>   | DSACKx Asserted to Data-In Valid                                 | †DADI              | _    | 100                      | _     | 50                       | _     | 32                                            | ns     |

| 31A               | DSACKx Asserted to DSACKx Valid (Skew)                           | †DADV              | _    | 60                       | _     | 30                       | _     | 20                                            | ns     |

| 32                | HALT and RESET Input Transition Time                             | <sup>t</sup> HRrf  | _    | 400                      |       | 200                      |       | 140                                           | ns     |

| 33                | CLKOUT Low to BG Asserted                                        | †CLBA              |      | 60                       | _     | 30                       | _     | 20                                            | ns     |

| 34                | CLKOUT Low to BG Negated                                         | tCLBN              |      | 60                       | _     | 30                       | _     | 20                                            | ns     |

| 35 <sup>6</sup>   | BR Asserted to BG Asserted (RMC Not Asserted)                    | <sup>†</sup> BRAGA | 1    | _                        | 1     | _                        | 1     | _                                             | CLKOUT |

| 37                | BGACK Asserted to BG Negated                                     | <sup>t</sup> GAGN  | 1    | 2.5                      | 1     | 2.5                      | 1     | 2.5                                           | CLKOUT |

| 39                | BG Width Negated                                                 | <sup>t</sup> GH    | 2    |                          | 2     | _                        | 2     |                                               | CLKOUT |

| 39A               | BG Width Asserted                                                | tga                | 1    |                          | 1     |                          | 1     | _                                             | CLKOUT |

| 46                | R/W Width Asserted (Write or Read)                               | <sup>†</sup> RWA   | 300  | _                        | 150   |                          | 100   | _                                             | ns     |

| 46A               | $R/\overline{W}$ Width Asserted (Fast Termination Write or Read) | tRWAS              | 180  | 1                        | 90    | 1                        | 60    | _                                             | ns     |

| 47A <sup>8</sup>  | Asynchronous Input Setup Time                                    | †AIST              | 15   | _                        | 8, 5  |                          | 5     |                                               | ns     |

| 47B               | Asynchronous Input Hold Time                                     | <sup>t</sup> AIHT  | 30   |                          | 15    | -                        | 10    | _                                             | ns     |

| 48 <sup>5,7</sup> | DSACKx Asserted to BERR, HALT Asserted                           | <sup>†</sup> DABA  |      | 60                       |       | 30                       | _     | 20                                            | ns     |

| 53                | Data-Out Hold from CLKOUT High                                   | tDOCH              | 0    | +                        | 0     | -                        | 0     |                                               | ns     |

| 54                | CLKOUT High to Data-Out High Impedance                           | tCHDH              | _    | 60                       | _     | 30                       | _     | 20                                            | ns     |

| 55                | R/W Asserted to Data Bus Impedance Change                        | †RADC              | 80   | -                        | 40    | -                        | 25    | _                                             | ns     |

| 56                | RESET Pulse Width (Reset Instruction)                            | tHRPW              | 512  | _                        | 512   | -                        | 512   | _                                             | CLKOUT |

| 56A               | RESET Pulse Width (Input from External Device)                   | tRPWI              | 590  | _                        | 590   | -                        | 590   |                                               | CLKOUT |

| 57                | BERR Negated to HALT Negated (Rerun)                             | <sup>†</sup> BNHN  | 0    | _                        | 0     |                          | 0     | _                                             | ns     |

| 70                | CLKOUT Low to Data Bus Driven (Show Cycle)                       | †SCLDD             | 0    | 60                       | 0     | 30                       | 0     | 20                                            | ns     |

| 71                | Data Setup Time to CLKOUT Low (Show Cycle)                       | tSCLDS             | 30   | _                        | 15    | _                        | 10    | _                                             | ns     |

| 72                | Data Hold from CLKOUT Low (Show Cycle)                           | tSCLDH             | 20   | _                        | 10    | -                        | 6     |                                               | ns     |

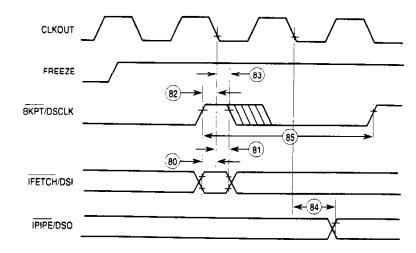

| 80                | DSI Input Setup Time                                             | tosisu             | 30   | _                        | 15    | _                        | 10    | _                                             | ns     |

| 81                | DSI Input Hold Time                                              | <sup>t</sup> DSIH  | 20   |                          | 10    | _                        | 6     | _                                             | ns     |

| 82                | DSCLK Setup Time                                                 | tDSCSU             | 30   | _                        | 15    |                          | 10    |                                               | ns     |

| 83                | DSCLK Hold Time                                                  | <sup>t</sup> DSCH  | 20   | _                        | 10    |                          | 6     |                                               | ns     |

| 84                | DSO Delay Time                                                   | tosoo              | _    | t <sub>cyc</sub><br>+ 50 | _     | t <sub>cyc</sub><br>+ 25 | _     | t <sub>cyc</sub><br>+ 16                      | ns     |

| 85                | DSCLK Cycle                                                      | tpsccyc            | 2    |                          | 2     |                          | 2     | <u>                                      </u> | CLKOUT |

**MOTOROLA**

**INTEGRATED CPU32 PROCESSOR**

### AC TIMING SPECIFICATIONS (Concluded)

|     |                                      |        | 3.   | 3 V | 3.3 V | 5.0 V | 5.0   | O V |      |

|-----|--------------------------------------|--------|------|-----|-------|-------|-------|-----|------|

| Num | Characteristic                       | Symbol | 8.39 | MHz | 16.78 | MHz   | 25.16 | MHz | Unit |

|     |                                      |        | Min  | Max | Min   | Max   | Min   | Max |      |

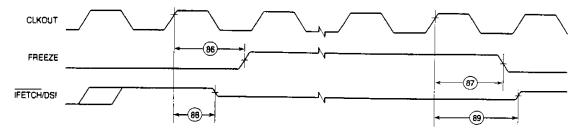

| 86  | CLKOUT High to FREEZE Asserted       | tFRZA  | 0    | 100 | 0     | 50    | 0     | 35  | ns   |

| 87  | CLKOUT High to FREEZE Negated        | tFRZN  | 0    | 100 | 0     | 50    | 0     | 35  | ns   |

| 88  | CLKOUT High to IFETCH High Impedance | tIFZ   | 0    | 100 | 0     | 50    | 0     | 35  | ns   |

| 89  | CLKOUT High to IFETCH Valid          | tiF    | 0    | 100 | 0     | 50    | 0     | 35  | ns   |

#### NOTES:

- (a) The electrical specifications in this document for both the 8.39 and 16.78 MHz @ 3.3 V ±0.3 V are preliminary and apply only to the appropriate MC68330V low-voltage part.

- (b) The 25.16 MHz @ 5.0 V ±5% electrical specifications are preliminary.

- (c) For extended-temperature parts,  $T_A = -40$  to  $+85^{\circ}$ C. These specifications are preliminary.

- 1. All AC timing is shown with respect to 0.8 V and 2.0 V levels unless otherwise noted.

- 2. This number can be reduced to 5 ns if strobes have equal loads.

- If multiple chip selects are used, the CS width negated (#15) applies to the time from the negation of a heavily loaded chip select to the assertion of a lightly loaded chip select.

- 4. These hold times are specified with respect to DS or CS on asynchronous reads and with respect to CLKOUT on fast termination reads. The user is free to use either hold time for fast termination reads.

- 5. If the asynchronous setup time (#47) requirements are satisfied, the DSACKx low to data setup time (#31) and DSACKx low to BERR low setup time (#48) can be ignored. The data must only satisfy the data-in to CLKOUT low setup time (#27) for the following clock cycle: BERR must only satisfy the late BERR low to CLKOUT low setup time (#27A) for the following clock cycle:

- 6. To ensure coherency during every operand transfer, BG will not be asserted in response to BR until after the current operand transfer cycles are complete and RMC is negated.

- 7. In the absence of DSACKx, BERR is an asynchronous input using the asynchronous setup time (#47).

- 8. Specification #47A for 16.78 MHz @ 3.3 V ±0.3V will be 8 ns.

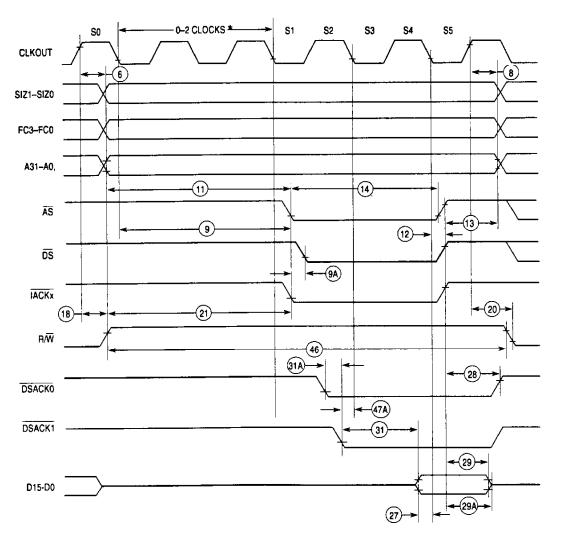

- During interrupt acknowledge cycles, up to two wait states may be inserted by the processor between states S0 and S1.

NOTE: All timing is shown with respect to 0.8V and 2.0V levels.

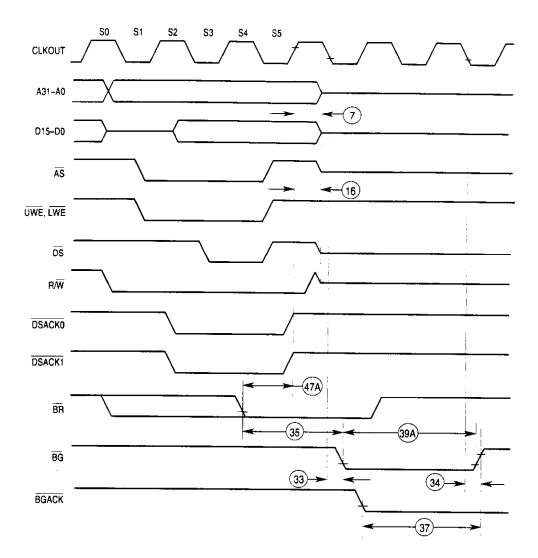

Figure 5. Read Cycle Timing Diagram

**MOTOROLA**

**INTEGRATED CPU32 PROCESSOR**

NOTE: All timing is shown with respect to 0.8V and 2.0V levels.

Figure 6. Write Cycle Timing Diagram

Figure 7. Fast Termination Read Cycle Timing Diagram

Figure 8. Fast Termination Write Cycle Timing Diagram

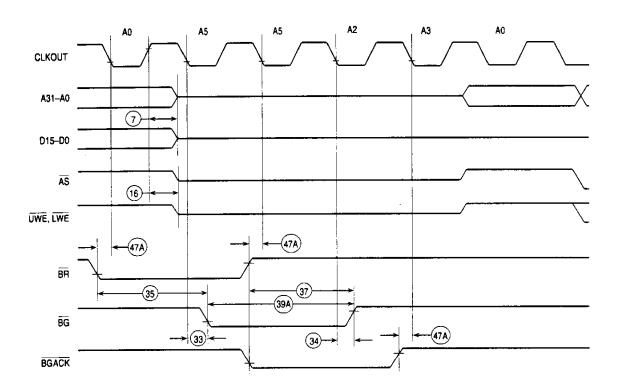

Figure 9. Bus Arbitration Timing—Active Bus Case

Figure 10. Bus Arbitration Timing—Idle Bus Case

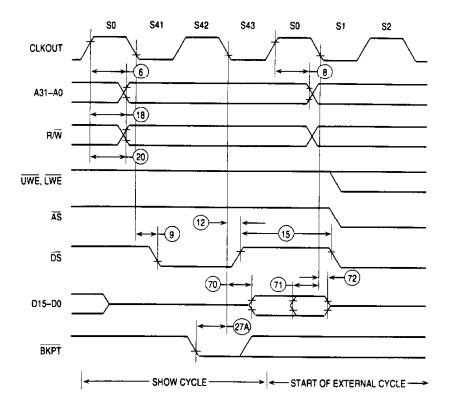

Figure 11. Show Cycle Timing Diagram

<sup>\*</sup>Up to two wait states may be inserted by the processor between states S0 and S1.

Figure 12. IACK Cycle Timing Diagram

Figure 13. Background Debug Mode Serial Port Timing

Figure 14. Background Debug Mode FREEZE Timing

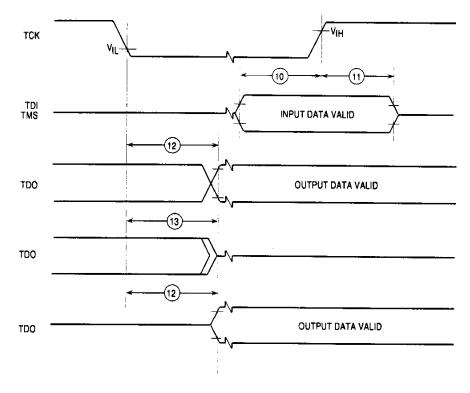

# **IEEE 1149.1 ELECTRICAL SPECIFICATIONS** (See notes (a), (b), (c) corresponding to part operation, GND = 0 Vdc, TA = 0 to 70°C; see Figures 15–17.)

|      |                                         | 3.3   | 3 V  | 3.3 V c | or 5.0 V | 5.0   | 0 V      |      |

|------|-----------------------------------------|-------|------|---------|----------|-------|----------|------|

| Num. | Characteristic                          | 8.39  | MHz  | 16.78   | MHz      | 25.16 | MHz      | Unit |

|      |                                         | Min   | Max  | Min     | Max      | Min   | Max      |      |

|      | TCK Frequency of Operation              | 0     | 8.39 | 0       | 16.78    | 0     | 25.16    | MHz  |

| 1    | TCK Cycle Time in Crystal Mode          | 119.2 | _    | 59.6    |          | 39.7  |          | ns   |

| 2    | TCK Clock Pulse Width Measured at 1.5 V | 56    | _    | 28      |          | 18.7  |          | ns   |

| 3    | TCK Rise and Fall Times                 | 0     | 10   | 0       | 5        | 0     | 3        | ns   |

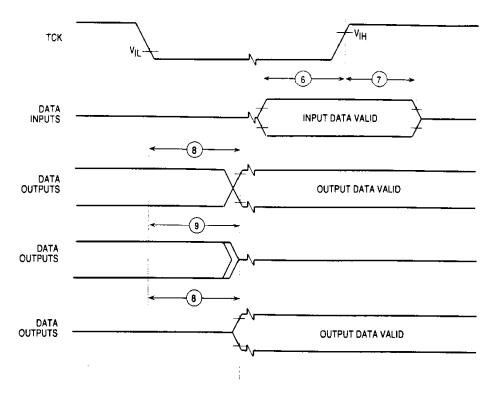

| 6    | Boundary Scan Input Data Setup Time     | 32    | _    | 16      | _        | 10    | <u> </u> | ns   |

| 7    | Boundary Scan Input Data Hold Time      | 52    |      | 26      | _        | 18    | _        | ns   |

| 8    | TCK Low to Output Data Valid            | 0     | 80   | 0       | 40       | 0     | 26       | ns   |

| 9    | TCK Low to Output High Impedance        | 0     | 120  | 0       | 60       | 0     | 40       | ns   |

| 10   | TMS, TDI Data Setup Time                | 30    |      | 15      | <u> </u> | 10    | _        | ns   |

| 11   | TMS, TDI Data Hold Time                 | 30    | _    | 15      |          | 10    | _        | ns   |

| 12   | TCK Low to TDO Data Valid               | 0     | 50   | 0       | 25       | 0     | 16       | ns   |

| 13   | TCK Low to TDO High Impedance           | 0     | 50   | 0       | 25       | 0     | 16       | ns   |

#### NOTES:

- (a) The electrical specifications in this document for both the 8.39 and 16.78 MHz @ 3.3 V ±0.3 V are preliminary and apply only to the appropriate MC68330V low-voltage part.

- (b) The 25.16 MHz @ 5.0 V  $\pm$ 5% electrical specifications are preliminary.

- (c) For extended-temperature parts,  $T_A = -40$  to +85°C. These specifications are preliminary.

Figure 15. TCK Input Timing Diagram

Figure 16. Boundary Scan Timing Diagram

Figure 17. Test Access Port Timing Diagram

MOTOROLA

**INTEGRATED CPU32 PROCESSOR**

# ORDERING INFORMATION AND MECHANICAL DATA

The following paragraphs discuss the ordering information, pin assignments, and package dimensions for the MC68330.

### MC68330 ORDERING INFORMATION

| Supply<br>Voltage | Package Type                        | Frequency (MHz)               | Temperature                                    | Order Number                                |

|-------------------|-------------------------------------|-------------------------------|------------------------------------------------|---------------------------------------------|

| 5.0 V             | Plastic Quad Flat Pack<br>FE Suffix | 0-16.78<br>0-16.78<br>0-25.16 | 0°C to +70°C<br>-40°C to +85°C<br>0°C to +70°C | MC68330FE16<br>MC68330CFE16<br>MC68330FE25  |

| 5.0 V             | Plastic Quad Flat Pack<br>FG Suffix | 0–16.78<br>0–16.78            | 0°C to +70°C<br>-40°C to +85°C                 | MC68330FG16<br>MC68330CFG16                 |

| 3.3 V             | Plastic Quad Flat Pack<br>FE Suffix | 0-8.39<br>0-8.39<br>0-16.78   | 0°C to +70°C<br>-40°C to +85°C<br>0°C to +70°C | MC68330FE8V<br>MC68330CFE8V<br>MC68330FE16V |

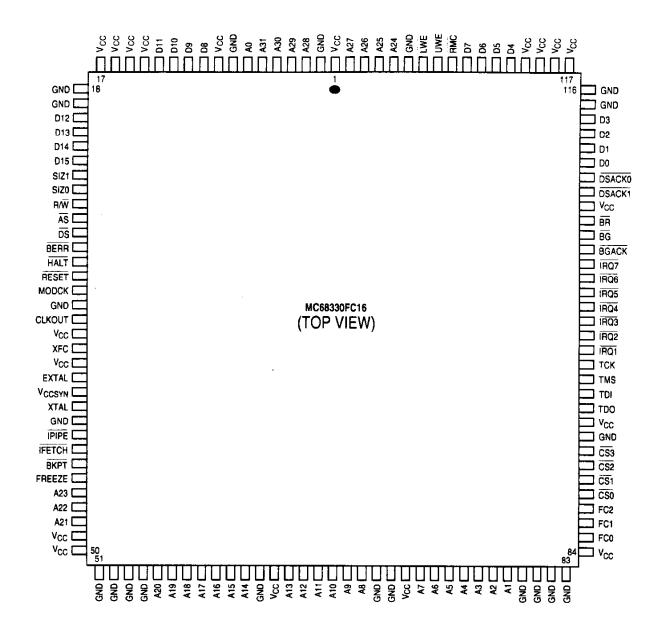

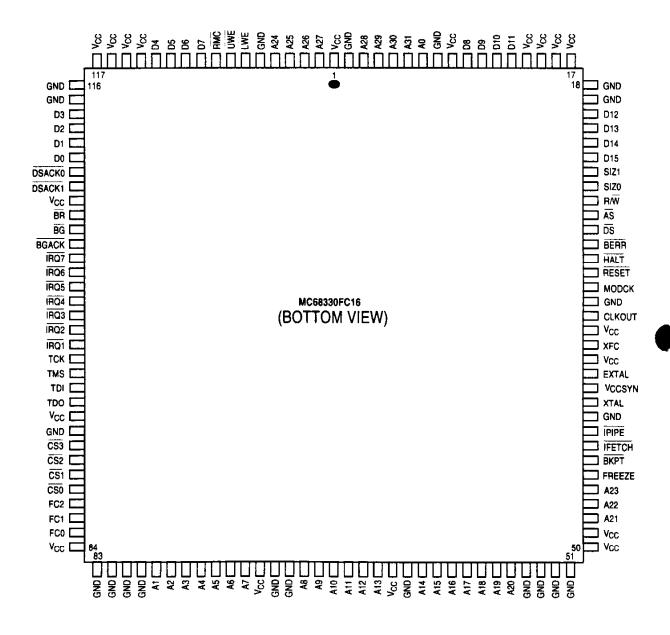

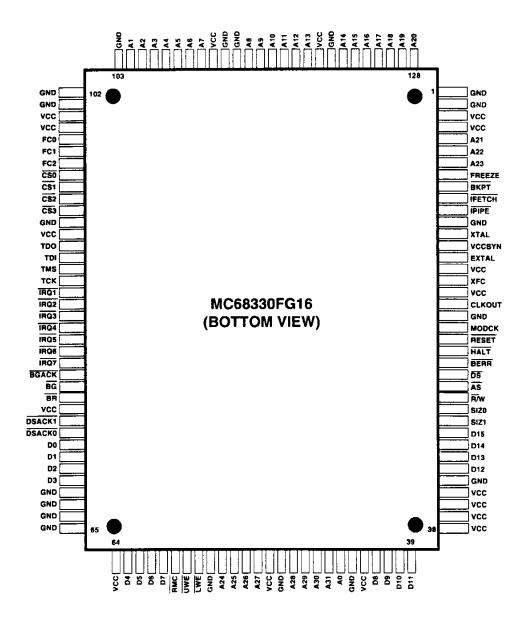

### **PIN ASSIGNMENTS**

### 132-PIN PLASTIC QUAD FLAT PACK (FC)

**MOTOROLA**

**INTEGRATED CPU32 PROCESSOR**

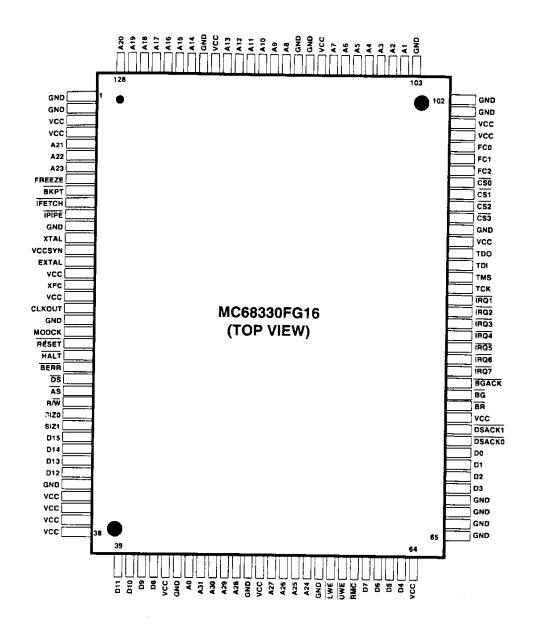

# 128-PIN PLASTIC QUAD FLAT PACK (FG)

**MOTOROLA**

**INTEGRATED CPU32 PROCESSOR**

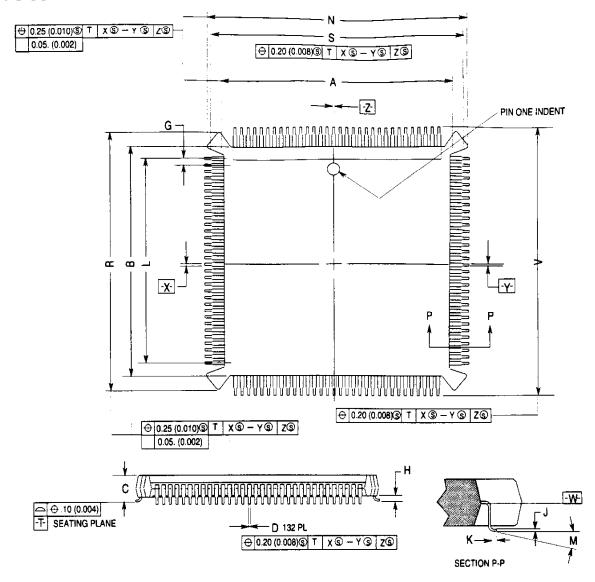

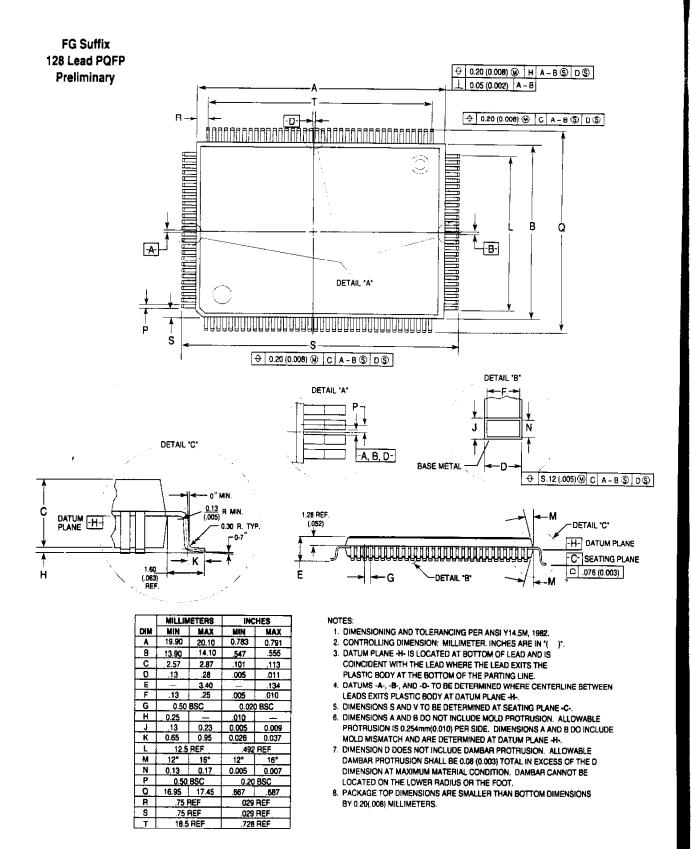

# PACKAGE DIMENSIONS

### **FC SUFFIX**

|     | MILLIM | ETERS | INC   | HES   |

|-----|--------|-------|-------|-------|

| DIM | MIN    | MAX   | MIN   | MAX   |

| Α   | 24.06  | 24.20 | 0.947 | 0.953 |

| В   | 24.06  | 24.20 | 0.947 | 0.953 |

| C   | 4.07   | 4.57  | 0.160 | 0.180 |

| D   | 0.21   | 0.30  | 0.008 | 0.012 |

| G   | 0.64   | BSC   | 0.029 | BSC   |

| Н   | 0.51   | 1.01  | 0.020 | 0.040 |

| J   | 0.16   | 0.20  | 0.006 | 0.008 |

| К   | 0.51   | 0.76  | 0.020 | 0.030 |

| М   | 0°     | 8°    | 0°    | 8°    |

| N   | 27.88  | 28.01 | 1.097 | 1.103 |

| R   | 27.88  | 28.01 | 1.097 | 1.103 |

| S   | 27.31  | 27.55 | 1.075 | 1.085 |

| V   | 27.31  | 27.55 | 1.075 | 1.085 |

#### NOTES

- 1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

- 2. CONTROLLING DIMENSION: INCHES

- 2. CONTROLLING DIMENSION: INCLUDE MOLD PROTRUSION.

ALLOWABLE MOLD PROTRUSION FOR DIMENSIONS A AND B IS 0.25 (0.010), FOR DIMENSIONS N AND R IS 0.18 (0.007).

- DATUM PLANE -W- IS LOCATED AT THE UNDERSIDE OF LEADS

WHERE LEADS EXIT PACKAGE BODY.

- DATUMS X-Y AND Z TO BE DETERMINED WHERE CENTER LEADS EXIT PACKAGE BODY AT DATUM -W-.

- 6. DIM S AND V TO BE DETERMINED AT SEATING PLANE, DATUM -T-.

- 7. DIM A, B, N AND R TO BE DETERMINED AT DATUM PLANE -W-.

**MOTOROLA**

**INTEGRATED CPU32 PROCESSOR**

### **DOCUMENTATION**

The documents listed in the following table contain detailed information on the MC68330. These documents may be obtained from the Literature Distribution Centers at the addresses listed at the bottom of this page.

| Document Number | Document Name                                 |

|-----------------|-----------------------------------------------|

| BR1114/D        | M68300 Integrated Processor Family            |

| MC68330UM/AD    | MC68330 User's Manual                         |

| M68000PM/AD     | M68000 Family Programmer's Reference Manual   |

| AN1063/D        | DRAM Controller for the MC68340               |

| AN453           | Software Implementation of SPI on the MC68340 |

| BR573/D         | M68340 Evaluation System Product Brief        |

| BR729/D         | The 68K Source                                |

| BR1407/D        | 3.3 Volt Logic and Interface Circuits         |

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and (A) are registered trademarks of Motorola, Inc. Motorola, inc. is an Equal Opportunity/Affirmative Action Employer.

#### **Literature Distribution Centers:**

USA: Motorola Literature Distribution; P.O. Box 20912; Phoenix, Arizona 85036.

EUROPE: Motorola Ltd.; European Literature Centre; 88 Tanners Drive, Blakelands, Milton Keynes, MK14 5BP, England.

JAPAN: Nippon Motorola Ltd.; 4-32-1, Nishi-Gotanda, Shinagawa-ku, Tokyo 141, Japan.

ASIA PACIFIC: Motorola Semiconductors H.K. Ltd.; Silicon Harbour Center, No. 2 Dai King Street, Tai Po Industrial Estate, Tai Po, N.T., Hong Kong.

MOTOROLA

1ATX30114-2 PRINTED IN USA 9/92 IMPERIAL LITHO 87867 18,000 MPU YGABAA