# **DSP Builder Handbook**

# **Volume 2: DSP Builder Standard Blockset**

101 Innovation Drive San Jose, CA 95134 www.altera.com

HB\_DSPB\_STD-2.0

Document last updated for Altera Complete Design Suite version: Document publication date: 12.0 June 2012

© 2012 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and service any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

## **Contents**

### Section I. DSP Builder Standard Blockset User Guide

#### **Chapter 1. About DSP Builder**

| Release Information                         | . 1–1 |

|---------------------------------------------|-------|

| Device Family Support                       | . 1–1 |

| Memory Options                              | . 1–1 |

| Features                                    | . 1–2 |

| General Description                         | . 1–2 |

| High-Speed DSP with Programmable Logic      | . 1–3 |

| Interoperability with the Advanced Blockset |       |

|                                             |       |

### **Chapter 2. Getting Started**

| Design Flow                               |      |

|-------------------------------------------|------|

| Creating the Amplitude Modulation Model   |      |

| Create a New Model                        |      |

| Add the Sine Wave Block                   |      |

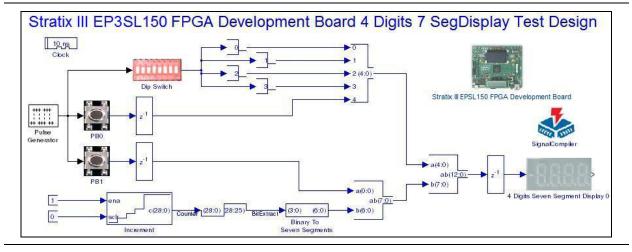

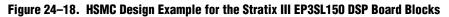

| Add the SinIn Block                       |      |

| Add the Delay Block                       |      |

| Add the SinDelay and SinIn2 Blocks        |      |

| Add the Mux Block                         |      |

| Add the Random Bitstream Block            |      |

| Add the Noise Block                       |      |

| Add the Bus Builder Block                 |      |

| Add the GND Block                         |      |

| Add the Product Block                     |      |

| Add the StreamMod and StreamBit Blocks    |      |

| Add the Scope Block                       |      |

| Add a Clock Block                         |      |

| Simulating the Model in Simulink          |      |

| Compiling the Design                      |      |

| Performing RTL Simulation                 |      |

| Adding the Design to a Quartus II Project |      |

| Creating a Quartus II Project             |      |

| Add the DSP Builder Design to the Project | 2–22 |

### **Chapter 3. Design Rules and Procedures**

| DSP Builder Naming Conventions                           |      |

|----------------------------------------------------------|------|

| Using a MATLAB Variable                                  |      |

| Fixed-Point Notation                                     |      |

| Binary Point Location in Signed Binary Fractional Format |      |

| Bit Width Design Rule                                    |      |

| Data Width Propagation                                   |      |

| Tapped Delay Line                                        |      |

| Arithmetic Operation                                     |      |

| Frequency Design Rules                                   |      |

| Single Clock Domain                                      |      |

| Multiple Clock Domains                                   |      |

| Using Clock and Clock_Derived Blocks                     | 3–10 |

| Clock Assignment                                                                  | 3–11 |

|-----------------------------------------------------------------------------------|------|

| Using the PLL Block                                                               |      |

| Using Advanced PLL Features                                                       | 3–15 |

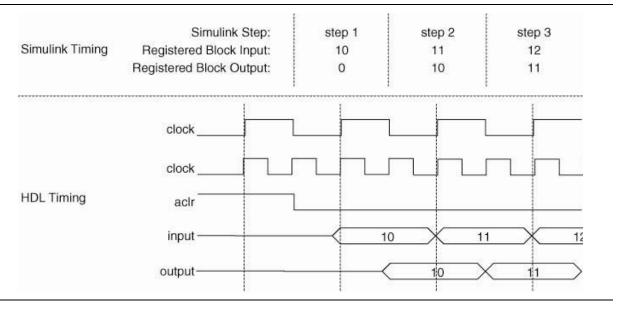

| Timing Semantics Between Simulink and HDL Simulation                              | 3–16 |

| Simulink Simulation Model                                                         | 3–16 |

| HDL Simulation Models                                                             | 3–16 |

| Startup & Initial Conditions                                                      |      |

| Initial Reset of HDL Import Blocks and MegaCore Functions in Simulink Simulations | 3–17 |

| DSP Builder Global Reset Circuitry                                                | 3–17 |

| Reference Timing Diagram                                                          | 3–18 |

| Signal Compiler and TestBench Blocks                                              | 3–19 |

| Design Flows for Synthesis, Compilation and Simulation                            | 3–19 |

| Hierarchical Design                                                               |      |

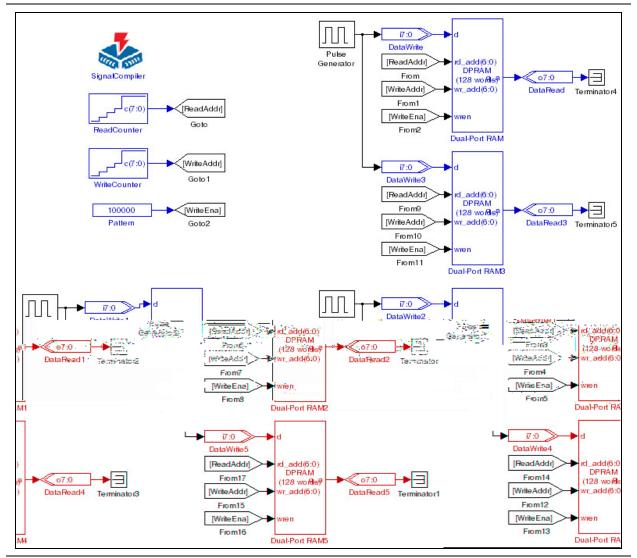

| Goto and From Block Support                                                       | 3–21 |

| Create Black Box and HDL Import                                                   |      |

| Using a MATLAB Array or .hex File to Initialize a Block                           |      |

| Comparison Utility                                                                |      |

| Adding Comments to Blocks                                                         | 3–24 |

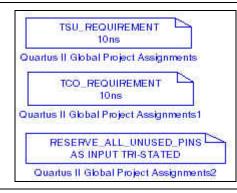

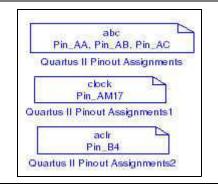

| Adding Quartus II Constraints                                                     | 3–24 |

| Displaying Port Data Types                                                        |      |

| Displaying the Pipeline Depth                                                     | 3–25 |

| Updating HDL Import Blocks                                                        |      |

| Analyzing the Hardware Resource Usage                                             |      |

| Loading Additional ModelSim Commands                                              |      |

| Making Quartus II Assignments to Block Entity Names                               | 3–28 |

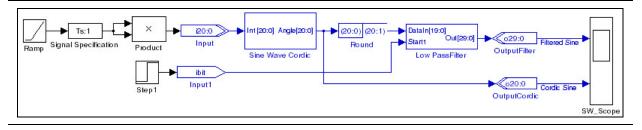

### Chapter 4. Using MegaCore Functions

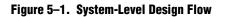

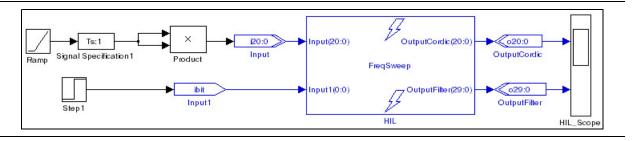

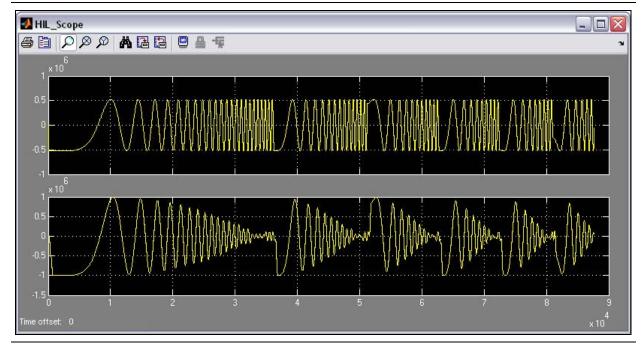

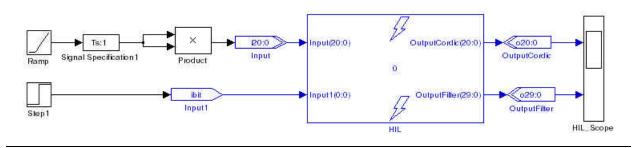

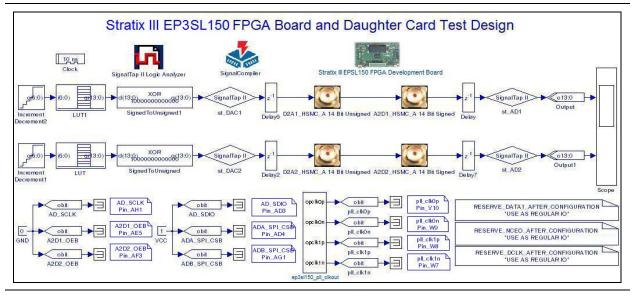

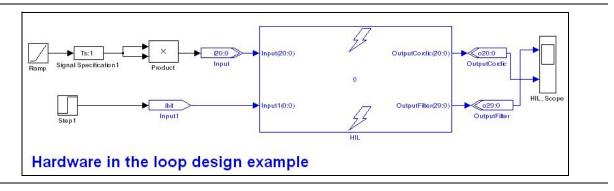

### Chapter 5. Using HIL

| HIL Design Flow    |  |

|--------------------|--|

| HIL Requirements   |  |

| HIL Design Example |  |

| Burst Mode                                      | 5-6 |

|-------------------------------------------------|-----|

| Using Burst Mode                                | 5-6 |

| Troubleshooting HIL Designs                     | 5-7 |

| Fails to Load the Specified Quartus II Project  | 5–7 |

| No Inputs Found From the Quartus II Project     | 5–7 |

| No Outputs Found From the Quartus II Project    | 5–7 |

| HIL Design Stays in Reset During Simulation     | 5–7 |

| HIL Compilation Appears to Hang                 | 5–8 |

| Scan JTAG Fails to Find Correct Cable or Device | 5–8 |

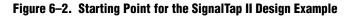

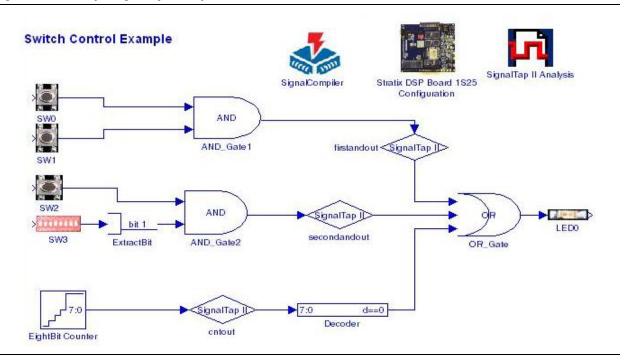

### Chapter 6. Performing SignalTap II Logic Analysis

| SignalTap II Design Flow                              | 6–1 |

|-------------------------------------------------------|-----|

| SignalTap II Nodes                                    |     |

| SignalTap II Trigger Conditions                       | 6–2 |

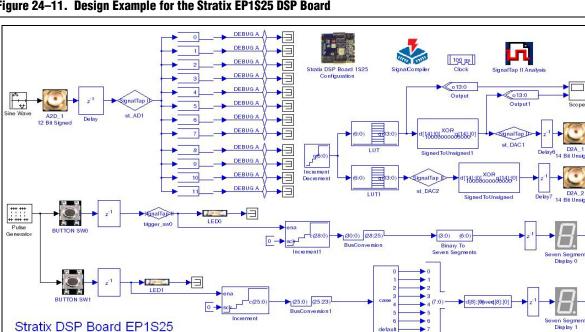

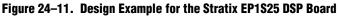

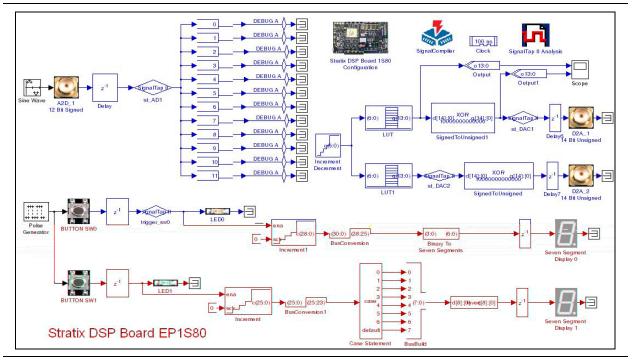

| SignalTap II Example Designs                          |     |

| Opening the Design Example                            | 6–3 |

| Adding the Configuration and Connector Blocks         | 6-4 |

| Specifying the Nodes to Analyze                       |     |

| Turning On the SignalTap II Option in Signal Compiler |     |

| Specifying the Trigger Levels                         | 6–7 |

| Performing SignalTap II Analysis                      | 6–7 |

|                                                       |     |

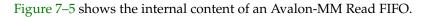

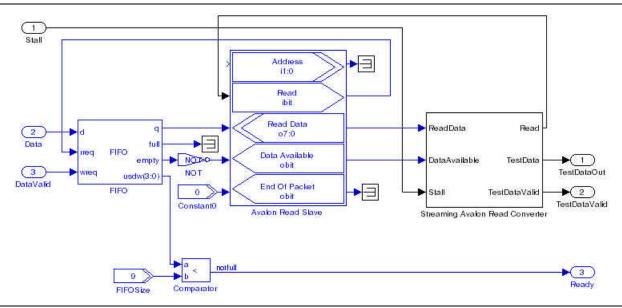

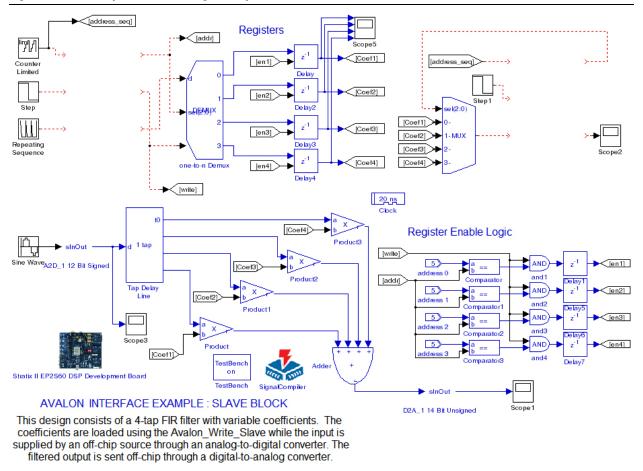

### Chapter 7. Using the Interfaces Library

| Avalon-MM Interface                           |  |

|-----------------------------------------------|--|

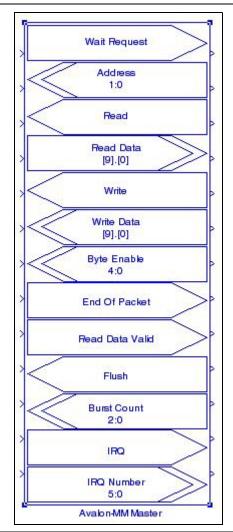

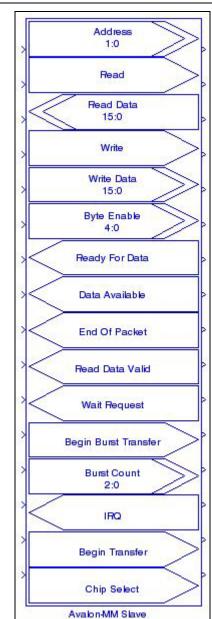

| Avalon-MM Interface Blocks                    |  |

| Avalon-MM Slave Block                         |  |

| Avalon-MM Master Block                        |  |

| Wrapped Blocks                                |  |

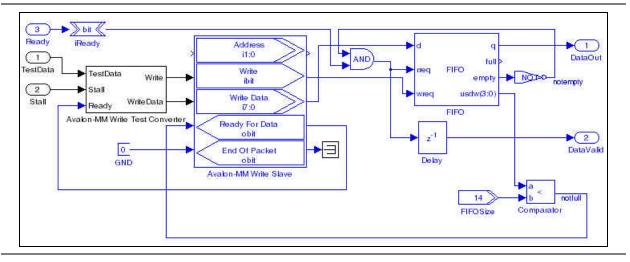

| Avalon-MM Write FIFO                          |  |

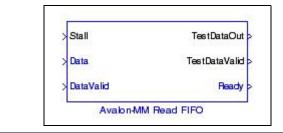

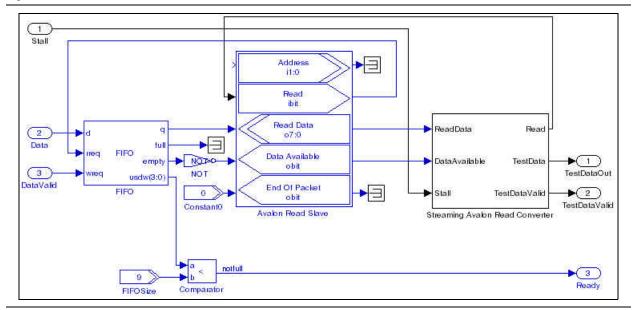

| Avalon-MM Read FIFO Buffer                    |  |

| Avalon-MM Interface Blocks Design Example     |  |

| Adding Avalon-MM Blocks to the Design Example |  |

| Verifying the Design                          |  |

| Running Signal Compiler                       |  |

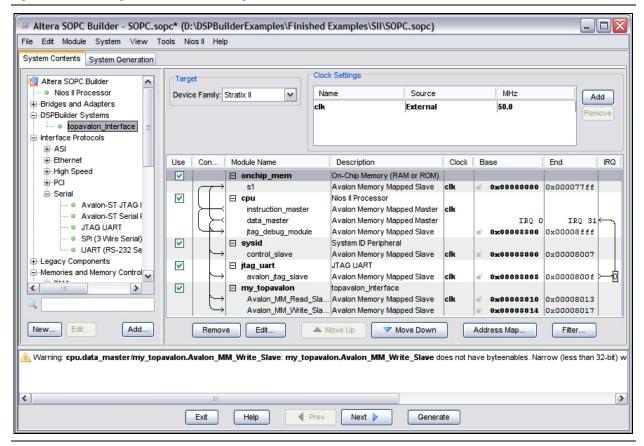

| Instantiating the Design in SOPC Builder      |  |

| Compiling the Quartus II Project              |  |

| Testing the DSP Builder Block from Software   |  |

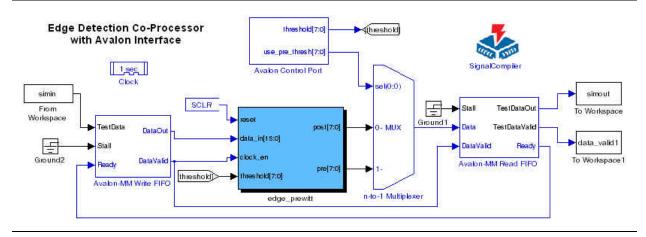

| Avalon-MM FIFO Design Example                 |  |

| Opening the Design Example                    |  |

| Compiling the Design                          |  |

| Instantiating the Design in SOPC Builder      |  |

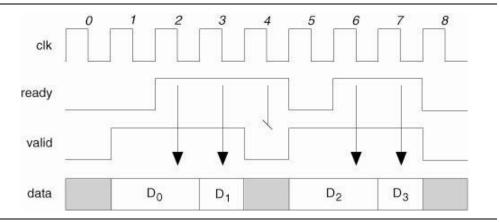

| Avalon-ST Interface                           |  |

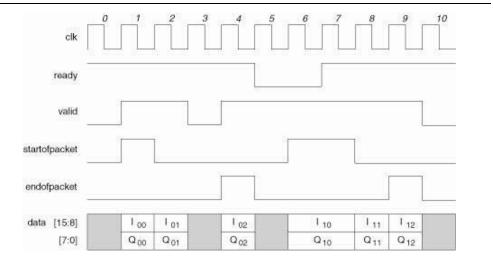

| Avalon-ST Packet Formats                      |  |

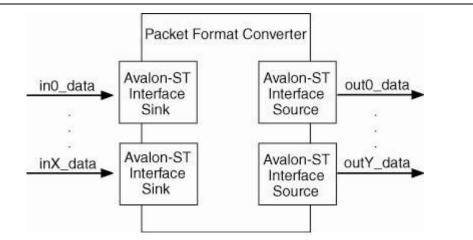

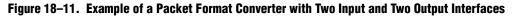

| Avalon-ST Packet Format Converter             |  |

### Chapter 8. Using Black Boxes for HDL Subsystems

| 8–1 |

|-----|

| 8–1 |

| 8–1 |

| 8–2 |

| 8–4 |

| 8–6 |

| 8–6 |

|     |

V

| Building the Black-Box SubSystem Simulation Model               | 8–8  |

|-----------------------------------------------------------------|------|

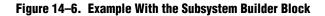

| Simulating the Subsystem Builder Model                          | 8–11 |

| Adding VHDL Dependencies to the Quartus II Project and ModelSim | 8–11 |

| Simulate the Design in ModelSim                                 | 8–12 |

### **Chapter 9. Using Custom Library Blocks**

| Creating a Custom Library Block                     | 9–1 |

|-----------------------------------------------------|-----|

| Creating a Library Model File                       | 9–2 |

| Building the HDL Subsystem Functionality            | 9–2 |

| Defining Parameters Using the Mask Editor           | 9–3 |

| Linking the Mask Parameters to the Block Parameters |     |

| Making the Library Block Read Only                  | 9–5 |

| Adding the Library to the Simulink Library Browser  | 9–5 |

| Synchronizing a Custom Library                      | 9–6 |

### Chapter 10. Adding a Board Library

| Creating a New Board Description   |  |

|------------------------------------|--|

| Predefined Components              |  |

| Component Types                    |  |

| Component Description File         |  |

| Example Component Description File |  |

| Board Description File             |  |

| Header Section                     |  |

| Board Description Section          |  |

| Building the Board Library         |  |

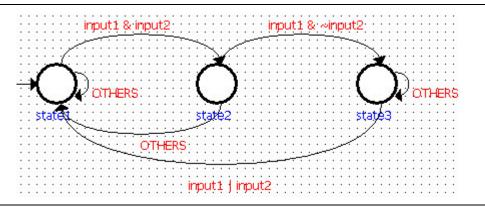

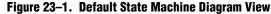

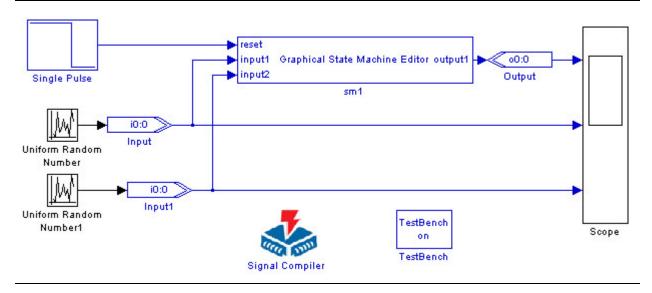

### Chapter 11. Using the State Machine Library

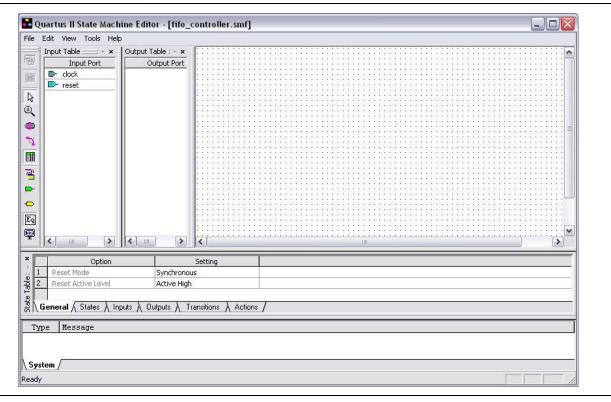

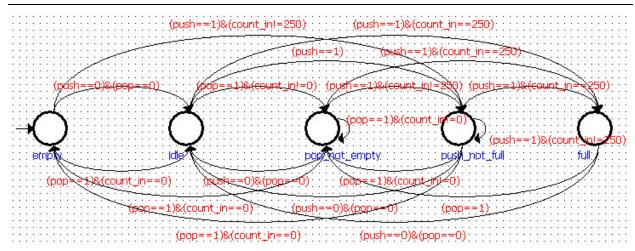

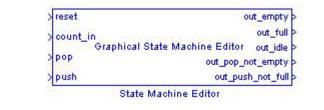

| Using the State Machine Table Block  | 11–2 |

|--------------------------------------|------|

| Using the State Machine Editor Block | 11–7 |

### Chapter 12. Managing Projects and Files

| Integration with Source Control Systems                              |  |

|----------------------------------------------------------------------|--|

| HDL Import                                                           |  |

| MegaCore Functions                                                   |  |

| Memory Initialization Files                                          |  |

| Exporting HDL                                                        |  |

| Using Exported HDL                                                   |  |

| Migration of DSP Builder (Standard Blockset) Files to a New Location |  |

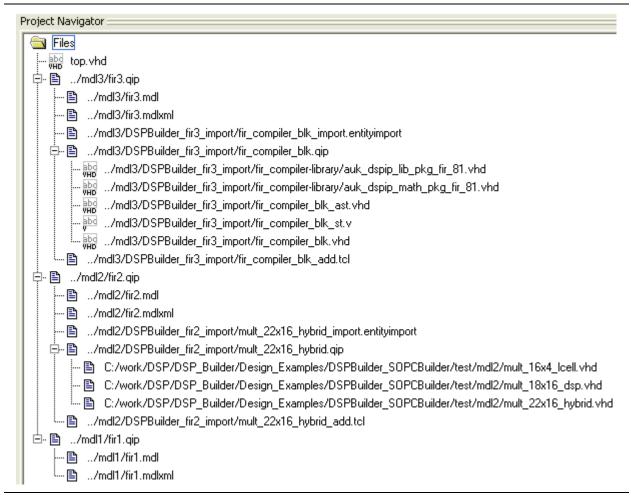

| Integration of Multiple Models in a Top-Level Quartus II Project     |  |

| Design Example                                                       |  |

|                                                                      |  |

### Chapter 13. Troubleshooting

| Troubleshooting Issues                                       | . 10 1 |

|--------------------------------------------------------------|--------|

| Signal Compiler Cannot Checkout a Valid License              | . 13–1 |

| Verifying That Your DSP Builder Licensing Functions Properly | . 13–2 |

| Verifying That the LM_LICENSE_FILE Variable Is Set Correctly |        |

| Verifying the Quartus II Path                                | . 13–3 |

| If You Still Cannot Get a License                            | . 13–4 |

| Loop Detected While Propagating Bit Widths                   | . 13–4 |

| The MegaCore Functions Library Does Not Appear in Simulink   | . 13–4 |

| The Synthesis Flow Does Not Run Properly                     | . 13–5 |

| Check the Software Paths                                     | . 13–5 |

| DSP Development Board Troubleshooting                        | . 13–5 |

| SignalTap II Analysis Appears to Hang                                       |       |

|-----------------------------------------------------------------------------|-------|

| Error if Output Block Connected to an Altera Synthesis Block                | 13–5  |

| Warning if Input/Output Blocks Conflict with clock or aclr Ports            | 13–6  |

| Wiring the Asynchronous Clear Signal                                        |       |

| Error Issues when a Design Includes Pre-v7.1 Blocks                         | 13–6  |

| Creating an Input Terminator for Debugging a Design                         | 13–6  |

| A Specified Path Cannot be Found or a File Name is Too Long                 |       |

| Incorrect Interpretation of Number Format in Output from MegaCore Functions | 13–7  |

| Simulation Mismatch For FIR Compiler MegaCore Function                      | 13–7  |

| Simulation Mismatch After Changing Signals or Parameters                    | 13–7  |

| Unexpected Exception Error when Generating Blocks                           |       |

| VHDL Entity Names Change if a Model is Modified                             | 13–8  |

| Algebraic Loop Causes Simulation to Fail                                    | 13–8  |

| Parameter Entry Problems in the DSP Block Dialog Box                        |       |

| DSP Builder System Not Detected in SOPC Builder                             | 13–9  |

| MATLAB Runs Out of Java Virtual Machine Heap Memory                         | 13–9  |

| ModelSim Fails to Invoke From DSP Builder                                   | 13–10 |

| Unexpected End of File Error When Comparing Simulation Results              | 13–10 |

| Section II. DSP Builder Standard Blockset Libraries                         |       |

| Chapter 14. AltLab Library                                                  |       |

| Chapter 15. Arithmetic Library                                              |       |

**Chapter 16. Complex Type Library**

### Chapter 17. Gate & Control Library

### **Chapter 18. Interfaces Library**

| PFC Data Flow             | . 18–14 |

|---------------------------|---------|

| Packet Format Description | . 18–14 |

| Packet Mapping            | . 18–16 |

| Multi-Packet Mapping      | . 18–17 |

| Error Handling            | . 18–17 |

#### Chapter 19. IO & Bus Library

### Chapter 20. Rate Change Library

### **Chapter 21. Simulation Library**

### Chapter 22. Storage Library

### Chapter 23. State Machine Functions Library

| Design Rule Checks |  | . 23- | -5 |

|--------------------|--|-------|----|

|--------------------|--|-------|----|

### Chapter 24. Boards Library

| Board Configuration |  |

|---------------------|--|

| PLL Output Clocks   |  |

| ADC Control Signals |  |

| Setting Up the Mezzanine Card Test Designs | <br>24-9 |

|--------------------------------------------|----------|

| Setting Up the Mezzanine Card Test Designs | <br>I–19 |

## Chapter 25. MegaCore Functions Library

### **Chapter 26. Design Examples**

### **Additional Information**

| Document Revision History | Info-1 |

|---------------------------|--------|

| How to Contact Altera     | Info-1 |

| Typographic Conventions   | Info-1 |

## 1. About DSP Builder

## **Release Information**

Table 1–1 provides information about this release of DSP Builder.

#### Table 1–1. DSP Builder Release Information

| Item          | Description    |

|---------------|----------------|

| Version       | 11.0           |

| Release Date  | April 2011     |

| Ordering Code | IPT-DSPBUILDER |

## **Device Family Support**

DSP Builder supports the following Altera<sup>®</sup> device families:

- Arria<sup>™</sup> GX

- Arria II GX

- Cyclone<sup>®</sup>

- Cyclone II

- Cyclone III.

- Stratix<sup>®</sup>

- Stratix GX

- Stratix II

- Stratix II GX

- Stratix III

- Stratix IV

## **Memory Options**

A number of the blocks in the Storage library allow you to choose the required memory block type. In general, DSP Builder lists all supported memory block types as options although some may not be available for all device families.

Table 1–2 on page 1–1 shows the device families that support each memory block type.

| Memory Block Type | Device Family                                     |

|-------------------|---------------------------------------------------|

| M144K             | Stratix IV, Stratix III, Arria II GX              |

| M9K               | Stratix IV, Stratix III, Cyclone III, Arria II GX |

| MLAB              | Stratix IV, Stratix III, Arria II GX              |

Table 1–2. Supported Memory Block Types

| Memory Block Type | Device Family                                                                 |

|-------------------|-------------------------------------------------------------------------------|

| M-RAM             | Stratix II GX, Stratix II, Stratix GX, Stratix, Arria GX                      |

| M4K               | Stratix II GX, Stratix II, Stratix GX, Stratix, Arria GX, Cyclone II, Cyclone |

| M512              | Stratix II GX, Stratix II, Stratix GX, Stratix, Arria GX                      |

Table 1–2. Supported Memory Block Types

**For more information about each memory block type, refer to the Quartus II Help.**

## **Features**

DSP Builder standard blockset supports the following features:

- Links The MathWorks MATLAB (Signal Processing ToolBox and Filter Design Toolbox) and Simulink software with the Altera<sup>®</sup> Quartus<sup>®</sup> II software.

- Generates VHDL testbench and controls Quartus II compilation.

- Provides a variety of fixed-point arithmetic and logical operators for use with the Simulink software.

- Enables rapid prototyping using Altera DSP development boards.

- Supports the SignalTap<sup>®</sup> II logic analyzer—an embedded signal analyzer that probes signals from the Altera device on the DSP board and imports the data into the MATLAB workspace to ease visual analysis.

- Allows HDL import of VHDL or Verilog HDL design entities and HDL defined in a Quartus II project file.

- Supports hardware-in-the loop (HIL) to enable FPGA hardware accelerated cosimulation with Simulink.

- Supports Avalon<sup>®</sup> Memory-Mapped (Avalon-MM) interfaces including user configurable blocks, which you can use to build custom logic that works with the Nios<sup>®</sup> II processor and other SOPC Builder designs.

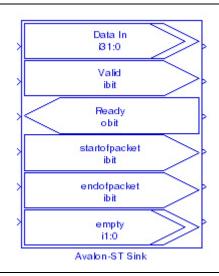

- Supports Avalon Streaming (Avalon-ST) interfaces including an Packet Format Converter block and configurable Avalon-ST sink and Avalon-ST source blocks.

- Allows you to instance Altera DSP MegaCore<sup>®</sup> functions in a DSP Builder design model.

- Supports tabular and graphical state machine editing.

- **For information about new features and errata in this release, refer to the** *DSP Builder Release Notes and Errata.*

## **General Description**

Digital signal processing (DSP) system design in Altera programmable logic devices (PLDs) requires both high-level algorithm and hardware description language (HDL) development tools.

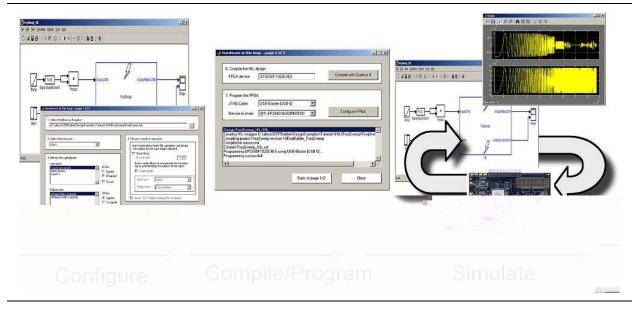

The Altera DSP Builder integrates these tools by combining the algorithm development, simulation, and verification capabilities of The MathWorks MATLAB and Simulink system-level design tools with VHDL and Verilog HDL design flows, including the Altera Quartus II software.

DSP Builder shortens DSP design cycles by helping you create the hardware representation of a DSP design in an algorithm-friendly development environment.

You can combine existing MATLAB functions and Simulink blocks with Altera DSP Builder blocks and Altera intellectual property (IP) MegaCore functions to link system-level design and implementation with DSP algorithm development. In this way, DSP Builder allows system, algorithm, and hardware designers to share a common development platform.

The DSP Builder Signal Compiler block reads Simulink Model Files (.mdl) that contain other DSP Builder blocks and MegaCore functions. Signal Compiler then generates the VHDL files and Tcl scripts for synthesis, hardware implementation, and simulation.

### High-Speed DSP with Programmable Logic

Programmable logic offers compelling performance advantages over dedicated DSP processors. Think of programmable logic as an array of elements, each of which you can configure as a complex processor routine.

You can link these routines together in serial (the same way that a DSP processor executes them), or connect them in parallel. When connected in parallel, they give many times better performance than standard DSP processors by executing hundreds of instructions at the same time.

Algorithms that benefit from this improved performance include forward-error correction (FEC), modulation and demodulation, and encryption.

### Interoperability with the Advanced Blockset

DSP Builder includes an optional advanced blockset.

**For more information about the advanced blockset, refer to** *Volume 3: DSP Builder Advanced Blockset* in the DSP Builder Handbook.

For more information about the differences between the standard and advanced blocksets and about design flows that combine both blocksets, refer to *Volume 1*: Introduction to DSP Builder in the DSP Builder Handbook.

## 2. Getting Started

This chapter describes the design flow and a tutorial.

## **Design Flow**

When using DSP Builder, you start by creating a Simulink design model in the MathWorks software. After you have created your model, you can compile directly in the Quartus II software, output VHDL files for synthesis and Quartus II compilation, or generate files for VHDL simulation.

DSP Builder generates VHDL and does not generate Verilog HDL. However, after you have created a Quartus II project, you can use the quartus\_map command in the Quartus II software to run a simulation netlist flow that generates files for Verilog HDL simulation.

**For information about this flow, refer to the Quartus II help.**

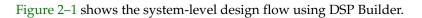

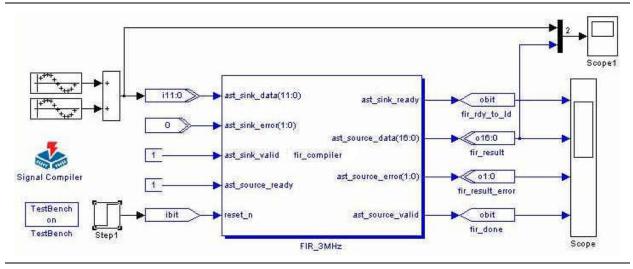

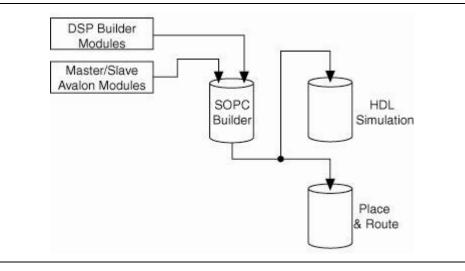

Figure 2–1. System-Level Design Flow

The design flow involves the following steps:

- 1. Use the MathWorks software to create a model with a combination of Simulink and DSP Builder blocks.

- Separate The DSP Builder blocks in your design from the Simulink blocks by Input and Output blocks from the DSP Builder IO and Bus library.

- 2. Include a Clock block from the DSP Builder AltLab library to specify the base clock for your design, which must have a period greater than 1ps but less than 2.1 ms.

- If no base clock exists in your design, DSP Builder creates a default clock with a 20ns real-world period and a Simulink sample time of 1. You can derive additional clocks from the base clock by adding Clock\_Derived blocks.

3. Set a discrete (no continuous states) solver in Simulink. Choose a **Fixed-step** solver type if you are using a single clock domain or a **Variable-step** type if you use multiple clock domains.

To set the solver options, click **Configuration Parameters** on the Simulation menu to open the **Configuration Parameters** dialog box and select the **Solver** page (Figure 2–2).

Figure 2–2. Configuration Parameters for Simulation

| 5elect:                                          | Simulation time                                      |             |                              |   |

|--------------------------------------------------|------------------------------------------------------|-------------|------------------------------|---|

| Solver                                           | Start time: 0.0                                      | Stop time:  | 10.0                         |   |

| Data Import/Export                               |                                                      | Stop and.   | 10.0                         |   |

| Optimization<br>3Diagnostics                     | Solver options                                       |             |                              |   |

| -Sample Time                                     | Type: Fixed-step                                     | Solver: Dis | crete (no continuous states) | ~ |

| Data Validity<br>Type Conversion<br>Connectivity | Fixed-step size (fundamental sample time): auto      |             |                              |   |

| Compatibility                                    | Tasking and sample time options                      |             |                              |   |

| Model Referencing<br>Saving                      | Periodic sample time constraint:                     | Unconstrai  | ned                          | ~ |

| Hardware Implementation<br>Model Referencing     | Tasking mode for periodic sample times:              | SingleTaski | ng                           | ~ |

| Simulation Target                                | Automatically handle rate transition for data        | transfer    |                              |   |

| LCustom Code                                     | Higher priority value indicates higher task priority |             |                              |   |

| £-Real-Time Workshop                             |                                                      |             |                              |   |

|                                                  |                                                      |             |                              |   |

- For detailed information about solver options, refer to the description of the "Solver Pane" in the Simulink Help.

- 4. Simulate your model in Simulink using a Scope block to monitor the results.

- 5. Run Signal Compiler to setup RTL simulation and synthesis.

- 6. Perform RTL simulation. DSP Builder supports an automated flow for the ModelSim software (using the TestBench block). You can also use the generated VHDL for manual simulation in other simulation tools.

- 7. Use the output files generated by the DSP Builder Signal Compiler block to perform RTL synthesis. Alternatively, you can synthesize the VHDL files manually using other synthesis tools.

- 8. Compile your design in the Quartus II software.

- 9. Download to a hardware development board and test.

For an automated design flow, the Signal Compiler block generates VHDL and Tcl scripts for synthesis in the Quartus II software. The Tcl scripts let you perform synthesis and compilation automatically in the MATLAB and Simulink environment. You can synthesize and simulate the output files in other software tools without the Tcl scripts. In addition, the Testbench block generates a testbench and supporting files for VHDL simulation.

- For information about controlling the DSP Builder design flow using Signal Compiler, refer to "Design Flows for Synthesis, Compilation and Simulation" on page 3–19.

- For more information about the blocks in the DSP Builder blockset, refer to the *DSP Builder Standard Blockset Libraries* section in volume 2 of the *DSP Builder Handbook*.

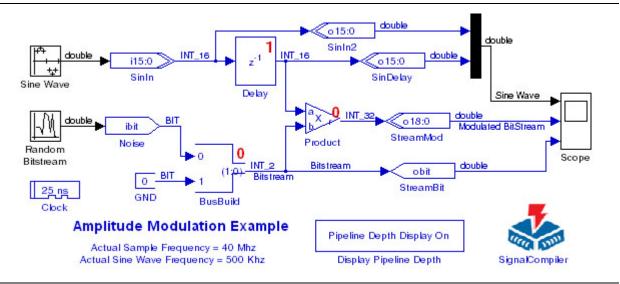

## **Creating the Amplitude Modulation Model**

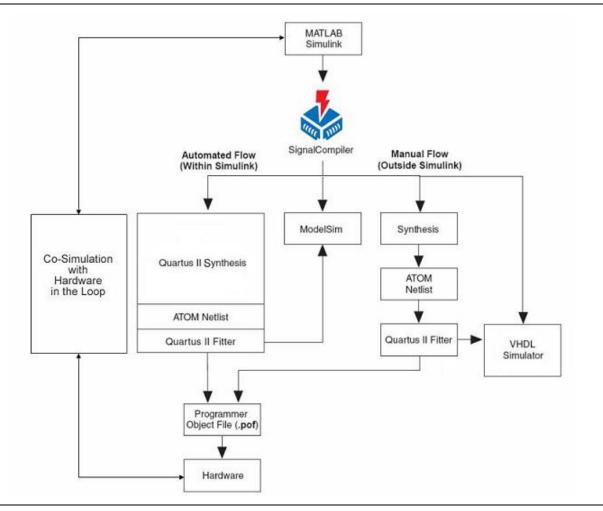

This tutorial uses an amplitude modulation design example, **singen.mdl**, to demonstrate the DSP Builder design flow.

The amplitude modulation design example is a modulator that has a sine wave generator, a quadrature multiplier, and a delay element. Each block in the model is parameterizable. When you double-click a block in the model, a dialog box displays where you can enter the parameters for the block. Click the **Help** button in these dialog boxes to view help for a specific block.

This tutorial assumes the following points:

- You are using a PC running Windows XP.

- You are familiar with the MATLAB, Simulink, Quartus II, and ModelSim<sup>®</sup> software and the software is installed on your PC in the default locations.

- You have basic knowledge of the Simulink software.

- **For information about using the Simulink software**, refer to the Simulink Help.

You can use the **singen.mdl** model file in *<DSP Builder install path>\DesignExamples\Tutorials\GettingStartedSinMdl* or you can create your own amplitude modulation model.

To create the amplitude modulation model, follow these instructions.

### **Create a New Model**

To create a new model, follow these steps:

- 1. Start the MATLAB software.

- 2. On the File menu, point to New, and click Model to create a new model window.

- 3. In the new model window, on the File menu click **Save**.

- Browse to a directory, your working directory, to save the file. This tutorial uses the working directory *<DSP Builder install path>\DesignExamples\Tutorials\GettingStartedSinMdl\my\_SinMdl.*

- 5. Type the file name into the File name box. This tutorial uses the name singen.mdl.

- 6. Click Save.

- 7. Click the MATLAB Start button. Point to Simulink and click Library Browser.

### Add the Sine Wave Block

To add the Sine Wave block, follow these steps:

- 1. In the Simulink Library Browser, click **Simulink** and **Sources** to view the blocks in the Sources library.

- 2. Drag and drop a Sine Wave block into your model.

- 3. Double-click the Sine Wave block in your model to display the **Block Parameters** dialog box (Figure 2–3).

#### Figure 2–3. 500-kHz, 16-Bit Sine Wave Specified in the Sine Wave Dialog Box

| Source Block Parameters: Sine Wave                                                                                      |             | × |

|-------------------------------------------------------------------------------------------------------------------------|-------------|---|

| Sine Wave                                                                                                               |             |   |

| Output a sine wave:                                                                                                     |             |   |

| O(t) = Amp*Sin(Freq*t+Phase) + Bias                                                                                     |             |   |

| Sine type determines the computational technique used. The parameters in the two<br>ypes are related through:           |             |   |

| Samples per period = 2*pi / (Frequency * Sample time)<br>Number of offset samples = Phase * Samples per period / (2*pi) |             |   |

|                                                                                                                         |             |   |

| Parameters                                                                                                              |             |   |

| Sine type: Sample based                                                                                                 | ~           |   |

| Time (t): Use simulation time                                                                                           | ~           |   |

| Amplitude:                                                                                                              |             |   |

| 2^15-1                                                                                                                  |             | 1 |

| Bias:                                                                                                                   |             |   |

| 0                                                                                                                       |             |   |

| Samples per period:                                                                                                     |             |   |

| 80                                                                                                                      |             |   |

| Number of offset samples:                                                                                               |             |   |

| 0                                                                                                                       |             |   |

| Sample time:                                                                                                            |             |   |

| 25e-9                                                                                                                   |             |   |

| Interpret vector parameters as 1-D                                                                                      |             |   |

|                                                                                                                         | Cancel Help | _ |

|                                                                                                                         |             |   |

4. Set the Sine Wave block parameters (Table 2–1).

#### Table 2–1. Parameters for the Sine Wave Block

| Parameter                         | Value           |

|-----------------------------------|-----------------|

| Sine type                         | Sample based    |

| Time                              | simulation time |

| Amplitude                         | 2^15-1          |

| Bias                              | 0               |

| Samples per period                | 80              |

| Number of offset examples         | 0               |

| Sample time                       | 25e-9           |

| Interpret vector parameters a 1-D | On              |

- 5. Click OK.

- For information about how you can calculate the frequency., refer to the equation in "Frequency Design Rules" on page 3–8.

### Add the SinIn Block

To add the SinIn block, follow these steps:

1. In the Simulink Library Browser, expand the **Altera DSP Builder Blockset** folder to display the DSP Builder libraries (Figure 2–4).

Figure 2–4. Altera DSP Builder Folder in the Simulink Library Browser

| File Edit View Help                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                        |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--|

| Enter search term                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | M 🎬                                                                                    |  |

| Libraries                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Library: Altera DSP Builder Blockset/IO & Bus                                          |  |

| Simulink     Altera DSP Builder Advanced Blockset     Altera DSP Builder Blockset     Storage     Video and Image Processing     Storage     Video and Image Processing     Real-Time Workshop     Real-Time Workshop     Real-Time Workshop Embedded Coder     Report Generator     Report Generator     Simulink Control Design     Simulink Control Design     Simulink Verification and Validation     Stateflow     Video and Image Processing Blockset | AltBus                                                                                 |  |

| 🔃 駴 Virtual Reality Toolbox                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                        |  |

| Block Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                        |  |

| Input: Input Port<br>In simulation, this block casts a Simulink signal to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | a DSP Builder internal signal.<br>signed fractional representation. The Simulink value |  |

2. Select the IO & Bus library.

3. Drag and drop the Input block from the Simulink Library Browser into your model. Position the block to the right of the Sine Wave block.

If you are unsure how to position the blocks or draw connection lines, refer to the completed design (Figure 2–7 on page 2–14).

- You can use the Up, Down, Right, and Left arrow keys to adjust the position of a block.

- 4. Click the text under the block icon in your model. Delete the text Input and type the text SinIn to change the name of the block instance.

- 5. Double-click the SinIn block in your model to display the **Block Parameters** dialog box.

- 6. Set the SinIn block parameters (Table 2–2).

#### Table 2–2. Parameters for the SinIn Block

| Parameter           | Value          |

|---------------------|----------------|

| Bus Type            | Signed Integer |

| [number of bits].[] | 16             |

| Specify Clock       | Off            |

- 7. Click OK.

- 8. Draw a connection line from the right side of the Sine Wave block to the left side of the SinIn block by holding down the left mouse button and dragging the cursor between the blocks.

- Alternatively, you can select a block, hold down the Ctrl key and click the destination block to automatically make a connection between the two blocks.

### Add the Delay Block

To add the Delay block, follow these steps:

- 1. Select the **Storage** library from the **Altera DSP Builder Blockset** folder in the Simulink Library Browser.

- 2. Drag and drop the Delay block into your model and position it to the right of the SinIn block.

- 3. Double-click the Delay block in your model to display the **Block Parameters** dialog box (Figure 2–5).

4. Type 1 as the **Number of Pipeline Stages** for the Delay block.

Figure 2–5. Setting the Downsampling Delay

| Delay A                                        | IteraBlockset (mask) (link)                                                                                                                                                                                                                                                                                                                                                                      |

|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Delay                                          |                                                                                                                                                                                                                                                                                                                                                                                                  |

| Implem                                         | ients a parameterized delay.                                                                                                                                                                                                                                                                                                                                                                     |

|                                                | umber of Pipeline Levels' specifies the delay length of the block. The delay<br>e greater than or equal to 1.                                                                                                                                                                                                                                                                                    |

| block i<br>For exa<br>010<br>Use th<br>control | lock Phase Selection' is a binary string which sets the phases in which the<br>s enabled.<br>ample;<br>0 - The delay block is enabled only on the 2nd phase of 4.<br>e 'Optional Ports' tab to select use of the additional clock enable and reset<br>inputs.<br>e 'Initialization' tab to select use of an optional non-zero reset value (use of<br>will increase the hardware resources used). |

|                                                |                                                                                                                                                                                                                                                                                                                                                                                                  |

| Main                                           | Optional Ports Initialization                                                                                                                                                                                                                                                                                                                                                                    |

|                                                |                                                                                                                                                                                                                                                                                                                                                                                                  |

| Number                                         | of Pipeline Stages                                                                                                                                                                                                                                                                                                                                                                               |

| Number                                         |                                                                                                                                                                                                                                                                                                                                                                                                  |

| Main<br>Number<br>1                            |                                                                                                                                                                                                                                                                                                                                                                                                  |

5. Click the **Optional Ports** tab and set the parameters (Table 2–3).

Table 2–3. Parameters for the Delay Block.

| Parameter                  | Value |

|----------------------------|-------|

| Clock Phase Selection      | 01    |

| Use Enable Port            | Off   |

| Use Synchronous Clear port | Off   |

- 6. Click OK.

- 7. Draw a connection line from the right side of the SinIn block to the left side of the Delay block.

### Add the SinDelay and SinIn2 Blocks

To add the SinDelay and SinIn2 blocks, follow these steps:

- 1. Select the **IO & Bus** library from the **Altera DSP Builder Blockset** folder in the Simulink Library Browser.

- 2. Drag and drop two Output blocks into your model, positioning them to the right of the Delay block.

- 3. Click the text under the block symbols in your model. Change the block instance names from Output and Output1 to SinDelay and SinIn2.

- 4. Double-click the SinDelay block in your model to display the **Block Parameters** dialog box.

5. Set the SinDelay block parameters (Table 2–4).

Table 2–4. Parameters for the SinDelay Block

| Parameter           | Value          |

|---------------------|----------------|

| Bus Type            | Signed Integer |

| [number of bits].[] | 16             |

| External Type       | Inferred       |

#### 6. Click OK.

7. Repeat steps 4 to 6 for the SinIn2 block setting the parameters (Table 2–5).

Table 2–5. Parameters for the SinIn2 Block

| Parameter           | Value          |

|---------------------|----------------|

| Bus Type            | Signed Integer |

| [number of bits].[] | 16             |

| External Type       | Inferred       |

8. Draw a connection line from the right side of the Delay block to the left side of the SinDelay block.

### **Add the Mux Block**

To add the Mux block, follow these steps:

- 1. Select the Simulink **Signal Routing** library in the Simulink Library Browser.

- 2. Drag and drop a Mux block into your design, positioning it to the right of the SinDelay block.

- 3. Double-click the Mux block in your model to display the **Block Parameters** dialog box.

- 4. Set the Mux block parameters (Table 2–6).

Table 2–6.

Parameters for the Mux Block

| Parameter        | Value |

|------------------|-------|

| Number of Inputs | 2     |

| Display Options  | bar   |

#### 5. Click OK.

- 6. Draw a connection line from the bottom left of the Mux block to the right side of the SinDelay block.

- 7. Draw a connection line from the top left of the Mux block to the line between the SinIn2 block.

- 8. Draw a connection line from the SinIn2 block to the line between the SinIn and Delay blocks.

### Add the Random Bitstream Block

To add the Random Bitstream block, follow these steps:

- 1. Select the Simulink Sources library in the Simulink Library Browser.

- 2. Drag and drop a Random Number block into your model, positioning it underneath the Sine Wave block.

- 3. Double-click the Random Number block in your model to display the **Block Parameters** dialog box.

- 4. Set the Random Number block parameters (Table 2-7).

#### Table 2–7. Parameters for the Random number Block

| Parameter                          | Value |

|------------------------------------|-------|

| Mean                               | 0     |

| Variance                           | 1     |

| Initial seed                       | 0     |

| Sample time                        | 25e–9 |

| Interpret vector parameters as 1-D | On    |

- 5. Click OK.

- 6. Rename the Random Noise block Random Bitstream.

### **Add the Noise Block**

To add the Noise block, follow these steps:

- 1. Select the **IO & Bus** library from the **Altera DSP Builder Blockset** folder in the Simulink Library Browser.

- 2. Drag and drop an Input block into your model, positioning it to the right of the Random Bitstream block.

- 3. Click the text under the block icon in your model. Rename the block Noise.

- 4. Double-click the Noise block to display the **Block Parameters** dialog box.

- 5. Set the Noise block parameters (Table 2–8).

#### Table 2–8. Parameters for the Noise Block

| Parameter     | Value      |

|---------------|------------|

| Bus Type      | Single Bit |

| Specify Clock | Off        |

- The dialog box options change to display only the relevant options when you select a new bus type.

- 6. Click OK.

- 7. Draw a connection line from the right side of the Random Bitstream block to the left side of the Noise block.

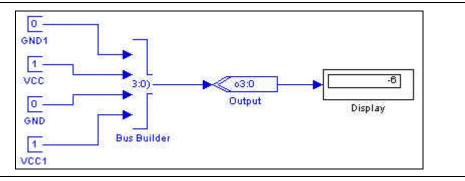

### Add the Bus Builder Block

The Bus Builder block converts a bit to a signed bus. To add the Bus Builder block, follow these steps:

- 1. Select the **IO & Bus** library from the **Altera DSP Builder Blockset** folder in the Simulink Library Browser.

- 2. Drag and drop a Bus Builder block into your model, positioning it to the right of the Noise block.

- 3. Double-click the Bus Builder block in your model to display the **Block Parameters** dialog box.

- 4. Set the Bus Builder block parameters (Table 2–9).

#### Table 2–9. Parameters for the Bus Builder Block

| Parameter           | Value          |

|---------------------|----------------|

| Bus Type            | Signer Integer |

| [number of bits].[] | 2              |

- 5. Click OK.

- 6. Draw a connection line from the right side of the Noise block to the top left side of the Bus Builder block.

### Add the GND Block

To add the GND block, follow these steps:

- 1. Select the **IO & Bus** library from the **Altera DSP Builder Blockset** folder in the Simulink Library Browser.

- 2. Drag and drop a GND block into your model, positioning it underneath the Noise block.

- 3. Draw a connection line from the right side of the GND block to the bottom left side of the Bus Builder block.

### **Add the Product Block**

To add the Product block, follow these steps:

- 1. Select the **Arithmetic** library from the **Altera DSP Builder Blockset** folder in the Simulink Library Browser.

- 2. Drag and drop a Product block into your model, positioning it to the right of the Bus Builder block and slightly above it. Leave enough space so that you can draw a connection line under the Product block.

- 3. Double-click the Product block to display the Block Parameters dialog box.

4. Set the Product block parameters (Table 2–10).

Table 2–10. Parameters for the Product Block

| Parameter                 | Value    |

|---------------------------|----------|

| Bus Type                  | Inferred |

| Number of Pipeline Stages | 0        |

- The bit width parameters are set automatically when you select **Inferred** bus type. The parameters in the **Optional Ports and Settings** tab of this dialog box can be left with their default values.

- 5. Click OK.

- 6. Draw a connection line from the top left of the Product block to the line between the Delay and SinDelay blocks.

### Add the StreamMod and StreamBit Blocks

To add the StreamMod and StreamBit blocks, follow these steps:

- 1. Select the **IO & Bus** library from the **Altera DSP Builder Blockset** folder in the Simulink Library Browser.

- 2. Drag and drop two Output blocks into your model, positioning them to the right of the Product block.

- 3. Click the text under the block symbols in your model. Change the block instance names from Output and Output1 to StreamMod and StreamBit.

- 4. Double-click the StreamMod block to display the **Block Parameters** dialog box.

- 5. Set the StreamMod block parameters (Table 2–11).

#### Table 2–11. Parameters for the StreamMod Block

| Parameter           | Value          |  |

|---------------------|----------------|--|

| Bus Type            | Signed Integer |  |

| [number of bits].[] | 19             |  |

| External Type       | Inferred       |  |

6. Click OK.

7. Double-click the StreamBit block to display the **Block Parameters** dialog box (Figure 2–6).

#### Figure 2–6. Set a Single-Bit Output Bus

| Ошрис Акегаріос                         | ckset (mask) (link)                                                                                                                                                          |

|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Output Port                             |                                                                                                                                                                              |

| Choose from sign<br>the type to be info | block casts a DSP Builder internal signal to a Simulink signal,<br>and integer, unsigned integer, signed fractional representation or allo<br>erred from the previous block. |

| Parameters                              | g hardware, this block generates an output port.                                                                                                                             |

| Bus Type Single                         | Bit                                                                                                                                                                          |

| [Number Of Bits].                       | .[]                                                                                                                                                                          |

| 19                                      |                                                                                                                                                                              |

|                                         | [5]                                                                                                                                                                          |

| [].[Number Of Bit                       |                                                                                                                                                                              |

| [].[Number Of Bit                       |                                                                                                                                                                              |

|                                         | iferred                                                                                                                                                                      |

8. Set the StreamBit block parameters (Table 2–12).

Table 2–12. Parameters for the StreamBit Block

| Parameter     | Value      |

|---------------|------------|

| Bus Type      | Single Bit |

| External Type | Inferred   |

9. Draw connection lines from the right side of the Product block to the left side of the StreamMod block, and from the right side of the Bus Builder block to the left side of the StreamBit block.

### Add the Scope Block

To add the Scope block, follow these steps:

- 1. Select the Simulink Sinks library in the Simulink Library Browser.

- 2. Drag and drop a Scope block into your model and position it to the right of the StreamMod block.

- 3. Double-click the Scope block and click the **Parameters** icon to display the **'Scope' parameters** dialog box.

- 4. Set the Scope parameters (Table 2–13).

#### Table 2–13. Parameters for the Scope Block

| Parameter      | Value |

|----------------|-------|

| Number of axes | 3     |

| Time range     | auto  |

| Parameter   | Value            |  |

|-------------|------------------|--|

| Tick labels | bottom axis only |  |

| Sampling    | Decimation 1     |  |

#### Table 2–13. Parameters for the Scope Block

- 5. Click OK.

- 6. Close the Scope.

- 7. Make connections to connect the complete your design as follows:

- a. From the right side of the Mux block to the top left side of the Scope block.

- b. From the right side of the StreamMod block to the middle left side of the Scope block.

- c. From the right side of the StreamBit block to the bottom left of the Scope block.

- d. From the bottom left of the Product block to the line between the Bus Builder block and the StreamBit block.

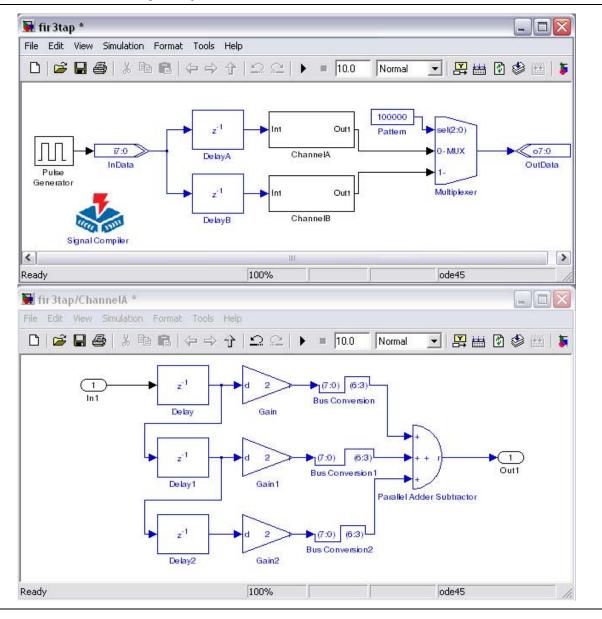

Figure 2–7 shows the required connections.

### **Add a Clock Block**

To add a Clock block, follow these steps:

- 1. Select the **AltLab** library from the **Altera DSP Builder Blockset** folder in the Simulink Library Browser.

- 2. Drag and drop a Clock block into your model.

- 3. Double-click on the Clock block to display the **Block Parameters** dialog box.

- 4. Set the Clock parameters (Table 2–14).

#### Table 2–14. Parameters for the Clock Block

| Parameter               | Value |

|-------------------------|-------|

| Real-World Clock Period | 20    |

| Period Unit:            | ns    |

| Parameter            | Value      |

|----------------------|------------|

| Simulink Sample Time | 2.5e-008   |

| Reset Name           | aclr       |

| Reset Type           | Active Low |

| Export As Output Pin | Off        |

Table 2–14. Parameters for the Clock Block

- A clock block is required to set a Simulink sample time that matches the sample time specified on the Sine Wave and Random Bitstream blocks. If no base clock exists in your design, a default clock with a 20ns real-world period and a Simulink sample time of 1 is automatically created.

- 5. Save your model.

## Simulating the Model in Simulink

To simulate your model in the Simulink software, follow these steps:

- 1. Click **Configuration Parameters** on the Simulation menu to display the **Configuration Parameters** dialog box and select the **Solver** page (Figure 2–8 on page 2–16).

- 2. Set the parameters (Table 2–15).

#### Table 2–15. Configuration Parameters for the singen Model

| Parameter  | Value                           |

|------------|---------------------------------|

| Start time | 0.0                             |

| Stop time  | 4e-6                            |

| Туре       | Fixed-step                      |

| Solver     | discrete (no continuous states) |

• For detailed information about solver options, refer to the description of the Solver Pane in the Simulink Help.

#### Figure 2–8. Configuration Parameters

| Select:                                      | Simulation time                                 |               |         |                                 |       |

|----------------------------------------------|-------------------------------------------------|---------------|---------|---------------------------------|-------|

| Solver<br>Data Import/Export                 | Start time: 0.0                                 |               | Stop ti | me: 4e-6                        |       |

| - Optimization                               | Solver options                                  |               |         |                                 |       |

| Sample Time<br>Data Validity                 | Type: Fixed-step                                | ~             | Solver: | Discrete (no continuous states) | ~     |

|                                              | Fixed-step size (fundamental sample time): auto |               |         |                                 |       |

| Compatibility<br>Model Referencing           | Tasking and sample time options                 |               |         |                                 |       |

| - Saving                                     | Periodic sample time constraint:                |               | Uncon:  | strained                        | ~     |

| Hardware Implementation<br>Model Referencing | Tasking mode for periodic sample times:         |               | SingleT | asking                          | ~     |

| Simulation Target                            | Automatically handle rate transition for (      | lata transfer |         |                                 |       |

| └──Custom Code<br>±-Real-Time Workshop       | Higher priority value indicates higher tas      | < priority    |         |                                 |       |

|                                              |                                                 |               |         |                                 |       |

| 0                                            |                                                 | Ē             | ОК      | Cancel Help                     | Apply |

- 3. Click OK.

- 4. Start simulation by clicking **Start** on the Simulation menu.

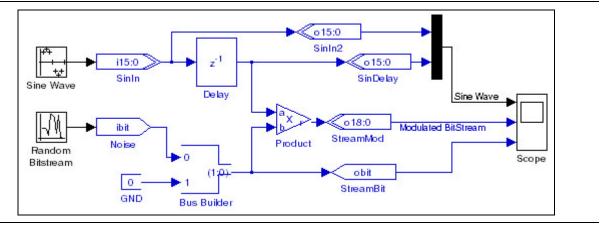

- 5. Double-click the Scope block to view the simulation results.

6. Click the **Autoscale** icon (binoculars) to auto-scale the waveforms.

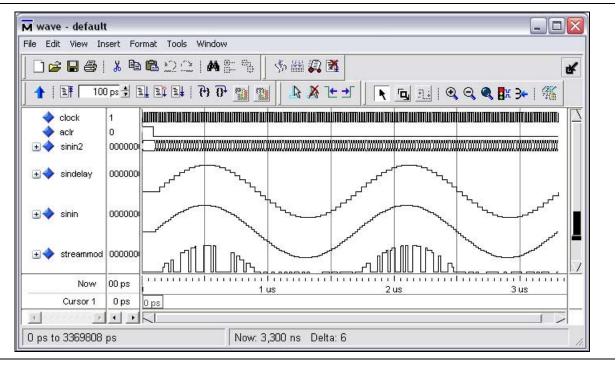

Figure 2–9 shows the scaled waveforms.

#### Figure 2–9. Scope Simulation Results

## **Compiling the Design**

To create and compile a Quartus II project for your DSP Builder design, and to program your design onto an Altera FPGA, add a Signal Compiler block by following these steps:

- 1. Select the **AltLab** library from the **Altera DSP Builder Blockset** folder in the Simulink Library Browser.

- 2. Drag and drop a Signal Compiler block into your model.

- 3. Double-click the Signal Compiler block in your model to display the **Signal Compiler** dialog box (Figure 2–10).

The dialog box allows you to set the target device family. For this tutorial, you can use the default **Stratix** device family.

#### 4. Click Compile.

#### Figure 2–10. Signal Compiler Block Dialog Box

| Description                                                                                                                                                                                                                                                                                                                                                                                                                         | ompiler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      | - 0 2  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |        |

| his block controls the com                                                                                                                                                                                                                                                                                                                                                                                                          | pilation of the design.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |        |

| Parameters                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |        |

| uartus II Project: singen_                                                                                                                                                                                                                                                                                                                                                                                                          | dspbuilder\singen.qpf                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |        |

| Family: Stratix                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |        |

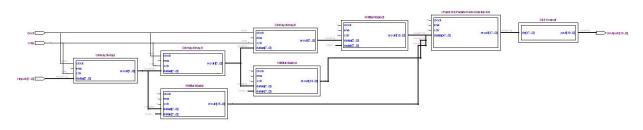

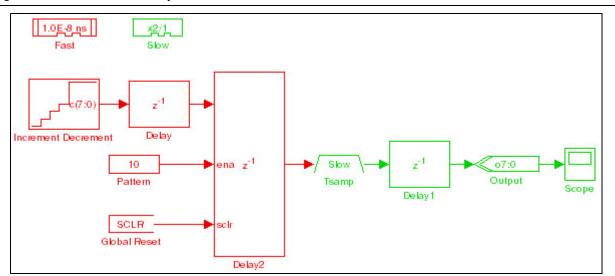

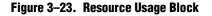

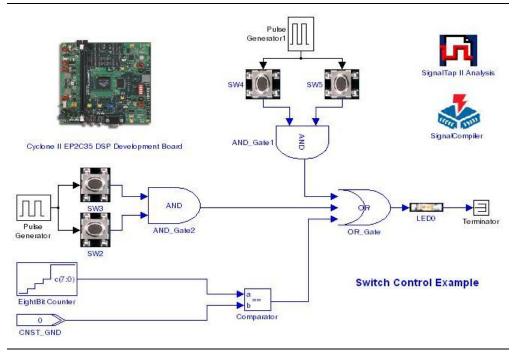

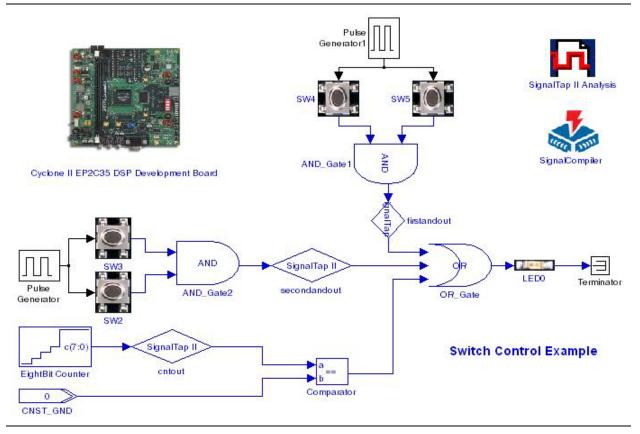

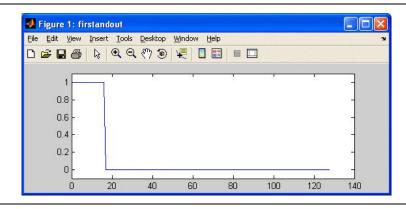

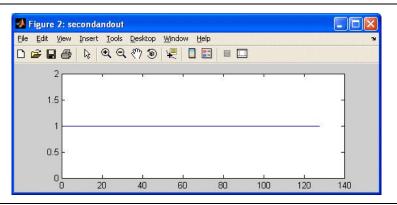

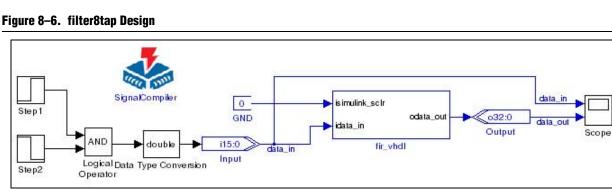

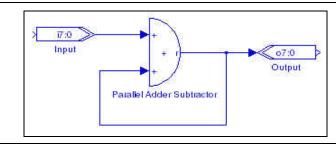

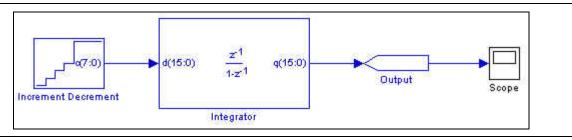

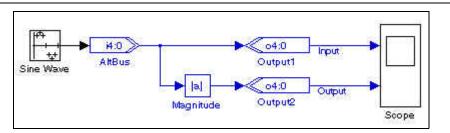

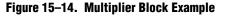

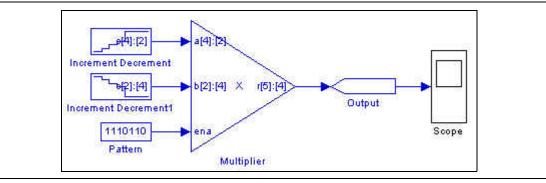

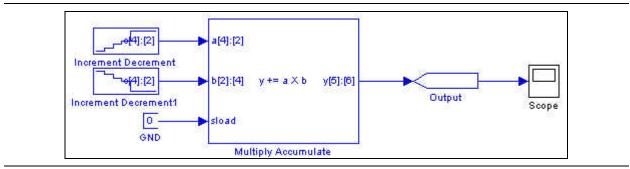

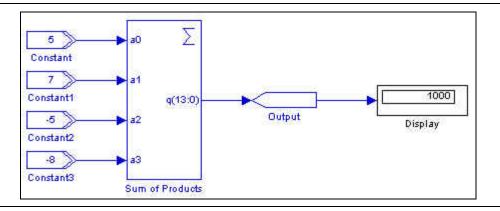

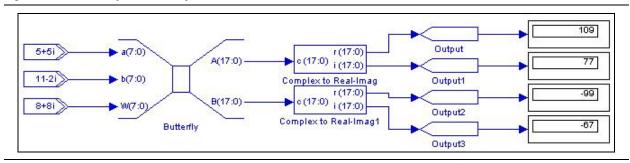

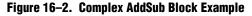

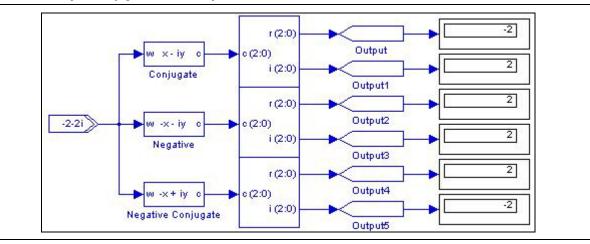

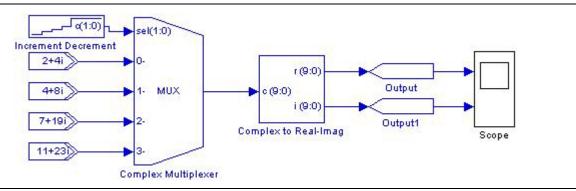

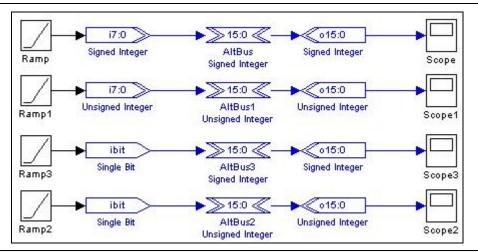

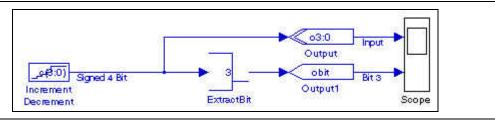

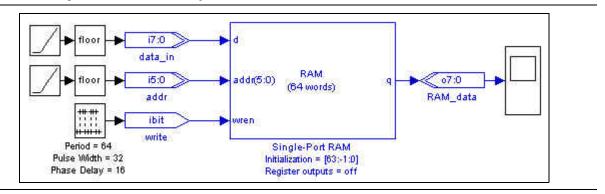

| ranny, j                                                                                                                                                                                                                                                                                                                                                                                                                            | 📕 🔲 Use Board Block to Specify Device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |        |