# YM12864T-2

# 图形点阵式液晶显示模块 使用说明

# 大连佳显电子有限公司

- 地址: 大连市沙河口区工华街17号轩煌大厦六楼

- 邮编: 116021

- 电话: (0411)84619565

- 传真: (0411)84619585

- E-mail: market@good-lcd.com

- 网址: <u>http://www.good-lcd.com</u>

# YM12864T-2

# **RECORDS OF REVISION**

| DATE       | REVISED<br>NO. | REVISED DESCRIPTIONS | PREPARED | CHECKED | APPROVED |

|------------|----------------|----------------------|----------|---------|----------|

| Apr-1-2006 | 1.00           | FIRST ISSUE          | tfb      |         |          |

|            |                |                      |          |         |          |

|            |                |                      |          |         |          |

|            |                |                      |          |         |          |

|            |                |                      |          |         |          |

|            |                |                      |          |         |          |

|            |                |                      |          |         |          |

|            |                |                      |          |         |          |

|            |                |                      |          |         |          |

|            |                |                      |          |         |          |

|            |                |                      |          |         |          |

|            |                |                      |          |         |          |

# <u>CONTENTS</u>

| 1.  | FEATURES                            | 1  |

|-----|-------------------------------------|----|

| 2.  | BLOCK DIAGRAM & APPLICATION CIRCUIT | 1  |

| 3.  | OUTLINE DIMENSIONS                  | 3  |

| 4.  | ABSOLUTE MAXIMUM RATING             | 4  |

| 5.  | ELECTRICAL CHARACTERISTICS          | 4  |

| 6.  | OPTICAL CHARACTERISTICS             | 5  |

| 7.  | TIMING CHARACTERISTICS              | 6  |

| 8.  | DISPLAY CONTROL INSTRUCTION         | 9  |

| 9.  | DISPLAY CONTROL FUNCTIONS           | 14 |

| 10. | INTERFACE PIN CONNECTIONS           | 21 |

| 11. | RELIABILITY                         | 22 |

| 12. | QUALITY GUARANTEE                   | 23 |

| 13. | INSPECTION CRITERIA                 | 24 |

| 14. | PRECAUTIONS FOR USING LCD MODULES   | 27 |

| 15. | USING LCD MODULES                   | 28 |

# 1. FEATURES :

| ITEM                   | STANDARD VALUE                                | UNIT |

|------------------------|-----------------------------------------------|------|

| Display Type           | 128 x 64 dots                                 | -    |

| LCD Type               | STN (Blue-white mode), Transmissive, Negative | -    |

| LCD Duty               | 1/65                                          | -    |

| LCD Bias               | 1/9                                           | -    |

| Viewing Direction      | 6:00                                          | -    |

| Backlight Type         | BLUE(LED)                                     | -    |

|                        | YELLOW-GREEN(LED)                             |      |

|                        | WHITE (LED)                                   |      |

| Interface              | 8080 Series / 6800 Series / Serial Interface  | -    |

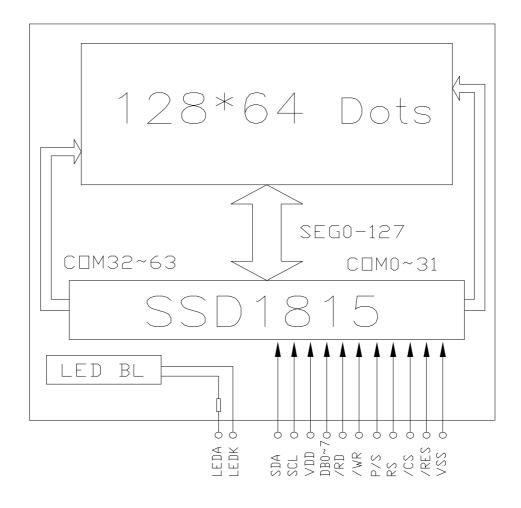

| Driver IC              | SSD1815                                       | -    |

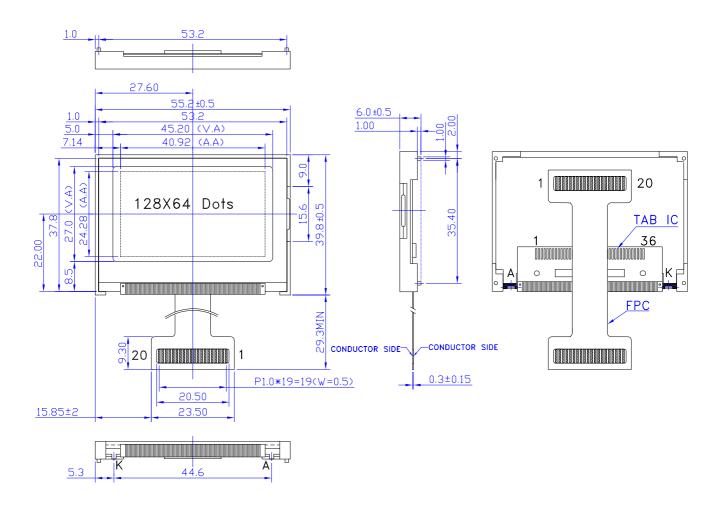

| Module Dimension       | 55.2(W) X39.8 (H) X6.0 (MAX)(T)               | mm   |

| Effective Display Area | 40.92(W) X24.28 (H)                           | mm   |

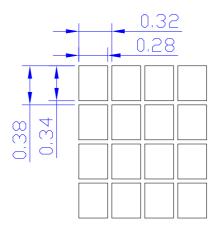

| Dot Size               | 0.28 (W) X 0.34 (H)                           |      |

| Dot Pitch              | 0.32 W) X 0.38 (H)                            | mm   |

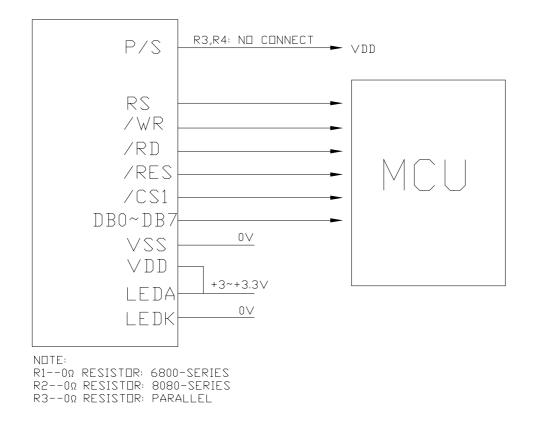

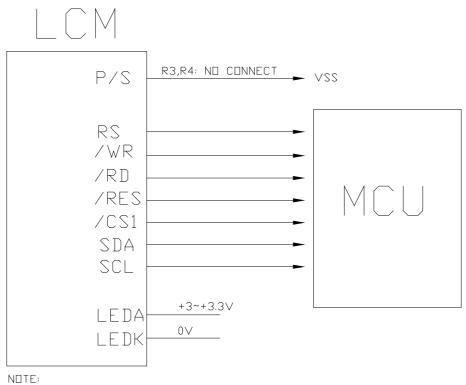

# 2. BLOCK DIAGRAM & APPLICATION CIRCUIT :

# **Parallel Application**

# **Serial Interface Application**

$R4--0\Omega$  RESISTOR: SERIAL INTERFACE

# 3. OUTLINE DIMENSIONS

# 4. ABSOLUTE MAXIMUM RATING

| ITEM                         | SYMBOL         | CONDITION  | STA     | STANDARD VALUE |         |      |

|------------------------------|----------------|------------|---------|----------------|---------|------|

| I I EIVI                     | STIVIDOL       | CONDITION  | MIN     | ΤΥΡ            | MAX     | UNIT |

| POWER SUPPLY FOR LOGIC       | VDD            | Ta=25      | -0.3    | -              | +4      | V    |

| INPUT VOLTAGE                | VIN            | Ta=25      | VSS-0.3 | -              | VDD+0.3 | V    |

| Module OPERATION TEMPERATURE | TOPR           |            | -20     | -              | +70     |      |

| Module STORAGE TEMPERATURE   | TSTG           |            | - 30    | -              | +80     |      |

| Storage Humidity             | H <sub>D</sub> | Ta < 40 °C | _       |                | 90      | %RH  |

# 5. ELECTRICAL CHARACTERISTICS

| ITEM                   | SYMBOL  | CONDITION   | MIN    | ТҮР  | MAX    | UNIT |

|------------------------|---------|-------------|--------|------|--------|------|

| Supply Voltage (logic) | VDD-VSS | -           | 2.4    | 3.3  | 3.5    | V    |

| Supply Voltage (LCD)   | VDD-V0  | Ta=+25      | -      | 9.6  | -      | V    |

| Input signal valtage   | V-IH    | "H" level   | 0.8VDD | -    | VDD    | V    |

| Input signal voltage   | V-IL    | "L" level   | VSS    | -    | 0.2VDD | V    |

| Output signal valtage  | V-OH    | "H" level   | 0.8VDD | -    | VDD    | V    |

| Output signal voltage  | VOL     | "H" level   | VSS    | -    | 0.2VDD | V    |

| Supply Current (logic) | IDD     | VDD=3.0V    | -      | 150  | 200    | μΑ   |

|                        |         | BLUE(LED)   |        | 2.9  |        |      |

| Backlight Voltage      | V-BL    | Y-G(LED)    | -      | 2.0  | -      | V    |

|                        |         | WHITE (LED) |        | 2.8  |        |      |

|                        |         | BLUE(LED)   |        | 20mA |        |      |

| Backlight Current      | I-BL    | Y-G(LED)    | -      | 60mA | -      | mA   |

|                        |         | WHITE (LED) |        | 40mA |        |      |

| Backlight Driver Wave  |         |             |        |      |        | kHz  |

| Backlight Brightness   |         |             |        |      |        |      |

| Backlight Life Time    |         |             |        |      |        |      |

# 6. OPTICAL CHARACTERISTICS

| Item           | Symbol | Condition  | Min | Тур | Max | Unit | Remarks | Note |

|----------------|--------|------------|-----|-----|-----|------|---------|------|

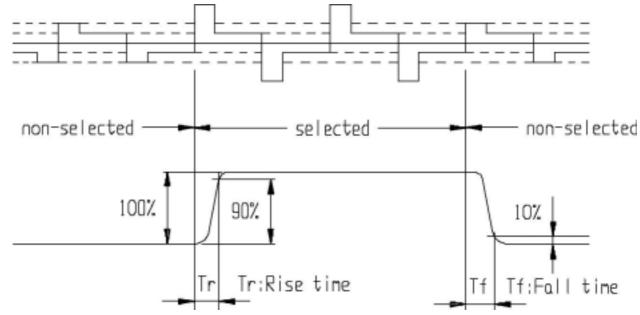

| Response       | Tr     | -          | -   | 239 | -   | ms   | -       | 1    |

| Time           | Tf     | -          | -   | 83  | -   | ms   | -       | 1    |

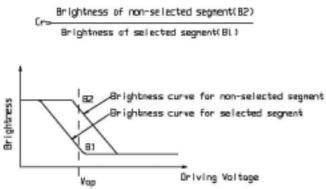

| Contrast Ratio | Cr     | -          | -   | 8.5 | -   | -    | -       | 2    |

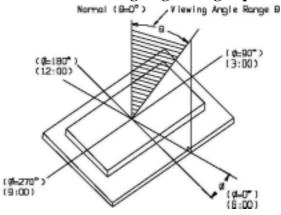

| V              |        |            | 33  | -   | -   | deg  | Ø= 90   | 3    |

| Viewing        | θ      | $Cr \ge 2$ | 32  | -   | -   | deg  | Ø = 270 | 3    |

| Angle<br>Range |        |            | 54  | -   | -   | deg  | Ø = 0   | 3    |

| Kange          |        |            | 34  | -   | -   | deg  | Ø = 180 | 3    |

### Note 1. Definition of response time

# Note 2. Definition of Contrast Ratio 'Cr'

### Note 3. Definition of Viewing Angle Range 'q'

# 7. TIMING CHARACTERISTICS

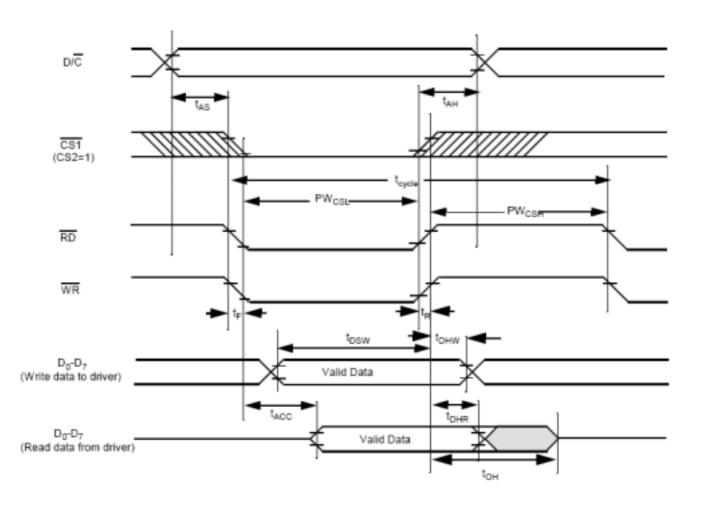

### 7.1 8080-Series MPU Parallel Interface Timing Characteristics

| Symbol             | Parameter                                                                   | Min       | Тур | Max | Unit     |

|--------------------|-----------------------------------------------------------------------------|-----------|-----|-----|----------|

| t <sub>cycle</sub> | Clock Cycle Time                                                            | 300       | -   | -   | ns       |

| tas                | Address Setup Time                                                          | 0         | -   | -   | ns       |

| t <sub>AH</sub>    | Address Hold Time                                                           | 0         | -   | -   | ns       |

| tosw               | Write Data Setup Time                                                       | 40        |     | -   | ns       |

| t <sub>DHW</sub>   | Write Data Hold Time                                                        | 15        | -   | -   | ns       |

| t <sub>DHR</sub>   | Read Data Hold Time                                                         | 20        |     | -   | ns       |

| t <sub>OH</sub>    | Output Disable Time                                                         | -         |     | 70  | ns       |

| t <sub>ACC</sub>   | Access Time                                                                 | -         | -   | 140 | ns       |

| PW <sub>CSL</sub>  | Chip Select Low Pulse Width (read)<br>Chip Select Low Pulse Width (write)   | 120<br>60 |     |     | ns<br>ns |

| PWCSH              | Chip Select High Pulse Width (read)<br>Chip Select High Pulse Width (write) | 60<br>60  | :   | -   | ns<br>ns |

| t <sub>R</sub>     | Rise Time                                                                   |           |     | 15  | ns       |

| t <sub>F</sub>     | Fall Time                                                                   | -         | -   | 15  | ns       |

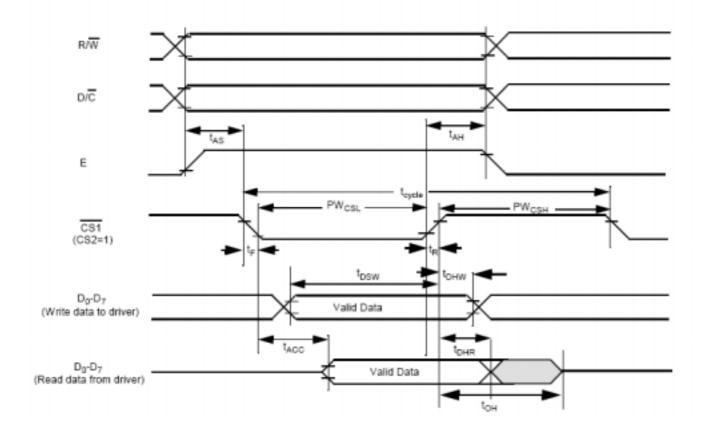

## 7.2 6800-Series MPU Parallel Interface Timing Characteristics

| Symbol             | Parameter                                                                   | Min       | Тур | Max | Unit     |

|--------------------|-----------------------------------------------------------------------------|-----------|-----|-----|----------|

| t <sub>cycle</sub> | Clock Cycle Time                                                            | 300       | -   | -   | ns       |

| t <sub>AS</sub>    | Address Setup Time                                                          | 0         | -   | -   | ns       |

| t <sub>AH</sub>    | Address Hold Time                                                           | 0         | -   | -   | ns       |

| tosw               | Write Data Setup Time                                                       | 40        | -   | -   | ns       |

| tонw               | Write Data Hold Time                                                        | 15        | -   | -   | ns       |

| t <sub>ohr</sub>   | Read Data Hold Time                                                         | 20        | -   | -   | ns       |

| t <sub>OH</sub>    | Output Disable Time                                                         | -         | -   | 70  | ns       |

| tacc               | Access Time                                                                 | -         | -   | 140 | ns       |

| PW <sub>CSL</sub>  | Chip Select Low Pulse Width (read)<br>Chip Select Low Pulse Width (write)   | 120<br>60 | -   | -   | ns<br>ns |

| PWCSH              | Chip Select High Pulse Width (read)<br>Chip Select High Pulse Width (write) | 60<br>60  | -   |     | ns<br>ns |

| t <sub>R</sub>     | Rise Time                                                                   | -         | -   | 15  | ns       |

| te                 | Fall Time                                                                   | -         | -   | 15  | ns       |

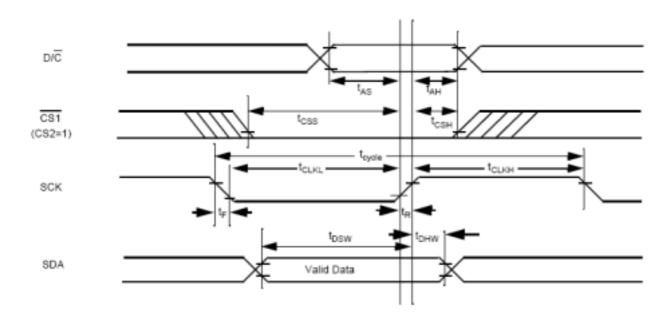

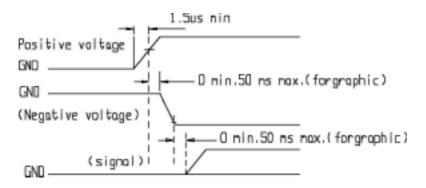

## 7.3 Serial Interface Timing Characteristics

# YM12864T-2

| Symbol             | Parameter                                         | Min | Тур | Max | Unit |

|--------------------|---------------------------------------------------|-----|-----|-----|------|

| t <sub>cycle</sub> | Clock Cycle Time                                  | 250 | -   | -   | ns   |

| t <sub>AS</sub>    | Address Setup Time                                | 150 | -   | -   | ns   |

| t <sub>an</sub>    | Address Hold Time                                 | 150 | -   | -   | ns   |

| t <sub>css</sub>   | Chip Select Setup Time (for D <sub>7</sub> input) | 120 | -   | -   | ns   |

| t <sub>CSH</sub>   | Chip Select Hold Time (for D <sub>D</sub> input)  | 60  | -   |     | ns   |

| tosw               | Write Data Setup Time                             | 100 | -   | -   | ns   |

| t <sub>DHW</sub>   | Write Data Hold Time                              | 100 |     |     | ns   |

| t <sub>CLKL</sub>  | Clock Low Time                                    | 100 |     |     | ns   |

| t <sub>CLKH</sub>  | Clock High Time                                   | 100 |     |     | ns   |

| t <sub>R</sub>     | Rise Time                                         |     |     | 15  | ns   |

| t <sub>F</sub>     | Fall Time                                         |     |     | 15  | ns   |

# 8. DISPLAY CONTROL INSTRUCTION

### COMMAND TABLE

| Bit Pattern                                                                                             | Write Command<br>(D/C=0, R/W(WR)=0, E(RD)=1)                                                                          | Comment                                                                                                                                                                                                                                                                                                         |

|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0000X <sub>3</sub> X <sub>2</sub> X <sub>1</sub> X <sub>0</sub>                                         | Set Lower Column Address                                                                                              | Set the lower nibble of the colume address register using $X_3 X_2 X_1 X_0$ as data bits. The initial display line register is reset to 0000b during POR.                                                                                                                                                       |

| 0001X <sub>3</sub> X <sub>2</sub> X <sub>1</sub> X <sub>0</sub>                                         | Set Higher Column Address                                                                                             | Set the higher nibble of the colume address register using $X_3 X_2 X_1 X_0$ as data bits. The initial display line register is reset to 00000b during POR.                                                                                                                                                     |

| 00100X <sub>2</sub> X <sub>1</sub> X <sub>0</sub>                                                       | Set Internal Regulator Resistor Ratio                                                                                 | Internal regulator gain increases as $X_2X_1X_0$ increased from 000b to 111b. At POR, $X_2X_1X_0 = 100b$ .                                                                                                                                                                                                      |

| 00101X <sub>2</sub> X <sub>1</sub> X <sub>0</sub>                                                       | Set Power Control Register                                                                                            | $X_0=0$ : turns off the output op-amp buffer (POR)<br>$X_0=1$ : turns on the output op-amp buffer<br>$X_1=0$ : turns off the internal regulator (POR)<br>$X_1=1$ : turns on the internal regulator<br>$X_2=0$ : turns off the internal voltage booster (POR)<br>$X_2=1$ : turns on the internal voltage booster |

| 01X <sub>0</sub> X <sub>4</sub> X <sub>3</sub> X <sub>2</sub> X <sub>1</sub> X <sub>0</sub>             | Set Display Start Line                                                                                                | Set display RAM display start line register from 0-63 using $X_6 X_4 X_3 X_2 X_1 X_0$ .<br>Display start line register is reset to 000000 during POR.                                                                                                                                                           |

| 10000001<br>**X <sub>8</sub> X <sub>4</sub> X <sub>3</sub> X <sub>2</sub> X <sub>1</sub> X <sub>0</sub> | Set Contrast Control Register                                                                                         | Set Contrast level from 64 contrast steps. Contrast increases (V <sub>L0</sub> decreases) as $X_8X_4X_3X_2X_1X_0$ is increased. $X_8X_4X_3X_2X_1X_0 = 100000b$ (POR)                                                                                                                                            |

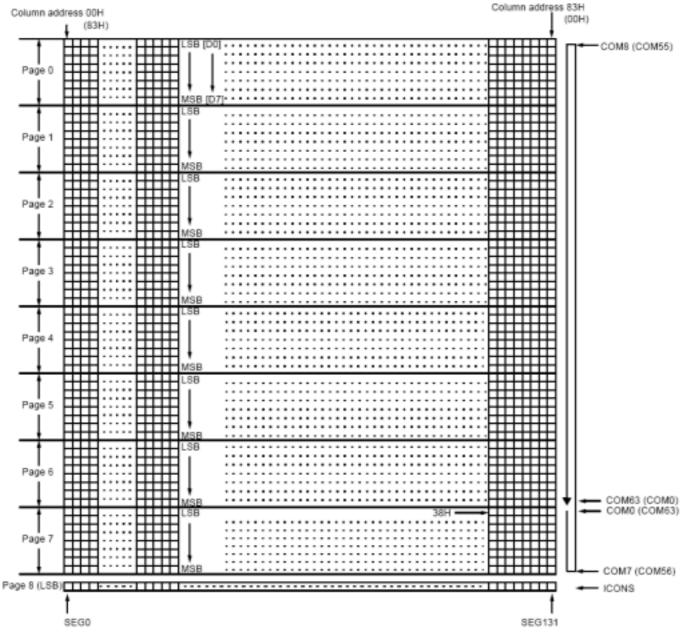

| 1010000X <sub>0</sub>                                                                                   | Set Segment Re-map                                                                                                    | X <sub>0</sub> =0: column address 00h is mapped to SEG0 (POR)<br>X <sub>0</sub> =1: column address 83h is mapped to SEG0<br>Refer to Figure 5 for example.                                                                                                                                                      |

| 1010001X <sub>0</sub>                                                                                   | Set LCD Blas                                                                                                          | $X_0{=}0{:}$ 1/9 bias (POR) $X_0{=}1{:}$ 1/7 bias For setting bias ratio to 1/4, 1/5, 1/6 or 1/8, see Extended Command Table.                                                                                                                                                                                   |

| 1010010X <sub>0</sub>                                                                                   | Set Entire Display On/Off                                                                                             | X <sub>0</sub> =0: normal display (POR)<br>X <sub>0</sub> =1: entire display on                                                                                                                                                                                                                                 |

| 1010011X <sub>0</sub>                                                                                   | Set Normal/Reverse Display                                                                                            | X <sub>0</sub> =0: normal display (POR)<br>X <sub>0</sub> =1: reverse display                                                                                                                                                                                                                                   |

| 1010111X <sub>0</sub>                                                                                   | Set Display On/Off                                                                                                    | X <sub>0</sub> =0: turns off LCD panel (POR)<br>X <sub>0</sub> =1: turns on LCD panel                                                                                                                                                                                                                           |

| 1011X <sub>3</sub> X <sub>2</sub> X <sub>1</sub> X <sub>0</sub>                                         | Set Page Address                                                                                                      | Set GDDRAM Page Address (0-8) using X <sub>3</sub> X <sub>2</sub> X <sub>1</sub> X <sub>0</sub>                                                                                                                                                                                                                 |

| 1100X <sub>3</sub> ***                                                                                  | Set COM Output Scan Direction                                                                                         | X <sub>3</sub> =0: normal mode (POR)<br>X <sub>3</sub> =1: remapped mode, COM0 to COM[N-1] becomes COM[N-1]<br>to COM0 when Multiplex ratio is equal to N. See Figure 5<br>as an example for N equal to 64.                                                                                                     |

| 11100000                                                                                                | Set Read-Modify-Write Mode                                                                                            | Read-modify-write mode will be entered in which the column<br>address will not be incremented during display data read. At POR,<br>Read-modify-write mode is turned OFF.                                                                                                                                        |

| 11100010                                                                                                | Software Reset                                                                                                        | Initialize the internal status register.                                                                                                                                                                                                                                                                        |

| 11101110                                                                                                | Set End of Read-Modify-Write Mode                                                                                     | Exit Read-modify-write mode. Column address before entering the<br>mode will be restored. At POR, Read-modify-write mode is OFF.                                                                                                                                                                                |

| 1010110X <sub>0</sub>                                                                                   | Set Indicator On/Off                                                                                                  | $X_0 = 0$ : indicator off (POR, no need of second command byte)<br>$X_0 = 1$ : indicator on (second command byte required)                                                                                                                                                                                      |

| ••••••x <sub>1</sub> x <sub>0</sub>                                                                     | Indicator Display Mode,<br>This second byte command is required<br>ONLY when "Set Indicator On" com-<br>mand is sent. | $ \begin{array}{l} X_{1}X_{0}=00; \mbox{ indicator off} \\ X_{1}X_{0}=01; \mbox{ indicator on and blinking at } \sim 1 \mbox{ second interval} \\ X_{1}X_{0}=10; \mbox{ indicator on and blinking at } \sim 1/2 \mbox{ second interval} \\ X_{1}X_{0}=11; \mbox{ indicator on constantly} \end{array} $         |

| 11100011                                                                                                | NOP                                                                                                                   | Command for No Operation                                                                                                                                                                                                                                                                                        |

| 11110000                                                                                                | Test Mode Reset                                                                                                       | Reserved for IC testing. Do NOT use.                                                                                                                                                                                                                                                                            |

| 1111 * * * *                                                                                            | Set Test Mode                                                                                                         | Reserved for IC testing. Do NOT use.                                                                                                                                                                                                                                                                            |

|                                                                                                         | Set Power Save Mode                                                                                                   | Standby or sleep mode will be entered with compound commands                                                                                                                                                                                                                                                    |

# YM12864T-2

| Bit Pattern                                                                                                                                                    | Read Command<br>(D/C=0, R/W(WR)=1, E(RD)=0) | Comment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D <sub>7</sub> D <sub>6</sub> D <sub>5</sub> D <sub>4</sub> D <sub>3</sub> D <sub>2</sub> D <sub>1</sub> D <sub>0</sub><br>(Data Read Back from the<br>driver) | Status Register Read                        | $\begin{array}{l} D_7{=}0; \mbox{ indicates an internal operation is completed.} \\ D_7{=}1; \mbox{ indicates an internal operation is in progress.} \\ D_8{=}0; \mbox{ indicates reverse segment mapping with column address} \\ D_8{=}0; \mbox{ indicates normal segment mapping with column address} \\ D_8{=}0; \mbox{ indicates the display is ON} \\ D_8{=}1; \mbox{ indicates the display is OFF} \\ D_4{=}0; \mbox{ initialization is not in progress} \\ D_8{=}1; \mbox{ initialization is in progress after $RES$ or software reset} \\ D_3{D}_2{D}_1{D}_0 = 1010, \mbox{ these 4-bit is fixed to 1010 which could be used} \\ \mbox{ to identify as Solomon Systech Device.} \\ \end{array}$ |

### EXTENDED COMMAND TABLE

| Bit Pattern                                                                                                                         | Command                                                                                                                                                             | Comment                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10101000<br>00X <sub>5</sub> X <sub>4</sub> X <sub>3</sub> X <sub>2</sub> X <sub>1</sub> X <sub>0</sub>                             | X <sub>5</sub> X <sub>4</sub> X <sub>3</sub> X <sub>2</sub> X <sub>1</sub> X <sub>0</sub> : Set Multiplex Ratio                                                     | To select multiplex ratio N from 2 to 65 [Included Icon Line].<br>N = $X_5X_4X_3X_2X_1X_0 + 2$ , eg. N = 111111b + 2 = 65 (POR)                                                                                                                                                                                                                                                                        |

| 10101001<br>X <sub>7</sub> X <sub>8</sub> X <sub>5</sub> X <sub>4</sub> X <sub>3</sub> X <sub>2</sub> X <sub>1</sub> X <sub>0</sub> | X <sub>1</sub> X <sub>0</sub> : Set Bias Ratio                                                                                                                      | X <sub>1</sub> X <sub>0</sub> = 00: 1/8, 1/6<br>X <sub>1</sub> X <sub>0</sub> = 01: 1/6, 1/5<br>X <sub>1</sub> X <sub>0</sub> = 10: 1/9, 1/7 (POR)<br>X <sub>1</sub> X <sub>0</sub> = 11: Prohibited                                                                                                                                                                                                   |

|                                                                                                                                     | $X_4 X_3 X_2$ : Set TC Value                                                                                                                                        | $\begin{array}{l} X_4 X_3 X_2 = 000: -0.01\%/C \; (TC0, POR) \\ X_4 X_3 X_2 = 010: -0.10\%/C \; (TC2) \\ X_4 X_3 X_2 = 100: -0.18\%/C \; (TC4) \\ X_4 X_3 X_2 = 111: -0.25\%/C \; (TC7) \\ X_4 X_3 X_2 = 001, \; 011, \; 101, \; 110: \; Reserved \end{array}$                                                                                                                                         |

|                                                                                                                                     | $X_7X_8X_8$ Modify Osc. Freq.                                                                                                                                       | Increase the value of $X_7 X_8 X_8$ will increase the oscillator frequency and vice versa. This command is not recommended to be used. $X_7 X_8 X_8 = 011$ (POR)                                                                                                                                                                                                                                       |

| 1010101X <sub>0</sub>                                                                                                               | X <sub>0</sub> : Set 1/4 Blas Ratio                                                                                                                                 | X <sub>0</sub> = 0: use Normal Setting (POR)<br>X <sub>0</sub> = 1: fixed at 1/4 Bias                                                                                                                                                                                                                                                                                                                  |

| 11010010<br>0X <sub>8</sub> X <sub>5</sub> 00010                                                                                    | X <sub>6</sub> X <sub>5</sub> : Set Total Frame Phases                                                                                                              | The On/Off of the Static Icon is given by 3 phases/1 phase overlapping of the M and MSTAT signals. This command set how many phases of dividing the M/MSTAT signals for each frame. The more the phases, the less the overlapping and thus the lower the effective driving voltage.<br>$X_8X_5 = 00: 3$ phases<br>$X_8X_5 = 00: 3$ phases<br>$X_8X_5 = 10: 7$ phases (POR)<br>$X_8X_5 = 11: 16$ phases |

| 11010011<br>00X <sub>5</sub> X <sub>4</sub> X <sub>3</sub> X <sub>2</sub> X <sub>1</sub> X <sub>0</sub>                             | X <sub>5</sub> X <sub>4</sub> X <sub>3</sub> X <sub>2</sub> X <sub>1</sub> X <sub>0</sub> : Set Display Offset<br>(for mux ratio has been<br>set less than 64 only) | After POR, $X_8X_4X_3X_2X_1X_0 = 0$<br>After setting mux ratio less than 64, data will be displayed at Center<br>of matrix. See Table 1.<br>To move display towards Row 0 by L, $X_8X_4X_3X_2X_1X_0 = L$<br>To move display away from Row 0 by L, $X_8X_4X_3X_2X_1X_0 = 64$ -L<br>Note: max. value of L = $(64 - display mux)/2$                                                                       |

Note: Patterns other than that given in Command Table and Extended Command Table are prohibited to enter to the chip as a command. Otherwise, unexpected result will occurs.

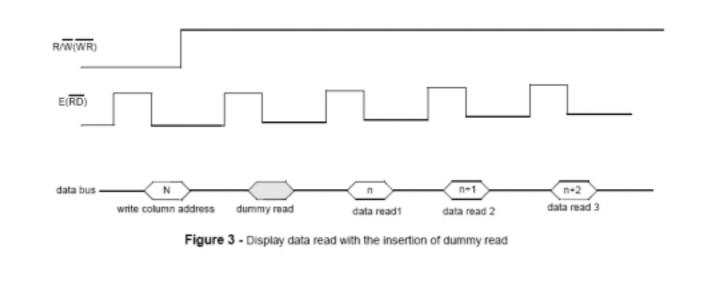

#### Data Read / Write

To read data from the GDDRAM, input High to R/W(WR) pin and D/C pin for 6800-series parallel mode, Low to E(RD) pin and High to D/C pin for 8080-series parallel mode. No data read is provided for serial mode. In normal mode, GDDRAM column address pointer will be increased by one automatically after each data read. However, no automatic increase will be performed in read-modify-write mode. Also, a dummy read is required before the first data read. See Figure 3 in Functional Description.

To write data to the GDDRAM, input Low to R/W(WR) pin and High to D/C pin for 6800-series parallel mode. For serial interface, it will always be in write mode. GDDRAM column address pointer will be increased by one automatically after each data write.

#### Address Increment Table (Automatic)

| D/C | R/W(WR) | Comment       | Address Increment | Remarks |

|-----|---------|---------------|-------------------|---------|

| 0   | 0       | Write Command | No                |         |

| 0   | 1       | Read Status   | No                |         |

| 1   | 0       | Write Data    | Yes               |         |

| 1   | 1       | Read Data     | Yes               | *1      |

Address Increment is done automatically after data read write. The column address pointer of GDDRAM'2 is affected.

Remarks: 1. If read data is issued in read-modify-write mode, address will NOT be increased.

2. Column Address will NOT wrap round to zero when overflow.

#### Commands Required for R/W(WR) Actions on RAM

| R/W(WR) Actions on RAMs             | Commands Required                                                                                                              |                                                                                                                                   |  |  |  |

|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Read/Write Data from/to GDDRAM.     | Set GDDRAM Page Address<br>Set GDDRAM Column Address<br>Read/Write Data                                                        | $\begin{array}{l} (1011X_3X_2X_1X_0)^* \\ (0001X_3X_2X_1X_0)^* \\ (0000X_3X_2X_1X_0)^* \\ (X_7X_8X_5X_4X_3X_2X_1X_0) \end{array}$ |  |  |  |

| Save/Restore GDDRAM Column Address. | Save GDDRAM Column Address by read-modify-<br>write mode<br>Restore GDDRAM Column Address by end of read-<br>modify-write mode |                                                                                                                                   |  |  |  |

Note: 1. No need to resend the command again if it is set previously.

The read / write action to the Display Data RAM does not depend on the display mode. This means the user can change the RAM content whether the target RAM content is being displayed or not.

#### Command Description

#### Set Lower Column Address

This command specifies the lower nibble of the 8-bit column address of the display data RAM. The column address will be incremented by each data access after it is pre-set by the MCU.

#### Set Higher Column Address

This command specifies the higher nibble of the 8-bit column address of the display data RAM. The column address will be incremented by each data access after it is pre-set by the MCU.

#### Set Internal Regulator Resistors Ratio

This command is to enable any one of the eight internal resistor sets for different regulator gain when using internal regulator resistor network (IRS pin pulled high). Please refer to Block Diagram Description section for detail calculation of the LCD driving voltage.

#### Set Power Control Register

This command turns on/off the various power circuits associated with the chip.

#### Set Display Start Line

This command is to set Display Start Line register to determine starting address of display RAM to be displayed by selecting a value from 0 to 63. With value equals to 0, D0 of Page 0 is mapped to COM0. With value equals to 1, D1 of Page0 is mapped to COM0. The display start line values of 0 to 63 are assigned to Page 0 to 7.

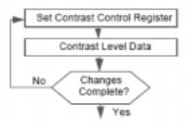

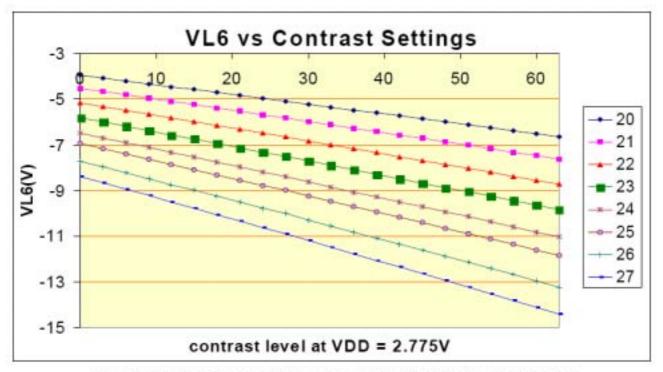

#### Set Contrast Control Register

This commands adjusts the contrast of the LCD panel by changing  $V_{L6}$  of the LCD drive voltage provided by the On-Chip power circuits.  $V_{L6}$  is set with 64 steps (6-bit) contrast control register. It is a compound commands:

#### Set Segment Re-map

This commands changes the mapping between the display data column address and segment driver. It allows flexibility in layout during LCD module assembly. Refer to Figure 5 for example.

#### Set LCD Bias

This command selects a suitable bias ratio (1/7 or 1/9) required for driving the particular LCD panel in use. The POR default for SSD1815 is set to 1/9 bias. For setting 1/4, 1/5, 1/6 and 1/8 bias, an extended compound command should be

#### used.

#### Set Entire Display On/Off

This command forces the entire display, including the icon row, to be "ON" regardless of the contents of the display data RAM. This command has priority over normal/reverse display. This command will be used with "Set Display Display ON/OFF" command to form a compound command for entering power save mode. See "Set Power Save Mode".

#### Set Normal/Reverse Display

This command sets the display to be either normal/ reverse. In normal display, a RAM data of 1 indicates an "ON" pixel while in reverse display, a RAM data of 0 indicates an "ON" pixel. In icon mode, the icon line is not reversed by this command.

#### Set Display On/Off

This command alternatively turns the display on and off. When display off is issued with entire display on, power save mode will be entered. See "Set Power Save Mode" for details.

#### Set Page Address

This command positions the page address from 0 to 8 possible positions in GDDRAM. Refer to Figure 5 for mapping.

#### Set COM Output Scan Direction

This command sets the scan direction of the COM output allowing layout flexibility in LCD module assembly.

#### Set Read-Modify-Write Mode

This command puts the chip in read-modify-write mode in which:

- 1. the column address is saved before entering the mode

- the column address is incremented by display data write but not by display data read

#### Software Reset

This command causes some of the internal status registers of the chip to be initialized:

- 1. Static indicator is turned OFF

- 2. Display start line register is set to 0

- 3. Column address counter is set to 0

- 4. Page address is set to 0

- 5. Normal scan direction of the COM outputs

- Contrast control register is set to 0

- 7. Test mode is turned OFF

#### Set End of Read-Modify-Write Mode

This command relieves the chip from read-modify-write mode. The column address that is saved before entering read-modify-write mode will be restored.

#### Set Indicator On/Off

This command turns on and off the static drive indicators. It also controls whether standby mode or sleep mode will be

entered after the power save compound command. See "Set Power Save Mode".

When the "Set Indicator On" command is sent, the "Indicator Display Mode" must be followed in the next command. The "Set Indicator Off" command is a single byte command and no following command is required.

#### NOP

A command causing No Operation.

#### Set Test Mode

This command force the driver chip into its test mode for internal testing of the chip. Under normal operation, user should NOT use this command.

#### Set Power Save Mode

To enter Standby or Sleep Mode, it should be done by using a compound command composed of "Set Display ON/OFF" and "Set Entire Display ON/OFF" commands. When "Set Entire Display ON" is issued when display is OFF, either Standby Mode or Sleep Mode will be entered.

The status of the Static Indicator will determine which power save mode is entered. If static indicator is off, the Sleep Mode will be entered:

- Internal oscillator and LCD power supply circuits are stopped

- Segment and Common drivers output V<sub>DD</sub> level

- The display data and operation mode before sleep are held

- 4. Internal display RAM can still be accessed

If the static indicator is on, the chip enters Standby Mode which is similar to sleep mode except:

- 1. Internal oscillator is on

- 2. Static drive system is on

Note also that if the software reset command is issued during Standby Mode, Sleep Mode will be entered. Both power save modes can be exited by the issue of a new software command or by pulling Low at hardware pin RES.

#### Status register Read

This command is issued by pulling D/C Low during a data read (refer to Figure 9 and 10 for parallel interface waveforms). It allows the MCU to monitor the internal status of the chip. No status read is provided for serial mode.

#### EXTENDED COMMANDS

These commands are used, in addition to basic commands, to trigger the enhanced features, on top of general ones, designed for the chip.

#### Set Multiplex Ratio

This command switches default 64 multiplex mode to any multiplex mode from 2 to 64. The chip pads ROW0-ROW63 will be switched to corresponding COM signal output, see Table 1 for examples of different multiplex settings.

#### Set Bias Ratio

Except the 1/4 bias, all the available bias ratios (1/5, 1/6, 1/7, 1/8 and 1/9) could be set using this command plus the Set LCD Bias. When changing the display multiplex ratio, the bias ratio also need to be adjusted to make display contrast consistent.

#### Set Temperature Coefficient (TC) Value

4 different temperature coefficient settings is selected by this command in order to match various liquid crystal temperature grades.

#### Modify Oscillator Frequency

The oscillator frequency can be fine tuned by applying this command. Since the oscillator frequency will be affected by some other factors, this command is not recommended for general usage. Please contact our application engineer for more detail explaination on this command.

#### Set 1/4 Bias Ratio

This command sets the bias ratio directly to 1/4 bias. This ratio is especially for use in under 12mux display.

In order to restore to other bias ratio, this command must be executed, with LSB=0, before the "Set Multiplex ratio" or "Set LCD Bias" command is sent.

#### Set Total Frame Phases

The total number of phases for one display frame is set by this command.

The Static Icon is generated by the overlapping of the M and MSTAT signals. To turn on the Static Icon, 3 phases overlapping will be applied to these signals, while 1 phase overlapping will be given to the Off status.

The more the total number of phases one frame, the less the overlapping time and thus the lower the effective driving voltage at the Static Icon on the LCD panel.

#### Set Display Offset

This command should be sent ONLY when the multiplex ratio is set less than 64.

When the mulitplex ratio less than 64 is set, the display will be mapped in the middle (y-direction) of the LCD, see Table 1. Use this command could move the display vertically within the 64 commons.

To make the Reduced-Mux Com 0 (Com 0 after reducing the multiplex ratio) towards the Row 0 direction for L lines, the 6-bit data in second command should be given by L.

To move in the other direction by L lines, the 6-bit data should be given by 64-L.

Please note that the display is confined within the un-reduced 64 mux. That is maximum value of L is given by the half of 64 minus the reduced-multiplex ratio. For an odd display mux after reduction, moving away from Row 0 direction will has 1 more step.

# 9. DISPLAY CONTROL FUNCTIONS

#### Command Decoder and Command Interface

This module determines whether the input data is interpreted as data or command. Data is directed to this module based upon the input of the D/C pin. If D/C is high, data is written to Graphic Display Data RAM (GDDRAM). If D/C is low, the input at  $D_7$ - $D_0$  is interpreted as a Command and it will be decoded and be written to the corresponding command register.

#### MPU Parallel 6800-series Interface

The parallel interface consists of 8 bi-directional data pins (D<sub>7</sub>-D<sub>0</sub>), R/W(WR), D/C, E(RD), CS1 and CS2, R/W(WR) input High indicates a read operation from the Graphic Display Data RAM (GDDRAM) or the status register. R/W(WR) input Low indicates a write operation to Display Data RAM or Internal Command Registers depending on the status of D/C input. The E(RD) input serves as data latch signal (clock) when high provided that CS1 and CS2 are low and high respectively. Refer to Figure 9 for Parallel Interface Timing Diagram of 6800-series microprocessors.

In order to match the operating frequency of display RAM with that of the microprocessor, some pipeline processing is internally performed which requires the insertion of a dummy read before the first actual display data read. This is shown in Figure 3 below.

#### MPU Parallel 8080-series interface

The parallel interface consists of 8 bi-directional data pins (D<sub>2</sub>-D<sub>0</sub>), E(RD), R/W(WR), D/C, CS1 and CS2. E(RD) input serves as data read latch signal (clock) when low provided that CS1 and CS2 are low and high respectively. Whether it is display data or status register read is controlled by D/C. R/W(WR) input serves as data write latch signal(clock) when high provided that CS1 and CS2 are low and high respectively. Whether it is display data or command register write is controlled by D/C. Refer to Figure 10 for Parallel Interface Timing Diagram of 8080-series microprocessor.

Similar to 6800-series interface, a dummy read is also required before the first actual display data read.

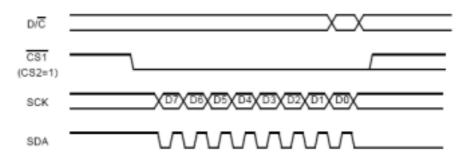

#### MPU Serial interface

The serial interface consists of serial clock SCK ( $D_6$ ), serial data SDA ( $D_7$ ), D/C, CS1 and CS2. SDA is shifted into a 8-bit shift register on every rising edge of SCL in the order of  $D_7$ ,  $D_6$ ,...  $D_0$ . D/C is sampled on every eighth clock to determine whether the data byte in the shift register is written to the Display Data RAM or command register at the same clock.

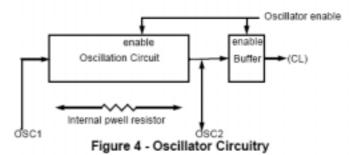

#### Oscillator Circuit

This module is an On-Chip low power RC oscillator circuitry (Figure 4). The oscillator generates the clock for the DC-DC voltage converter. This clock is also used in the Display Timing Generator.

Graphic Display Data RAM (GDDRAM)

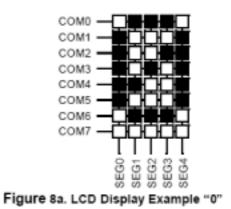

The GDDRAM is a bit mapped static RAM holding the bit pattern to be displayed. The size of the RAM is 132 X 65= 8580 bits. Figure 5 is a description of the GDDRAM address map. For mechanical flexibility, re-mapping on both Segment and Common outputs can be selected by software. For vertical scrolling of display, an internal register storing the display start line can be set to control the portion of the RAM data to be mapped to the display. Figure 5 shows the case in which the display start line register is set to 38h.

Note: The configuration in parentheses represent the remapped values of Rows and Columns

Figure 5. Graphic Display Data RAM (GDDRAM) Address Map (with display start line at 38H) For 132 X 64 Graphic Display Mode with separated icon Line

#### LCD Driving Voltage Generator and Regulator

This module generates the LCD voltage required for display driving output. It takes a single supply input and generate necessary voltage levels. This block consists of:

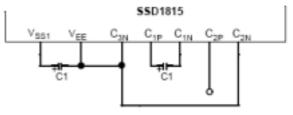

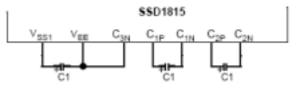

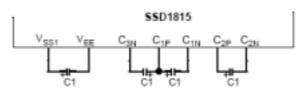

1. 2X, 3X and 4X DC-DC voltage converter

The built-in DC-DC voltage converter is use to generate large negative LCD driving voltage with reference to  $V_{DD}$  from the voltage input (V<sub>SS1</sub>). For SSD1815, it is possible to produce 2X, 3X or 4X boosting from the protential different between  $V_{SS1} - V_{DD}$ . Detail configurations of the DC-DC converter for different boosting

multiples are given in Figure 6 at the right.

2. Voltage Regulator (Voltages referenced to V<sub>DD</sub>)

The feedback gain control for LCD driving contrast curves can be selected by IRS pin to either internal (IRS pin = H) or external (IRS pin = L).

For internal resistor network is enabled, there are eight setting can be set by software.

If external control is selected, external resistors are required to be connected between  $V_{DD}$  and  $V_F$  (R1), and between  $V_F$  and  $V_{L8}$ (R2).

3. Contrast Control (Voltages referenced to V<sub>DD</sub>)

Software control of the 64 contrast voltage levels at each voltage regulator feedback gain. The equation of calculating the LCD driving voltage is given as:

$$V_{L6} - V_{DD} = Gain * (1 + \frac{Contrast}{\beta}) * V_{ref}$$

$$V_{ref} = (\frac{V_{BE} + R * (V_{DD} - V_{SS})}{1 + R})$$

where

| Int Reg Resistor<br>Ratio Setting | 0     | 1     | 2     | 3     | 4    | 5     | 6     | 7     | Est.<br>Resister |

|-----------------------------------|-------|-------|-------|-------|------|-------|-------|-------|------------------|

| Gain                              | -3.29 | -3.76 | -429  | 422   | -539 | -5.76 | -6.40 | -695  | -(1+R2R1)        |

| β                                 | 92.59 | 91.86 | 91.12 | 90.40 | 9.67 | 89.18 | 88.29 | 87,49 | 96.68            |

and

| тс  | 0<br>(-0.01%6 <sup>-0</sup> C) | 2<br>(-0.10%6/°C) | 4<br>(-0.18%/*C) | 7<br>(-0.25%/4C) |

|-----|--------------------------------|-------------------|------------------|------------------|

| Vis | 0.025                          | 0.523             | 0.520            | 0.517            |

| R.  | 0.72                           | 0.423             | 0.272            | 0.121            |

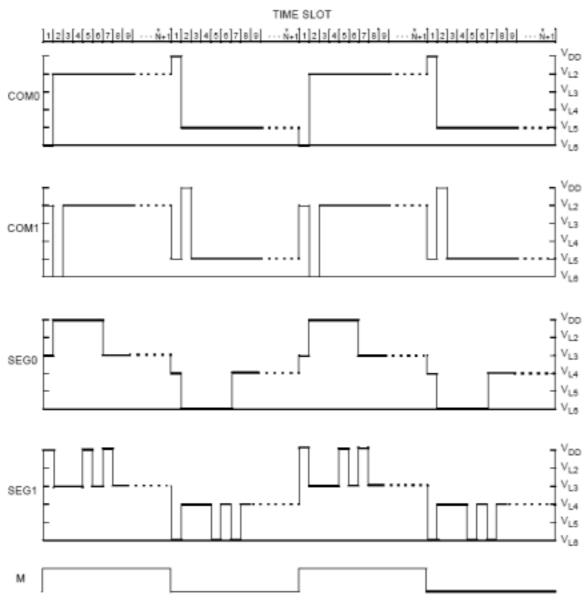

#### 4. Bias Divider

Divide the regulator output to give the LCD driving voltages ( $V_{L2}$  -  $V_{L5}$ ). A low power consumption circuit design in this bias divider saves most of the display current comparing to traditional design.

5. Bias Ratio Selection circuitry

Software control of 1/7 and 1/9 bias ratio to match the characteristic of LCD panel. In addition, 1/4, 1/5, 1/6 and 1/8 bias ratios are also software selectable using the extended command for any mux application.

6. Self adjust temperature compensation circuitry

This block provides 4 different compensation settings to satisfy various liquid crystal temperature gradings by software control. Default temperature coefficient (TC) setting is TC0.

2X Boosting Configuration

3X Boosting Configuration

#### 4X Boosting Configuration

Remarks:

- 1. C1 = 0.47 1.0uF

- 2. Boosting input from V<sub>SS1</sub>.

- 3. V<sub>SS1</sub> should be lower potential than or equal to V<sub>SS</sub>

4. All voltages are referenced to V<sub>DD</sub>

#### Figure 6 - Configurations for DC-DC Converter

Figure 7 - Contrast Curves at Different Interneal Feedback Resistor Ratio Settings

#### **Reset Circuit**

This block includes Power On Reset circuitry and the Reset pin, RES. Both of these having the same reset function. Once RES receives a negative reset pulse, all internal circuitry will start to initialize. Minimum pulse width for completing the reset sequence is 1us. The status of the chip after reset is given by:

- 1. Display is turned OFF

- 2. 132X64 Display Display Mode with separated Icon Line

- Normal segment and display data column address mapping (SEG0 mapped to address 00h)

- 4. Read-modify-write mode is OFF

- 5. Power control register is set to 000b

- 6. Shift register data clear in serial interface

- 7. Bias ratio is set to 1/9

- 8. Static indicator is turned OFF

- 9. Display start line is set to display RAM column address 0

- 10. Column address counter is set to 0

- 11. Page address is set to 0

- 12. Normal scan direction of the COM outputs

- 13. Contrast control register is set to 20h

- 14. Test mode is turned OFF

#### **Display Data Latch**

A series of registers carrying the display signal information. For SSD1815, there are 197 latches (132 + 65) for holding the data, which will be fed to the HV Buffer Cell and Level Selector to output the required voltage level.

#### Level Selector

Level Selector is a control of the display synchronization. Display

voltage can be separated into two sets and used with different cycles. Synchronization is important since it selects the required LCD voltage level to the HV Buffer Cell, which in turn outputs the COM or SEG LCD waveform.

#### HV Buffer Cell (Level Shifter)

HV Buffer Cell work as a level shifter which translates the low voltage output signal to the required driving voltage. The output is shifted out with an internal FRM clock which comes from the Display Timing Generator. The voltage levels are given by the level selector which is synchronized with the internal M signal.

\* Note : N is the number of multiplex ratio not included loon, N is equal to 64 on POR.

# **10. INTERFACE PIN CONNECTIONS**

| PIN | SYMBOL | I/O | FUNCTION                                                                                                                                                        |

|-----|--------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | VSS    |     | Ground pin, connected to 0V                                                                                                                                     |

| 2   | /RES   |     | Reset signal input:                                                                                                                                             |

|     |        |     | Initialization of the chip is started once this pin is pulled low. Minimum pulse                                                                                |

|     |        |     | width for completing the reset procedure is 5us.                                                                                                                |

| 3   | /CS    | Ι   | Chip select input:                                                                                                                                              |

|     |        |     | The chip is enabled for MCU communication only when /CS is pulled low.                                                                                          |

| 4   | RS     | Ι   | Data/Command control pin:                                                                                                                                       |

|     |        |     | When the pin is pulled high, the data at DB0~DB7 is treated as display data.                                                                                    |

|     |        |     | When the pin is pulled low, the data at DB0~DB7 wll be transferred to the                                                                                       |

|     |        |     | command register                                                                                                                                                |

| 5   | P/S    | I   | Parallel/Serial interface select:                                                                                                                               |

|     |        |     | When the pin is pulled high, parallel interface mode is selected.                                                                                               |

|     |        |     | When the pin is pulled low, serial interface will be selected.                                                                                                  |

|     |        |     | It is valid only when internal pull high resistor(R3) and pull low resistor(R4) are not used.                                                                   |

| 6   | /WR    | 1   |                                                                                                                                                                 |

| 0   |        | 1   | When interfacing to an 6800-series microprocessor, this pin will be used as Read/Write select input. Read mode will be carried out when this pin is pulled high |

|     |        |     | and write mode when low.                                                                                                                                        |

|     |        |     | When interfacing to an 8080-series microprocessor, this pin will be the Write                                                                                   |

|     |        |     | input. Data write operation is initiated when this pin is pulled low when the chip is                                                                           |

|     |        |     | selected.                                                                                                                                                       |

| 7   | /RD    | I   | When interfacing to an 6800-series microprocessor, this pin will be used as the                                                                                 |

|     |        |     | Enable signal. Read/Write operation is initiated when this pin is pulled high when                                                                              |

|     |        |     | the chip is selected.                                                                                                                                           |

|     |        |     | When interfacing to an 8080-series microprocessor, this pin receives the Read                                                                                   |

|     |        |     | signal. Data read operation is initiated when this pin is pulled low when the chip is                                                                           |

|     |        |     | selected.                                                                                                                                                       |

| 8   | DB0    |     | 8-bit bi-directional data bus                                                                                                                                   |

| 9   | DB1    |     | 8-bit bi-directional data bus                                                                                                                                   |

| 10  | DB2    | 0   | 8-bit bi-directional data bus                                                                                                                                   |

| 11  | DB3    | 0   | 8-bit bi-directional data bus                                                                                                                                   |

| 12  | DB4    | 0   | 8-bit bi-directional data bus                                                                                                                                   |

| 13  | DB5    | 0   | 8-bit bi-directional data bus                                                                                                                                   |

| 14  | DB6    | 0   | 8-bit bi-directional data bus                                                                                                                                   |

|     | DB7    | 0   | 8-bit bi-directional data bus                                                                                                                                   |

| 16  | VDD    | I/O | Power for supply(3.0V)                                                                                                                                          |

| 17  | SCL    | I/O | Serial clock input                                                                                                                                              |

|     | SDA    | I/O | Serial data input                                                                                                                                               |

|     | LEDA   | I/O | LCD driver supplies voltage.                                                                                                                                    |

| 20  | LEDK   | I/O | LCD driver supplies voltage.                                                                                                                                    |

# **11.RELIABILITY**

## **Content of Reliability Test**

|      | i                  | Environmental Test                                                     | i                     | ł               |

|------|--------------------|------------------------------------------------------------------------|-----------------------|-----------------|

| No.  | Test Item          | Content of Test                                                        | Test Condition        | Applicable      |

|      |                    |                                                                        |                       | Standard        |

| 1    | High temperature   | Endurance test applying the high storage                               | 80                    |                 |

|      | storage            | temperature for a long time.                                           | 200 hrs               |                 |

| 2    | Low temperature    | Endurance test applying the low storage                                | -30                   |                 |

|      | storage            | temperature for a long time.                                           | 200 hrs               |                 |

| 3    | High temperature   | Endurance test applying the electric stress                            | 70                    |                 |

|      | operation          | (Voltage & Current) and the thermal stress to                          | 200 hrs               |                 |

|      |                    | the element for a long time.                                           |                       |                 |

| 4    | Low temperature    | Endurance test applying the electric stress                            | -20                   |                 |

|      | operation          | under low temperature for a long time.                                 | 200 hrs               |                 |

| 5    | High temperature   | Endurance test applying the high temperature                           | 50 , 90 <u>.</u> RH   | MIL-202E-103B   |

|      | Humidity storage   | and high humidity storage for a long time.                             | 96 hrs                | JIS-C5023       |

| 6    | High temperature   | Endurance test applying the electric stress                            | 50 , 90 <u>.</u> RH   | MIL-202E-103B   |

|      | Humidity           | (Voltage & Current) and temperature humidity                           | 96 hrs                | JIS-C5023       |

|      | operation          | stress to the element for a long time.                                 |                       |                 |

| 7    | Temperature        | Endurance test applying the low and high                               | -20 - 70 10 cycles    |                 |

|      | cycle              | temperature cycle.                                                     |                       |                 |

|      |                    | -20°C 25°C 70°C                                                        |                       |                 |

|      |                    | $30$ min. $\rightleftharpoons$ $5$ min. $\rightleftharpoons$ $30$ min. |                       |                 |

|      |                    | $\leftarrow \longrightarrow$                                           |                       |                 |

|      |                    | 1 cycle                                                                |                       |                 |

| Mech | anical Test        |                                                                        |                       |                 |

| 8    | Vibration test     | Endurance test applying the vibration during                           |                       | MIL-202E-201A   |

|      |                    | transportation and using.                                              | 10-22Hz 1.5mmp-p      | JIS-C5025       |

|      |                    |                                                                        |                       | JIS-C7022-A-10  |

|      |                    |                                                                        | 22-500Hz 1.5G         |                 |

|      |                    |                                                                        | Total 0.5hrs          |                 |

| 9    | Shock test         | Constructional and mechanical endurance test                           | 50G half sign wave 11 | MIL-202E-213B   |

|      |                    | applying the shock during transportation.                              | msedc 3 times of each |                 |

|      |                    |                                                                        | direction             |                 |

| 10   | Atmospheric        | Endurance test applying the atmospheric                                | 115 mbar 40 hrs       | MIL-202E-105C   |

|      | pressure test      | pressure during transportation by air.                                 |                       |                 |

| Othe | rs                 | •                                                                      |                       | •               |

| 11   | Static electricity | Endurance test applying the electric stress to                         | VS=800V, RS=1.5 k     | MIL-883B-3015.1 |

|      | test               | the terminal.                                                          | CS=100 pF             |                 |

|      |                    |                                                                        | 1 time                |                 |

\*\*\* Supply voltage for logic system = 3V. Supply voltage for LCD system = Operating voltage at 25 .

# YM12864T-2

### **Failure Judgement Criterion**

| Criterion Item            |   |   |   | Test Item No. |   |   |   |   |   |    | Failure Judgment Criterion |                                     |

|---------------------------|---|---|---|---------------|---|---|---|---|---|----|----------------------------|-------------------------------------|

|                           | 1 | 2 | 3 | 4             | 5 | 6 | 7 | 8 | 9 | 10 | 11                         |                                     |

| Basic specification       |   |   |   |               |   |   |   |   |   |    |                            | Out of the Basic Specification      |

| Electrical characteristic |   |   |   |               |   |   |   |   |   |    |                            | Out of the DC and AC Characterstic  |

| Mechanical                |   |   |   |               |   |   |   |   |   |    |                            | Out of the Mechanical Specification |

| characterstic             |   |   |   |               |   |   |   |   |   |    |                            | Color change : Out of Limit         |

|                           |   |   |   |               |   |   |   |   |   |    |                            | Apperance Specification             |

| Optical characterstic     |   |   |   |               |   |   |   |   |   |    |                            | Out of the Apperance Standard       |

# **12. QUALITY GUARANTEE**

# Acceptable Quality Level

Each lot should satisfy the quality level defined as follows.

- Inspection method : MIL-STD-105E LEVEL II Normal one time sampling

- AQL

| Partition | AQL  | Definition                                                         |

|-----------|------|--------------------------------------------------------------------|

| A: Major  | 0.4% | Functional defective as product                                    |

| B: Minor  | 1.5% | Satisfy all functions as product but not satisfy cosmetic standard |

## **Definition of 'LOT'**

One lot means the delivery quantity to customer at one time.

# **Conditions of Cosmetic Inspection**

### **Environmental condition**

The inspection should be performed at the 1cm of height from the LCD module under 2 pieces of

40W white fluorescent lamps (Normal temperature 20~25 and normal humidity 60±15%RH).

### **Inspection method**

The visual check should be performed vertically at more than 30cm distance from the LCD panel.

### **Driving voltage**

The VO value which the most optimal contrast can be obtained near the specified VO in the

specification. (Within  $\pm 0.5V$  of typical value at 25 .).

# **13. INSPECTION CRITERIA**

# 13.1 Module Cosmetic Criteria

| No. | Item                        | Judgement Criterion                                                                                                                                                                                                                                                                              | Partition |

|-----|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| 1   | Difference in Spec.         | None allowed                                                                                                                                                                                                                                                                                     | Major     |

| 2   | Pattern peeling             | No substrate pattern peeling and floating                                                                                                                                                                                                                                                        | Major     |

| 3   | Soldering defects           | No soldering missing                                                                                                                                                                                                                                                                             | Major     |

|     |                             | No soldering bridge                                                                                                                                                                                                                                                                              | Major     |

|     |                             | No cold soldering                                                                                                                                                                                                                                                                                | Major     |

| 4   | Resist flaw on substrate    | Invisible copper foil ('0.5mm or more) on substrate pattern                                                                                                                                                                                                                                      | Minor     |

| 5   | Accretion of metallic       | No soldering dust No accretion of metallic foreign matters                                                                                                                                                                                                                                       | Minor     |

|     | Foreign matter              | (Not exceed '0.2mm)                                                                                                                                                                                                                                                                              | Minor     |

| 6   | Stain                       | No stain to spoil cosmetic badly                                                                                                                                                                                                                                                                 | Minor     |

| 7   | Plate discoloring           | No plate fading, rusting and discoloring                                                                                                                                                                                                                                                         | Minor     |

| 8   | Solder amount 1. Lead parts | <ul> <li>a. Soldering side of PCB<br/>Solder to form a 'Filet' all<br/>around the lead.<br/>Solder should not hide the<br/>lead form perfectly. (too<br/>much)</li> <li>b. Components side<br/>( In case of 'Through Hole PCB' )</li> <li>Solder to reach the Components side of PCB.</li> </ul> | Minor     |

|     | 2. Flat packages            | Either 'Toe' (A) or 'Seal'<br>(B) of the lead to be covered<br>by 'Filet'.<br>Lead form to be assume over solder. A B                                                                                                                                                                            | Minor     |

|     | 3. Chips                    | (3/2) H h (1/2) H                                                                                                                                                                                                                                                                                | Minor     |

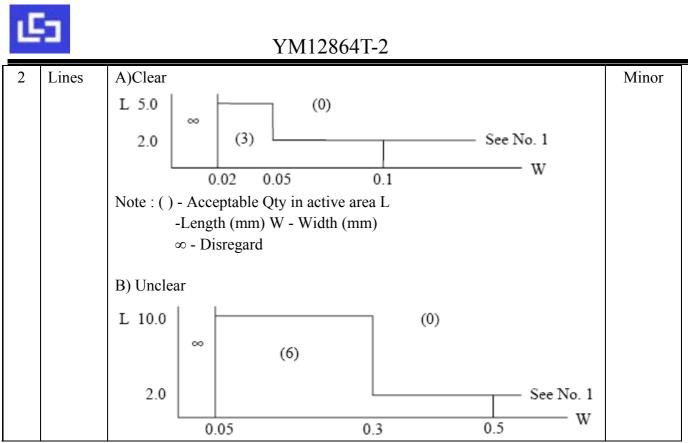

# 13.2 Screen Cosmetic Criteria (Non-Operating)

| No. | Defect | Judgement Criterion | Partition |

|-----|--------|---------------------|-----------|

|     |        |                     |           |

# YM12864T-2

|   |               | 1101120                                                             | • •                                                                    |        |  |  |  |  |  |

|---|---------------|---------------------------------------------------------------------|------------------------------------------------------------------------|--------|--|--|--|--|--|

| 1 | Spots         | In accordance with Screen                                           | n accordance with Screen Cosmetic Criteria (Operating) No.1.           |        |  |  |  |  |  |