# UM1845

User manual

# STM32F2 Series safety manual

## Introduction

This document must be read along with the technical documentation such as reference manual(s) and datasheets for the STM32F2 Series microcontroller devices, available on www.st.com.

It describes how to use the devices in the context of a safety-related system, specifying the user's responsibilities for installation and operation in order to reach the targeted safety integrity level. It also pertains to the X-CUBE-STL software product.

It provides the essential information pertaining to the applicable functional safety standards, which allows system designers to avoid going into unnecessary details.

The document is written in compliance with IEC 61508, and it provides information relative to other functional safety standards.

The safety analysis in this manual takes into account the device variation in terms of memory size, available peripherals, and package.

# 1 About this document

# 1.1 Purpose and scope

This document describes how to use Arm<sup>®</sup> Cortex<sup>®</sup>-M3 -based STM32F2 Series microcontroller unit (MCU) devices (further also referred to as Device(s)) in the context of a safety-related system, specifying the user's responsibilities for installation and operation, in order to reach the desired safety integrity level. It is useful to system designers willing to evaluate the safety of their solution embedding one or more *Device(s)*. For terms used, refer to the glossary at the end of the document.

Note: Arm is a registered trademark of Arm Limited (or its subsidiaries) in the US and/or elsewhere.

arm

## **1.2** Normative references

This document is written in compliance with the IEC 61508 international norm for functional safety of electrical, electronic and programmable electronic safety-related systems, version IEC 61508:1-7 © IEC:2010. The other functional safety standards considered in this manual are:

- ISO 13849-1:2015, ISO13849-2:2012

- IEC 62061:2005+AMD1:2012+AMD2:2015

- IEC 61800-5-2:2016

The following table maps the document content with respect to the IEC 61508-2 Annex D requirements.

#### Table 1. Document sections versus IEC 61508-2 Annex D safety requirements

| Safety requirement                                                                                                                                                                                                                            | Section number |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--|

| D2.1 a) a functional specification of the functions capable of being performed                                                                                                                                                                | 3              |  |

| D2.1 b) identification of the hardware and/or software configuration of the Compliant item                                                                                                                                                    | 3.2            |  |

| D2.1 c) constraints on the use of the <i>Compliant item</i> or assumptions on which analysis of the behavior or failure rates of the item are based                                                                                           | 3.2            |  |

| 02.2 a) the failure modes of the <i>Compliant item</i> due to random hardware failures, that result in a failure f the function and that are not detected by diagnostics internal to the <i>Compliant item</i> ;                              |                |  |

| D2.2 b) for every failure mode in a), an estimated failure rate;                                                                                                                                                                              |                |  |

| D2.2 c) the failure modes of the <i>Compliant item</i> due to random hardware failures, that result in a failure of the function and that are detected by diagnostics internal to the <i>Compliant item</i> ;                                 | 3.7            |  |

| D2.2 d) the failure modes of the diagnostics, internal to the <i>Compliant item</i> due to random hardware failures, that result in a failure of the diagnostics to detect failures of the function;                                          | -              |  |

| D2.2 e) for every failure mode in c) and d), the estimated failure rate;                                                                                                                                                                      |                |  |

| D2.2 f) for every failure mode in c) that is detected by diagnostics internal to the <i>Compliant item</i> , the diagnostic test interval;                                                                                                    | 3.2.2          |  |

| D2.2 g) for every failure mode in c) the outputs of the <i>Compliant item</i> initiated by the internal diagnostics;                                                                                                                          | 3.6            |  |

| D2.2 h) any periodic proof test and/or maintenance requirements;                                                                                                                                                                              |                |  |

| D2.2 i) for those failure modes, in respect of a specified function, that are capable of being detected by external diagnostics, sufficient information must be provided to facilitate the development of an external diagnostics capability. | 3.7            |  |

| D2.2 j) the hardware fault tolerance;                                                                                                                                                                                                         | 3              |  |

| D2.2 k) the classification as type A or type B of that part of the <i>Compliant item</i> that provides the function (see 7.4.4.1.2 and 7.4.4.1.3);                                                                                            |                |  |

# **1.3** Reference documents

- [1] AN5365, Results of FMEA on STM32F2 Series microcontrollers.

- [2] AN5363, Results of FMEDA on STM32F2 Series microcontrollers.

# 2 Device development process

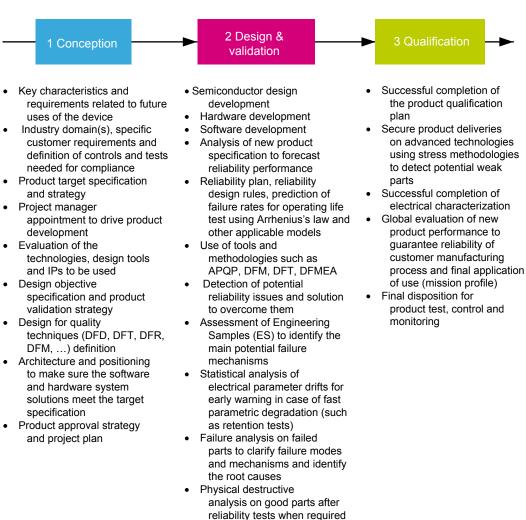

STM32 series product development process (see Figure 1), compliant with the IATF 16949 standard, is a set of interrelated activities dedicated to transform customer specification and market or industry domain requirements into a semiconductor device and all its associated elements (package, module, sub-system, hardware, software, and documentation), qualified with ST internal procedures and fitting ST internal or subcontracted manufacturing technologies.

#### Figure 1. STMicroelectronics product development process

reliability tests when required

Electrostatic discharge

(ESD) and latch-up sensitivity

measurement

# **3** Reference safety architecture

This section reports details of the STM32F2 Series safety architecture.

# 3.1 Safety architecture introduction

Device(s) analyzed in this document can be used as Compliant item(s) within different safety applications.

The aim of this section is to identify such *Compliant item*(s), that is, to define the context of the analysis with respect to a reference concept definition. The concept definition contains reference safety requirements, including design aspects external to the defined *Compliant item*.

As a consequence of *Compliant item* approach, the goal is to list the system-related information considered during the analysis, rather than to provide an exhaustive hazard and risk analysis of the system around the device. Such information includes, among others, application-related assumptions for danger factors, frequency of failures and diagnostic coverage already guaranteed by the application.

# 3.2 Compliant item

This section defines the *Compliant item* term and provides information on its usage in different safety architecture schemes.

#### 3.2.1 Definition of Compliant item

According to IEC 61508:1 clause 8.2.12, *Compliant item* is any item (for example an element) on which a claim is being made with respect to the clauses of IEC 61508 series. Any mature *Compliant item* must be described in a safety manual available to End user.

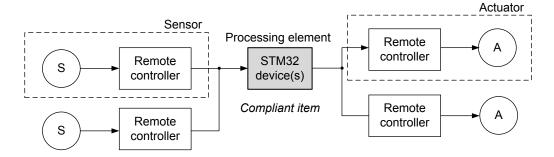

In this document, *Compliant item* is defined as a system including one or two STM32 devices (see Figure 2). The communication bus is directly or indirectly connected to sensors and actuators.

#### Figure 2. STM32 as Compliant item

Other components might be related to the *Compliant item*, like the external HW components needed to guarantee either the functionality of the device (external memory, clock quartz and so on) or its safety (for example, the external watchdog or voltage supervisors).

A defined Compliant item can be classified as element according to IEC61508-4, 3.4.5.

#### 3.2.2 Safety functions performed by Compliant item

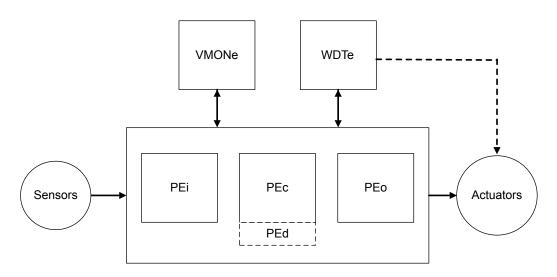

In essence, *Compliant item* architecture encompasses the following processes performing the safety function or a part of it:

- input processing elements (PEi) reading safety related data from the remote controller connected to the sensor(s) and transferring them to the following computation elements

- computation processing elements (PEc) performing the algorithm required by the safety function and transferring the results to the following output elements

- output processing elements (PEo) transferring safety related data to the remote controller connected to the actuator

- in 1002 architecture, potentially a further voting processing element (PEv)

- the computation processing elements can be involved (to the extent depending to the target safety integrity) in the implementation of local software-based diagnostic functions; this is represented by the block PEd

- processes external to the *Compliant item* ensuring safety integrity, such as watchdog (WDTe) and voltage monitors (VMONe)

The role of the PEv process and WDTe and VMONe external processes is clarified in the sections where the conditions of use (CoU) (definition of safety mechanism) are detailed:

- WDTe: refer to External watchdog CPU\_SM\_5 and Control flow monitoring in Application software CPU\_SM\_1,

- VMONe: refer to Supply voltage monitoring VSUP\_SM\_1 and System-level power supply management -VSUP\_SM\_5.

In summary, the devices support the implementation of *End user* safety functions consisting of three operations:

- safe acquisition of safety-related data from input peripheral(s)

- · safe execution of application software program and safe computation of related data

- safe transfer of results or decisions to output peripheral(s)

Claims on the *Compliant item* and computation of safety metrics are done with respect to these three basic operations.

According to the definition for implemented safety functions, *Compliant item* (element) can be regarded as type B (as per IEC61508-2, 7.4.4.1.3 definition). Despite accurate, exhaustive and detailed failure analysis, *Device* has to be considered as intrinsically complex. This implies its type B classification.

Two main safety architectures are identified: 1001 (using one device) and 1002 (using two devices).

#### 3.2.3 Reference safety architectures - 1001

1001 reference architecture (Figure 3) ensures safety integrity of *Compliant item* through combining device internal processes (implemented safety mechanisms) with external processes WDTe and VMONe. 1001 reference architecture targets safety integrity level (SIL) *SIL2*.

UM1845 - Rev 5

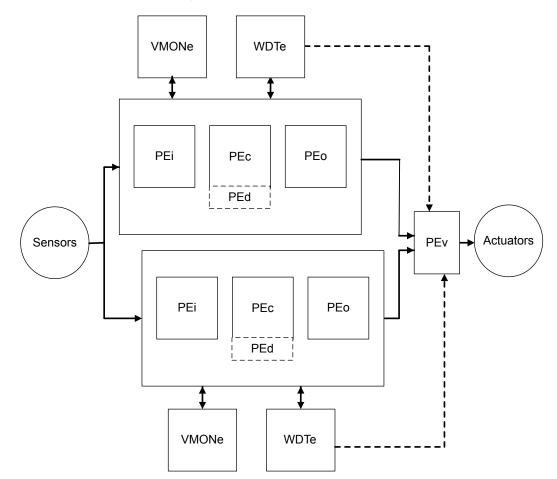

#### 3.2.4 Reference safety architectures - 1002

1002 reference architecture (Figure 4) contains two separate channels, either implemented as 1001 reference architecture ensuring safety integrity of *Compliant item* through combining device internal processes (implemented safety mechanisms) with external processes WDTe and VMONe. The overall safety integrity is then ensured by the external voter PEv, which allows claiming hardware fault tolerance (HFT) equal to 1. Achievement of higher safety integrity levels as per IEC61508-2 Table 3 is therefore possible. Appropriate separation between the two channels (including power supply separation) should be implemented in order to avoid huge impact of common-cause failures (refer to Section 4.2 Analysis of dependent failures). However,  $\beta$  and  $\beta$ D parameters computation is required.

1002 reference architecture targets SIL3.

Figure 4. 1002 reference architecture

# 3.3 Safety analysis assumptions

This section collects all assumptions made during the safety analysis of the devices.

#### 3.3.1 Safety requirement assumptions

The concept specification, the hazard and risk analysis, the overall safety requirement specification and the consequent allocation determine the requirements for *Compliant item* as further listed. *ASR* stands for assumed safety requirements.

#### **Caution:** It is the *End user*'s responsibility to check the compliance of the final application with these assumptions.

**ASR1:** *Compliant item* can be used to implement four kinds of safety function modes of operation according to part 4,3.5.16:

- a continuous mode (CM) or high-demand (HD) SIL3 safety function (CM3), or

- a low-demand (LD) SIL3 safety function (LD3), or

- a CM or HD SIL2 safety function (CM2), or

- a LD SIL2 safety function (LD2).

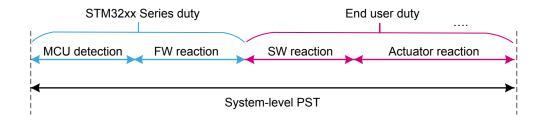

**ASR2:** *Compliant item* is used to implement safety function(s) allowing a specific worst-case time budget (see note below) for the STM32 *MCU* to detect and react to a failure. That time corresponds to the portion of the process safety time (PST) allocated to the device (*STM32xx Series duty* in Figure 5) in error reaction chain at system level.

Note: The computation for time budget mainly depends on the execution speed for periodic tests implemented by software. Such duration might depends on the actual amount of hardware resources (RAM memory, Flash memory, peripherals) actually declared as safety-related. Further constraints and requirements from IEC61508-2, 7.4.5.3 must be considered.

#### Figure 5. Allocation and target for STM32 PST

**ASR3:** Compliant item is used to implement safety function(s) that can be continuously powered on for a period over eight hours. It is assumed to not require any proof test, and the lifetime of the product is considered to be no less than 10 years.

**ASR4:** It is assumed that only one safety function is performed or if many, all functions are classified with the same *SIL* and therefore they are not distinguishable in terms of their safety requirements.

**ASR5:** In case of multiple safety function implementations, it is assumed that *End user* is responsible to duly ensure their mutual independence.

**ASR6:** It is assumed that there are no *non-safety-related* functions implemented in application software, coexisting with safety functions.

**ASR7:** It is assumed that the implemented safety function(s) does (do) not depend on transition of the device to and from a low-power state.

ASR8: The local safe state of Compliant item is the one in which either:

- SS1: the application software is informed by the presence of a fault and a reaction by the application software itself is possible.

- SS2: the application software cannot be informed by the presence of a fault or the application software is not able to execute a reaction.

Note:

End user must take into account that random hardware failures affecting the Device can compromise its operation (for example failure modes affecting the program counter prevent the correct execution of software).

The following table provides details on the SS1 and SS2 safe states.

| Safe<br>state | Condition                                                                                                                                      | Compliant item<br>action                | System transition to safe state – 1001 architecture                                | System transition to safe state – 1002 architecture                                               |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| SS1           | The application software is<br>informed by the presence of a<br>fault and a reaction by the<br>application software itself is<br>possible.     | Fault reporting to application software | Application software drives<br>the overall system in its safe<br>state             | Application software in one of<br>the two channels drives the<br>overall system in its safe state |

| SS2           | The application software cannot<br>be informed by the presence of a<br>fault or the application software is<br>not able to execute a reaction. | Reset signal issued by WDTe             | WDTe drives the overall system in its safe state ("safe shut-down") <sup>(1)</sup> | PEv drives the overall system in its safe state                                                   |

#### Table 2. SS1 and SS2 safe state details

1. Safe state achievement intended here is compliant to Note on IEC 61508-2, 7.4.8.1

**ASR9:** It is assumed that the safe state defined at system level by *End user* is compatible with the assumed local safe state (SS1, SS2) for *Compliant item*.

ASR10: Compliant item is assumed to be analyzed according to routes 1H and 1S of IEC 61508-2.

Note: Refer to Section 3.5 Systematic safety integrity and Section 3.6 Hardware and software diagnostics.

ASR11: Compliant item is assumed to be regarded as type B, as per IEC 61508:2, 7.4.4.1.2.

#### **3.4** Electrical specifications and environment limits

To ensure safety integrity, the user must operate the Device(s) within its (their) specified:

- absolute maximum rating

- capacity

- operating conditions

For electrical specifications and environmental limits of *Device*(s), refer to its (their) technical documentation such as datasheet(s) and reference manual(s) available on www.st.com.

## 3.5 Systematic safety integrity

According to the requirements of IEC 61508 -2, 7.4.2.2, the *Route 1S* is considered in the analysis of *Device*(s). As clearly authorized by IEC61508-2, 7.4.6.1, STM32 *MCU* products can be considered as standard, massproduced electronic integrated devices, for which stringent development procedures, rigorous testing and extensive experience of use minimize the likelihood of design faults. However, ST internally assesses the compliance of the *Device* development flow, through techniques and measures suggested in the IEC 61508-2 Annex F. A *safety case database* (see Section 5 List of evidences) keeps evidences of the current compliance level to the norm. This section lists all the safety mechanisms (hardware, software and application-level) considered in the device safety analysis. It is expected that users are familiar with the architecture of the device, and that this document is used in conjunction with the related device datasheet, user manual and reference information. To avoid inconsistency and redundancy, this document does not report device functional details. In the following descriptions, the words *safety mechanism, method*, and *requirement* are used as synonyms.

As the document provides information relative to the superset of peripherals available on the devices it covers (not all devices have all peripherals), users are supposed to disregard any recommendations not applicable to their *Device* part number of interest.

Information provided for a function or peripheral applies to all instances of such function or peripheral on *Device*. Refer to its reference manual or/and datasheet for related information.

The implementation guidelines reported in the following section are for reference only. The safety verification executed by ST during the device safety analysis and related diagnostic coverage figures reported in this manual (or related documents) are based on such guidelines. For clarity, safety mechanisms are grouped by *Device* function.

Information is organized in form of tables, one per safety mechanism, with the following fields:

| SM CODE                               | Unique safety mechanism code/identifier used also in <i>FMEA</i> document. Identifiers use the scheme $mmm\_SM\_x$ where $mmm$ is a 3- or 4-letter module (function, peripheral) short name, and x is a number. It is possible that the numbering is not sequential (although usually incremental) and/or that the module short name is different from that used in other documents. |

|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Description                           | Short mnemonic description                                                                                                                                                                                                                                                                                                                                                           |

| Ownership                             | ST : means that method is available on silicon.                                                                                                                                                                                                                                                                                                                                      |

|                                       | <i>End user</i> : method must be implemented by <i>End user</i> through <i>Application software</i> modification, hardware solutions, or both.                                                                                                                                                                                                                                       |

| Detailed implementation               | Detailed implementation sometimes including notes about the safety concept behind the introduction of the safety mechanism.                                                                                                                                                                                                                                                          |

| Error reporting                       | Describes how the fault detection is reported to application software.                                                                                                                                                                                                                                                                                                               |

| Fault detection time                  | Time that the safety mechanism needs to detect the hardware failure.                                                                                                                                                                                                                                                                                                                 |

| Addressed fault model                 | Reports fault model(s) addressed by the diagnostic (permanent, transient, or both), and other information:                                                                                                                                                                                                                                                                           |

|                                       | <ul> <li>If ranked for Fault avoidance: method contributes to lower the probability of occurrence of a<br/>failure</li> </ul>                                                                                                                                                                                                                                                        |

|                                       | <ul> <li>If ranked for Systematic: method is conceived to mitigate systematic errors (bugs) in<br/>application software design</li> </ul>                                                                                                                                                                                                                                            |

| Dependency on<br>Device configuration | Reports if safety mechanism implementation or characteristics change among different <i>Device</i> part numbers.                                                                                                                                                                                                                                                                     |

| Initialization                        | Specific operation to be executed to activate the contribution of the safety mechanism                                                                                                                                                                                                                                                                                               |

| Periodicity                           | Continuous : safety mechanism is active in continuous mode.                                                                                                                                                                                                                                                                                                                          |

|                                       | Periodic: safety mechanism is executed periodically <sup>(1)</sup> .                                                                                                                                                                                                                                                                                                                 |

|                                       | On-demand: safety mechanism is activated in correspondence to a specified event (for instance, reception of a data message).                                                                                                                                                                                                                                                         |

|                                       | Startup: safety mechanism is supposed to be executed only at power-up or during off-line maintenance periods.                                                                                                                                                                                                                                                                        |

| Test for the<br>diagnostic            | Reports specific procedure (if any and recommended) to allow on-line tests of safety mechanism efficiency.                                                                                                                                                                                                                                                                           |

| Multiple-fault protection             | Reports the safety mechanism(s) associated in order to correctly manage a multiple-fault scenario (refer to Section 4.1.3 Notes on multiple-fault scenario).                                                                                                                                                                                                                         |

| Recommendations and known limitations | Additional recommendations or limitations (if any) not reported in other fields.                                                                                                                                                                                                                                                                                                     |

1. In CM systems, safety mechanism can be accounted for diagnostic coverage contribution only if it is executed at least once per PST. For LD and HD systems, constraints from IEC61508-2, 7.4.5.3 must be applied.

# 3.6.1 Arm<sup>®</sup> Cortex<sup>®</sup>-M3 CPU

## Table 3. CPU\_SM\_0

| SM CODE                               | CPU_SM_0                                                                                                                                                                                                                                                                                                                                                          |

|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Description                           | Periodical core self-test software for Arm <sup>®</sup> Cortex <sup>®</sup> -M3 CPU                                                                                                                                                                                                                                                                               |

| Ownership                             | End user or ST                                                                                                                                                                                                                                                                                                                                                    |

| Detailed implementation               | The software test is built around well-known techniques already addressed by IEC 61508:7, A.3.2 (Self-test by software: walking bit one-channel). To reach the required values of coverage, the self-test software is specified by means of a detailed analysis of all the <i>CPU</i> failure modes and related failure modes distribution                        |

| Error reporting                       | Depends on implementation                                                                                                                                                                                                                                                                                                                                         |

| Fault detection time                  | Depends on implementation                                                                                                                                                                                                                                                                                                                                         |

| Addressed fault model                 | Permanent                                                                                                                                                                                                                                                                                                                                                         |

| Dependency on Device configuration    | None                                                                                                                                                                                                                                                                                                                                                              |

| Initialization                        | None                                                                                                                                                                                                                                                                                                                                                              |

| Periodicity                           | Periodic                                                                                                                                                                                                                                                                                                                                                          |

| Test for the diagnostic               | Self-diagnostic capabilities can be embedded in the software, according the test implementation design strategy chosen. The adoption of checksum protection on results variables and defensive programming are recommended.                                                                                                                                       |

| Multiple-fault protection             | CPU_SM_5: external watchdog                                                                                                                                                                                                                                                                                                                                       |

| Recommendations and known limitations | This method is the main asset in STM32F2 Series safety concept. <i>CPU</i> integrity is a key factor because the defined diagnostics for <i>MCU</i> peripherals are to major part software-based. Startup execution of this safety mechanism is recommended for multiple fault mitigations - refer to Section 4.1.3 Notes on multiple-fault scenario for details. |

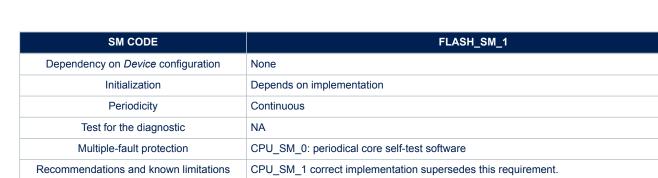

## Table 4. CPU\_SM\_1

| SM CODE                               | CPU_SM_1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Description                           | Control flow monitoring in Application software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Ownership                             | End user                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                       | A significant part of the failure distribution of <i>CPU</i> core for permanent faults is related to failure modes directly related to program counter loss of control or hang-up. Due to their intrinsic nature, such failure modes are not addressed by a standard software test method like SM_CPU_0. Therefore it is necessary to implement a run-time control of the <i>Application software</i> flow, in order to monitor and detect deviation from the expected behavior due to such faults. Linking this mechanism to watchdog firing assures that severe loss of control (or, in the worst case, a program counter hang-up) is detected. |

|                                       | The guidelines for the implementation of the method are the following:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                       | • Different internal states of the <i>Application software</i> are well documented and described (the use of a dynamic state transition graph is encouraged).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Detailed implementation               | <ul> <li>Monitoring of the correctness of each transition between different states of the<br/>Application software is implemented.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                       | • Transition through all expected states during the normal <i>Application software</i> program loop is checked.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                       | • A function in charge of triggering the system watchdog is implemented in order to constrain the triggering (preventing the issue of <i>CPU</i> reset by watchdog) also to the correct execution of the above-described method for program flow monitoring. The use of window feature available on internal window watchdog (WWDG) is recommended.                                                                                                                                                                                                                                                                                               |

|                                       | • The use of the independent watchdog (IWDG), or an external one, helps to implement a more robust control flow mechanism fed by a different clock source.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                       | In any case, safety metrics do not depend on the kind of watchdog in use (the adoption of independent or external watchdog contributes to the mitigation of dependent failures, see Section 4.2.2 Clock)                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Error reporting                       | Depends on implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Fault detection time                  | Depends on implementation. Higher value is fixed by watchdog timeout interval.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Addressed fault model                 | Permanent and transient                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Dependency on Device configuration    | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Initialization                        | Depends on implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Periodicity                           | Continuous                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Test for the diagnostic               | NA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Multiple-fault protection             | CPU_SM_0: periodical core self-test software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Recommendations and known limitations | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

## Table 5. CPU\_SM\_2

| SM CODE                               | CPU_SM_2                                                                                                                                                                                                                                                              |

|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Description                           | Double computation in Application software                                                                                                                                                                                                                            |

| Ownership                             | End user                                                                                                                                                                                                                                                              |

|                                       | A timing redundancy for safety-related computation is considered to detect transient faults affecting the Arm <sup>®</sup> Cortex <sup>®</sup> -M3 <i>CPU</i> subparts devoted to mathematical computations and data access.                                          |

|                                       | The guidelines for the implementation of the method are the following:                                                                                                                                                                                                |

| Detailed implementation               | The requirement needs be applied only to safety-relevant computation, which in case of wrong result could interfere with the system safety functions. Such computation must be therefore carefully identified in the original <i>Application software</i> source code |

|                                       | Both mathematical operation and comparison are intended as computation.                                                                                                                                                                                               |

|                                       | • The redundant computation for mathematical computation is implemented by using copies of the original data for second computation, and by using an equivalent formula if possible                                                                                   |

| Error reporting                       | Depends on implementation                                                                                                                                                                                                                                             |

| Fault detection time                  | Depends on implementation                                                                                                                                                                                                                                             |

| Addressed fault model                 | Transient                                                                                                                                                                                                                                                             |

| Dependency on Device configuration    | None                                                                                                                                                                                                                                                                  |

| Initialization                        | Depends on implementation                                                                                                                                                                                                                                             |

| Periodicity                           | Continuous                                                                                                                                                                                                                                                            |

| Test for the diagnostic               | Not needed                                                                                                                                                                                                                                                            |

| Multiple-fault protection             | CPU_SM_0: periodical core self-test software                                                                                                                                                                                                                          |

| Recommendations and known limitations | <i>End user</i> is responsible to carefully avoid that the intervention of optimization features of the used compiler removes timing redundancies introduced according to this condition of use.                                                                      |

# Table 6. CPU\_SM\_3

| SM CODE                               | CPU_SM_3                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Description                           | Arm <sup>®</sup> Cortex <sup>®</sup> -M3 HardFault exceptions                                                                                                                                                                                                                                                                                                                                                                                                 |

| Ownership                             | ST                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Detailed implementation               | HardFault exception raise is an intrinsic safety mechanism implemented in Arm <sup>®</sup> Cortex <sup>®</sup> -M3 core, mainly dedicated to intercept systematic faults due to software limitations or error in software design (causing for example execution of undefined operations, unaligned address access). This safety mechanism is also able to detect hardware random faults inside the <i>CPU</i> bringing to such described abnormal operations. |

| Error reporting                       | High-priority interrupt event                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Fault detection time                  | Depends on implementation. Refer to functional documentation.                                                                                                                                                                                                                                                                                                                                                                                                 |

| Addressed fault model                 | Permanent and transient                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Dependency on Device configuration    | None                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Initialization                        | None                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Periodicity                           | Continuous                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Test for the diagnostic               | It is possible to write a test procedure to verify the generation of the HardFault exception; anyway, given the expected minor contribution in terms of hardware random-failure detection, such implementation is not recommended.                                                                                                                                                                                                                            |

| Multiple-fault protection             | CPU_SM_0: periodical core self-test software                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Recommendations and known limitations | Enabling related interrupt generation on the detection of errors is highly recommended.                                                                                                                                                                                                                                                                                                                                                                       |

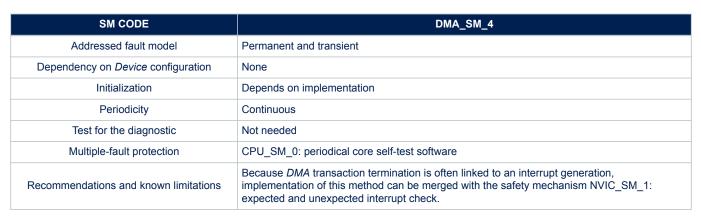

## Table 7. CPU\_SM\_4

| SM CODE                               | CPU_SM_4                                                                                                                                                                                                                                                     |

|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Description                           | Stack hardening for Application software                                                                                                                                                                                                                     |

| Ownership                             | End user                                                                                                                                                                                                                                                     |

|                                       | The stack hardening method is required to address faults (mainly transient) affecting <i>CPU</i> register bank. This method is based on source code modification, introducing information redundancy in register-passed information to called functions.     |

|                                       | The guidelines for the implementation of the method are the following:                                                                                                                                                                                       |

| Detailed implementation               | • To pass also a redundant copy of the passed parameters values (possibly inverted) and to execute a coherence check in the function.                                                                                                                        |

|                                       | • To pass also a redundant copy of the passed pointers and to execute a coherence check in the function.                                                                                                                                                     |

|                                       | • For parameters that are not protected by redundancy, to implement defensive programming techniques (plausibility check of passed values). For example enumerated fields are to be checked for consistency.                                                 |

| Error reporting                       | Depends on implementation                                                                                                                                                                                                                                    |

| Fault detection time                  | Depends on implementation                                                                                                                                                                                                                                    |

| Addressed fault model                 | Permanent and transient                                                                                                                                                                                                                                      |

| Dependency on Device configuration    | None                                                                                                                                                                                                                                                         |

| Initialization                        | Depends on implementation                                                                                                                                                                                                                                    |

| Periodicity                           | On demand                                                                                                                                                                                                                                                    |

| Test for the diagnostic               | Not needed                                                                                                                                                                                                                                                   |

| Multiple-fault protection             | CPU_SM_0: periodical core self-test software                                                                                                                                                                                                                 |

| Recommendations and known limitations | This method partially overlaps with defensive programming techniques required by IEC61508 for software development. Therefore in presence of <i>Application software</i> qualified for safety integrity greater or equal to SC2, optimizations are possible. |

## Table 8. CPU\_SM\_5

| SM CODE                               | CPU_SM_5                                                                                                                                                                                                                                                                                  |

|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Description                           | External watchdog                                                                                                                                                                                                                                                                         |

| Ownership                             | End user                                                                                                                                                                                                                                                                                  |

|                                       | Using an external watchdog linked to control flow monitoring method (refer to CPU_SM_1) addresses failure mode of program counter or control structures of <i>CPU</i> .                                                                                                                   |

| Detailed implementation               | External watchdog can be designed to be able to generate the combination of signals needed on the final system to achieve the safe state. It is recommended to carefully check the assumed requirements about system safe state reported in Section 3.3.1 Safety requirement assumptions. |

|                                       | It also contributes to dramatically reduce potential common cause failures, because the external watchdog is clocked and supplied independently of <i>Device</i> .                                                                                                                        |

| Error reporting                       | Depends on implementation                                                                                                                                                                                                                                                                 |

| Fault detection time                  | Depends on implementation (watchdog timeout interval)                                                                                                                                                                                                                                     |

| Addressed fault model                 | Permanent and transient                                                                                                                                                                                                                                                                   |

| Dependency on Device configuration    | None                                                                                                                                                                                                                                                                                      |

| Initialization                        | Depends on implementation                                                                                                                                                                                                                                                                 |

| Periodicity                           | Continuous                                                                                                                                                                                                                                                                                |

| Test for the diagnostic               | To be defined at system level (outside the scope of Compliant item analysis)                                                                                                                                                                                                              |

| Multiple-fault protection             | CPU_SM_1: control flow monitoring in Application software                                                                                                                                                                                                                                 |

| Recommendations and known limitations | In case of usage of windowed watchdog, <i>End user</i> must consider possible tolerance in <i>Application software</i> execution, to avoid false error reports (affecting system availability).                                                                                           |

|                                       | It is worth to note that the use of an external watchdog could be needed anyway when the <i>Device</i> is used to trigger final elements, in order to comply at system level with requirements from IEC61508-2:2010 Table A.1/Table A.14.                                                 |

#### Table 9. CPU\_SM\_6

| SM CODE                               | CPU_SM_6                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Description                           | Independent watchdog                                                                                                                                                                                                                                                                                                                                                                                                          |

| Ownership                             | ST                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Detailed implementation               | Using the IDWG watchdog linked to control flow monitoring method (refer to CPU_SM_1) addresses failure mode of program counter or control structures of <i>CPU</i> .                                                                                                                                                                                                                                                          |

| Error reporting                       | Reset signal generation                                                                                                                                                                                                                                                                                                                                                                                                       |

| Fault detection time                  | Depends on implementation (watchdog timeout interval)                                                                                                                                                                                                                                                                                                                                                                         |

| Addressed fault model                 | Permanent                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Dependency on Device configuration    | None                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Initialization                        | IWDG activation. It is recommended to use <i>hardware watchdog</i> in Option byte settings (IWDG is automatically enabled after reset)                                                                                                                                                                                                                                                                                        |

| Periodicity                           | Continuous                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Test for the diagnostic               | WDG_SM_1: Software test for watchdog at startup                                                                                                                                                                                                                                                                                                                                                                               |

| Multiple foult protection             | CPU_SM_1: control flow monitoring in Application software                                                                                                                                                                                                                                                                                                                                                                     |