# **TS2026L**

## **Dual-Channel Power Distribution Switch**

SOP-8

Pin assignment:

1. ENA

2. FLGA

6. GND

3. FLGB

7. IN

4. ENB 8. OUTA

140mΩ max. on-resistance per channel 2.7V to 5.5V operating range Under voltage lockout

## **General Description**

The TS2026L is high-side MOSFET switches optimized for general-purpose power distribution requiring circuit protection.

The TS2026L are internally current limited and have thermal shutdown that protects the device and load. When a thermal shutdown fault occurs, the output is latched off until the faulty load is removed. Removing that load or toggling the enable input will reset the device output. Both device employ soft-start circuitry that minimized inrush current in application where highly capacitive loads are employed. A fault status output flag is asserted during over current and thermal shutdown conditions. Transient faults are internally filtered.

#### **Features**

- $\Rightarrow$  140mΩ max. on-resistance per channel

- ♦ 2.7V to 5.5V operating range

- ♦ 500mA min. continuous current per channel

- ♦ Short-circuit protection with thermal shutdown

- ♦ Thermal isolated channels.

- Fault status flag with 3ms filter eliminates false assertions.

- ♦ Under voltage lockout

- Reverse current flow blocking (no "body diode")

- ♦ Logic-compatible inputs

- ♦ Soft-start circuit

- Low quiescent current

# **Applications**

- ♦ USB peripherals

- ♦ General purpose power switching

- ♦ ACPI power distribution

- ♦ Notebook PCs

- ♦ PDAsPC

- ♦ Card hot swap

## **Ordering Information**

| Part No.  | Operating Temp.<br>(Ambient) | Package |  |

|-----------|------------------------------|---------|--|

| TS2026LCS | -40 ~ +85 °C                 | SOP-8   |  |

## **Absolute Maximum Rating**

| Supply Voltage      | V <sub>IN</sub>  | +6               | V  |

|---------------------|------------------|------------------|----|

| Fault Flag Voltage  | $V_{FLG}$        | +6               | V  |

| Fault Flag Current  | I <sub>FLG</sub> | 25               | mA |

| Output Voltage      | V <sub>OUT</sub> | +6               | °C |

| Output Current      | I <sub>OUT</sub> | Internal Limited |    |

| Enable input        | I <sub>EN</sub>  | -0.3 ~ +3        | V  |

| Storage Temperature | T <sub>STG</sub> | -65 ~ +150       | °C |

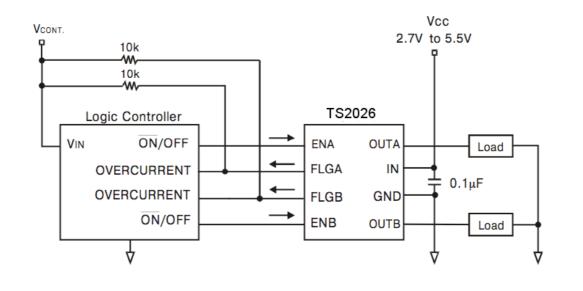

# **Typical Application**

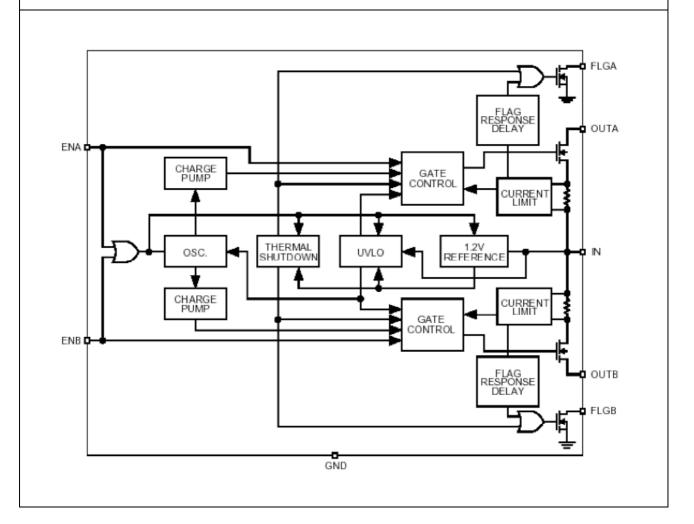

# **Block Diagram**

#### **Electrical Characteristics**

Vin=5V, T<sub>A</sub> = 25 °C, unless noted

| Parameter                        | Parameter Symbol Condition                     |                                                                                          | Min. | Тур.  | Max. | Units |

|----------------------------------|------------------------------------------------|------------------------------------------------------------------------------------------|------|-------|------|-------|

| Overally Overand                 |                                                | V <sub>ENA</sub> =V <sub>ENB</sub> ≥2.4V (switch off),<br>OUT = open                     |      | 0.75  | 5    | uA    |

| Supply Current                   | I <sub>DD</sub>                                | V <sub>ENA</sub> =V <sub>ENB</sub> ≤0.8V (switch on),<br>OUT = open                      |      | 100   | 160  | uA    |

| For able to most them also also  | V <sub>EN</sub>                                | Low-to-high transition                                                                   |      | 1.7   | 2.4  | V     |

| Enable Input threshold           |                                                | High-to-low transition                                                                   | 0.8  | 1.455 | -    | V     |

| Enable Input Hysteresis          |                                                |                                                                                          |      | 250   |      | mV    |

| Enable Input Current             | - I <sub>EN</sub>                              | V <sub>ENA</sub> = 0V to 5.5V                                                            | -1   | 0.01  | 1    | uA    |

| Enable Input Capacitance         |                                                |                                                                                          |      | 1     |      | pF    |

| 0.11.5                           |                                                | V <sub>IN</sub> = 5V, I <sub>OUT</sub> = 500mA                                           |      | 90    | 140  | mΩ    |

| Switch Resistance Note 4         | R <sub>DS(ON)</sub>                            | V <sub>IN</sub> = 3.3V, I <sub>OUT</sub> = 500mA                                         |      | 100   | 160  | mΩ    |

| Output Leakage Current           |                                                | V <sub>ENX</sub> ≤0.8V or V <sub>ENX</sub> ≥2.4V                                         |      |       | 10   | uA    |

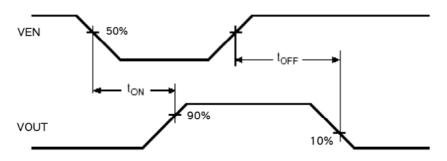

| Output Turn-on Delay             | ton                                            |                                                                                          |      | 1.3   | 5    | mS    |

| Output Turn-on Rise Time         | urn-on Rise Time $t_R$ $R_L=10\Omega, C_L=1F,$ |                                                                                          |      | 1.15  | 4.9  | mS    |

| Output Turn-off Delay            | t <sub>OFF</sub>                               | t <sub>OFF</sub> see "Timing Diagrams"                                                   |      | 35    | 100  | uS    |

| Output Turn-off Fall Time        | t <sub>F</sub>                                 |                                                                                          |      | 32    | 100  | uS    |

| Short-Circuit Output Current     | I <sub>LIMIT</sub>                             | V <sub>OUT</sub> = 0V, enable into short-circuit                                         | 0.5  | 0.9   | 1.25 | Α     |

| Current –Limit Threshold         |                                                | Ramped load applied to output                                                            |      | 1.0   | 1.25 | Α     |

| Short-Circuit Response Time      |                                                | V <sub>OUT</sub> = 0V to I <sub>OUT</sub> = I <sub>LIMIT</sub> (short applied to output) |      | 20    |      | uS    |

| 0 15 5                           |                                                | V <sub>IN</sub> =5V, apply V <sub>OUT</sub> =0V, Until FLG low                           | 1.5  | 3     | 7    | mS    |

| Over current Flag Response Delay | t <sub>D</sub>                                 | $V_{\text{IN}}$ =3.3V, apply $V_{\text{OUT}}$ =0V, Until FLG low                         |      | 3     |      | mS    |

| Under voltage Lockout            |                                                | V <sub>IN</sub> rising                                                                   | 2.2  | 2.4   | 2.7  | V     |

| Threshold                        |                                                | V <sub>IN</sub> falling                                                                  | 2.0  | 2.15  | 2.5  | V     |

| Francisco Outrout Desistance     |                                                | I <sub>L</sub> =10mA, V <sub>IN</sub> =5V                                                |      | 10    | 25   | Ω     |

| Error Flag Output Resistance     |                                                | I <sub>L</sub> =10mA, V <sub>IN</sub> =3.3V                                              |      | 15    | 40   | Ω     |

| Error Flag Off Current           |                                                | V <sub>FLAG</sub> =5V                                                                    |      |       | 10   | uA    |

|                                  |                                                | T <sub>J</sub> increasing, each switch                                                   |      | 140   |      | °C    |

| Over temperature Threshold       |                                                | T <sub>J</sub> decreasing, each switch                                                   |      | 120   |      | °C    |

| Note 5                           |                                                | T <sub>J</sub> increasing, both switch                                                   |      | 160   |      | °C    |

|                                  |                                                | T <sub>J</sub> decreasing, both switch                                                   |      | 150   |      | °C    |

Note 1. Exceeding the absolute maximum rating may damage the device.

TS2026L 3-7 2005/11 rev. A

Note 2. The device is not guaranteed to function outside its operating rating.

Note 3. Devices are ESD sensitive. Handing precautions recommended.

Note 4. For maintenance  $R_{DS} \le 140 m\Omega$  assembly to make gold conductors in diameter 50m.

Note 5. If there is a fault on one channel, that channel will shut down when the die reaches approximately 140 °C. If the die reaches approximately 160 °C, both channels will shut down, even if neither channel is in current limit.

| Pin Description |      |                                                                                                                                                                                          |  |  |

|-----------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin             | Name | Description                                                                                                                                                                              |  |  |

| 1               | ENA  | Switch A Enable (Input): Logic-compatible enable input. active low (L)                                                                                                                   |  |  |

| 2               | FLGA | Fault Flag A (Output): Active-low, open-drain output. Indicated over current or thermal shutdown conditions. Over current conditions mush last longer than $t_D$ in order to assert FLGA |  |  |

| 3               | FLGB | Fault Flag B (Output): Active-low, open-drain output. Indicated over current or thermal shutdown conditions. Over current conditions mush last longer than $t_D$ in order to assert FLGB |  |  |

| 4               | ENB  | Switch B Enable (Input): Logic-compatible enable input. active-low (L)                                                                                                                   |  |  |

| 5               | OUTB | Switch B (Output)                                                                                                                                                                        |  |  |

| 6               | GND  | Ground                                                                                                                                                                                   |  |  |

| 7               | IN   | Input: Switch and logic supply input                                                                                                                                                     |  |  |

| 8               | OUTA | Switch A (Output)                                                                                                                                                                        |  |  |

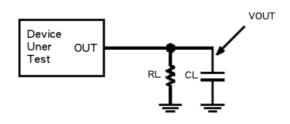

# **Test Circuit**

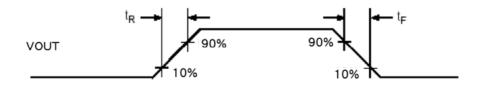

# Timing Diagram

# **Output Rise and Fall Time**

**Active-Low Switch Times**

TS2026L 4-7 2005/11 rev. A

#### **Function Description**

#### **Input and Output**

IN is the power supply connection to the logic circuitry and the drain of the output MOSFET. OUT is the source of the output MOSFET. In a typical circuit, current flows from IN to OUT toward the load. If  $V_{OUT}$  is greater than  $V_{IN}$ , current will flow from OUT to IN, since the switch is bidirectional when enabled. The output MOSFET and driver circuitry are also designed to allow the MOSFET source to be externally forced to a higher voltage than the drain  $(V_{OUT} > V_{IN})$  when the switch is disabled. In this situation, the TS2026 prevents undesirable current flow from OUT to IN.

#### **Thermal Shutdown**

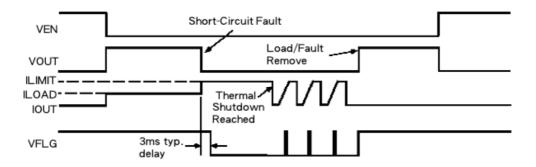

Thermal shutdown is employed to protect the device from damage should the die temperature exceed safe margins due mainly to short circuit faults. Each channel employs its own thermal sensor. Thermal shutdown shuts off the output MOSFET and asserts the FLG output if the die temperature reaches 140 °C and the overheated channel is in current limit. The over channel will be shut off. Upon determining a thermal shutdown condition. The TS2026 will automatically reset its output when the die temperature cools down to 120 °C . The TS2026 output and FLG signal will continue to cycle on and off until the device is disabled or the fault is removed. Figure 1. Depicts typical timing. Depending on PCB layout, package, ambient temperature, etc., it may take several hundred milliseconds from the incidence of the fault to the output MOSFET being shut off. This time will be shortest in the case of dead short on the output.

#### **Power Dissipation**

The device's junction temperature depends on several factors such as the load, PCB layout, ambient temperature and package type. Equations that can be used to calculate power dissipation of each channel and junction temperature are found below.

$$P_D = R_{DS(ON)} x I_{OUT}^2$$

Total power dissipation of the device will be the summation of PD for both channels. To relate this to junction temperature, the following equation can be used:

$$T_J = P_D \times \theta_{JA} + T_A$$

Where:

$T_J$  = junction temperature

$T_A$  = ambient temperature

$\theta_{JA}$  = is the thermal resistance of the package

#### **Current Sensing and Limiting**

The current-limit threshold is preset internally. The preset level prevents damage to the device and external load but still allows a minimum current of 500mA to be delivered to the load. The current-limit circuit senses a portion of the output MOSFET switch current. The current-sense resistor shown in the block diagram is virtual and has no voltage drop. The reaction to an over current condition varies with three scenarios.

#### **Switch Enable into Short-Circuit**

If a switch is enabled into a heavy load or short-circuit, the switch immediately enters into a constant-current mode, reducing the output voltage. The FLG signal is asserted indicating an over current condition.

#### Switch Enable Applied to Enabled Output

When a heavy load or short-circuit is applied to an enabled switch, a large transient current may flow until the current limit circuitry responds. Once this occurs the device limits current to less than the short circuit current limit specification.

#### **Current-Limit Response-Ramped Load**

The TS2026 current-limit profile exhibits a small fold back effect of about 200mA. Once this current-limit threshold is exceeded the device switches into a constant current mode. It is important to note that the device will supply current up to the current-limit threshold

TS2026L 5-7 2005/11 rev. A

## **Function Description**

#### **Fault Flag**

The FLG signal is an N-channel open-drain MOSFET output. FLG is asserted (active-low) when either an over current or thermal shutdown condition occurs. In the case of and over current condition, FLG will be asserted only after the flag response delay time,  $t_D$ , has elapsed. This ensured that FLG is asserted only upon valid over current conditions and that erroneous error reporting is eliminated. For example, false over current condition can occur during hot plug event when a highly capacitive load is connected and causes a high transient inrush current that exceeds the current-limit threshold for up to 1ms. The FLG response delay time  $t_D$  is typically 3ms.

#### **Undervoltage Lockout**

Undervoltage lockout (UVLO) prevents the output MOSFET from turning on until VIN exceeds approximately 2.5V. Undervoltage detection function only when the switch is enabled.

Figure 1. TS2026L Fault Timing

TS2026L 6-7 2005/11 rev. A

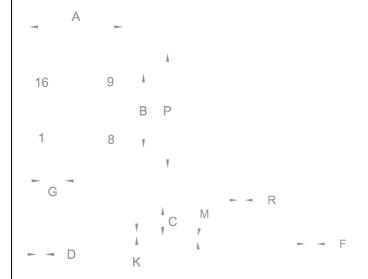

# **SOP-8 Mechanical Drawing**

| SOP-8 DIMENSION |             |      |                       |       |  |

|-----------------|-------------|------|-----------------------|-------|--|

| DIM             | MILLIMETERS |      | INCHES                |       |  |

|                 | MIN         | MAX  | MIN                   | MAX   |  |

| Α               | 4.80        | 5.00 | 0.189                 | 0.196 |  |

| В               | 3.80        | 4.00 | 0.150                 | 0.157 |  |

| С               | 1.35        | 1.75 | 0.054                 | 0.068 |  |

| D               | 0.35        | 0.49 | 0.014                 | 0.019 |  |

| F               | 0.40        | 1.25 | 0.016                 | 0.049 |  |

| G               | 1.27 (typ)  |      | 1.27 (typ) 0.05 (typ) |       |  |

| K               | 0.10        | 0.25 | 0.004                 | 0.009 |  |

| М               | 0°          | 7°   | 0°                    | 7°    |  |

| Р               | 5.80        | 6.20 | 0.229                 | 0.244 |  |

| R               | 0.25        | 0.50 | 0.010                 | 0.019 |  |

|                 |             |      |                       |       |  |

TS2026L 7-7 2005/11 rev. A