SRFS001F - D3864, DECEMBER 1989 - REVISED FEBRUARY 1993

- Four Arrays With up to 2000 Usable Equivalent Gates

- TI Action Logic™ System (TI-ALS) Software for:

- ViewLogic™

- Mentor™

- OrCAD/SDT III ™

- Cadence™/Valid™

- Reliable Antifuse Interconnect

- Built-In Clock Distribution Network

- Silicon-Gate CMOS Technology

- Desktop Ti-ALS Creates Design Files for:

- I/O Pin Assignment

- Design Validation

- Place and Route

- Circuit Timing Analysis

- Array Antifuse Programming

- Test and Debug

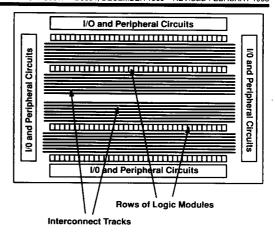

**TPC10 Series FPGA Die Architecture**

### description

The Texas Instruments (TI) TPC10 Series comprises four field-programmable gate arrays (FPGAs). The TPC1010A, TPC1010B, TPC1020A, and TPC1020B FPGAs are fabricated using the TI silicon-gate CMOS process. The process features polysilicon gate, source, drain elements, and two levels of copper-doped-aluminum metallization to reduce internal resistance and enhance performance. Typical die architecture is illustrated above.

These field-programmable devices combine gate-array flexibility with desktop programmability. This combination allows the designer to avoid fabrication cycle times and nonrecurring engineering charges associated with conventional mask-programmed gate arrays. The FPGAs are unique in that the arrays are fabricated, tested, and shipped to the user for programming. The FPGA contains user-configurable inputs, outputs, logic modules, and minimum-skew clock driver with hardwired distribution network. The FPGA also includes on-chip diagnostic probe capabilities and security fuses to protect the proprietary design.

**Table 1. Product Family Profile**

| DEVICE                      | TPC1010A | TPC1020A | TPC1010B | TPC1020B |

|-----------------------------|----------|----------|----------|----------|

| Capacity                    |          |          |          |          |

| Gate array equivalent gates | 1200     | 2000     | 1200     | 2000     |

| TTL equivalent packages     | 34       | 53       | 34       | 5,3 (    |

| CMOS Process                | 1.2 μm   | 1.2 μm   | 1.0 μm   | 1.0 µm   |

| Logic Modules               | 295      | 547      | 295      | 547      |

| Flip-Flops (maximum)        | 130      | 273      | 130      | 273      |

| Antifuses                   | 112,000  | 186,000  | 112,000  | 186,000  |

| Horizontal Tracks           | 22       | 22       | 22       | 22       |

| Vertical Tracks             | 13       | 13       | 13       | 13       |

Action Logic, Activator, and Actionprobe are trademarks of ACTEL Corporation. Cadence/Valid are trademarks of Cadence Design Systems, Inc. Mentor is a trademark of Mentor Graphics Corporation. OrCAD/SDT III is a trademark of OrCad Systems Corporation. ViewLogic is a trademark of Viewlogic System, Incorporated.

UNLESS OTHERWISE NOTED this document contains PRODUCTION DATA information current as of publication date. Products conform specifications per the terms of lexas instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright © 1993, Texas Instruments Incorporated

### **Action Logic System (ALS) and Activator**

TPC10 Series FPGAs are supported by the ALS software and Activator™ programming hardware. The combination facilitates logic design and FPGA programming on popular CAE workstations with minimum effort. ALS interfaces to the resident CAE system providing a complete library of TPC10 Series functions. The ALS includes automatic place and route, timing verification, and FPGA device programming. The ALS and Activator are available for View*Logic* or OrCAD (SDT III) 386/486 based PC systems, Mentor-equipped Apollo workstations, and View*Logic*- or Valid/Cadence-equipped Sun-4 workstations.

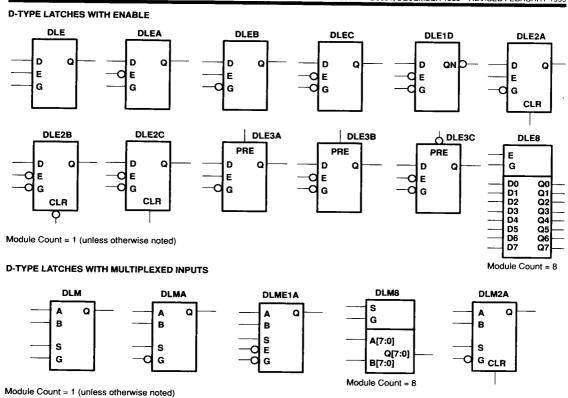

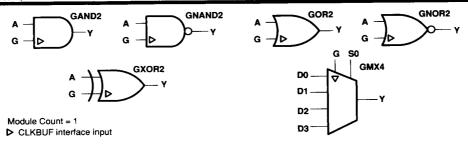

## library functions

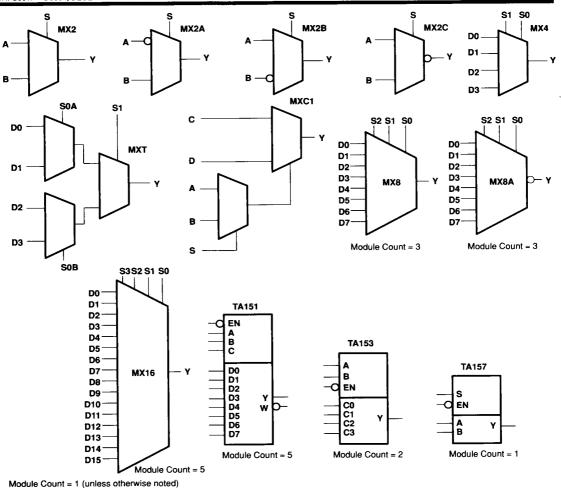

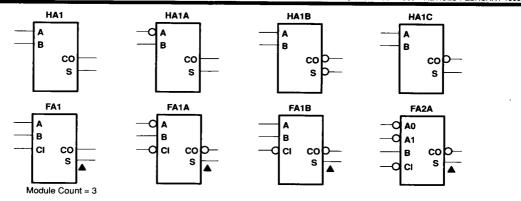

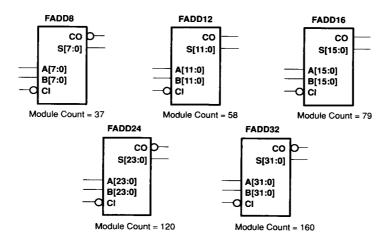

The TPC10 Series FPGA library contains over 250 logic building blocks of hardwired and soft macros. The hardwired macros provide a wide selection of predesigned, fully characterized functions. The soft macros provide popular MSI functions that can be called into the design. Additional user-defined soft macros can be created using the TPC10 library macros. The library contains the following classes of macros:

- Primitive Gates, Booleans, and Buffers

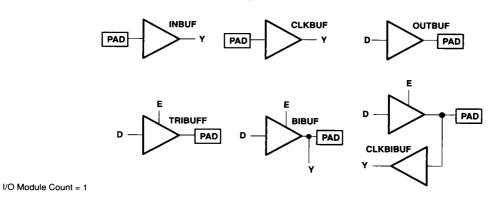

- CMOS, TTL, and Clock Buffer Inputs and Totem-Pole, 3-State, and I/O Output Buffers

- Adders and Multiplexers

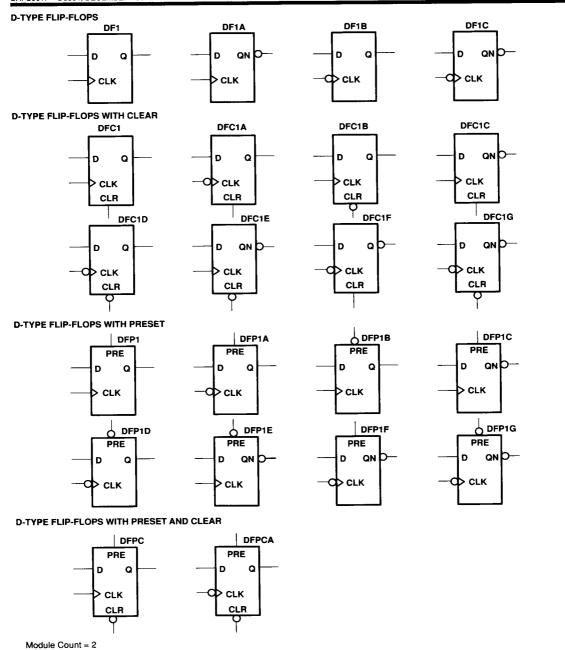

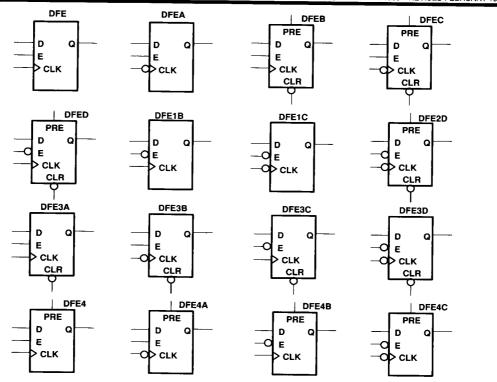

- D-Type Flip-Flops

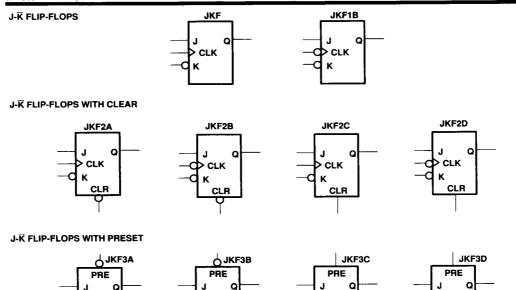

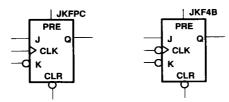

- J-K Flip-Flops

- Latches

- MSI Complexity Soft Macros

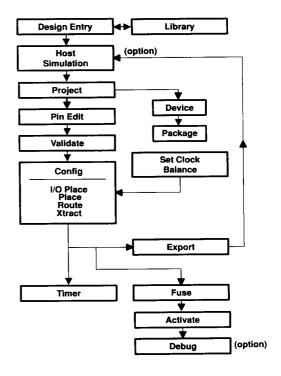

## design flow

Custom logic functions, designed in conjunction with the TPC10 Series FPGA library, can be simulated and verified prior to creating the ALS design data base and programming files. Figure 1 provides an overview of the design flow.

Figure 1. Design Flow

SRFS001F - D3864, DECEMBER 1989 - REVISED FEBRUARY 1993

Table 2. TI-ALS Design Configurations (see Note 1)

| HARDWARE            | LIBRARY/CAE HOST  | DESIGN SUF | PPORT (gates) | TI SUSTEM                |

|---------------------|-------------------|------------|---------------|--------------------------|

| PLATFORM            | ENVIRONMENT       | UP TO 2500 | UP TO 10000   | PART NUMBER              |

|                     | View <i>Logic</i> | X          |               | TPC-ALS-DS-PC-VL         |

| 386/486-based<br>PC | View <i>Logic</i> |            | х             | TPC-ALS-DA-PC-VL         |

|                     | OrCAD             | Х          |               | TPC-ALS-DS-PC-OR         |

|                     | OrCAD             |            | х             | TPC-ALS-DA-PC-OR         |

|                     | Cadence           |            | X             | TPC-ALS-DA-SN-CD         |

| Sun                 | Mentor            |            | X             | TPC-ALS-DA-SN-MG         |

| Gan                 | Valid             |            | X             | TPC-ALS-245 <sup>†</sup> |

|                     | View <i>Logic</i> |            | X             | TPC-ALS-DA-SN-VL         |

| HP700               |                   |            |               | TPC-ALS-DA-HP7-MG        |

| DN4000/<br>HP400    | Mentor            |            | ×             | TPC-ALS-235†             |

NOTE 1: Authorization codes for design systems are supplied upon request, after receipt of the system.

Table 3. TI-ALS Programming Configurations (see Note 2)

| HARDWARE                                       | CAE HOST                 | DESIGN     | SUPPORT           | TI SUSTEM          |

|------------------------------------------------|--------------------------|------------|-------------------|--------------------|

| PLATFORM                                       | ENVIRONMENT              | ONE DEVICE | FOUR DEVICES      | PART NUMBER        |

| 386/486-based<br>PC                            | View <i>Logic</i> /OrCAD | Х          |                   | TPC-ALS-DS-P2S-PC  |

|                                                | VIEW LOGIC / CICAD       |            | X                 | TPC-ALS-219        |

| Sun Cadence/Mentor/<br>Valid/View <i>Logic</i> | X                        |            | TPC-ALS-DS-P2S-SN |                    |

|                                                | Valid/ViewLogic          |            | Х                 | TPC-ALS-249        |

| HP700                                          | Mentor                   | X          |                   | TPC-ALS-DS-P2S-HP7 |

|                                                |                          |            | X                 | TPC-ALS-DS-P2-HP7  |

| HP400                                          | Mentor                   | X          |                   | TPC-ALS-DS-P2S-HP4 |

|                                                | Wertto                   |            | Х                 | TPC-ALS-DS-P2-HP4  |

| DN Series                                      | Mentor                   |            | X                 | TPC-ALS-239        |

NOTE 2: Programming units are compatible with both high (10000 gates) and low (2500 gates) density systems.

<sup>†</sup> The TPC-ALS-235 and TPC-ALS-245 systems only provide support for the TPC10 and TPC12 series, and will not be supported in Revision 3.0 scheduled for release in the fourth quarter of 1993. These systems are being replaced by TPC-ALS-DA-HP7-MG and TPC-ALS-DA-SN-CD, respectively.

#### architecture

#### device organization

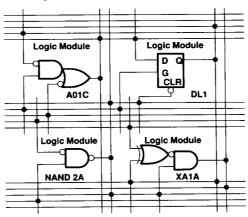

Each FPGA consists of a matrix of logic modules arranged in rows separated by channels containing interconnect tracks. The matrix is surrounded with peripheral inputs, outputs, I/Os, and diagnostic circuits. A partial view of the TPC10 Series logic modules with examples of interconnections is illustrated in Figure 2.

Figure 2. Partial View of TPC10 Series Interconnection Capability

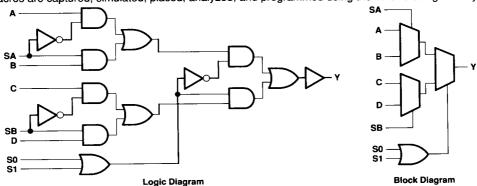

### logic module

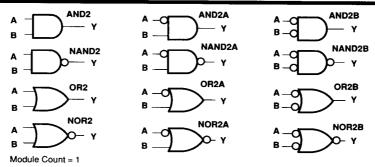

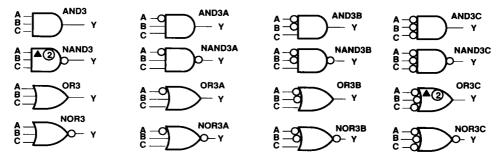

Each core logic module has the equivalent complexity of four 2-input NAND gates. The module shown in Figure 3, is an 8-input, 1-output gate cluster that can implement hardwired primitive gates, Booleans, latches, flip-flops, multiplexers, half or full adder slices, or multiplexed-input flip-flops. The TI-ALS library contains a full spectrum of 2-, 3-, and 4-input AND, NAND, OR, and NOR gate macros covering all derivatives of true and/or complement input combinations. Similar modular implementations, covering the spectrum of true and/or complement input combinations, are included for each functional category of macros in the library. Latches and flip-flops are created by connecting two or more logic modules in the appropriate circuit configuration. The macros are captured, simulated, placed, analyzed, and programmed using the TPC10 design library.

Figure 3. TPC10 Series Logic Module

SRFS001F - D3864, DECEMBER 1989 - REVISED FEBRUARY 1993

#### interconnect tracks

The channeled interconnect tracks consist of isolated metal segments that can be connected by addressing and programming antifuses. Each channel has 25 horizontal routing tracks, 22 are for logic, one is for clock, one is for power, and one is for ground. In addition, there are 13 vertical routing tracks per logic module column. Both horizontal and vertical tracks, in combination with the approximately 340 antifuses per logic module, produce a network that is capable of interconnecting up to 90 percent of the equivalent gates. Based on the placement of macros, the programming process selects and activates antifuses that both create the logic module macros and I/Os, and interconnect the entire array.

#### I/O buffers

Each I/O pin is configurable as an input or an output. In addition, I/O pins configured as outputs can be defined as totem-pole, 3-state, or bidirectional. Inputs can be driven by CMOS or TTL levels and output levels are compatible with standard CMOS and TTL specifications. Outputs sink or source a current of 4 mA at TTL output levels. See the dc characteristics for additional I/O buffer specifications. The I/Os can be manually assigned to any available package pin, or the ALS software can automatically place the I/Os in the optimum configuration.

### diagnostic probe pins

TPC10 Series devices have two independent diagnostic probe pins, PRA and PRB. The pins allow the user to observe any internal signals by entering the appropriate net name in the diagnostic software. Signals may be viewed on an oscilloscope, logic analyzer, or with the workstation diagnostics using the Actionprobe diagnostic tools. The probe pins can also be used as user-defined I/Os, depending on the level of the mode control pin. When configured as user-defined I/Os, the pins have the same characteristics as other I/O pins.

#### security fuses

The TPC10 Series security fuses can be used to permanently disable further diagnostics and testing. After the security fuses are programmed, access to the architecture is not available. This makes the FPGA design difficult to copy.

SRFS001F - D3864, DECEMBER 1989 - REVISED FEBRUARY 1993

### FPGA array performance

## logic module size

A mask-programmed gate array cell with four transistors usually implements only one logic level. The TPC10 Series array logic module is more complex and typically implements multiple logic levels within a single module. This reduces intermodule wiring and associated RC delays. In effect, the TPC10 logic module implements the equivalent of a net compression that enhances performance.

#### **TERMINAL FUNCTIONS**

| PIN<br>NAME | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK         |     | Clock. TTL clock input for global clock distribution network. The clock input is buffered prior to clocking the logic modules. This pin can also be used as an I/O.                                                                                                                                                                                                                                                                                                                                                                                           |

| DCLK        | I   | Diagnostic clock. TTL clock input for diagnostic probe and device programming. DCLK is active when the MODE pin is high. This pin functions as an I/O when the MODE pin is low.                                                                                                                                                                                                                                                                                                                                                                               |

| GND         | T   | Ground. Input low supply voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| I/O         | 1/0 | Input/output. I/O pin functions as an input, output, 3-state, or bidirectional buffer. Input and output levels are compatible with standard TTL and CMOS specifications. Unused I/O pins are automatically set low by the ALS software.                                                                                                                                                                                                                                                                                                                       |

| MODE        | 1   | Mode. The MODE pin controls the use of multifunction pins (DCLK, PRA, PRB, SDI). When the MODE pin is high, the special functions are active. When the MODE pin is low, the pins function as I/Os.                                                                                                                                                                                                                                                                                                                                                            |

| NC          |     | No connection. This pin is not connected to circuitry within the device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| PRA         | 0   | Probe A. The probe A pin is used to output data from any user-defined design node within the device. This independent diagnostic pin is used in conjunction with the probe B pin to allow real-time diagnostic output of any signal path within the device. The probe A pin can be used as a user-defined I/O when debugging has been completed. The pin's probe capabilities can be permanently disabled to protect the programmed design's confidentiality. PRA is active when the MODE pin is high. This pin functions as an I/O when the MODE pin is low. |

| PRB         | 0   | Probe B. The probe B pin is used to output data from any user-defined design node within the device. This independent diagnostic pin is used in conjunction with the probe A pin to allow real-time diagnostic output of any signal path within the device. The probe B pin can be used as a user-defined I/O when debugging has been completed. The pin's probe capabilities can be permanently disabled to protect the programmed design's confidentiality. PRB is active when the MODE pin is high. This pin functions as an I/O when the MODE pin is low. |

| SDI         | ı   | Serial data input. Serial data input for diagnostic probe and device programming. SDI is active when the MODE pin is high. This pin functions as an I/O when the MODE pin is low.                                                                                                                                                                                                                                                                                                                                                                             |

| Vcc         | 1   | Supply voltage. Input high supply voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| VPP         | I   | Programming voltage. Input supply voltage used for device programming. This pin must be connected to V <sub>CC</sub> during normal operation.                                                                                                                                                                                                                                                                                                                                                                                                                 |

SRFS001F - D3864, DECEMBER 1989 - REVISED FEBRUARY 1993

# absolute maximum ratings over operating free-air temperature range (unless otherwise noted)†

|                                                                      | •                                             |

|----------------------------------------------------------------------|-----------------------------------------------|

| Supply voltage range , V <sub>CC</sub>                               | – 0.5 V to 7 V                                |

| Input voltage range, V <sub>I</sub>                                  | $-0.5$ to $V_{CC} + 0.5$ V                    |

| Output voltage range, VO                                             | $-0.5 \text{ to V}_{CC} + 0.5 \text{ V}_{CC}$ |

| Input clamp current $\mp$ , $I_{1K}$ ( $V_1 < 0$ or $V_1 > V_{CC}$ ) | + 20 mA                                       |

| Output clamp currents, $I_{OK}$ ( $V_{O} < 0$ or $V_{O} > V_{CC}$ )  | + 20 mA                                       |

| Continuous output current\$, (VO = 0 to VCC)                         | + 25 mA                                       |

| Operating free-air temperature range, TA: Commercial                 | 0°C to 70°C                                   |

| Industrial                                                           |                                               |

| Operating case temperature range, T <sub>C</sub> : Military          | – 55°C to 125°C                               |

| Storage temperature range                                            | - 65°C to 150°C                               |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## recommended operating conditions

|                |                                                |            | MIN  | NOM | MAX                  | UNIT |

|----------------|------------------------------------------------|------------|------|-----|----------------------|------|

|                |                                                | Commercial | 4.75 | 5   | 5.25                 |      |

| $v_{CC}$       | Supply voltage                                 | Industrial | 4.5  | 5   | 5.5                  | ٧    |

|                | PP Program pin voltage (while not programming) | Military   | 4.5  | 5   | 5.5                  |      |

| VPP            |                                                |            | Vcc  |     | Vcc                  | V    |

| $v_{IH}$       | High-level input voltage                       |            | 2    |     | V <sub>CC</sub> +0.3 | V    |

| VIL            | Low-level input voltage                        |            | -0.3 |     | 0.8                  | ٧    |

| TA             | Operating free-air temperature                 | Commercial | 0    | 25  | 70                   |      |

| ·^             | oporating troo at temperature                  | Industrial | -40  | 25  | 85                   | °C   |

| T <sub>C</sub> | Operating case temperature                     | Military   | -55  | 25  | 125                  | °C   |

<sup>‡</sup> Applies for input and bidirectional buffers

<sup>§</sup> Applies for bidirectional and output buffers

SRFS001F - D3864, DECEMBER 1989 - REVISED FEBRUARY 1993

# electrical characteristics over full ranges of recommended operating conditions (unless otherwise noted)

|                |                                       | TEST                                                   | C    | SUFFIX | (    | - 1 | SUFFIX |      | N   | SUFFIX |      | UNIT   |

|----------------|---------------------------------------|--------------------------------------------------------|------|--------|------|-----|--------|------|-----|--------|------|--------|

| ]              | PARAMETER                             | CONDITIONS                                             | MIN  | TYP    | MAX  | MIN | TYP    | MAX  | MIN | TYPT   | MAX  | UNII   |

|                | High-level output voltage             | IOH = -4 mA                                            | 3.84 |        |      |     |        |      |     |        |      | v      |

| VOH            | (see Note 3)                          | I <sub>OH</sub> = -3.2 mA                              |      |        |      | 3.7 |        |      | 3.7 |        |      |        |

| VOL            | Low-level output voltage (see Note 3) | i <sub>OL</sub> = 4 mA                                 |      |        | 0.33 |     |        | 0.4  |     |        | 0.4  | ٧      |

| I <sub>I</sub> | Input current                         | V <sub>1</sub> = V <sub>CC</sub> or 0                  |      |        | ±10  |     |        | ±10  |     |        | ±10  | μΑ     |

| loz            | Off-state output current              | VO = VCC or 0                                          |      |        | ±10  |     |        | ±10  |     |        | ±10  | μA     |

|                | Short-circuit output                  | VO = VCC                                               | 20   |        | 140  | 20  |        | 140  | 20  |        | 140  | mA     |

| los            | current (see Note 4)                  | VO = 0                                                 | -10  |        | -100 | -10 |        | -100 | -10 |        | -100 | 1117-1 |

| lcc            | Standby supply current                | V <sub>I</sub> = V <sub>CC</sub> or 0,<br>Outputs open |      | 3      | 10   |     | 3      | 20   |     | 3      | 25   | mA     |

| Cio            | Input/output capacitance (see Note 5) | V <sub>O</sub> = 0,<br>f = 1 MHz                       |      | 7      |      |     | 7      |      |     | 7      |      | рF     |

<sup>†</sup> Typical values are at  $V_{CC} = 5 \text{ V}$ ,  $T_A = 25^{\circ}\text{C}$ .

NOTES: 3. These limits apply when all other outputs are open.

- When testing TPC1010A and TPC1020A, not more than one output should be shorted at a time, and duration of the short circuit should not exceed one second. The los parameter does not apply to TPC1010B or TPC1020B.

- 5. These limits apply for each user I/O pin.

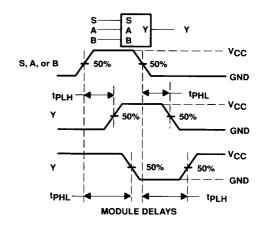

### switching characteristics

The following tables summarize switching characteristics of various classes of TPC10 Series logic module hardwired macros. An unloaded logic module propagation delay time is 4 ns. All other delays shown include the module delay time and statistical estimates for wiring delays based on 85% to 95% FPGA logic module utilization. Module utilization above 95% can result in performance degradation. Actual delay values are determined after place and route is accomplished using the ALS. ALS provides for assigning criticality to nets, automatic balancing of clock buffer loads, and utilizing long horizontal or vertical nets for connecting noncritical functions. For specific timing parameters pertaining to a hardwired logic module, refer to the individual macro library specification.

The ALS provides a capability to assign one of four levels of criticality to logic module output nets. The switching characteristics reflect the delay time differences for nets with criticality and without criticality assigned. Nets assigned as critical will be limited to a fan-out of 6 loads by the ALS. Clock load balancing, selectable by the designer, can be specified as moderate, strong, or very strong to control clock skew.

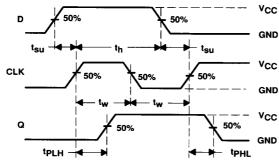

# timing requirements over recommended operating conditions, no further derating required

|                    |                               |                                                |         | MIN | MAX | UNIT |  |

|--------------------|-------------------------------|------------------------------------------------|---------|-----|-----|------|--|

| <sup>f</sup> clock | Clock frequency               | ck frequency                                   |         |     |     |      |  |

|                    |                               |                                                | FO = 1  | 7.7 |     |      |  |

|                    |                               |                                                | FO = 2  | 8.5 |     |      |  |

| t <sub>w</sub>     | Pulse duration                | CLK, PRE, or CLR                               | FO = 3  | 9.2 |     | ns   |  |

|                    |                               |                                                | FO = 4  | 10  |     |      |  |

|                    |                               |                                                | FO = 8  | 14  |     |      |  |

| t <sub>su</sub>    | Setup time, flip-flop         | All synchronous inputs before clock tran       | nsition | 3.9 |     | ns   |  |

|                    |                               |                                                | FO = 1  | 3.5 |     |      |  |

|                    |                               | <b></b>                                        | FO = 2  | 3.9 | -   |      |  |

| t <sub>su</sub>    | Setup time, latch             | All synchronous inputs before clock transition | FO = 3  | 4.2 |     | ns   |  |

|                    |                               | transition                                     | FO = 4  | 4.5 |     |      |  |

|                    |                               |                                                | FO = 8  | 4.8 |     |      |  |

| th                 | Hold time, flip-flop or latch | All synchronous inputs after clock trans       | ition   | 0   |     | ns   |  |

### typical switching characteristics

# single-level logic module hardwired macro (module count = 1) , $V_{CC}$ = 5 V, $T_J$ = 25°C, typical process

| PARAMETER       | OUTPUT-NET CRITICALITY | DELAY TIME (see Note 6) |        |        |        |            |      |  |

|-----------------|------------------------|-------------------------|--------|--------|--------|------------|------|--|

|                 | OUTFUT-NET CHITICALITY | FO = 1                  | FO = 2 | FO = 3 | FO = 4 | FO = 8     | UNIT |  |

| t <sub>pd</sub> | Critical               | 5.4                     | 5.8    | 6.2    | 8.5    | See Note 7 | ns   |  |

| <sup>t</sup> pd | Not critical           | 6.3                     | 6.7    | 7.7    | 8.6    | 10.8       | ns   |  |

# double-level logic module hardwired macro (module count = 2) , $V_{CC}$ = 5 V, $T_J$ = 25°C, typical process

| PARAMETER       | OUTPUT-NET CRITICALITY | DELAY TIME (see Note 6) |        |        |        |            |      |  |

|-----------------|------------------------|-------------------------|--------|--------|--------|------------|------|--|

|                 |                        | FO = 1                  | FO = 2 | FO = 3 | FO = 4 | FO = 8     | UNIT |  |

| <sup>t</sup> pd | Critical               | 9.2                     | 9.6    | 10     | 12.3   | See Note 7 | ns   |  |

| <sup>t</sup> pd | Not critical           | 10.2                    | 10.6   | 11.6   | 12.5   | 14.6       | ns   |  |

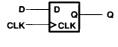

### flip-flop and latch hardwired macro, V<sub>CC</sub> = 5 V, T<sub>J</sub> = 25°C, typical process

| PARAMETER       | OUTPUT-NET CRITICALITY | DELAY TIME (see Note 6) |        |        |        |            |      |  |

|-----------------|------------------------|-------------------------|--------|--------|--------|------------|------|--|

|                 |                        | FO = 1                  | FO = 2 | FO = 3 | FO = 4 | FO = 8     | UNIT |  |

| <sup>t</sup> pd | Critical               | 5.4                     | 5.8    | 6.2    | 8.5    | See Note 7 | ns   |  |

| <sup>t</sup> pd | Not critical           | 6.3                     | 6.7    | 7.7    | 8.6    | 10.8       | ns   |  |

NOTES: 6. An unloaded logic module propagation delay time is 4 ns. All delays shown include the module delay time and statistical estimates for wiring delays based on 85% to 95% FPGA logic module utilization.

### long net, $V_{CC} = 5 \text{ V}$ , $T_J = 25^{\circ}\text{C}$ , typical process

Long nets include long horizontal and vertical routing resources used for noncritical signals and interconnecting logic macros separated by large distances. Long nets are used by the autorouter when no other means exist to complete the interconnection. Delays due to the use of long nets range from 15 ns to 35 ns. Typically less than one percent of all nets in a design require the use of a long net.

<sup>7.</sup> Critical nets are limited to a fan-out of 6 loads.

SRFS001F - D3864, DECEMBER 1989 - REVISED FEBRUARY 1993

## typical switching characteristics

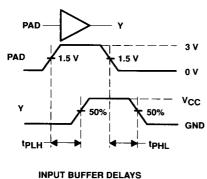

## input buffer and bidirectional-input buffer, V<sub>CC</sub> = 5 V, T<sub>J</sub> = 25°C, typical process

|           | FROM    | то             |        |        | DELAY TIME |        |        | UNIT   |

|-----------|---------|----------------|--------|--------|------------|--------|--------|--------|

| PARAMETER | (INPUT) | (OUTPUT)       | FO = 1 | FO = 2 | FO = 3     | FO = 4 | FO = 8 | Olviii |

| tPHL      |         |                | 6.9    | 7.6    | 8.9        | 10.7   | 14.3   | ns     |

| tPLH      | Pad     | ļ <sup>Ÿ</sup> | 5.9    | 6.5    | 7.7        | 8.4    | 12.4   | 115    |

## output buffer, V<sub>CC</sub> = 5 V, T<sub>J</sub> = 25°C, typical process

| PARAMETER     | FROM<br>(INPUT) | TO<br>(OUTPUT) | TEST<br>CONDITIONS                    | DRIVING<br>CMOS LOADS | DRIVING<br>TTL LOADS | UNIT  |

|---------------|-----------------|----------------|---------------------------------------|-----------------------|----------------------|-------|

| tPHL          |                 | 2.1            | 0 50-5                                | 3.9                   | 4.9                  | ns    |

| tPLH          | D               | Pad            | C <sub>L</sub> = 50 pF                | 7.2                   | 5.7                  |       |

| $\Delta$ tpHL | _               |                | · · · · · · · · · · · · · · · · · · · | 0.03                  | 0.046                | ns/pF |

| ΔtpLH         | D               | .Pad           |                                       | 0.07                  | 0.039                | По/рг |

The BIBUF macro's output section exhibits the same delays as the OUTBUF macro. The delta numbers can be extrapolated down to 15 pF minimum.

Example: Delay for an OUTBUF output buffer driving a 100-pF TTL load

$t_{PHL} = 4.9 + [(0.046 \times (100 - 50)] = 4.9 + 2.3 = 7.2 \text{ ns}$  $t_{PHH} = 5.7 + [(0.039 \times (100 - 50)] = 5.7 + 2.0 = 7.7 \text{ ns}$

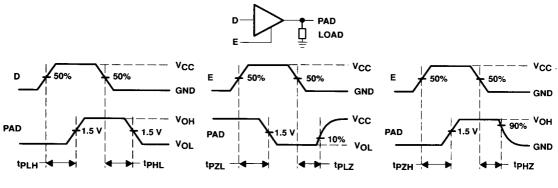

# 3-state and bidirectional output buffer, $V_{CC} = 5 \text{ V}$ , $T_J = 25^{\circ}\text{C}$ , typical process

| PARAMETER        | FROM<br>(INPUT) | TO<br>(OUTPUT) | TEST CONDITIONS        | DRIVING<br>CMOS LOADS | DRIVING<br>TTL LOADS | UNIT    |             |       |

|------------------|-----------------|----------------|------------------------|-----------------------|----------------------|---------|-------------|-------|

| t <sub>PHL</sub> |                 | Pad            | C <sub>I</sub> = 50 pF | 3.9                   | 4.9                  | ns      |             |       |

| <sup>†</sup> PLH | D               | Pad            | CL = 50 pr             | 7.2                   | 5.7                  | 113     |             |       |

| t <sub>PHZ</sub> | E               | Pad            |                        | 5.2                   | 3.4                  | ns      |             |       |

| <sup>t</sup> PZH | E               | Pau            |                        | 6.5                   | 4.9                  | 1,3     |             |       |

| tPLZ             | E               | Pad            | 7                      | 6.9                   | 5.2                  | ns      |             |       |

| <sup>t</sup> PZL | E               | rau            | ı au                   |                       | 4.9                  | 5.9     | 113         |       |

| ΔtPHL            |                 | Pad            | Pad                    | Pad                   | See test loads       | 0.03    | 0.046       | ns/pF |

| ΔtpLH            | D               |                |                        |                       | Pao                  | rau     | in Figure 8 | 0.07  |

| $\Delta_{tPHZ}$  | _               |                | <b>-</b>               | 0.08                  | 0.046                | ns/pF   |             |       |

| ΔtpzH            | E               | Pad            |                        | 0.07                  | 0.039                | Т па/рг |             |       |

| ΔtpLZ            | _               |                |                        | 0.07                  | 0.039                | ns/pF   |             |       |

| ΔtpZL            | E               | Pad            |                        | 0.03                  | 0.039                | IIS/PF  |             |       |

# clock buffer, $V_{CC}$ = 5 V, $T_J$ = 25°C, typical process (see Note 8)

|           |      |    | DELAY TIME |          |          |      |

|-----------|------|----|------------|----------|----------|------|

| PARAMETER | FROM | то | FO = 40    | FO = 160 | FO = 320 | UNIT |

| †PHL      |      |    | 9          | 12       | 15       | ns   |

| tPLH      | Pad  | Y  | 9          | 12       | 15       | ] "" |

NOTE 8: The ALS software provides user-selectable options for choosing four levels of automatic clock load balancing. There is no limit to the number of loads that may be connected to the clock buffer (CLKBUF) macro.

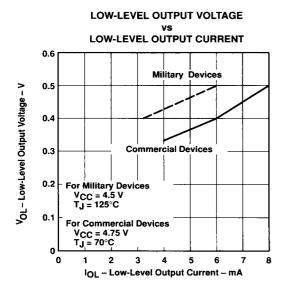

#### extended output current operation

The TPC10 Series devices are capable of driving larger sink current loads by derating the low-level output voltage to 0.5 V and high-level output voltage to 2.4 V. The derating factors for commercial and military devices are illustrated in Figure 4 and Figure 5. The commercial devices are derated up to 8 mA and military devices are derated for up to 6 mA.

HIGH-LEVEL OUTPUT VOLTAGE **HIGH-LEVEL OUTPUT CURRENT** 6 VOH - High-Level Output Voltage - V 5 **Commercial Devices** 3 Military Devices For Military Devices V<sub>CC</sub> = 4.5 V TJ = 125°C For Commercial Devices V<sub>CC</sub> = 4.75 V Tj = 70°C O - 3 - 2 -8 \_4 IOH - High-Level Output Current - mA

Figure 4

Figure 5

#### slow input transition (rise and fall) times

Slow signal transition is a condition that commonly occurs even in today's high-performance systems. A typical example is the signal degradation encountered with signals coming off of a highly capacitive bus. These slow signal transitions can cause undesirable results when traveling through the threshold region of a CMOS input. Texas Instruments recommends that input signal transitions be limited to 500 ns or less to ensure device integrity.

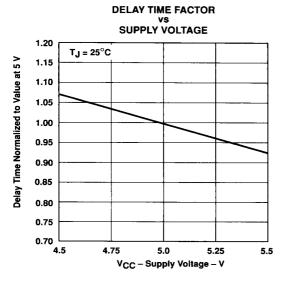

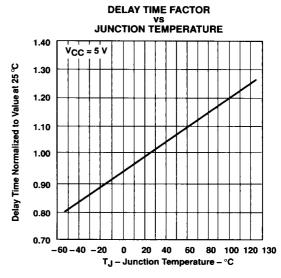

#### worst-case delay time

Unlike mask-programmed gate arrays, performance variations of TPC10 Series arrays caused by voltage and temperature changes are due primarily to the changes in the active elements. Voltage and temperature delay time factors are shown in Figure 6 and Figure 7.

#### timing derating

Operating temperature, operating voltage, and device processing conditions, along with product revision and speed grade, account for variations in array timing characteristics. These variations are summarized in derating factors for TPC10 array typical timing specifications. The derating factors as shown in Table 4 are based on the recommended operating conditions for TPC10 commercial, industrial, and military applications.

For estimating performance, the delay factors may be used in conjunction with the delay values shown in the typical switching characteristics tables. Temperature and voltage variations are measured according to the curves in the graphs shown in Figure 6 and Figure 7. The ALS timing analyzer can be used to provide actual postlayout timing specifications for each circuit implementation.

Table 4. Timing Derating Factor (x typical) (see Note 9)

| TPC1010A, TPC1020A | C SUFFIX  |            | I SU      | IFFIX      | M SUFFIX  |            |

|--------------------|-----------|------------|-----------|------------|-----------|------------|

| TPC1010B, TPC1020B | BEST CASE | WORST CASE | BEST CASE | WORST CASE | BEST CASE | WORST CASE |

| Standard speed     | 0.45      | 1.54       | 0.40      | 1.65       | 0.37      | 1.79       |

| -1 Speed grade     | 0.45      | 1.28       | 0.40      | 1.37       | 0.37      | 1.49       |

| -2 Speed grade†    | 0.45      | 1.13       | 0.40      | 1.20       | 0.37      | 1.32       |

† Applies to TPC1010B and TPC1020B only

NOTE 9: Best case reflects maximum operating voltage, minimum operating temperature, and best case processing. Worst case reflects minimum operating voltage, maximum operating temperature, and worst case processing. Best case derating is based on sample data only and is not guaranteed.

Figure 7

POST OFFICE BOX 655303 . DALLAS, TEXAS 7526

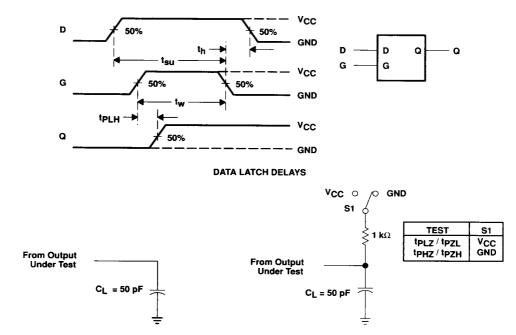

## PARAMETER MEASUREMENT INFORMATION

**OUTPUT BUFFER DELAYS**

D FLIP-FLOP SHOWING POSITIVE-EDGE TRIGGERED CLOCK

Figure 8. Symbols, Test Loads, and Voltage Waveforms

ww.dzsc.com

Powerec

### PARAMETER MEASUREMENT INFORMATION

LOAD CIRCUIT FOR PROPAGATION DELAY TIMES

LOAD CIRCUIT FOR ENABLE AND DISABLE TIMES

Figure 8. Symbols, Test Loads, and Voltage Waveforms (Continued)

### dynamic power calculations

The formula for calculating typical dynamic die power consumption in mW is:

Total die power =

$$(0.20N \times f1) + (0.085M \times f2) + (0.80P \times f3)$$

where:

f1 = Average logic module switching rate in MHz

f2 = Average clock pin switching rate in MHz (see Note 10)

f3 = Average I/O switching rate in MHz

M = Number of logic modules connected to the clock pin (see Note 10)

N = Number of logic modules used on the chip (including M)

P = Number of I/Os used with 50-pF load

NOTE 10: The F2 and M factors can be ignored if the CLKBUF macro is not used.

For example, if a TPC1010A design has 200 logic modules used, 40 of which are connected to the high-fan-out clock buffer running at 20 MHz and the rest running at 4 MHz, plus 50 I/Os (25 outputs, 25 inputs) running at an average of 4 MHz, it will dissipate the following amount of power:

Total die power =

$$(0.20N \times f1) + (0.085M \times f2) + (0.80P \times f3)$$

=  $0.20 (200 \times 4) + 0.085 (40 \times 20) + 0.80 (25 \times 4)$

=  $308 \text{ mW}$

### **ESD** rating

ESD characterization of Texas Instruments FPGAs is performed in accordance with Method 3015 of MIL-STD-883. This calls out the human body model which included discharging a 10-pF capacitor through a 1.5-k $\Omega$  resistor. Three positive and three negative pulses are discharged into each pin at each voltage level. After pulsing, the units are tested on a VLSI tester. Testing is performed for initial device qualification and product redesign only. All devices have been designed for ESD protection.

dzsc.com

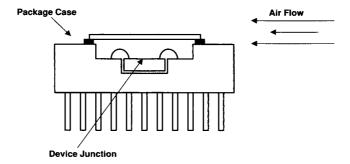

#### package thermal characteristics

The device junction to case thermal characteristic is  $R_{\theta JC}$ , and the junction to ambient air characteristic is  $R_{\theta JA}$ . The thermal characteristics for  $R_{\theta JA}$  are shown with two different air-flow rates. Maximum junction temperature is 150°C for short durations. However, a maximum junction temperature of 140°C is recommended for continuing operation. A sample calculation of the maximum power dissipation for a PLCC 84-pin package at commercial temperature is as follows:

$$\frac{\text{Max. junction temp. (°C)} - \text{Max. commercial temp. (°C)}}{\text{R}_{\theta \text{JA}} \text{ (°C/W)}} = \frac{150^{\circ}\text{C} - 70^{\circ}\text{C}}{40^{\circ}\text{C/W}} = 2 \text{ W}$$

| PACKAGE TYPE                        | PIN COUNT      | R <sub>OJC</sub> | R <sub>OJA</sub><br>STILL AIR | R <sub>OJA</sub><br>300 FT/MIN | UNIT |

|-------------------------------------|----------------|------------------|-------------------------------|--------------------------------|------|

| Ceramic Pin Grid Array<br>(CPGA)    | 84             | 3.5              | 48                            | NA                             | °C/W |

| Ceramic Quad Flat<br>Package (CQFP) | 84             | 3.5              | 75                            | NA                             | °C/W |

| Plastic Leaded Chip Carrier<br>PLCC | 44<br>68<br>84 | 13<br>13<br>10   | 65<br>50<br>40                | 41<br>32<br>27                 | °C/W |

| Plastic Quad Flat Package (PQFP)    | 100            | 10               | 60                            | 38                             | °C/W |

## TPC1010A device availability and resources

### Commercial

| PACKAGE      | LOGIC   | GATES | USER I/Os | SPEED GRADE |    |  |

|--------------|---------|-------|-----------|-------------|----|--|

| TYPE         | MODULES |       | USEN I/US | STD         | -1 |  |

| 44-pin PLCC  |         |       | 34        | R           | R  |  |

| 68-pin PLCC  | 295     | 1200  | 57        | R           | R  |  |

| 100-pin PQFP |         |       | 57        | R           | R  |  |

#### Industrial

| PACKAGE      | LOGIC   | GATES | CATES     | GATES USER I/Os | SPEED GRADE |  |

|--------------|---------|-------|-----------|-----------------|-------------|--|

| TYPE         | MODULES |       | USEN I/OS | STD             | -1          |  |

| 44-pin PLCC  |         |       | 34        | R               | R           |  |

| 68-pin PLCC  | 295     | 1200  | 57        | R               | R           |  |

| 100-pin PQFP | 1       |       | 57        | R               | R           |  |

### **Military**

| PACKAGE     | LOGIC   | GATES | USER I/Os | SPEED | GRADE |

|-------------|---------|-------|-----------|-------|-------|

| TYPE        | MODULES |       | OSER I/OS | STD   | -1    |

| 84-pin CPGA | 295     | 1200  | 57        | R     | R     |

| 84-pin CQFP | 295     |       | 57        | R     | R     |

### TPC1020A device availability and resources

#### Commercial

| PACKAGE      | LOGIC   | GATES | GATES USER I/Os |     | SPEED GRADE |  |  |

|--------------|---------|-------|-----------------|-----|-------------|--|--|

| TYPE         | MODULES |       | USEN I/US       | STD | <b>–1</b>   |  |  |

| 44-pin PLCC  |         | 2000  | 34              | R   | R           |  |  |

| 68-pin PLCC  | 547     |       | 57              | R   | R           |  |  |

| 84-pin PLCC  | 547     |       | 69              | R   | R           |  |  |

| 100-pin PQFP |         |       | 69              | R   | R           |  |  |

#### Industrial

| PACKAGE      | LOGIC   | GATES | USER I/Os | SPEED GRADE |    |

|--------------|---------|-------|-----------|-------------|----|

| TYPE         | MODULES |       | USEN I/US | STD         | -1 |

| 44-pin PLCC  |         |       | 34        | R           | R  |

| 68-pin PLCC  | 547     | 2000  | 57        | R           | R  |

| 84-pin PLCC  | 547     |       | 69        | R           | R  |

| 100-pin PQFP |         |       | 69        | R           | R  |

### Military

| PACKAGE     | LOGIC   | GATES | USER I/Os | SPEED | GRADE |

|-------------|---------|-------|-----------|-------|-------|

| TYPE        | MODULES | GATES | USEN I/US | STD   | -1    |

| 84-pin CPGA | 547     | 2000  | 69        | R     | R     |

| 84-pin CQFP | 547     |       | 69        | R     | R     |

R = released

P = planned, consult your local TI sales representative for current availability.

R = released P = planned, consult your local TI sales representative for current availability.

SRFS001F - D3864, DECEMBER 1989 - REVISED FEBRUARY 1993

## TPC1010B device availability and resources

#### Commercial

| PACKAGE      | LOGIC   | GATES | USER I/Os |     | SPEED GRADE |    |

|--------------|---------|-------|-----------|-----|-------------|----|

| TYPE         | MODULES | GAIES | USEN I/US | STD | -1          | -2 |

| 44-pin PLCC  |         |       | 34        | R   | R           | Р  |

| 68-pin PLCC  | 295     | 1200  | 57        | R   | R           | Р  |

| 100-pin PQFP |         |       | 57        | Р   | Р           | Р  |

### Industrial

| PACKAGE      | LOGIC<br>MODULES | GATES | USER I/Os | SPEED GRADE |    |    |

|--------------|------------------|-------|-----------|-------------|----|----|

| TYPE         |                  |       |           | STD         | -1 | -2 |

| 44-pin PLCC  | 295              | 1200  | 34        | R           | R  | Р  |

| 68-pin PLCC  |                  |       | 57        | R           | R  | Р  |

| 100-pin PQFP |                  |       | 57        | Р           | Р  | Р  |

## TPC1020B device availability and resources

#### Commercial

| PACKAGE      | LOGIC   | GATES | ES USER I/Os | SPEED GRADE |    |    |

|--------------|---------|-------|--------------|-------------|----|----|

| TYPE         | MODULES | GATES |              | STD         | -1 | -2 |

| 44-pin PLCC  | 547     | 2000  | 34           | Р           | Р  | Р  |

| 68-pin PLCC  |         |       | 57           | Р           | Р  | P  |

| 84-pin PLCC  |         |       | 69           | Р           | Р  | Р  |

| 100-pin PQFP |         |       | 69           | Р           | Р  | Р  |

#### Industrial

| PACKAGE<br>TYPE | LOGIC<br>MODULES | GATES | USER I/Os | SPEED GRADE |    |    |

|-----------------|------------------|-------|-----------|-------------|----|----|

|                 |                  |       |           | STD         | -1 | -2 |

| 44-pin PLCC     | 547              | 2000  | 34        | Р           | Р  | Р  |

| 68-pin PLCC     |                  |       | 57        | Р           | Р  | Р  |

| 84-pin PLCC     |                  |       | 69        | Р           | Р  | Р  |

| 100-pin PQFP    |                  |       | 69        | Р           | P  | Р  |

R = released

P = planned, consult your local TI sales representative for current availability.

R = released P = planned, consult your local TI sales representative for current availability.

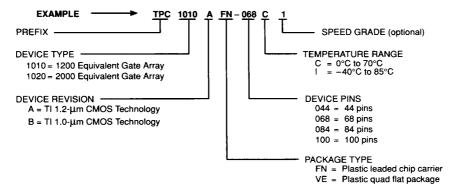

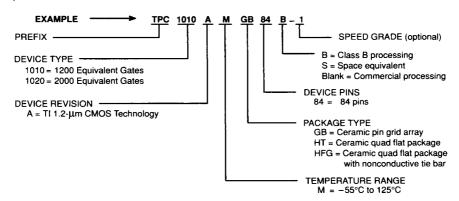

### ordering information

Configurations of the TPC10 Series devices can be ordered using the part numbers in the examples below. Commercial and industrial versions can be ordered as follows:

Military versions can be ordered as follows:

#### **DEFENSE ELECTRONIC SYSTEM CENTER (DESC) NUMBER**

| DEVICE NAME | AVAILABLE<br>PROCESSING     | DESC<br>N <b>UMBE</b> R |

|-------------|-----------------------------|-------------------------|

| TPC1010AM   | Class B                     | 5962-9096401M           |

| TPC1020AM   | Class B<br>Space Equivalent | 5962-9096501M           |

#### macro library

The TPC10 Series is supported by a macro library of more than 250 hardwired and soft macro functions. The macros range from primitive logic gates to MSI-level complex functions such as counters, decoders, and comparators. The hardwired macro characteristics are provided in the electrical and switching characteristics. The software macros have characteristics similar to the components of the macro but need the place and route data back annotated into the design to establish actual performance.

The FPGA logic module implements logic functions with inverted inputs as efficiently as noninverted inputs, without an increase in propagation delay. By taking advantage of the various combinations of input polarity, the use of separate inverters can be virtually eliminated.

### **TPC10 SERIES SOFTWARE MACROS**

| MACRO NAME | DESCRIPTION                                    | MODULE COUNT | LOGIC LEVELS |

|------------|------------------------------------------------|--------------|--------------|

| CNT4A      | 4-Bit Binary Counter With Load and Clear       |              | 4            |

| CNT4B      | 4-Bit Presettable Binary Counter With Load and | d Clear15    | 4            |

| DEC2X4     | 2-Line to 4-Line Decoder                       | 4            | 1            |

| DEC2X4A    | 2-Line to 4-Line Inverting Decoder             | 4            | 1            |

| DECE2X4    | 2-Line to 4-Line Decoder With Enable           | 4            | 1            |

| DECE2X4A   | 2-Line to 4-Line Inverting Decoder With Enable | 5            | 1            |

| DEC3X8     | 3-Line to 8-Line Decoder                       | 8            | 1            |

| DEC3X8A    | 3-Line to 8-Line Inverting Decoder             | 9            | 1            |

| DECE3X8    | 3-Line to 8-Line Decoder With Enable           | 11           | 2            |

| DECE3X8A   | 3-Line to 8-Line Inverting Decoder With Enable | 11           | 2            |

| DEC4X16A   | 4-Line to 16-Line Inverting Decoder            | 20           | 2            |

| DLOTATOA   | Octal D-Type Latch With Clear                  |              | 4            |

| DLCOA      | Octal D-Type Latch With Enable                 |              | I            |

| DLEO       | Octal D. Type Latch With Multipleyed Incute    |              |              |

| DLIVIB     | Octal D-Type Latch With Multiplexed Inputs     |              | 1            |

| FA1        | 1-Bit Full Adder                               | <u>3</u>     | 3            |

| FADD8      | 8-Bit Fast Adder                               |              | 4            |

|            | 12-Bit Fast Adder                              |              |              |

| FADD16     | 16-Bit Fast Adder                              | 79           | 5            |

|            | 24-Bit Fast Adder                              |              |              |

| FADD32     | 32-Bit Fast Adder                              | 160          | 7            |

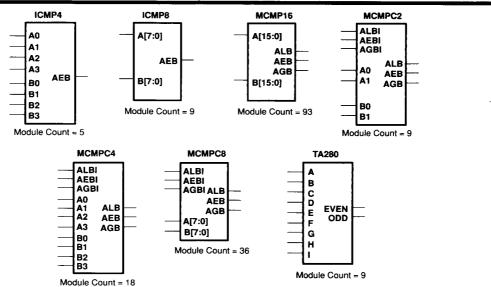

| ICMP4      | 4-Bit Identity Comparator                      | 5            | 2            |

| ICMP8      | 8-Bit Identity Comparator                      | 9            | 3            |

| MCMPC2     | 2-Bit Magnitude Comparator With Enable         | 9            | 3            |

| MCMPC4     | 4-Bit Magnitude Comparator With Enable         | 18           | 4            |

| MCMPC8     | 8-Bit Magnitude Comparator With Enable         | 36           | 6            |

| MCMP16     | 16-Bit Magnitude Comparator                    | 93           | 5            |

| MX8        | 8-Line to 1-Line Multiplexer                   | 3            | 2            |

| MX8A       | 8-Line to 1-Line Inverting Multiplexer         | 3            | 2            |

| MX16       | 16-Line to 1-Line Multiplexer                  | 5            | 2            |

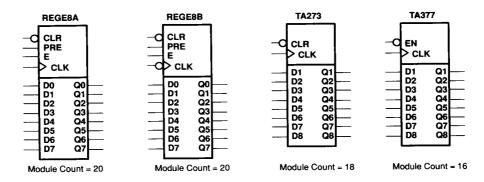

| REGE8A     | Octal Register With Preset and Clear           | 20           | 1            |

| BEGE8B     | Octal Register With Preset and Clear           | 20           | 1            |

| SMULTS     | 8 x 8 Twos Complement Multiplier               | 241          |              |

| SREG4A     | 4-Bit Shift Register With Clear                | 0            | 4            |

| SREGRA     | 8-Bit Shift Register With Clear                | 10           | 4            |

| TA129      | 3-Line to 8-Line Decoder/Demultiplexer         |              |              |

| TA130      | 2 Line to 4 Line Decoder/Demultiplexer         |              |              |

| TA159      | 2-Line to 4-Line Decoder/Demultiplexer         | 4            | 1            |

| TA151      | 8-Line to 1-Line Multiplexer                   |              | 3            |

| IA153T     | 4-Line to 1-Line Multiplexer                   | 2            | 2            |

| IA15/T     | 2-Line to 1-Line Multiplexer                   |              | 1            |

| IA161      | Synchronous 4-Bit Counter With Direct Clear .  | 22           | 3            |

| TA164      | 8-Bit Parallel-Out Shift Register              | 18           | 1            |

| TA169      | 4-Bit Up/Down Counter                          | 25           | 6            |

| TA194      | 4-Bit Bidirectional Universal Shift Register   | 14           | 1            |

| TA195      | 4-Bit Parallel-Access Shift Register           |              | 1            |

| TA269      | 8-Bit Up/Down Counter                          | 50           | 8            |

| TA273      | Octal D-Type Flip-Flop With Clear              | 18           | 1            |

|            | 9-Bit Odd/Even Parity Generator/Checker        |              |              |

|            | Octal D-Type Flip-Flop With Clock Enable       |              |              |

| UDCNT4A    | 4-Bit Up/Down Counter With Sync Load and C     | arry 24      | 6            |

|            | nardwired.                                     | ,            |              |

† These MSI functions are hardwired.

SRFS001F - D3864, DECEMBER 1989 - REVISED FEBRUARY 1993

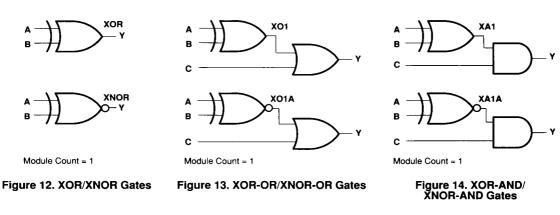

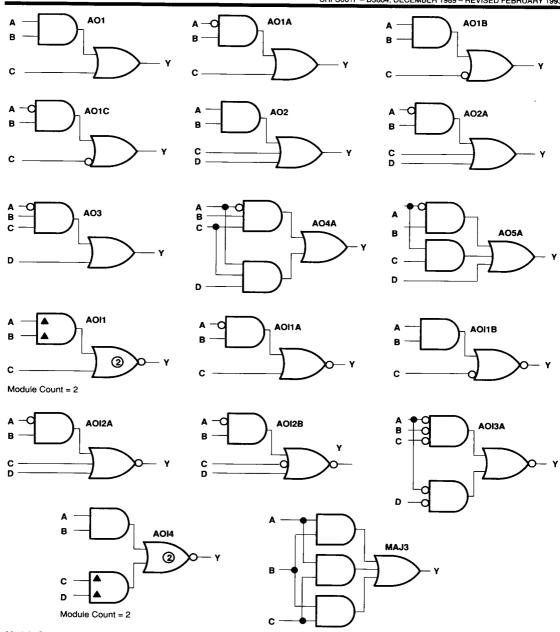

Figure 9. 2-Input Gates

Module Count = 1 (unless otherwise noted)

2) Indicates Module Count = 2

▲ Indicates extra delay input

Figure 10. 3-Input Gates

Copyright © 1993, Texas Instruments Incorporated

SRFS001F - D3864, DECEMBER 1989 - REVISED FEBRUARY 1993

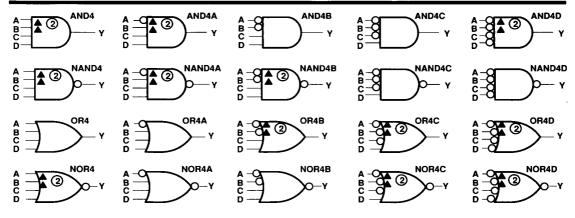

Module Count = 1 (unless otherwise noted)

- 2 Indicates Module Count = 2

- ▲ Indicates extra delay input

Figure 11. 4-Input Gates

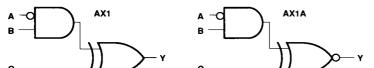

Figure 15. AND-XOR/AND-XNOR Gates

Powerec

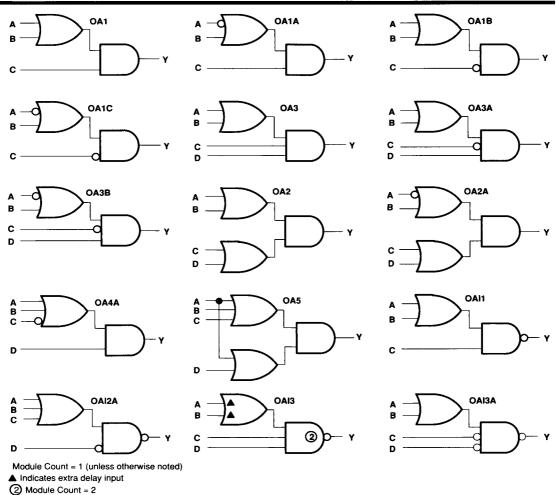

Module Count = 1

ww.dzsc.com

POST OFFICE BOX 655303 ● DALLAS, TEXAS 75265

SRFS001F - D3864, DECEMBER 1989 - REVISED FEBRUARY 1993

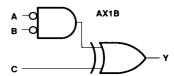

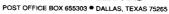

Module Count = 1 (unless otherwise noted)

- 2 Indicates Module Count = 2

- ▲ Indicates extra delay input

Figure 16. AND-OR/AND-NOR Gates

Figure 17. OR-AND/OR-NAND Gates

www.dzsc.com

Powerec

Figure 18. Buffers

Figure 19. I/O Buffers

Figure 20. Multiplexers

Module Count = 2 (unless otherwise noted)

▲ Indicates two logic module delay path

Figure 21. Adders

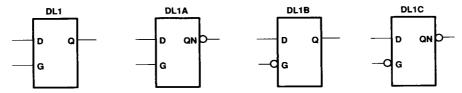

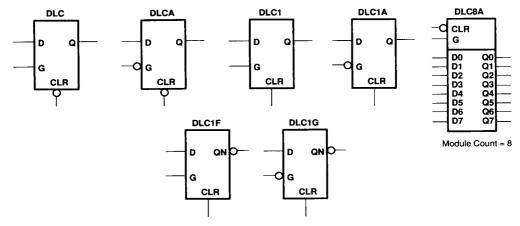

#### **D-TYPE LATCHES**

#### **D-TYPE LATCHES WITH CLEAR**

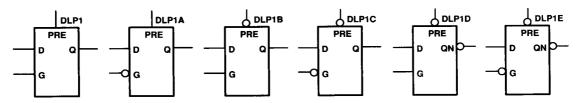

## **D-TYPE LATCHES WITH PRESET**

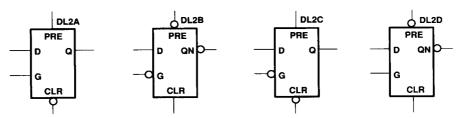

### **D-TYPE LATCHES WITH CLEAR AND PRESET**

Module Count = 1 (unless otherwise noted)

Figure 22. D-Type Latches

Figure 22. D-Types Latches (Continued)

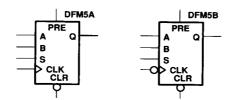

Figure 23. D-Type Flip-Flops

Module Count = 2

Figure 24. D-Type Flip-Flops With Enable

SRFS001F - D3864, DECEMBER 1989 - REVISED FEBRUARY 1993

CLK

## J-K FLIP-FLOPS WITH PRESET AND CLEAR

CLK

CLK

CLK

Module Count = 2

Figure 25. J-K Flip-Flops

2 26

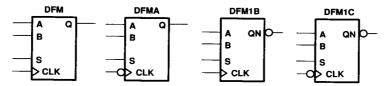

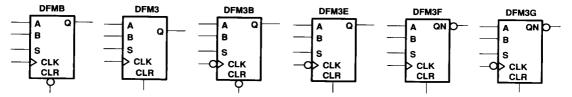

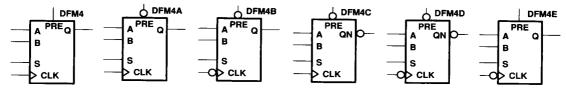

### **MULTIPLEXED-INPUT FLIP-FLOPS**

#### **MULTIPLEXED-INPUT FLIP-FLOPS WITH CLEAR**

### **MULTIPLEXED-INPUT FLIP-FLOPS WITH PRESET**

## MULTIPLEXED-INPUT FLIP-FLOPS WITH PRESET AND CLEAR

## MULTIPLEXED-INPUT FLIP-FLOPS WITH ENABLE

Module Count = 2

Figure 26. Multiplexed-Input Flip-Flops

Figure 27. Clock Buffer (CLKBUF) Interface

Figure 28. Octal D-Type Flip-Flops and Registers

SRFS001F - D3864, DECEMBER 1989 - REVISED FEBRUARY 1993

Figure 29. Comparators/Parity Checker

Figure 30. Counters

Figure 31. Decoders

ww.dzsc.com

# TPC10 SERIES CMOS FIELD-PROGRAMMABLE GATE ARRAYS

SRFS001F - D3864, DECEMBER 1989 - REVISED FEBRUARY 1993

Figure 32. Shift Registers

Figure 33. 8-Bit Multiplier

Figure 34. Logic Module

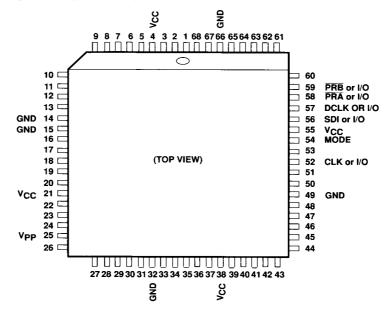

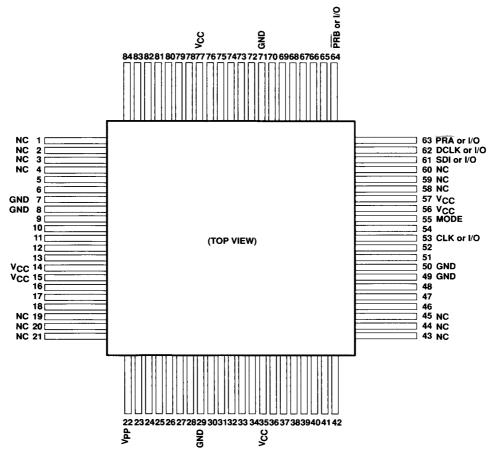

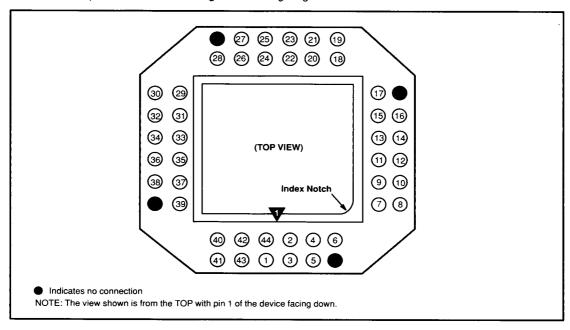

#### package pin assignments

- NOTES: A. All pins marked GND are ground connections and must be connected to circuit ground.

- B. Vpp must be terminated to VCC except during programming.

- C. PRA and PRB, the diagnostic probe outputs, should remain open if not used as I/Os.

- D. MODE must be terminated to circuit ground except during programming.†

- E. SDI and DCLK should be terminated to circuit ground during normal operation if not used as I/Os.†

- F. Unused I/O pins are automatically designated by the Action Logic System as outputs and should remain unconnected. Unused I/O pins are driven low by design.

- G. All unidentified pins on the pin assignment drawings are standard I/Os.

- † The security fuse must be programmed for SDI and DCLK to function as I/Os. For device debugging on the user's circuit board, MODE, SDI, and DCLK should be terminated to circuit ground through a 10-k $\Omega$  (or greater) resistor. They can be tied to ground if not debugging.

Figure 35. 44-Pin PLCC Pin Assignment

w.dzsc.com

Powered

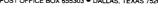

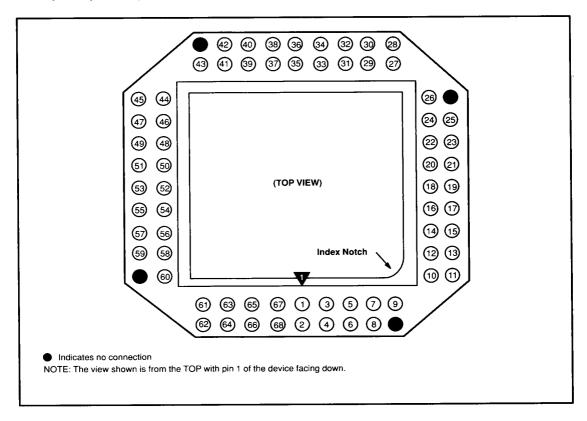

#### package pin assignments (continued)

NOTES: A. All pins marked GND are ground connections and must be connected to circuit ground.

- B. Vpp must be terminated to VCC except during programming.

- C. PRA and PRB, the diagnostic probe outputs, should remain open if not used as I/Os.

- D. MODE must be terminated to circuit ground except during programming.†

- E. SDI and DCLK should be terminated to circuit ground during normal operation if not used as I/Os.†

- F. Unused I/O pins are automatically designated by the Action Logic System as outputs and should remain unconnected. Unused I/O pins are driven low by design.

- G. All unidentified pins on the pin assignment drawings are standard I/Os.

Figure 36. 68-Pin PLCC Pin Assignment

<sup>†</sup> The security fuse must be programmed for SDI and DCLK to function as I/Os. For device debugging on the user's circuit board, MODE, SDI, and DCLK should be terminated to circuit ground through a 10-k $\Omega$  (or greater) resistor. They can be tied to ground if not debugging.

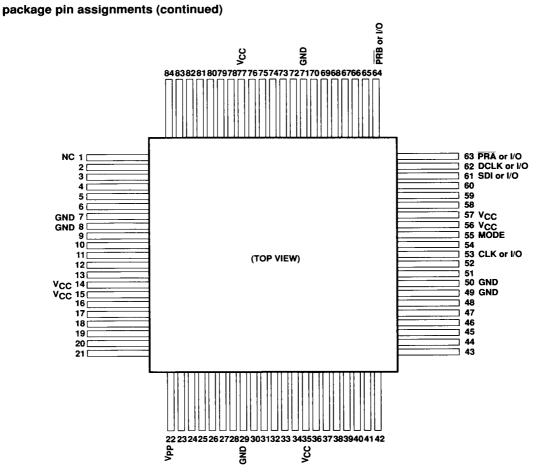

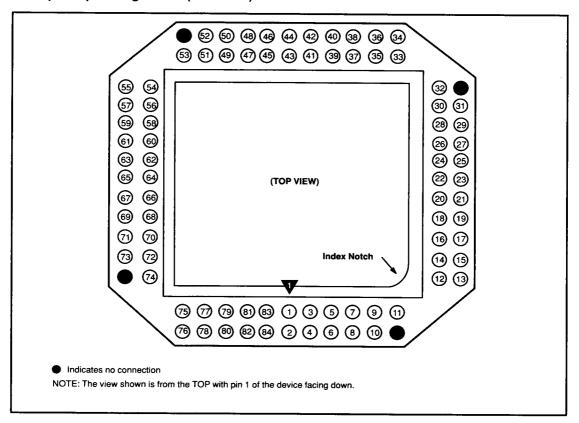

#### package pin assignments (continued)

NOTES: A. All pins marked GND are ground connections and must be connected to circuit ground.

- B. Vpp must be terminated to VCC except during programming.

- C. PRA and PRB, the diagnostic probe outputs, should remain open if not used as I/Os.

- D. MODE must be terminated to circuit ground except during programming.†

- E. SDI and DCLK should be terminated to circuit ground during normal operation if not used as I/Os.†

- F. Unused I/O pins are automatically designated by the Action Logic System as outputs and should remain unconnected. Unused I/O pins are driven low by design.

- G. All unidentified pins on the pin assignment drawings are standard I/Os.

Figure 37. 84-Pin PLCC Pin Assignment

2-44

w.dzsc.com

Powered

POST OFFICE BOX 655303 ● DALLAS, TEXAS 75265

<sup>†</sup> The security fuse must be programmed for SDI and DCLK to function as I/Os. For device debugging on the user's circuit board, MODE, SDI, and DCLK should be terminated to circuit ground through a 10-k $\Omega$  (or greater) resistor. They can be tied to ground if not debugging.

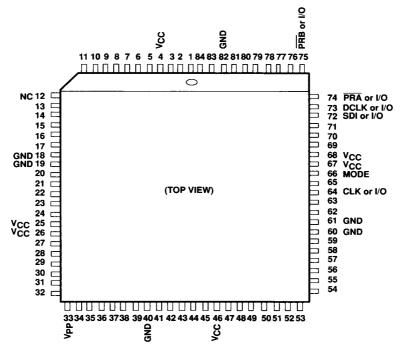

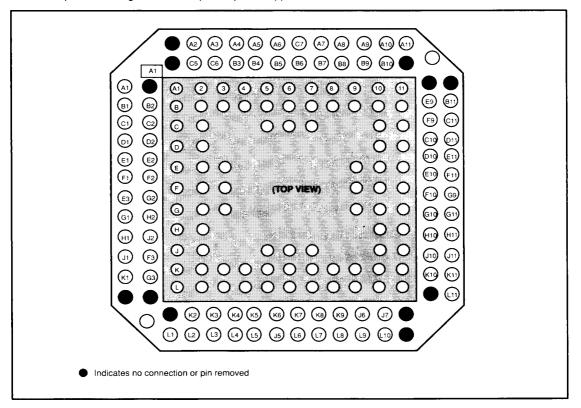

#### package pin assignments (continued)

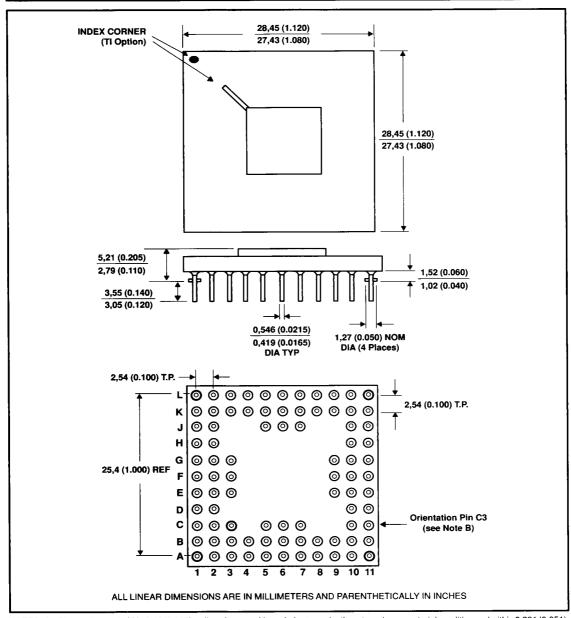

# I/O Pin Assignments for the 84-Pin Ceramic Pin Grid Array Package

| SIGNAL                      | TPC1010A                                                    | TPC1020A                 |

|-----------------------------|-------------------------------------------------------------|--------------------------|

| PRA                         | A11                                                         | A11                      |

| PRB                         | B10                                                         | B10                      |

| MODE                        | E11                                                         | E11                      |

| SDI                         | B11                                                         | B11                      |

| DCLK                        | C10                                                         | C10                      |

| Vpp                         | K2                                                          | K2                       |

| CLK or I/O                  | F9                                                          | F9                       |

| GND                         | B7, E2, E3, K5, F10, G10                                    | B7, E2, E3, K5, F10, G10 |

| Vcc                         | B5, F1, G2, K7, E9, E10                                     | B5, F1, G2, K7, E9, E10  |

| NC (No internal connection) | B1, B2, C1, C2, K1, J2, L1,<br>J10, K10, K11, C11, D10, D11 | B2                       |

- NOTES: A. All pins marked GND are ground connections and must be connected to circuit ground.

- B. Vpp must be terminated to VCC except during programming.

- C. PRA and PRB, the diagnostic probe outputs, should remain open if not used as I/Os.

- D. MODE must be terminated to circuit ground except during programming.†

- E. SDI and DCLK should be terminated to circuit ground during normal operation if not used as I/Os.†

- F. Unused I/O pins are automatically designated by the Action Logic System as outputs and should remain unconnected. Unused I/O pins are driven low by design.

- G. All unidentified pins on the pin assignment drawings are standard I/Os.

- H. Orientation pin C3 is connected internally to pin C2.

w.dzsc.com

Figure 38. 84-Pin CPGA Pin Assignment

<sup>†</sup> The security fuse must be programmed for SDI and DCLK to function as I/Os. For device debugging on the user's circuit board, MODE, SDI, and DCLK should be terminated to circuit ground through a 10-k $\Omega$  (or greater) resistor. They can be tied to ground if not debugging.

#### package pin assignments (continued)

- NOTES: A. All pins marked GND are ground connections and must be connected to circuit ground.

- B. Vpp must be terminated to VCC except during programming.

- C. PRA and PRB, the diagnostic probe outputs, should remain open if not used as I/Os.

- D. MODE must be terminated to circuit ground except during programming.†

- E. SDI and DCLK should be terminated to circuit ground during normal operation if not used as I/Os.†

- F. Unused I/O pins are automatically designated by the Action Logic System as outputs and should remain unconnected. Unused I/O pins are driven low by design.

- G. All unidentified pins on the pin assignment drawings are standard I/Os.

- H. NC = No internal connection

Figure 39. TPC1010A 84-Pin CQFP Pin Assignment

2-46

POST OFFICE BOX 655303 ● DALLAS, TEXAS 75265

<sup>†</sup> The security fuse must be programmed for SDI and DCLK to function as I/Os. For device debugging on the user's circuit board, MODE, SDI, and DCLK should be terminated to circuit ground through a 10-k $\Omega$  (or greater) resistor. They can be tied to ground if not debugging.

- NOTES: A. All pins marked GND are ground connections and must be connected to circuit ground.

- B. VPP must be terminated to VCC except during programming.

- C. PRA and PRB, the diagnostic probe outputs, should remain open if not used as I/Os.

- D. MODE must be terminated to circuit ground except during programming.†

- E. SDI and DCLK should be terminated to circuit ground during normal operation if not used as I/Os.†

- F. Unused I/O pins are automatically designated by the Action Logic System as outputs and should remain unconnected. Unused I/O pins are driven low by design.

- G. All unidentified pins on the pin assignment drawings are standard I/Os.

- H. NC = No internal connection

ww.dzsc.com

Powered

Figure 40. TPC1020A 84-Pin CQFP Pin Assignment

<sup>†</sup> The security fuse must be programmed for SDI and DCLK to function as I/Os. For device debugging on the user's circuit board, MODE, SDI, and DCLK should be terminated to circuit ground through a 10-k $\Omega$  (or greater) resistor. They can be tied to ground if not debugging.

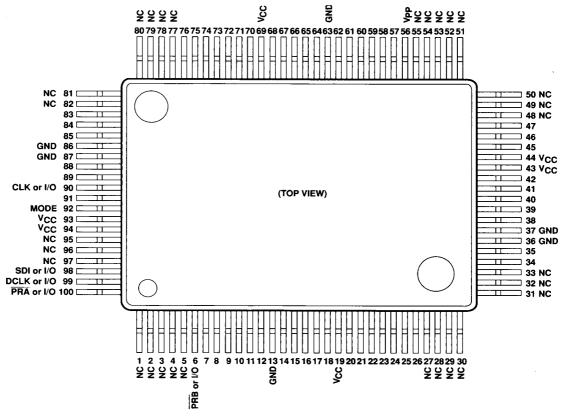

#### package pin assignments (continued)

NOTES: A. All pins marked GND are ground connections and must be connected to circuit ground.

- B. Vpp must be terminated to VCC except during programming.

- C. PRA and PRB, the diagnostic probe outputs, should remain open if not used as I/Os.

- D. MODE must be terminated to circuit ground except during programming.†

- E. SDI and DCLK should be terminated to circuit ground during normal operation if not used as I/Os.†

- F. Unused I/O pins are automatically designated by the Action Logic System as outputs and should remain unconnected. Unused I/O pins are driven low by design.

- G. All unidentified pins on the pin assignment drawings are standard I/Os.

- H. NC = No internal connection

Figure 41. TPC1010A 100-Pin PQFP Pin Assignment

ww.dzsc.com

Powered

POST OFFICE BOX 655303 ● DALLAS, TEXAS 75265

<sup>†</sup> The security fuse must be programmed for SDI and DCLK to function as I/Os. For device debugging on the user's circuit board, MODE, SDI, and DCLK should be terminated to circuit ground through a 10-k $\Omega$  (or greater) resistor. They can be tied to ground if not debugging.

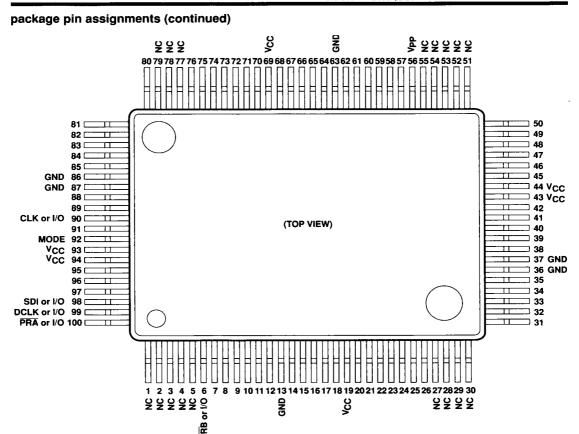

NOTES: A. All pins marked GND are ground connections and must be connected to circuit ground.

- B. Vpp must be terminated to VCC except during programming.

- C. PRA and PRB, the diagnostic probe outputs, should remain open if not used as I/Os.

- D. MODE must be terminated to circuit ground except during programming.†

- E. SDI and DCLK should be terminated to circuit ground during normal operation if not used as I/Os.†

- F. Unused I/O pins are automatically designated by the Action Logic System as outputs and should remain unconnected. Unused I/O pins are driven low by design.

- G. All unidentified pins on the pin assignment drawings are standard I/Os.

- H. NC = No internal connection

Figure 42. TPC1020A 100-Pin PQFP Pin Assignment

<sup>†</sup> The security fuse must be programmed for SDI and DCLK to function as I/Os. For device debugging on the user's circuit board, MODE, SDI, and DCLK should be terminated to circuit ground through a 10-k $\Omega$  (or greater) resistor. They can be tied to ground if not debugging.

#### actionprobe pin assignments

There are four types of Actionprobes available: 44-, 68-, and 84-pin PLCC, and 84-pin PGA. At the time your order is placed, please specify which Actionprobe you need.

The Actionprobes are detailed in Figure 43 through Figure 46.

Figure 43. 44-Pin PLCC Actionprobe

#### actionprobe pin assignments (continued)

Figure 44. 68-Pin PLCC Actionprobe

#### actionprobe pin assignments (continued)

Figure 45. 84-Pin PLCC Actionprobe

ww.dzsc.com

Powerec

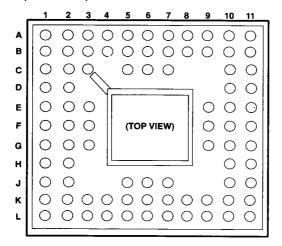

#### actionprobe pin assignments (continued)

The 84-pin pin-grid-array (PGA) Actionprobe has a number of pins around the socket connected to the device pins. The exact ordering of these pins is not obvious.

Figure 46 shows the Actionprobe with the top view up, which is how the device sits in the socket. Pin A1 is at the top left. Looking at the Actionprobe, pin A1 appears on the circuit board for reference.

Figure 46. 84-Pin PGA Actionprobe

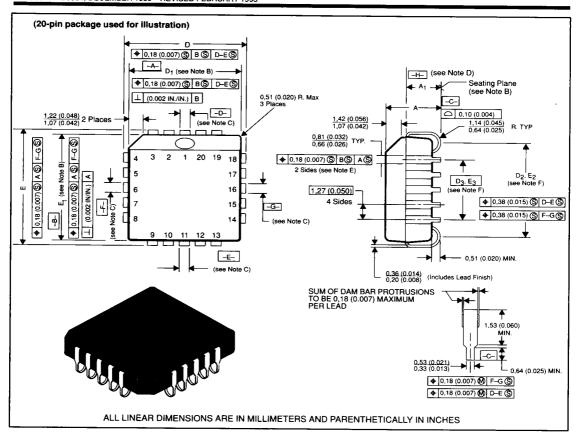

| JEDEC<br>OUTLINE | PINS | MIN             | MAX             | MIN             | MAX             | D,<br>MIN        | E<br>MAX         | D1,<br>MIN       | E1<br>MAX        | D2<br>MIN        | , E2<br>MAX      | D3, E3 BASIC  |

|------------------|------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|------------------|------------------|------------------|------------------|---------------|

| MO-047AC         | 44   | 4,19<br>(0.165) | 4,57<br>(0.180) | 2,29<br>(0.090) | 3,04<br>(0.120) | 17,40<br>(0.685) | 17,65<br>(0.695) | 16,51<br>(0.650) | 16,66<br>(0.656) | 14,99<br>(0.590) | 16,00<br>(0.630) | 12,70 (0.500) |

| MO-047AE         | 68   | 4,19<br>(0.165) | 5,08<br>(0.200) | 2,29<br>(0.090) | 3,30<br>(0.130) | 25,02<br>(0.985) | 25,27<br>(0.995) | 24,13<br>(0.950) | 24,33<br>(0.958) | 22,61<br>(0.890) | 23,62<br>(0.930) | 20,32 (0.800) |

| MO-047AF         | 84   | 4,19<br>(0.165) | 5,08<br>(0.200) | 2,29<br>(0.090) | 3,30<br>(0.130) | 30,10<br>(1.185) | 30,35<br>(1.195) | 29,21<br>(1.150) | 29,41<br>(1.158) | 27,69<br>(1.090) | 28,70<br>(1.130) | 25,40 (1.000) |

- NOTES: A. All dimensions conform to JEDEC Specification MO-047AA/AF. Dimensions and tolerancing are per ANSI Y14.5M-1982.

- B. Dimension D<sub>1</sub> and E<sub>1</sub> do not include mold flash protrusion. Protrusion shall not exceed 0,25 (.010) on any side.

- C. Datums D-E and F-G for center leads are determined at datum -H-

- D. Datum H is located at top of leads where they exit plastic body.

- E. Location to datums -A- and -B- to be determined at datum -H-

- F. Determined at seating plane | -C-

Figure 47. Plastic Leaded Chip Carriers

ww.dzsc.com

POST OFFICE BOX 655303 ● DALLAS, TEXAS 75265

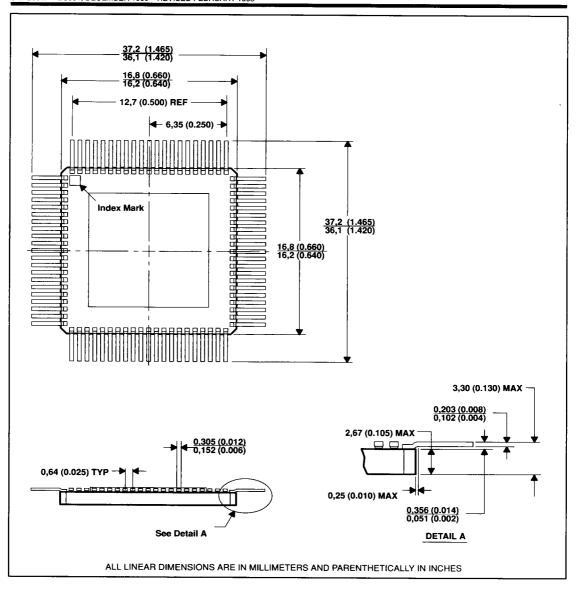

NOTES: A. Pins are located within 0,13 (0.005) radius of true position relative to each other at maximum material condition and within 0,381 (0.051) radius relative to the center of the ceramic.

Figure 48. 84-Pin Ceramic Pin-Grid-Array Package

POST OFFICE BOX 655303 ● DALLAS, TEXAS 75265

B. Orientation pin C3 is connected internally to pin C2.

Figure 49. 84-Pin Ceramic Quad Flat Package

www.dzsc.com

# TPC10 SERIES CMOS FIELD-PROGRAMMABLE GATE ARRAYS

SRFS001F - D3864, DECEMBER 1989 - REVISED FEBRUARY 1993 Contact the factory for mechanical data

Figure 50. 84-Pin Ceramic Quad Flat Package With Nonconductive Tie Bar

Figure 51. Plastic Quad Flat Packages

ww.dzsc.com

Powerec

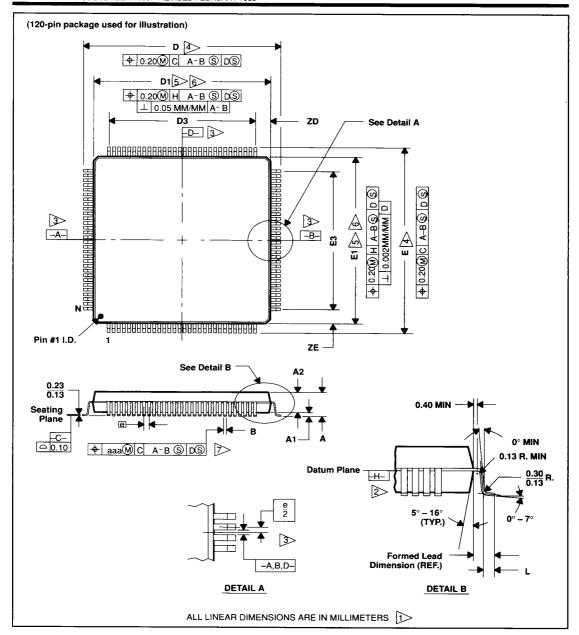

|                 |        | L.                 | ٧                    | FA        | A2                              | ٥                                                               | D1             | <b>EQ</b>  | αz        | Е                | ы              | E3            | ZE         | _            | •                                                                                                                                                        | 8          |            |        |        | FORMED                                                                                                                                                           |

|-----------------|--------|--------------------|----------------------|-----------|---------------------------------|-----------------------------------------------------------------|----------------|------------|-----------|------------------|----------------|---------------|------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------|--------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| JEDEC           | # SI   | # PKG<br>PINS TYPE | MAX                  |           | MAX                             | MAX                                                             | MAX            | Ç          | ç<br>e    | MAX              | MAX            | Ę.            | Ģ          | MAX          | 000                                                                                                                                                      | MAX        | 88         | 2      | 및      | LEAD<br>DIM.                                                                                                                                                     |

|                 |        |                    |                      | Z         | Z                               | Z<br>X                                                          | Z              | (שבנ)      | )<br>E    | Z                | MIN            | (עבינ) (עבינ) | (44)       | MIN          |                                                                                                                                                          | RIN        |            |        |        | (REF)                                                                                                                                                            |

| MO-<br>108/CC-1 | 92     |                    | RECT 3,40            | 0,25      | 3,05                            | 23,45<br>22,95                                                  | 20,10<br>19,90 | 18,85      | 95'0      | 17,45<br>16,95   | 14,10<br>13,90 | 12,35         | 0,83       | 0,95<br>0,65 | 9'0                                                                                                                                                      | 0,38       | 0,12 30 20 | 30     | 20     | 1,60                                                                                                                                                             |

| NOTES: 1        | a<br>∆ | dimen              | sions are            | e millim  | eters (mr                       | n), and c                                                       | conform t      | o JEDEC    | Specific  | ation M(         | J-108 (is      | sue A/O       | ctober 1   | 990). Din    | nensions a                                                                                                                                               | and tolera | ancing     | er Ah  | ISI Y1 | NOTES: D All dimensions are millimeters (mm), and conform to JEDEC specification MO-108 (issue A/October 1990). Dimensions and tolerancing per ANSI Y14.5M-1982. |