# FAIRCHILD

SEMICONDUCTOR

# FST16210 20-Bit Bus Switch

## **General Description**

The Fairchild Switch FST16210 provides 20-Bits of highspeed CMOS TTL-compatible bus switching. The low on resistance of the switch allows inputs to be connected to outputs without adding propagation delay or generating additional ground bounce noise.

The device is organized as a 10-bit or 20-Bit bus switch. When  $\overline{\text{OE}}_1$  is LOW, the switch is ON and Port 1A is connected to Port 1B. When  $\overline{\text{OE}}_2$  is LOW, Port 2A is connected to Port 2B.

# **Ordering Code:**

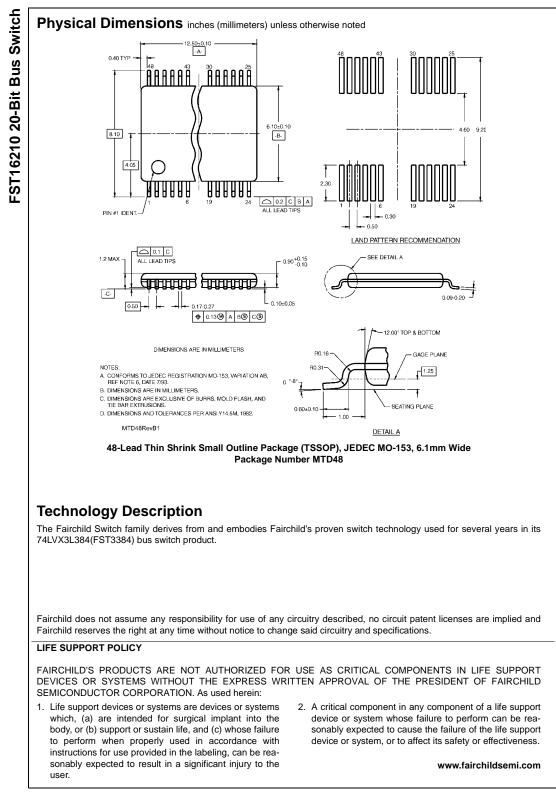

| Order Number                                                                                              | Package Number | Package Description                                                         |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------|----------------|-----------------------------------------------------------------------------|--|--|--|--|--|

| FST16210MTD                                                                                               | MTD48          | 48-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 6.1mm Wide |  |  |  |  |  |

| Devices also available in Tape and Reel. Specify by appending the suffix letter "X" to the ordering code. |                |                                                                             |  |  |  |  |  |

# **Connection Diagram**

| NC -                        |    | 48 | - OE,              |

|-----------------------------|----|----|--------------------|

| 1A <sub>1</sub>             | 2  | 47 |                    |

| 1A2 -                       | 3  | 46 | - 1B1              |

| 1A3                         | 4  | 45 | - 1B2              |

| 1A4                         | 5  | 44 | - 1 B <sub>3</sub> |

| 1A5 -                       | 6  | 43 | 184                |

| 1A6                         | 7  | 42 | 18 <sub>5</sub>    |

| GND -                       | 8  | 41 | - GND              |

| 1A7 —                       | 9  | 40 | - 18 <sub>6</sub>  |

| 1A <sub>8</sub>             | 10 | 39 | - 1B7              |

|                             | 11 | 38 | - 1B <sub>8</sub>  |

| 1A <sub>10</sub> -          | 12 | 37 | — 1Bg              |

| 2 A <sub>1</sub> —          | 13 | 36 | - <sup>18</sup> 10 |

| 2A2                         | 14 | 35 | — 28 <sub>1</sub>  |

| V <sub>CC</sub> —           | 15 | 34 | - 2B <sub>2</sub>  |

| 2A3-                        | 16 | 33 | _ 2B <sub>3</sub>  |

| GND —                       | 17 | 32 | - GND              |

| -                           | 18 | 31 | - 2B <sub>4</sub>  |

| ~                           | 19 | 30 | — 2B <sub>5</sub>  |

| 2A <sub>6</sub> —           | 20 | 29 | - 28 <sub>6</sub>  |

| <sup>2</sup> A <sub>7</sub> | 21 | 28 | —2В <sub>7</sub>   |

| 2Ag                         | 22 | 27 | -28 <sub>8</sub>   |

| 2Ag                         | 23 | 26 | -2Bg               |

| 2A <sub>10</sub> —          | 24 | 25 | 28 <sub>1.0</sub>  |

|                             |    |    |                    |

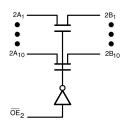

# Logic Diagram

### Truth Table

| its             | Inputs/Outputs |                        |  |  |  |

|-----------------|----------------|------------------------|--|--|--|

| OE <sub>2</sub> | 1A, 1B         | 2A, 2B                 |  |  |  |

| L               | 1A = 1B        | 2A = 2B                |  |  |  |

| н               | 1A = 1B        | Z                      |  |  |  |

| L               | Z              | 2A = 2B                |  |  |  |

| н               | Z              | Z                      |  |  |  |

|                 | L              | L 1A = 1B<br>H 1A = 1B |  |  |  |

# Pin Descriptions

| Pin Name                           | Description        |  |  |

|------------------------------------|--------------------|--|--|

| $\overline{OE}_1, \overline{OE}_2$ | Bus Switch Enables |  |  |

| 1A, 2A                             | Bus A              |  |  |

| 1B, 2B                             | Bus B              |  |  |

FST16210 20-Bit Bus Switch

Features

- $4\Omega$  switch connection between two ports.

- Minimal propagation delay through the switch.

- Low I<sub>CC</sub>.

- Zero bounce in flow-through mode.

- Control inputs compatible with TTL level.

Revised December 1999

November 1998

# Absolute Maximum Ratings(Note 1)

| Supply Voltage (V <sub>CC</sub> )                                    | -0.5V to +7.0V   |

|----------------------------------------------------------------------|------------------|

| DC Switch Voltage (V <sub>S</sub> )                                  | -0.5V to +7.0V   |

| DC Input Voltage (VIN) (Note 2)                                      | -0.5V to +7.0V   |

| DC Input Diode Current (I <sub>IK</sub> ) V <sub>IN</sub> <0V        | –50mA            |

| DC Output (I <sub>OUT</sub> ) Sink Current                           | 128mA            |

| DC V <sub>CC</sub> /GND Current (I <sub>CC</sub> /I <sub>GND</sub> ) | +/- 100mA        |

| Storage Temperature Range (T <sub>STG</sub> )                        | -65°C to +150 °C |

|                                                                      |                  |

# Recommended Operating Conditions (Note 3)

| Power Supply Operating (V <sub>CC)</sub>         | 4.0V to 5.5V     |

|--------------------------------------------------|------------------|

| Input Voltage (V <sub>IN</sub> )                 | 0V to 5.5V       |

| Output Voltage (V <sub>OUT</sub> )               | 0V to 5.5V       |

| Input Rise and Fall Time $(t_r, t_f)$            |                  |

| Switch Control Input                             | 0nS/V to 5nS/V   |

| Switch I/O                                       | 0nS/V to DC      |

| Free Air Operating Temperature (T <sub>A</sub> ) | -40 °C to +85 °C |

Note 1: The "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the Electrical Characteristics tables are not guaranteed at the absolute maximum rating. The "Recommended Operating Conditions" table will define the conditions for actual device operation.

Note 2: The input and output negative voltage ratings may be exceeded if the input and output diode current ratings are observed.

Note 3: Unused control inputs must be held high or low. They may not float.

# **DC Electrical Characteristics**

|                 | Parameter                             | V <sub>CC</sub><br>(V) | $T_A = -40 \ ^\circ C \ to \ +85 \ ^\circ C$ |                 |      |       |                                         |

|-----------------|---------------------------------------|------------------------|----------------------------------------------|-----------------|------|-------|-----------------------------------------|

| Symbol          |                                       |                        | Min                                          | Typ<br>(Note 4) | Мах  | Units | Conditions                              |

| V <sub>IK</sub> | Clamp Diode Voltage                   | 4.5                    |                                              |                 | -1.2 | V     | I <sub>IN</sub> = -18mA                 |

| V <sub>IH</sub> | HIGH Level Input Voltage              | 4.0-5.5                | 2.0                                          |                 |      | V     |                                         |

| V <sub>IL</sub> | LOW Level Input Voltage               | 4.0-5.5                |                                              |                 | 0.8  | V     |                                         |

| l <sub>l</sub>  | Input Leakage Current                 | 5.5                    |                                              |                 | ±1.0 | μΑ    | 0≤ V <sub>IN</sub> ≤5.5V                |

|                 |                                       | 0                      |                                              |                 | 10   | μΑ    | $V_{IN} = 5.5V$                         |

| I <sub>OZ</sub> | OFF-STATE Leakage Current             | 5.5                    |                                              |                 | ±1.0 | μΑ    | 0 ≤A, B ≤V <sub>CC</sub>                |

| R <sub>ON</sub> | Switch On Resistance                  | 4.5                    |                                              | 4               | 7    | Ω     | $V_{IN} = 0V, I_{IN} = 64mA$            |

|                 | (Note 5)                              | 4.5                    |                                              | 4               | 7    | Ω     | $V_{IN} = 0V, I_{IN} = 30mA$            |

|                 |                                       | 4.5                    |                                              | 8               | 12   | Ω     | $V_{IN} = 2.4V, I_{IN} = 15mA$          |

|                 |                                       | 4.0                    |                                              | 11              | 20   | Ω     | $V_{IN} = 2.4V, I_{IN} = 15mA$          |

| I <sub>CC</sub> | Quiescent Supply Current              | 5.5                    |                                              |                 | 3    | μA    | $V_{IN} = V_{CC}$ or GND, $I_{OUT} = 0$ |

| $\Delta I_{CC}$ | Increase in I <sub>CC</sub> per Input | 5.5                    |                                              |                 | 2.5  | mA    | One input at 3.4V                       |

|                 |                                       |                        |                                              |                 |      |       | Other inputs at V <sub>CC</sub> or GND  |

Note 4: Typical values are at  $V_{CC}$  = 5.0V and  $T_A$  = +25°C

Note 5: Measured by the voltage drop between A and B pins at the indicated current through the switch. On resistance is determined by the lower of the voltages on the two (A or B) pins.

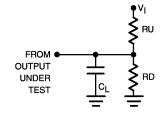

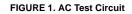

# **AC Electrical Characteristics**

| Symbol                              | Parameter                         |                     | $T_A = -40 \text{ °C to } +85 \text{ °C},$<br>$C_L = 50 \text{pF}, \text{RU} = \text{RD} = 500 \Omega$ |     |                 |    | Conditions                                             | Figure No.            |

|-------------------------------------|-----------------------------------|---------------------|--------------------------------------------------------------------------------------------------------|-----|-----------------|----|--------------------------------------------------------|-----------------------|

| Symbol                              |                                   | V <sub>CC</sub> = 4 | $V_{CC}=4.5-5.5V$                                                                                      |     | $V_{CC} = 4.0V$ |    | Conditions                                             | i igure No.           |

|                                     |                                   | Min                 | Max                                                                                                    | Min | Max             |    |                                                        |                       |

| t <sub>PHL</sub> ,t <sub>PLH</sub>  | Prop Delay Bus to Bus<br>(Note 6) |                     | 0.25                                                                                                   |     | 0.25            | ns | V <sub>I</sub> = OPEN                                  | Figure 1,<br>Figure 2 |

| t <sub>PZH</sub> , t <sub>PZL</sub> | Output Enable Time                | 1.5                 | 6.0                                                                                                    |     | 6.5             | ns | $V_I = 7V$ for $t_{PZL}$<br>$V_I = OPEN$ for $t_{PZH}$ | Figure 1,<br>Figure 2 |

| t <sub>PHZ</sub> , t <sub>PLZ</sub> | Output Disable Time               | 1.5                 | 7.0                                                                                                    |     | 7.2             | ns | $V_I = 7V$ for $t_{PLZ}$<br>$V_I = OPEN$ for $t_{PHZ}$ | Figure 1,<br>Figure 2 |

Note 6: This parameter is guaranteed by design but is not tested. The bus switch contributes no propagation delay other than the RC delay of the typical On resistance of the switch and the 50pF load capacitance, when driven by an ideal voltage source (zero output impedance).

### Capacitance (Note 7)

| Symbol           | Parameter                     | Тур | Max | Units | Conditions                     |

|------------------|-------------------------------|-----|-----|-------|--------------------------------|

| C <sub>IN</sub>  | Control pin Input Capacitance | 3   |     | pF    | $V_{CC} = 5.0V$                |

| C <sub>I/O</sub> | Input/Output Capacitance      | 6   |     | pF    | $V_{CC}, \overline{OE} = 5.0V$ |

Note 7:  $T_A = +25^{\circ}C$ , f = 1 MHz, Capacitance is characterized but not tested.

# AC Loading and Waveforms

Note: Input driven by 50  $\Omega$  source terminated in 50  $\Omega$  Note: CL includes load and stray capacitance

**Note:** Input PRR = 1.0 MHz,  $t_W = 500$  ns

FST16210

www.fairchildsemi.com