Data Sheet January 21, 2005 FN8239.1

## SMBus Accelerator (SMA)

The ISL88694 SMBus accelerator (SMA) is a dual active pull-up bus terminator designed to improve data transmission speed on SMBus or similar 2-wire serial bus interfaces. The ISL88694 is also compatible to the I<sup>2</sup>C serial bus.

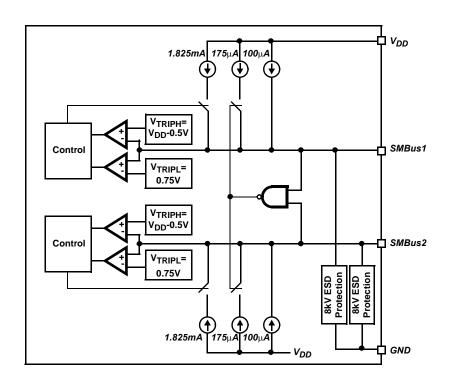

The SMA detects rising input transitions with two internal voltage references and two comparators per channel. After the voltage on a data line crosses the first threshold (V<sub>TRIPL</sub>), the boost pull-up current source is activated to speed transition. After the voltage crosses the second threshold (V<sub>TRIPH</sub>), the boost pull-up current source is deactivated, leaving an active pull-up current of 275 $\mu$ A on the line. When both channels are HIGH, the pull-up current for both lines is reduced to 100 $\mu$ A to save power. Internal logic ensures that the active and boost pull-up current sources are not activated during downward transitions.

The level for  $V_{TRIPH}$  is controlled by a bandgap voltage referred to  $V_{DD}$ . This feature makes the switching behavior invariant for all power supply voltages between 2.7V and 5.5V.

A noise filter on cachichain el prevens the circuit from responding to input transit bis that do receve ed a voltage-time threshold. To activate the boost circuit, the input must exceed V<sub>TRIPI</sub> by 100Vns (typical) (See Figure 10).

The SMA permits operation of the bus at frequencies up to 100kHz, despite the capacitive loads of multiple devices and/or long PC board traces. Enhanced ESD protection on the accelerator pins are guaranteed to withstand 8kV ESD (HBM) events.

The SMBus Accelerator provides an essential function in SMBus applications because of distributed capacitance of SMBus and multiple device input capacitances at various nodes. By incorporating SMA, systems using SMBus or I<sup>2</sup>C can reliably increase their bus load without the risk of data loss.

# Ordering Information

| PART NUMBER         | PACKAGE             | TEMP RANGE (°C) |

|---------------------|---------------------|-----------------|

| ISL88694IH5         | 5-pin SOT           | -40 to 85       |

| ISL88694IH5Z (Note) | 5-pin SOT (Pb-Free) | -40 to 85       |

Add "-TK" suffix for tape and reel.

NOTE: Intersil Pb-free products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate termination finish, which are RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

### Features

- · Active Termination for SMBus lines

- · Enhances System Bus Signal Rise Time

- · Increases Bus Capacity While Guaranteeing Data Integrity

- · 2.2mA Rise Time Supply Current

- · 8kV ESD Protection on SDA and SCL Pins

- · Wide Operating Voltage Range: 2.7V to 5.5V

- 2-Wire SMBus and I<sup>2</sup>C Compatible (100kHz)

- · Small Package SOT23-5

- · Pin-for-Pin Compatible with the LTC1694

- · Pb-Free Available (RoHS Compliant)

## **Target Applications**

- Servers

- · Data Acquisition

- Routers

- · Battery Chargers

- PC

- Facilities Tracking System

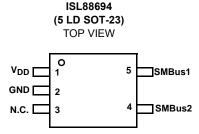

### **Pinout**

# Pin Descriptions

| SOT-23 | SYMBOL   | DESCRIPTION              |

|--------|----------|--------------------------|

| 1      | $V_{DD}$ | Supply Voltage           |

| 2      | GND      | Ground                   |

| 3      | N.C.     | No Connect               |

| 4      | SMBus1   | Active Pull-Up for SMBus |

| 5      | SMBus2   | Active Pull-Up for SMBus |

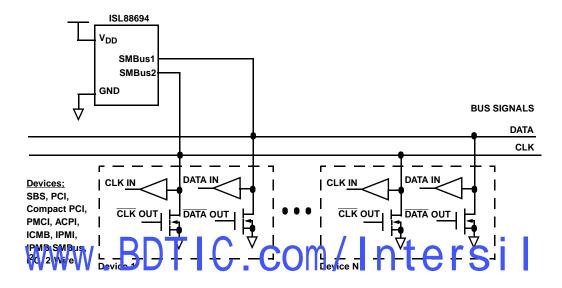

# System Diagram

# IC Block Diagram

### **Absolute Maximum Ratings**

### **Recommended Operating Conditions**

| Supply Voltage Range                     | 1V to 6.5V             |

|------------------------------------------|------------------------|

| Operating Junction Temperature           | +135°C                 |

| Storage Temperature Range                | 65°C to +150°C         |

| Voltage on pins                          | 0.3V to $V_{DD}$ +0.3V |

| Lead temperature (soldering, 10 seconds) | 300°C                  |

| ESD min other pins (HBM)                 | >2kV                   |

| ESD SMBus1 and SMBus2 pins (HBM)         | >8kV                   |

Temperature

-40°C to +85°C

Supply Voltage

2.7V to 5.5V

CAUTION: Absolute Maximum Ratings indicate limits beyond which permanent damage to the device and impaired reliability may occur. These are stress ratings provided for information only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification are not implied.

For guaranteed specifications and test conditions, see Electrical Specifications. The guaranteed specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions.

# **Electrical Specifications** Over operating conditions unless otherwise specified, Typical values are measured at $V_{DD}$ = 3.3V and $T_A$ = +25°C

| SYMBOL               | PARAMETER                                       | CONDITIONS                                                         | MIN                   | TYP                    | MAX                    | UNIT   |  |  |  |

|----------------------|-------------------------------------------------|--------------------------------------------------------------------|-----------------------|------------------------|------------------------|--------|--|--|--|

| ANALOG PARAMETERS    |                                                 |                                                                    |                       |                        |                        |        |  |  |  |

| $V_{DD}$             | Supply Voltage Range                            |                                                                    | 2.7                   |                        | 5.5                    | V      |  |  |  |

| V <sub>DD RAMP</sub> | V <sub>DD</sub> Ramp Rate                       |                                                                    | 0.05                  |                        | 50                     | V/msec |  |  |  |

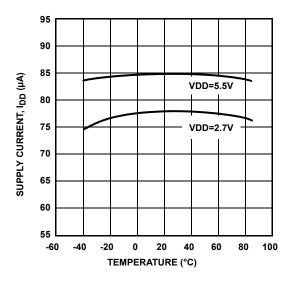

| I <sub>DD</sub>      | Supply Current                                  | SMBus1=SMBus2=Open                                                 |                       | 80                     | 100                    | μA     |  |  |  |

| I <sub>OUT_SB</sub>  | Standby Pull-Up Current                         | SMBus1=SMBus2=V <sub>DD</sub> -1.0V                                |                       | 80                     | 125                    | μA     |  |  |  |

| I <sub>OUT_A1</sub>  | Active Pull-Up Current                          | SMBus1=GND; SMBus2=Open                                            | 125                   | 275                    | 350                    | μA     |  |  |  |

| I <sub>OUT_A2</sub>  |                                                 | SMBus1= Open; SMBus2=GND                                           | 125                   | 275                    | 350                    | μA     |  |  |  |

| I <sub>OUT_B1</sub>  | Boost Pull-Up Current (Figure 1)                | V <sub>TRIPL</sub> <smbus1<v<sub>TRIPH, SMBus2=Open</smbus1<v<sub> | 1.6                   | 2.2                    |                        | mA     |  |  |  |

| I <sub>OUT_B2</sub>  | l www Bl                                        | V <sub>T RIPL</sub> : SMBus2 <v<sub>T RIPL SMBus1=Dper</v<sub>     | <b>1</b> 1.6          | 2.                     |                        | mA     |  |  |  |

| V <sub>TRIPL</sub>   | Input Voltage Threshold Low                     | 1 0 . 00                                                           | 0.65                  | 0.75                   | 0.85                   | V      |  |  |  |

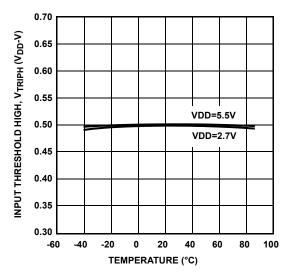

| V <sub>TRIPH</sub>   | Input Voltage Threshold High                    |                                                                    | V <sub>DD</sub> -0.60 | V <sub>DD</sub> - 0.50 | V <sub>DD</sub> - 0.40 | V      |  |  |  |

| f <sub>MAX</sub>     | SMBus Max Frequency                             |                                                                    |                       |                        | 100                    | kHz    |  |  |  |

| NSS                  | Noise Spike Suppression<br>(Note 1) (Figure 10) |                                                                    |                       | 20                     |                        | V-nsec |  |  |  |

#### NOTES:

1. Measured as area under triangular waveform above  $V_{TRIPL}$ , with time as base and  $V_{IN}$  as height (See Figure 10).

intersil

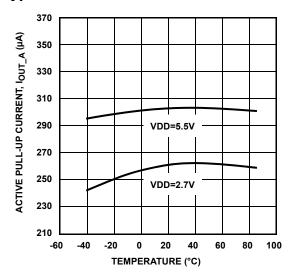

# **Typical Performance Curves**

FIGURE 1. ACTIVE PULL-UP CURRENT. SMBus PIN=0V

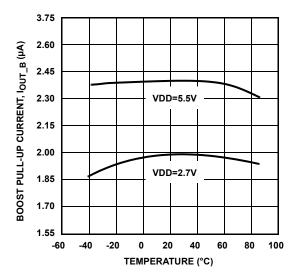

FIGURE 2. BOOST PULL-UP CURRENT. SMBus PIN =  $V_{DD}/2$ .

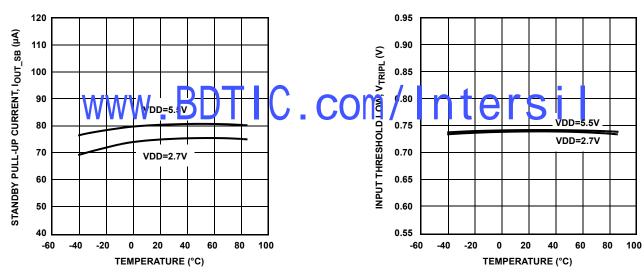

FIGURE 3. STANDBY PULL-UP CURRENT. SMBus1,2= $V_{DD}$ -0.5V

FIGURE 4. V<sub>TRIPL</sub> VOLTAGE

## Typical Performance Curves (Continued)

FIGURE 5. V<sub>TRIPH</sub> VOLTAGE

FIGURE 6. IDD CURRENT. SMBus1=SMBus2=OPEN.

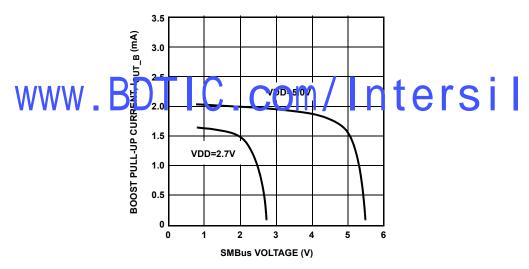

FIGURE 7. BOOST PULL-UP CURRENT vs. SMBus VOLTAGE

## **Functional Description**

### SMBus Overview

The SMBus or I<sup>2</sup>C bus is a 2-wire multimaster bus, meaning that more than one device connected to the bus is capable of controlling it. Master devices communicate to other master or slave devices using one clock and one data line. These are both bidirectional.

In order to allow multimaster operation without bus contention, it is necessary to allow each bus to be connected to a positive supply voltage via a current-source or pull-up resistor (see "System Diagram" on page 2). When the bus is free, both lines are HIGH. The output stages of devices

connected to the bus must have an open-drain or opencollector to perform the wired-AND function.

Simple pull-up resistors on the clock and data lines work well unless there are long signal lines or many devices connected to the bus. Then, the combined capacitance of the bus increases the rise time on the signal to such an extent that the communication becomes unreliable or fails to meet the bus timing specifications. Smaller resistors can sometimes compensate for the extra capacitance, but this increases the current consumption when the signal lines are pulled LOW.

FN8239.1 January 21, 2005

5V/DIV

### ISL88694 Operation

1V/DIV

R=15.8K

C= 200pF

To improve the operation of the SMBus where larger bus capacitance exists, the ISL88694 provides active pull-up using switched current sources. When the bus is idle and both lines are HIGH, a standby pull-up current of  $100\mu A$  is used to maintain the signal level while minimizing power consumption. When either of the two signals is pulled LOW, an active pull-up current of  $275\mu A$  maintains a good  $V_{OL}$  noise margin.

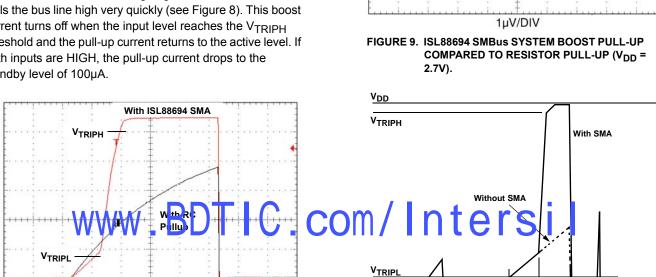

When the bus line is released, it is pulled high by the ISL88694 active current until the voltage exceeds the  $V_{TRIPL}$  level for a period of time. This voltage-time combination filters out noise on the signal line. Once the ISL88694 detects a valid rising edge, a 2.2mA boost current pulls the bus line high very quickly (see Figure 8). This boost current turns off when the input level reaches the  $V_{TRIPH}$  threshold and the pull-up current returns to the active level. If both inputs are HIGH, the pull-up current drops to the standby level of  $100\mu A$ .

Gnd / SMBus1 SMBus2

FIGURE 8. ISL88694 SMBus SYSTEM BOOST PULL-UP COMPARED TO RESISTOR PULL-UP ( $V_{DD} = 5.5V$ ).

1µs/DIV

FIGURE 10. NOISE SUPPRESSION. BOOST CURRENT APPLIED WHEN INPUT SIGNAL EXCEEDS 20Vns (TYPICAL).

>20Vns

(Typical)

With ISL88694 SMA

With RC

Pullup

$V_{TRIPH}$

VTRIPL

R=15.8K

C= 200pF

FN8239.1 January 21, 2005

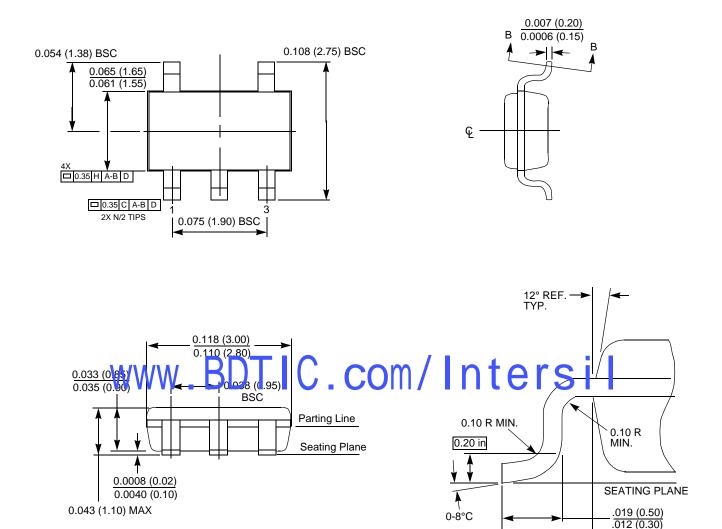

## Package Outline Drawing

### 5-Lead, SOT23, Package Code H5

### NOTES:

- 1. ALL DIMENSIONS IN INCHES (IN PARENTHESES IN MILLIMETERS)

- 2. PACKAGE DIMENSIONS EXCLUDE MOLDING FLASH

- 3. DIMENSIONING AND TOLERANCES PER ASME, Y14.5-1994

- 4. THIS PART IS COMPLIANT WITH JEDEC SPECIFICATION MO-193.

- 5. THIS PART IS FULL COMPLIANCE TO EIAJ SPECIFICATION SC-74

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

0.575 REF.